UVM_Errata_new_final

UVM实战指南范文

UVM实战指南范文UVM(Universal Verification Methodology)是一种基于SystemVerilog语言的验证方法学,广泛应用于硬件验证领域。

在UVM中,通过建立一个可重复使用的测试环境,结合使用事务级建模(TLM)和事务级验收测试(TLM),实现了分层、模块化的测试方法,提高了验证效率和可复用性。

一、UVM基础知识1.UVM组成:UVM主要由以下几个组成部分组成:- testbench:测试平台,包括环境、测试、配置和结果收集。

- environment:包含需要被验证的设计和其他组件,如计时模型(TLM)和监控器。

- agent:代理,用于管理测试和设计之间的数据传输和控制通信。

- sequence:序列,用于控制测试向设计发送输入和观察输出。

- driver:驱动器,控制从测试平台发送数据到设计。

- monitor:监控器,从设计中监听信号和寄存器的值。

- scoreboard:比分板,用于比较设计的输出和期望的输出。

2. UVM中的消息系统:UVM中的消息系统可以用于在验证过程中传递和显示消息信息。

消息分为几个级别,如UVM_DEBUG、UVM_INFO、UVM_WARNING和UVM_ERROR等。

通过设置消息级别,可以控制消息的显示和记录。

在UVM中,可以使用`uvm_info(`,`uvm_warning(`,`uvm_error(`等函数来生成和发送消息。

二、UVM测试环境构建1.UVM测试环境构建:UVM测试环境的构建遵循一个分层、模块化的方法。

首先,可以定义一个基础环境,包含全局配置和全局测试。

然后,可以在基础环境的基础上构建更高级的环境,如顶层环境和模块环境。

在每个环境中,可以定义组件(如代理、序列和监控器)和接口,然后进行连接。

三、UVM测试流程1.UVM测试配置:首先,可以使用UVM配置对象来指定测试的配置选项,如时钟频率和寄存器的初始值。

uvm 基础知识

uvm 基础知识UVM是一种基于SystemVerilog语言的硬件验证方法学,它为验证工程师提供了一套验证环境和方法,帮助他们设计和开发复杂的硬件验证测试台。

以下为UVM的基础知识:1. UVM环境:UVM环境由各种组件组成,包括顶层测试环境,验证IP,驱动(driver),监控(monitor),事务(transaction),序列(sequence)和配置参数等。

2. UVM顶层测试环境:UVM顶层测试环境是UVM环境的主体,它实例化和连接各种验证组件,管理验证过程和数据路径。

3. 驱动(Driver):驱动是UVM环境的一个组件,负责将测试向硬件发送数据。

它接收事务(transaction)并将其转换为物理信号发送到被测设备。

4. 监控(Monitor):监控是UVM环境的一个组件,用于监听硬件信号并将其转换为事务(transaction)。

它将被测设备的输出信号捕获并生成与之对应的事务。

5. 事务(Transaction):事务是UVM环境中的一种数据结构,它封装了验证过程中的数据和控制信息。

事务用于在驱动和监控之间传递数据。

6. 序列(Sequence):序列是UVM环境中的一个组件,用于生成一系列的事务。

序列定义了事务的数据和控制信息,以及生成和管理事务序列的逻辑。

7. UVM Testbench:UVM Testbench是UVM环境的一部分,它是整个验证环境的顶层组织结构。

UVM Testbench包含了顶层测试环境、监控、驱动、序列等组件。

8. 配置参数:UVM使用一种叫作配置参数(configuration parameter)的机制,用于动态地配置和管理各种验证组件的行为和功能。

9. UVM测试用例:UVM测试用例是UVM环境中的一个组件,它描述了验证目标的特定功能和行为。

测试用例通常由一个或多个序列组成,用来生成一系列的事务。

以上是UVM的基础知识,了解这些概念可以帮助你更好地理解和应用UVM验证方法学。

uvm警告reading unwritten address -回复

uvm警告reading unwritten address -回复[UVM警告读取未被写入的地址]引言:在使用UVM(Universal Verification Methodology)进行硬件验证时,我们经常会遇到各种警告和错误。

其中,一个常见的警告是“UVM警告:读取未被写入的地址”。

这个警告意味着我们正在尝试读取一个在写入之前未被初始化的地址。

本文将一步一步回答关于这个警告的问题,并提供解决方案,以确保我们的硬件验证流程的正确性和性能。

第一步:了解UVM警告首先,我们需要了解为什么会出现这个警告。

当我们尝试读取一个未被写入的地址时,UVM会通过生成一个警告来提醒我们潜在的问题。

这是因为未初始化的数据可能会导致验证流程中的错误或不确定行为。

第二步:识别警告来源在遇到这个警告时,我们需要找出是哪个部分的代码导致了这个问题。

最常见的情况是在测试程序中,我们可能会在发送数据之前尝试读取数据。

因此,我们需要检查测试中的代码,并确认是否存在这样的错误。

第三步:检查初始化过程一旦我们找到了潜在的警告来源,我们需要确保在读取之前已经正确初始化了相应的地址。

这可以通过仔细检查初始化过程来完成。

在初始化过程中,我们应该确认所有的地址都被正确地写入了初始值。

第四步:验证环境中的数据我们还需要检查验证环境中的数据是否正确传输到了待验证的组件。

如果数据未能正确地传输到目标组件,则可能导致读取未被写入的地址。

因此,我们需要检查数据传输的路径,并确保数据在正确的时间和位置上被正确传输。

第五步:添加错误检查和处理机制为了避免读取未被写入的地址,我们可以在代码中添加错误检查和处理机制。

一种方法是在读取之前检查地址是否已经被初始化。

如果地址未被写入,我们可以选择向用户发出警告、报告错误或采取其他适当的行动。

第六步:进行综合和仿真验证一旦我们对代码进行了修改,并添加了错误处理机制,我们需要进行综合和仿真验证。

通过这些验证步骤,我们可以确保我们的修改不会导致其他错误,并且解决了读取未被写入地址的问题。

uvm验证题库

uvm验证题库摘要:1.UVM 验证题库简介2.UVM 验证题库的作用和意义3.如何使用UVM 验证题库4.UVM 验证题库的优缺点正文:一、UVM 验证题库简介UVM(Universal Verification Methodology)验证方法学是一种验证电子设计自动化(EDA)技术的标准,主要用于验证数字集成电路和片上网络(NoC)。

UVM 验证题库是一个基于UVM 标准的库,包含了许多用于验证不同类型电路的模板和例子。

二、UVM 验证题库的作用和意义UVM 验证题库的主要作用是为验证工程师提供一个标准化、可重用的验证环境,从而提高验证效率和质量。

使用UVM 验证题库的意义主要体现在以下几点:1.提高验证效率:通过使用已有的验证模板和例子,验证工程师可以避免重复性的工作,将更多的精力投入到核心逻辑的验证上。

2.保证验证质量:UVM 验证题库遵循统一的验证方法学标准,有助于确保验证环境的一致性和完整性,从而提高验证的准确性和可靠性。

3.便于团队协作:使用UVM 验证题库可以统一团队的验证环境,降低不同验证工程师之间的沟通成本,提高团队协作效率。

三、如何使用UVM 验证题库使用UVM 验证题库的步骤如下:1.学习UVM 验证方法学:熟悉UVM 的基本概念、术语和操作方法,为使用UVM 验证题库打下基础。

2.获取UVM 验证题库:可以从官方或第三方网站下载UVM 验证题库,或者根据项目需求自行创建。

3.配置UVM 验证环境:根据项目需求,选择合适的UVM 验证题库模板,配置相应的环境参数,搭建验证环境。

4.编写验证脚本:利用UVM 验证题库中的模板和例子,编写验证脚本,对电路进行功能性和性能验证。

5.分析验证结果:运行验证脚本,分析验证结果,对电路进行调试和优化。

四、UVM 验证题库的优缺点UVM 验证题库的优点包括:1.标准化:遵循UVM 验证方法学标准,有助于提高验证质量和效率。

2.可重用:包含大量可重用的验证模板和例子,降低验证工程师的工作负担。

uvm new函数

uvm new函数UVM New函数UVM(Universal Verification Methodology,通用验证方法学)是一种用于硬件验证的开发方法学。

它提供了使用SystemVerilog语言进行验证的一系列类和方法,使得验证工程师能够更高效地开发和管理验证环境。

在UVM中,使用到了许多不同的函数和类,其中一个重要的函数就是new函数。

new函数是UVM中用于创建对象的函数。

它的作用是在运行时动态地分配内存并构造对象。

使用new函数,可以方便地创建各种需要的对象,从而构建出复杂的验证环境。

在UVM中,使用new函数创建对象的语法如下:```my_object = new("my_object");```这里,my_object是要创建的对象的句柄,"my_object"是对象的名称。

通过调用new函数,可以在运行时创建一个名为"my_object"的对象,并将其句柄赋值给my_object。

new函数的参数可以是一个字符串,也可以是一个类或对象的类型。

当参数为字符串时,new函数会根据字符串的内容来决定创建哪种类型的对象。

当参数为类型时,new函数会直接创建该类型的对象。

除了创建对象外,new函数还可以接受其他参数,用于初始化对象的成员变量。

例如:```my_object = new("my_object", 10, "hello");```这里,除了传入对象名称外,还传入了两个额外的参数10和"hello",用于初始化my_object对象的成员变量。

在UVM中,new函数的返回值是一个对象的句柄。

通过该句柄,可以访问和操作对象的各个成员变量和方法。

使用new函数创建对象后,可以通过delete函数销毁对象并释放内存。

delete函数的语法如下:```delete my_object;```这里,my_object是要销毁的对象的句柄。

uvm知识点总结

uvm知识点总结UVM 架构UVM 的架构包括以下几个重要部分:1. UVM 库 (UVM Library): UVM 库是一个可复用的验证组件集合,包含了多个验证类,如uvm_component、uvm_object、uvm_sequence 等,这些类组成了 UVM 框架。

2. UVM Testbench: UVM Testbench 是一个验证环境框架,它是基于 UVM 库构建起来的,用于创建验证环境、生成测试用例、进行仿真等。

3. UVM Test: UVM Test 是一个测试用例,主要由 UVM sequence 和 UVM 配置对象构成,它是用来验证被测试设计的功能是否正确。

4. UVM Agent: UVM Agent 是一个验证组件,是用于连接被测试设计和验证环境的中间层;它包括了 driver、monitor、sequence、sequencer 等。

基本概念UVM 中的一些基本概念包括以下内容:1. UVM Component: UVM 组件是 UVM 测试环境中的基本单元,用于组织和管理验证环境中的各种功能。

UVM 组件包括了 uvm_component、uvm_object、uvm_sequence 等。

2. UVM Object: UVM 对象是 UVM 中的一个基本概念,它是 uvm_component、uvm_sequence 和 uvm_transaction 的基类,用于实现类似于面向对象编程的功能。

3. UVM Phase: UVM 通过阶段 (Phase) 来管理验证环境的初始化、运行和结束等过程。

UVM 提供了一系列的任务来进行阶段的管理,如 uvm_phase、uvm_sequence、uvm_objection 等。

4. UVM Transaction: UVM 事务是指在验证中进行的交互过程,包括了数据传输、信号传递、命令执行等;UVM 提供了 uvm_transaction 类来实现事务级建模。

uvm仿真超时解决方法

(原创实用版3篇)编制人员:_______________审核人员:_______________审批人员:_______________编制单位:_______________编制时间:____年___月___日序言下面是本店铺为大家精心编写的3篇《uvm仿真超时解决方法》,供大家借鉴与参考。

下载后,可根据实际需要进行调整和使用,希望能够帮助到大家,谢射!(3篇)《uvm仿真超时解决方法》篇1UVM(Universal Verification Methodology)是一种用于验证数字电路设计的仿真方法。

在 UVM 仿真过程中,如果出现超时现象,可能有以下几种原因: 1. 仿真时间过长:UVM 仿真需要耗费大量时间,特别是在设计规模较大、仿真精度要求较高时,可能需要较长的时间来完成。

如果仿真时间过长,可能会导致仿真超时。

2. 仿真平台不稳定:UVM 仿真需要一个稳定的仿真平台,如果平台出现故障或不稳定,可能会导致仿真超时。

3. 代码优化不足:在 UVM 仿真中,代码的优化程度也会影响仿真速度。

如果代码优化不足,可能会导致仿真超时。

针对以上问题,可以采取以下措施来解决 UVM 仿真超时的问题:1. 优化仿真参数:调整仿真参数,如减小仿真精度、减少仿真时间等,以缩短仿真时间。

2. 优化代码:对代码进行优化,如减少不必要的计算、优化数据结构等,以提高仿真速度。

3. 更换仿真平台:如果仿真平台不稳定,可以考虑更换仿真平台,以获得更稳定的仿真环境。

4. 检查网络连接:如果 UVM 仿真是在网络环境下进行的,需要检查网络连接是否稳定,以确保数据传输的畅通。

总之,针对 UVM 仿真超时的问题,需要根据具体情况采取不同的解决方法。

《uvm仿真超时解决方法》篇2UVM(Universal Verification Methodology)是一种验证方法论,用于验证数字电路和系统的正确性和性能。

在 UVM 仿真中,如果出现超时的情况,可能有以下几种解决方法:1. 检查仿真时间参数:在 UVM 仿真中,可以通过设置时间参数来控制仿真的速度和准确性。

uvm 句柄-概述说明以及解释

uvm 句柄-概述说明以及解释1.引言1.1 概述UVM(Universal Verification Methodology)是一种用于验证设计(Design)与验证环境(Testbench)之间交互的标准方法学。

它提供了一种结构化的方式来开发、组织和管理验证环境。

在UVM中,句柄(Handle)是一种重要的概念,它是指对UVM组件或对象的引用,可以通过句柄来访问和操作这些组件或对象。

句柄为工程师提供了方便和灵活性,使得他们能够快速且有效地操控各种验证元素,从而提高了验证的效率。

本文将对UVM句柄进行详细的介绍和讨论。

首先,我们将介绍UVM 框架的基本概念和结构,以便读者了解UVM的基础知识。

然后,我们将深入探讨UVM句柄的概念和特性,包括句柄的定义和类型,以及如何使用句柄来操作UVM对象。

最后,我们将介绍UVM句柄的应用场景,包括在验证环境中的使用和设计模式。

通过阅读本文,读者可以全面了解UVM句柄的重要性和作用,并且能够在实际的验证工作中灵活运用句柄来提高工作效率。

我们还将展望UVM句柄的未来发展,并对本文进行总结。

1.2文章结构1.2 文章结构本文主要围绕着UVM句柄展开讨论,旨在介绍UVM句柄的概念、应用场景以及其在UVM框架中的重要性。

文章结构如下:引言部分将首先概述本文的主要内容,简要介绍UVM框架以及UVM 句柄的概念,并阐述本文的目的。

正文部分将详细介绍UVM框架的基本原理和核心模块,然后重点深入探讨UVM句柄的概念。

在此背景下,我们将解释UVM句柄在UVM 测试环境中的作用和功能,并提供一些具体的应用场景,以帮助读者更好地理解UVM句柄的实际应用。

结论部分将对本文进行总结,强调UVM句柄在UVM框架中的重要性,并展望UVM句柄的未来发展趋势。

最后,我们将得出结论,并提出对进一步研究和应用UVM句柄的建议。

通过以上结构的设计,本文将全面讲解UVM句柄的概念和应用,为读者提供一个系统而清晰的视角,帮助读者更好地理解和应用UVM句柄。

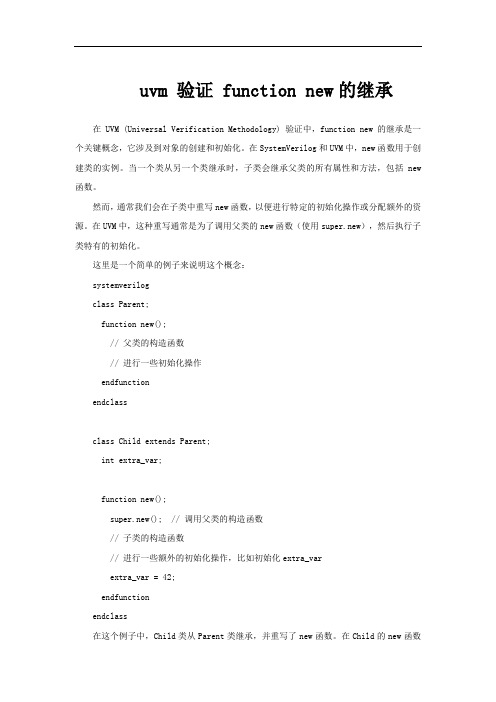

uvm 验证 function new的继承

uvm 验证 function new的继承在UVM (Universal Verification Methodology) 验证中,function new 的继承是一个关键概念,它涉及到对象的创建和初始化。

在SystemVerilog和UVM中,new函数用于创建类的实例。

当一个类从另一个类继承时,子类会继承父类的所有属性和方法,包括new 函数。

然而,通常我们会在子类中重写new函数,以便进行特定的初始化操作或分配额外的资源。

在UVM中,这种重写通常是为了调用父类的new函数(使用super.new),然后执行子类特有的初始化。

这里是一个简单的例子来说明这个概念:systemverilogclass Parent;function new();// 父类的构造函数// 进行一些初始化操作endfunctionendclassclass Child extends Parent;int extra_var;function new();super.new(); // 调用父类的构造函数// 子类的构造函数// 进行一些额外的初始化操作,比如初始化extra_varextra_var = 42;endfunctionendclass在这个例子中,Child类从Parent类继承,并重写了new函数。

在Child的new函数中,我们首先通过super.new()调用父类的构造函数,以确保父类的所有初始化操作都被执行。

然后,我们执行子类特有的初始化操作,比如初始化extra_var。

这种方式确保了对象在创建时得到了正确的初始化,同时也允许子类添加额外的初始化步骤。

这是UVM中创建可重用、模块化验证组件的一个关键方面。

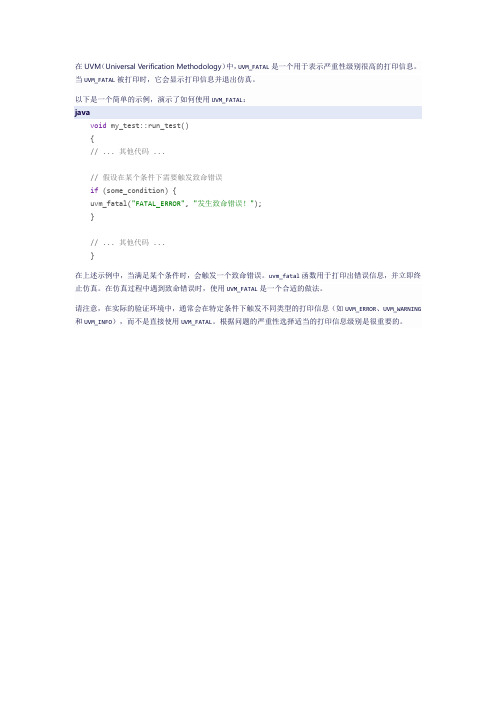

uvm_fatal用法示例

在UVM(Universal Verification Methodology)中,UVM_FATAL是一个用于表示严重性级别很高的打印信息。

当UVM_FATAL被打印时,它会显示打印信息并退出仿真。

以下是一个简单的示例,演示了如何使用UVM_FATAL:

java

void my_test::run_test()

{

// ... 其他代码 ...

// 假设在某个条件下需要触发致命错误

if (some_condition) {

uvm_fatal("FATAL_ERROR", "发生致命错误!");

}

// ... 其他代码 ...

}

在上述示例中,当满足某个条件时,会触发一个致命错误。

uvm_fatal函数用于打印出错误信息,并立即终止仿真。

在仿真过程中遇到致命错误时,使用UVM_FATAL是一个合适的做法。

请注意,在实际的验证环境中,通常会在特定条件下触发不同类型的打印信息(如UVM_ERROR、UVM_WARNING 和UVM_INFO),而不是直接使用UVM_FATAL。

根据问题的严重性选择适当的打印信息级别是很重要的。

uvm_register illegal class method access

在UVM(Universal Verification Methodology)中,uvm_register是一个重要的类,用于注册类实例并跟踪这些实例的名称和类型。

它确保验证环境中对象的唯一性并确保所有对象都被适当地管理。

然而,有时候在访问uvm_register的非法类方法时可能会遇到问题。

非法类方法访问是指试图访问一个不存在的类方法或者该方法已被其他类重写。

这通常发生在试图调用一个不存在的方法或者调用一个被覆盖的方法时。

这可能导致程序运行时错误或者程序行为不符合预期。

要避免非法类方法访问,您应该确保:

1.检查方法名是否正确,确保没有拼写错误。

2.检查类是否拥有该方法,如果没有,可能需要使用继承或其他机制来实现。

3.如果方法已被重写,请确保在正确的上下文中调用该方法。

下面是一个简单的例子来说明非法类方法访问的问题:

在上面的例子中,我们试图将OtherClass 实例作为MyClass 实例来使用,并调用其myMethod 方法。

由于OtherClass 覆盖了MyClass 的myMethod 方法,因此输出的是"OtherClass method",而不是我们期望的"MyClass method"。

这表明在调用方法时必须注意类的实例化,以避免非法类方法访问。

uvm实战-学习笔记

uvm实战-学习笔记预览说明:预览图片所展示的格式为文档的源格式展示,下载源文件没有水印,内容可编辑和复制《UVM实战(卷1)》学习笔记看了第1/2/3/4/5/6/8/9.1这几个章节。

第一章是综述,第二章是一个具体的例子,学习笔记从第三章相关内容开始。

我个人觉得UVM重要的部分(特点的部分):1)factory机制(overrideconfig_db)2)TLM传递3)phase机制4)sequence-sequencer以及virtualseq/sqr内容中的截图基本来自于UVM源代码、书自带的例子和《uvm1.1应用指南及源代码分析》这个PDF里的。

需要结合书(第3也uvm_void常用的是item,当发现有常用的transaction-level向signal-level的转换。

uvm_driver需要参数(REQRSP),比uvm_component增加了几个成员。

重要的是seq_item_port和req/rsp.(src/comps/uvm_driver.svh)monitor/scoreboard派生自uvm_monitor和uvm_scoreboard,但是uvm_monitor和uvm_scoreboard并没有在uvm_component 基础上做扩展。

src/comps/uvm_monitor.svh因为driver和envmacro1)对于2)对于对于`uvm_component_utils(类名)uvm_component里的成员也可以像uvm_object里成员一样,用field_automation机制。

field_automation机制:对于uvm_object派生类来说,field_automation机制让对象自动有的copycompareprintpackunpack等函数,简化了实现uvm_component派生类里一些function/task的工作量对于uvm_component派生类来说,field_automation机制最重要的是可以在build_phase中自动获取uvm_config_db#()::set()的数值(必须加super.build_phase(phase))----也就是不用写uvm_config_db#()::get()注意:field_automation的macro的类型要和uvm_config_db 的参数类型一致:如下示例代码,field_intvsuvm_config_db#(bit[47:0])这个时候super.build_phase()是不起作用的。

uvm二维数组随机化约束

uvm二维数组随机化约束UVM二维数组随机化约束引言:UVM(Universal Verification Methodology)是一种用于验证硬件设计的标准方法学。

在UVM中,随机化是一种常用的测试生成技术,可以有效地生成多样化的测试用例。

本文将探讨如何使用UVM中的约束来随机化二维数组,以增加测试用例的多样性。

1. 什么是二维数组?在编程中,二维数组是一种由行和列组成的数据结构。

它可以用于存储和操作多个数据元素,通常用于表示矩阵、图像等复杂的数据结构。

在UVM中,二维数组广泛应用于测试用例生成和数据分析等方面。

2. UVM中的二维数组随机化约束在UVM中,使用约束(constraint)可以限制随机化生成的值的范围,从而生成符合特定要求的测试用例。

对于二维数组,我们可以通过定义约束来控制每个元素的取值范围和关系。

3. 定义二维数组的约束假设我们要随机化一个2x2的二维数组,每个元素的取值范围是0到9。

我们可以使用UVM的约束语言来定义这个约束:```verilogclass my_array_constraint extends uvm_constraint;rand int unsigned array[0:1][0:1];constraint array_c {foreach(array[i][j]) {array[i][j] inside {[0:9]};}}endclass```在上述代码中,我们使用`rand`关键字定义了一个2x2的二维数组`array`,并使用`constraint`关键字定义了约束`array_c`。

通过`inside`关键字,我们限制了每个元素的取值范围为0到9。

4. 随机化二维数组在UVM中,我们可以使用`uvm_rand_objection`类的`randomize()`函数来随机化二维数组。

在随机化过程中,UVM会自动应用之前定义的约束。

```verilogmy_array_constraint array_constraint;my_array my_array_inst;// 随机化二维数组array_constraint = new("array_constraint");array_constraint.randomize();my_array_inst = new("my_array_inst");my_array_inst.randomize(array_constraint);```通过以上代码,我们创建了一个`my_array_constraint`对象`array_constraint`,并随机化了约束。

uvm debug 技巧

uvm debug 技巧

在UVM中进行调试时,可以使用以下几种技巧:

1. 使用消息日志:UVM提供了消息日志记录功能,可以使用

`uvm_info`和`uvm_error`等宏来打印出日志消息。

通过调整日

志级别,可以控制输出的详细程度。

2. 使用断言:通过在关键位置添加断言语句,可以检查特定的条件是否满足。

如果断言失败,将会自动打印出有关详细信息,帮助我们找出问题所在。

3. 使用波形调试器:可以将UVM测试环境与波形调试器集成

在一起,以便在运行时查看信号波形。

这样可以更直观地了解当前系统的状态,并诊断问题。

4. 设置断点:在关键部分设置断点,可以暂停运行,并在此处检查变量的值和代码行为。

这对于找出逻辑错误和调试复杂的交互作用非常有用。

5. 使用Tracing:通过在关键位置添加跟踪代码,可以捕获测

试活动的关键事件和变量的值,并将其输出到跟踪文件。

通过分析跟踪文件,可以更深入地了解系统的行为和状态。

6. 结合仿真器调试:如果使用仿真器运行UVM测试,可以使

用仿真器的调试功能来观察信号波形、设置触发条件和分析内部状态。

7. 使用GUI调试:一些UVM框架提供了GUI调试功能,允许用户直接在图形界面中查看和操作UVM测试环境的各个部分。

总的来说,UVM调试需要结合各种工具和技术,以便更好地理解系统行为并找出问题所在。

以上只是一些常用的技巧,具体的调试方法和技术取决于具体的情况和工具的支持。

uvm extern用法

uvm extern用法UVM(Universal Verification Methodology)是一种基于SystemVerilog的验证方法学,被广泛应用于硬件设计的验证过程中。

在UVM中,通过定义和使用UVM组件来实现模块化和可重用的验证代码。

在UVM组件之间进行通信和交互的方式之一是使用UVM Extern。

UVM Extern是一种用于建立UVM组件之间连接的机制,它允许我们在不同的UVM组件中共享数据。

通过将需要共享的数据声明为extern变量,并在需要访问这些数据的组件中引用该extern变量,我们可以实现数据的共享和传递。

在使用UVM Extern时,首先需要在UVM组件中声明extern变量。

这可以通过在声明变量时使用`extern`关键字来完成。

例如,我们可以在一个UVM组件中声明一个名为`data`的extern变量:```systemverilogclass MyComponent extends uvm_component;extern int data;// ...endclass```接下来,在需要访问这个extern变量的另一个UVM组件中,我们可以使用`uvm_config_db`这个UVM工具类来获取extern变量的引用。

`uvm_config_db`提供了用于在不同组件之间传递数据的API。

以下是一个示例:```systemverilogclass AnotherComponent extends uvm_component;int data;// ...function void build_phase(uvm_phase phase);super.build_phase(phase);if (!uvm_config_db#(int)::get(this, "", "data", data))`uvm_fatal("DATA_NOT_FOUND", "Failed to get the data usinguvm_config_db")endfunction// ...endclass```在上述代码中,`uvm_config_db#(int)::get`函数用于从之前声明的extern变量中获取data的值,并将其存储在AnotherComponent的data变量中。

uvm的override机制 -回复

uvm的override机制-回复UVM(Universal Verification Methodology)是一种常用于硬件验证的方法学,它提供了一套完整的验证框架和一系列约定。

在UVM中,override机制是一种允许用户修改或覆盖已有功能或方法的机制,它的应用范围广泛且灵活。

本文将逐步解释UVM的override机制的原理、应用以及使用中的注意事项。

首先,我们来了解override机制的工作原理。

在UVM中,override机制允许用户在顶层测试类(即测试环境)中覆盖或修改建立在基础类上的方法。

这些方法可以是UVM仲裁器、UVM序列、UVM端口或UVM组件提供的方法。

当在测试类中调用被重写的方法时,UVM会根据继承链从子类开始向上搜索,找到并运行最合适的重写方法。

这种特性使得用户能够根据具体的需求对框架中的方法进行个性化的修改或扩展。

在实际应用中,override机制有多种用途。

首先,它允许用户在测试环境中对既有的UVM方法进行个性化调整。

例如,在UVM中,UVM序列是用于驱动和监控测试环境中的各种信号和数据的。

通过使用override 机制,用户可以修改序列中的各种方法,使其更适应当前设计的需求。

其次,override机制还可以用于在测试环境中增加新的功能。

例如,用户可以通过重写UVM端口中的方法来实现自定义的通信协议。

这样一来,用户可以轻松地在测试环境中添加对新协议的支持,而无需修改底层硬件设计。

在使用override机制时,有一些值得注意的事项。

首先,把握override 的时机和范围十分重要。

过度使用override可能会导致代码变得复杂且难以维护。

因此,应该仅在必要的情况下使用override来修改或扩展UVM 框架中的方法。

另外,override机制对于继承链的搜索顺序非常敏感。

如果多个类都重写了同一个方法,那么UVM会选择搜索最靠近搜索类的重写方法。

因此,设计者应该明确各个类之间的继承关系,以确保最合适的override方法被调用。

uvm知识点

uvm知识点UVM知识点UVM(Universal Verification Methodology)是一种用于硬件验证的标准方法学。

它提供了一套完整的验证框架和库,可用于设计和验证工程师开发的各种硬件设计。

UVM的主要目标是提高验证效率、加速验证流程,并提供一种可重用性的验证方法。

下面将介绍UVM的几个重要知识点。

1. UVM中的基本概念UVM中有几个基本概念需要理解。

首先是UVM Testbench,它是一个验证环境的集合,包括UVM Agent、UVM Sequence、UVM Driver、UVM Monitor等组件。

UVM Agent是验证环境中的一个重要组成部分,负责模拟设计中的一个或多个接口,并与设计进行通信。

UVM Sequence是一个用于生成测试向量的对象,它通过UVM Driver将测试向量发送给设计。

UVM Monitor是用于监控设计中信号变化的组件。

2. UVM中的消息和日志在UVM中,消息和日志用于记录验证过程中的重要信息。

UVM提供了几种不同级别的消息,包括FATAL、ERROR、WARNING、INFO和DEBUG。

开发人员可以根据需要选择适当的级别来记录不同类型的消息。

UVM还提供了灵活的消息过滤机制,可以根据需求过滤和控制消息的输出。

3. UVM中的事务和序列事务是在UVM中用于描述和传输数据的基本单元。

它包含了一些用于描述数据的字段,例如地址、数据和控制信号等。

事务通常由UVM Sequence生成,并通过UVM Driver发送给设计。

序列是一组事务的集合,用于描述测试向量的生成方式。

UVM提供了丰富的序列控制机制,可以灵活地生成各种测试向量。

4. UVM中的环境配置UVM提供了一种灵活的配置机制,可以在运行时配置验证环境的各个组件。

通过使用UVM的配置对象,可以在运行时修改和控制环境中的各种参数和属性。

这种配置机制可以大大提高验证环境的灵活性和可重用性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

UVM 1.0 Errata DocumentationThis errata document details the Natural Doc (API) changes found in the latest Base Class Library (BCL) release relative to the officially approved Accellera UVM 1.0 spec. The intention of this document is to aid developers utilizing this version of the release so that a very clear set of changes are described.The UVM committee within Accellera provides four documents for the community.1.An officially sanctioned and Accellera approved standards document,also known as our API Reference Guide which describes the UVMfeature by feature in API format. This is considered a specificationdocument for the UVM and anyone can use it to create their ownimplementation (should they choose).2.A BCL implementation of the UVM. This is implemented inSystemVerilog and is a set of base classes and utilities put together to enable the creation of test environments.3.A User‟s Guide. This details an overview of the UVM, what it contains,how it should be used, and methodology recommendations to enable VIP reuse.4.An Errata document. Describes API changes made in the currentrelease of the BCL relative to the officially approved standard.We decided as a committee to release the BCL, UG, and Errata document more often than the standards document. This would allow the UVM implementation and User‟s Guide to be more nimble, responsive, and fluid according to end user needs. This also required however that we detail any changes in the API Natural Docs relative to the approved standard so that EDA companies, 3rd party vendors, and end user developers understood the differences.For this version of errata it is based on the Accellera approved UVM 1.0 version approved on February 18th, 2011. This API spec can be found here: /activities/vip/And is cal led the “Class Reference Manual”.The formatting for this Errata document is as follows:Text shown crossed and red removes existing material. Text shown underlined and blue adds new material without disturbing the existing material.This document is organized according to the main chapters found in the API UVM spec.Base:CHANGE SET #1: Add to uvm_transaction.BCL LOCATION: distrib/src/base/uvm_transaction.svhPDF LOCATION: page 22The uvm_transaction class is the root base class for UVM transactions. Inheriting all the methods of uvm_object, uvm_transaction adds a timing and recording interface.Use of the class uvm_transaction as a base for user-defined transactions is deprecated. Its subtype, uvm_sequence_item, shall be used as the base class for all user-defined transaction types.CHANGE SET #2: Add default values to uvm_phase::new()LOCATION: distrib/src/base/uvm_phases.svhPDF LOCATION: page 55function new( s tring name = "uvm_phase",uvm_phase_type p hase_type = U VM_PHASE_SCHEDULE,uvm_phase parent = n ull )CHANGE SET #3: Change uvm_phase::find()LOCATION: distrib/src/base/uvm_phases.svhPDF LOCATION: page 56Locate the phase node with the specified phase IMP and return its handle. Withstay_in_scope set, searches only within this phase‟s schedule or domain.Locate a phase node with the specified name and return its handle. Look first within the current schedule, then current domain, then globalCHANGE SET #4: Replace uvm_phase::add_phase() and add_schedule() with add()LOCATION: distrib/src/base/uvm_phases.svhPDF LOCATION: page 57Build up a schedule structure inserting phase by phase, specifying linkagePhases can be added anywhere, in series or parallel with existing nodesphase handle of singleton derived imp containing actual functor. by default the new phase is appended to the schedulewith_phase specify to add the new phase in parallel with this oneafter_phase specify to add the new phase as successor to this onebefore_phase specify to add the new phase as predecessor to this oneBuild up schedule structure by adding another schedule flattened within it.Inserts a schedule structure hierarchically within the enclosing schedule'sgraph. It is essentially flattened graph-wise, but the hierarchy is preservedby the 'm_parent' handles which point to that schedule's begin node.schedule - handle of new schedule to insert within this onewith_phase - specify to add the schedule in parallel with this phase nodeafter_phase - specify to add the schedule as successor to this phase nodebefore_phase - specify to add the schedule as predecessor to this phase nodeBuild up a schedule structure inserting phase by phase, specifying linkage Phases can be added anywhere, in series or parallel with existing nodesphase handle of singleton derived imp containing actual functor.by default the new phase is appended to the schedulewith_phase specify to add the new phase in parallel with this oneafter_phase specify to add the new phase as successor to this onebefore_phase specify to add the new phase as predecessor to this one CHANGE SET #5: Add ‘hier’ arg with default value=0 touvm_phase::get_schedule()LOCATION: distrib/src/base/uvm_phases.svhPDF LOCATION: page 58Returns the topmost parent schedule node, if any, for hierarchical graph traversal CHANGE SET #6: Add ‘hier’ arg with default value=0 touvm_phase::get_schedule_name() plus additional changes LOCATION: distrib/src/base/uvm_phases.svhPDF LOCATION: page 58Returns the schedule name associated with this phase nodeAccessor to return the schedule name associated with this scheduleCHANGE SET #7: Add the following methods in uvm_phases:-find_by_name()-get_full_name()-get_domain()-get_imp()-get_domain_name()LOCATION: distrib/src/base/uvm_phases.svhPDF LOCATION: N/ALocate a phase node with the specified name and return its handle. With stay_in_scope set, searches only within this phase‟s schedule or domain.Returns the full path from the enclosing domain down to this node. The singleton IMP phases have no hierarchy.Returns the enclosing domainReturns the phase implementation for this this node. Returns null if this phase type is not a UVM_PHASE_LEAF_NODE.Returns the domain name associated with this phase nodeCHANGE SET #8: Add to sync and unsync relationship to uvm_phase before the description of the sync function. Change sync and unsync API’s:LOCATION: distrib/src/base/uvm_phases.svhPDF LOCATION: page 59Add soft sync relationships between nodesSummary of usageComponents in different schedule domains can be phased independently or in sync with each other. An API is provided to specify synchronization rules between any two domains. Synchronization can be done at any of three levels:∙the domain‟s whole phase schedule can be synchronized∙ a phase can be specified, to sync that phase with a matching counterpart∙or a more detailed arbitrary synchronization between any two phasesEach kind of synchronization causes the same underlying data structures to be managed. Like other APIs, we use the parameter dot-notation to set optional parameters.When a domain is synced with another domain, all of the matching phases in the two domains get a …with‟ relationship between them. Likewise, if a domain is unsynched, all of the matching phases that have a …with‟ relationship have the dependency removed. It is possible to sync two domains and then just remove a single phase from the dependency relationship by unsyncing just the one phase.Synchonize two domains, fully or partiallytarget handle of target domain to synchronize this one tophase optional single phase in this domain to synchronize, otherwise sync allwith_phase optional different target-domain phase to synchronize with, otherwiseuse phase in the target domainfunction void unsync( u vm_domain t arget,uvm_phase phase = n ull,uvm_phase with_phase = n ull ) Remove synchronization between two domains, fully or partiallytarget handle of target domain to remove synchronization fromphase optional single phase in this domain to un-synchronize, otherwiseunsync allwith_phase optional different target-domain phase to un-synchronize with,otherwise use phase in the target domainCHANGE SET #9: Add to uvm_domain.BCL LOCATION: distrib/src/base/uvm_phases.svhPDF LOCATION: page 61Phasing schedule node representing an independent branch of the schedule. Handle used to assign domains to components or hierarchies in the testbenchSummaryGet the “common” domain, which consists of the common phases that all components execute in sync with each other. Phases in the “common” domain are build, connect, end_of_elaboration, start_of_simulation, run, extract, check, report, and final. Get the common domain objection which consists of the common phases that all components executed together (build, connect, ..., report, final).Create a new instance of a phase domain.TLM:CHANGE SET #11: Change uvm_pair as follows:BCL LOCATION: distrib/src/comps/uvm_pair.svhPDF LOCATION: page 347This section defines container classes for handling value pairs.Contentsuvm_pair classes This section defines container classes for handling value pairs.uvm_class_pair uvm_pair #(T1,T2) Container holding handles to two objects whose types are specified by the type parameters, T1 and T2.uvm_built_in_pair #(T1,T2)Container holding two variables of built-in types (int, string, etc.)Container holding handles to two objects whose types are specified by the type parameters, T1 and T2.Summaryuvm_class_pair uvm_pair #(T1,T2)Container holding handles to two objects whose types are specified by the type parameters, T1 andT2.Class HierarchyClass Declarationclass uvm_class_pair #(t ype T1 = i nt,T2 = T1) extends uvm_objectVariablesT1 first The handle to the first object in the pairT2 second The handle to the second object second variable in the pairMethodsnew Creates an instance that holds a handle to two objects of uvm_pair that holds two built-in type values.The handle to the first object in the pairThe handle to the second object second variable in the pairCreates an instance that holds a handle to two objects of uvm_pair that holds two built-in type values. The optional name argument gives a name to the new pair object.Container holding two variables of built-in types (int, string, etc.). The types are specified by the type parameters, T1 and T2.Summaryuvm_built_in_pair #(T1,T2)Container holding two variables of built-in types (int, string, etc.)Class Hierarchyuvm_voiduvm_objectuvm_transactionuvm_built_in_pair#(T1,T2)Class DeclarationVariablesT1 first The first value in the pairT2 second The second value in the pairMethodsnew Creates an instance that holds two built-in type values of uvm_pair that holds a handle to two elements, as provided by the first two arguments.The first value in the pairThe second value in the pairCreates an instance that holds two built-in type values of uvm_pair that holds two built-in type values. The optional name argument gives a name to the new pair object.CHANGE SET #12: Change uvm_tlm_generic_payload as follows.BCL LOCATION: distrib/src/tlm2/tlm2_generic_payload.svhPDF LOCATION: page 243, 244The elements in the byte enable array shall be interpreted as follows. A value of 8‟h000 shall indicate that that corresponding byte is disabled, and a value of 8‟hFF1 shall indicate that the corresponding byte is enabled.(…)If the byte enable pointer is not empty is non-null, the target shall either implement the semantics of the byte enable as defined below or shall generate a standard error response. The recommended response status is UVM_TLM_BYTE_ENABLE_ERROR_RESPONSE. CHANGE SET #13: Change uvm_component as follows.BCL LOCATION: distrib/src/base/uvm_component.svhPDF LOCATION: starting on page 289Phasing Interface These methods implement an interface which allows all components tostep through a standard schedule of phases, or a customized schedule,and also an API to allow independent phase domains which can jump likestate machines to reflect behavior e.g.build_phase The Pre-Defined Phases::uvm_build_ph ase phase implementationmethod.connect_phase The Pre-Defined Phases::uvm_connect_ph ase phase implementationmethod.end_of_elaboration_phase The Pre-Defined Phases::uvm_end_of_elaboration_ph ase phaseimplementation method.start_of_simulation_phase The Pre-Defined Phases::uvm_start_of_simulation_ph ase phaseimplementation method.run_phase The Pre-Defined Phases::uvm_run_ph ase phase implementation method. pre_reset_phase The Pre-Defined Phases::uvm_pre_reset_ph ase phase implementationmethod.reset_phase The Pre-Defined Phases::uvm_reset_ph ase phase implementationmethod.post_reset_phase The Pre-Defined Phases::uvm_post_reset_ph ase phase implementationmethod.pre_configure_phase The Pre-Defined Phases::uvm_pre_configure_ph ase phaseimplementation method.configure_phase The Pre-Defined Phases::uvm_configure_ph ase phase implementationmethod.post_configure_phase The Pre-Defined Phases::uvm_post_configure_ph ase phaseimplementation method.pre_main_phase The Pre-Defined Phases::uvm_pre_main_ph ase phase implementationmethod.main_phase The Pre-Defined Phases::uvm_main_ph ase phase implementationmethod.post_main_phase The Pre-Defined Phases::uvm_post_main_ph ase phase implementationmethod.pre_shutdown_phase The Pre-Defined Phases::uvm_pre_shutdown_ph ase phaseimplementation method.shutdown_phase The Pre-Defined Phases::uvm_shutdown_ph ase phase implementationmethod.post_shutdown_phase The Pre-Defined Phases::uvm_post_shutdown_ph ase phaseimplementation method.extract_phase The Pre-Defined Phases::uvm_extract_ph ase phase implementationmethod.check_phase The Pre-Defined Phases::uvm_check_ph ase phase implementationmethod.report_phase The Pre-Defined Phases::uvm_report_ph ase phase implementationmethod.final_phase The Pre-Defined Phases::uvm_final_ph ase phase implementationmethod.phase_started Invoked at the start of each phase.phase_ended Invoked at the end of each phase.(…)The Pre-Defined Phases::uvm_build_ph ase phase implementation method.(…)The Pre-Defined Phases::uvm_connect_ph ase phase implementation method.(…)The Pre-Defined Phases::uvm_end_of_elaboration_ph ase phase implementation method. (…)The Pre-Defined Phases::uvm_start_of_simulation_ph ase phase implementation method. (…)The Pre-Defined Phases::uvm_run_ph ase phase implementation method.(…)The Pre-Defined Phases::uvm_pre_reset_ph ase phase implementation method.(…)The Pre-Defined Phases::uvm_reset_ph ase phase implementation method.(…)The Pre-Defined Phases::uvm_post_reset_ph ase phase implementation method. (…)The Pre-Defined Phases::uvm_pre_configure_ph ase phase implementation method. (…)The Pre-Defined Phases::uvm_configure_ph ase phase implementation method. (…)The Pre-Defined Phases::uvm_post_configure_ph ase phase implementation method. (…)The Pre-Defined Phases::uvm_pre_main_ph ase phase implementation method. (…)The Pre-Defined Phases::uvm_main_ph ase phase implementation method.(…)The Pre-Defined Phases::uvm_post_main_ph ase phase implementation method. (…)The Pre-Defined Phases::uvm_pre_shutdown_ph ase phase implementation method. (…)The Pre-Defined Phases::uvm_shutdown_ph ase phase implementation method. (…)The Pre-Defined Phases::uvm_post_shutdown_ph ase phase implementation method. (…)The Pre-Defined Phases::uvm_extract_ph ase phase implementation method.(…)The Pre-Defined Phases::uvm_check_ph ase phase implementation method.(…)The Pre-Defined Phases::uvm_report_ph ase phase implementation method.(…)The Pre-Defined Phases::uvm_final_ph ase phase implementation method.Components:CHANGE SET #14: Change uvm_component::set_domain()BCL LOCATION: distrib/src/base/uvm_component.svhPDF LOCATION: page 301Apply a phase domain to this component and, if hier is set, recursively to all its children(by default, also to it's children).Calls the virtual define_domain method, which derived components can override to augment or replace the domain definition of ita base class.Get a copy of the schedule graph for this component base class as defined by virtualdefine_phase_schedule(), and add an instance of that to our domain branch in the master phasing schedule graph, if it does not already exist.CHANGE SET #15: Delete uvm_component::get_schedule()BCL LOCATION: distrib/src/base/uvm_component.svhPDF LOCATION: page 301Return handle to the phase schedule graph that applies to this componentCHANGE SET #16: Replace uvm_component::define_phase_schedule() withdefine_domain()BCL LOCATION: distrib/src/base/uvm_component.svhPDF LOCATION: page 301Builds custom phase schedules into the provided domain handle.This method is called by set_domain, which integrators use to specify this component belongs in a domain apart from the default …uvm‟ domain.Custom component base classes requiring a custom phasing schedule can augment or replace the domain definition they inherit by overriding <defined_domain>. To augment, overrides would call super.define_domain(). To replace, overrides would not callsuper.define_domain().The default implementation adds a copy of the uvm phasing schedule to the given domain, if one doesn‟t already exist, and only if the domain is currently empty.Calling set_domain with the default uvm domain (see <uvm_domain::get_uvm_domain>) on a component with no define_domain override effectively reverts the that component to using the default uvm domain. This may be usefulIf a branch of the testbench hierarchy defines a custom domain, but some child sub-branch should remain in the default uvm domain, call set_domain with a new domain instance handle with hier set. Then, in the sub-branch, call set_domain with the default uvm domain handle, obtained via uvm_domain::get_uvm_domain().Alternatively, the integrator may define the graph in a new domain externally, then callset_domain to apply it to a component.Builds and returns the required phase schedule subgraph for this component baseHere we define the structure and organization of a schedule for this component basetype (uvm_component). We give that schedule a name (default …uvm‟) and return ahandle to it to the caller (either the set_domain() method, or a subclass‟sdefine_phase_schedule() having called super.define_phase_schedule(), ready to be added into the main schedule graph.Custom component base classes requiring a custom phasing schedule to augment or replace the default UVM schedule can override this method. They can inherit the parent schedule and build on it by calling super.define_phase_schedule(MYNAME) or they can create a new schedule from scratch by not calling the super method.CHANGE SET #17: Change uvm_component::stop() to stop_phase() as follows: BCL LOCATION: distrib/src/base/uvm_component.svhPDF LOCATION: page 303The stop_phase task is called when this component‟s enable_stop_interrupt bit is set and<global_stop_request> is called during a task-based phase, e.g., run.Before a phase is abruptly ended, e.g., when a test deems the simulation complete, some components may need extra time to shut down cleanly. Such components may implement stop_phase to finish the currently executing transaction, flush the queue, or perform other cleanup. Upon return from stop_phase, a component signals it is ready to be stopped.The stop_phase method will not be called if enable_stop_interrupt is 0.The default implementation is empty, i.e., it will return immediately.This method should never be called directly.CHANGE SET #18: Add new method uvm_component::phase_ready_to_end() after phase_started() and before phase_ended().BCL LOCATION: distrib/src/base/uvm_component.svhPDF LOCATION: page 300Invoked when all objections to ending the given phase have been dropped, thus indicating that phase is ready to end. All this component‟s processes forked for the given phase will be killed upon return from this method. Components needing to consume delta cycles or advance time to perform a clean exit from the phase may raise the phase‟s objection.This effectively resets the wait-for-all-objections-dropped loop for phase. It is the responsibility of this component to drop the objection once it is ready for this phase to end (and processes killed).Macros:CHANGE SET #19: Remove macros related to new uvm_sequence_library class, which are not yet part of the approved standard.BCL LOCATION: distrib/macros/uvm_sequence_defines.svhPDF LOCATION: page 378SEQUENCE LIBRARY`uvm_add_to_sequence_library Adds the given sequence TYPE to the givensequence library LIBTYPE`uvm_sequence_library_utils Declares the infrastructure needed to define extensionsto the <uvm_sequence_library> class.Globals:CHANGE SET #20: Replace Enumerates for uvm_phase_type in GLOBALS:BCL LOCATION: distrib/src/base/uvm_object_globals.svhPDF LOCATION: page 603This is an attribute of a uvm_phase object which defines the phase type.UVM_PHASE_IMP The phase object is used to traverse the componenthierarchy and call the component phase method as well asthe phase_started and phase_ended callbacks. Thesenodes are created by the phase macros,`uvm_builtin_task_phase, `uvm_builtin_topdown_phase,and `uvm_builtin_bottomup_phase. These nodesrepresent the phase type, i.e. uvm_run_phase,uvm_main_phase.UVM_PHASE_NODE The object represents a simple node instance in the graph.These nodes will contain a reference to their correspondingIMP object.UVM_PHASE_SCHEDULE The object represents a portion of the phasing graph,typically consisting of several NODE types, in series,parallel, or both.UVM_PHASE_TERMINAL This internal object serves as the termination NODE for aSCHEDULE phase object.UVM_PHASE_DOMAIN This object represents an entire graph segment thatexecutes in parallel with the …run‟ phase. Domains maydefine any network of NODEs and SCHEDULEs. The built-indomain, uvm, consists of a single schedule of all the run-time phases, starting with pre_reset and ending withpost_shutdown.Every phase we define has a type. It is used only for information, as the type behavioris captured in three derived classes uvm_task/topdown/bottomup_phase.UVM_PHASE_TASK - The phase is a task-based phase, a fork is done foreach participating component and so the traversal order is arbitraryUVM_PHASE_TOPDOWN - The phase is a function phase, components aretraversed from top-down, allowing them to add to the component treeas they go.UVM_PHASE_BOTTOMUP - The phase is a function phase, components aretraversed from the bottom up, allowing roll-up / consolidationfunctionality.UVM_PHASE_SCHEDULE_NODE - The phase is not an imp, but a dummy phasegraph node representing the beginning of a VIP schedule of phases.UVM_PHASE_ENDSCHEDULE_NODE - The phase is not an imp, but a dummyphase graph node representing the end of a VIP schedule of phasesUVM_PHASE_DOMAIN_NODE - The phase is not an imp, but a dummy phasegraph node representing an entire domain branch with schedules beneath。