两级放大电路的设计(参考版)

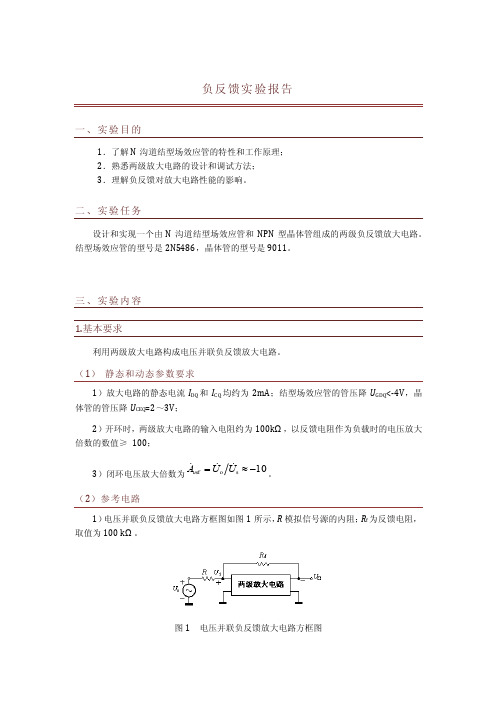

负反馈放大电路实验报告

(4)提高要求

usf

Rif

Rof

9.46

526.5Ω

3.43kΩ

与仿真数据比较:

usf =

if =

10.2 − 9.46

× 100% = 7.25%

10.2

526.5 − 310.13

3.58 − 3.43

× 100% = 41.10% ; =

× 100% = 4.19%

× 100% = 39.86%

854.1

393.1

误差分析:闭环时的电压放大倍数的误差相对较小,而输入输出电阻则与仿真值误差较大,

这主要是由于电压幅值较小,导致在测量输入输出电阻(尤其是输出电阻)时,两次测量的

电压(对于输入电阻指串入输入回路电阻两端的电压;对于输出电阻指带负载和不带负载时

的输出电压)的幅值变化很小,导致读数时的误差对结果影响较大。

526.5

3.58

误差分析:提高要求中闭环放大倍数、输出电阻与仿真值误差比较小,而输入电阻一项的误

差较大,其可能原因一方面与上面分析输入电阻误差的原因一致,另外可能与示波器显示波

形相对不稳定导致读数偏差增大有关。

七、分析与总结

由以上数据对比和误差分析可知:

此次试验数据与仿真数据的误差整体较小。这一方面是由于调整了仿真时晶体管的β 值,

3.

6

图 3 电流并联负反馈放大电路

四、仿真数据

基本要求:(原电路)

(1) 静态工作点的调试第一级:I DQ=1.99mA,

UGDQ=-9V.

UGSQ=-2.38V,

第二级:I CQ=2.03mA,

UA= 2.43 V,

US= 4.81 V,

UCEQ=2.303V

音频小信号前置放大电路

音频小信号前置放大电路1 选题背景在现在的时代我们的身边有着各种各样对于声音放大的需求,如麦克风,及一些音像设备中是最常见的,随着人们生活质量的提高对于音质的要求也越来越高,简单的音质已经无法满足大家的需求,恶劣的音质也对人们的日常生活有很大的影响,就如同噪音一样,在对音质进行调整中,对其放大是很重要的内容,音频放大电路就是在保持原声的基础上对声音进行放大,对声音中小信号的放大在音频放大电路中也有着很重要的应用,对小信号的放大可以让我们更好的获得对较弱的原声的放大,对较弱的音频进行放大后可以更好的去分析这个音频信号,对于科学研究和电子产品的开发很有帮助,也可以充分的满足人们的需求。

1.1指导思想“放大”的本质是实现能量的控制,即能量的转换:用能量比较小的输入信号来控制另一个能源,使输出端的负载上得到能量比较大的信号。

放大的对象是变化量,放大的前提是传输不失真。

通过NE5532对小信号进行放大,对相应的电阻进行合理的选择以达到对放大倍数的要求,对输出部分串电阻来达到对输出电阻的要求。

1.2 方案论证方案一:采用NE5532两级电路放大方法,用运算放大器作音频前置放大电路。

其优点是体积小、噪音低、功耗小、一致性较好。

利用运算放大器可取得很深的负反馈,同时提高不失真输出,使信号失真度在1%以下。

方案二:采用NE5532一级放大方法,优点是所用资源少,更加的简便,缺点是不稳定,电流过大,故予以否定综合考虑,采用方案一1.3 基本设计任务设计并制作音频小信号前置放大电路。

具体要求如下:≥1000;(40分)(1)放大倍数AV(2)通频带20Hz~20KHz;(40分)≥1MΩ;输出电阻R O=600Ω;(10分)(3)放大电路的输入电阻RI说明:设计方案和器件根据题目要求自行选择,但要求在通用器件范围内。

测试条件:技术指标在输入正弦波信号峰值Vpp=10mv的条件进行测试(输入输出电阻通过设计方案预以保证),设计报告中应有含有详细的测试数据说明设计结果。

2.4G+1W+双向智能功率放大器参考资料

2.4G 1W 双向智能功率放大器参考资料(带图片)“务必(双向放大),否则没意义”参考资料1:在两个或多个网络互连时,无线局域网的低功率与高频率限制了其覆盖范围,为了扩大覆盖范围,可以引入蜂窝或者微蜂窝的网络结构或者通过增大发射功率扩大覆盖半径等措施来实现。

前者实现成本较高,而后者则相对较便宜,且容易实现。

现有的产品基本上通信距离都比较小,而且实现双向收发的比较少。

本文主要研究的是距离扩展射频前端的方案与硬件的实现,通过增大发射信号功率、放大接收信号提高灵敏度以及选择增益较大的天线来实现,同时实现了双向收发,最终成果可以直接应用于与IEEE802.11b/g兼容的无线通信系统中。

双向功率放大器的设计双向功率放大器设计指标:工作频率:2400MHz~2483MHz最大输出功率:+30dBm(1W)发射增益:≥27dB接收增益:≥14dB接收端噪声系数:< 3.5dB频率响应:<±1dB输入端最小输入功率门限:<?15dB m具有收发指示功能具有电源极性反接保护功能根据时分双工TDD的工作原理,收发是分开进行的,因此可以得出采用图1的功放整体框图。

功率检波器信号输入端接在RF信号输入通道上的定向耦合器上。

当无线收发器处在发射状态时,功率检波器检测到无线收发器发出的信号,产生开关切换信号控制RF开关打向发射PA通路,LNA电路被断开,双向功率放大器处在发射状态。

当无线收发器处在接收状态时,功率检波器由于定向耦合器的单方向性而基本没有输入信号,这时通过开关切换信号将RF开关切换到LNA通路,PA通路断开,此时双向功率放大器处在接收状态。

下面介绍重点部位的设计:发射功率放大(PA)电路发射功率放大电路的作用是将无线收发器输入功率放大以达到期望输出功率。

此处选择单片微波集成电路(MMIC)作为功率放大器件,并采用两级级联的方式来同时达到最大输出功率与增益的要求。

前级功率放大芯片选择RFMD公司的RF5189,该芯片主要应用在IEEE802.11b WLAN、2.4GHz ISM频段商用及消费类电子、无线局域网系统、扩频与MMDS系统等等。

两级放大电路增加频率范围的方法

增加频率范围的方法可以通过两级放大电路来实现。

以下是一种常见的方法:

1. 使用高增益的放大器:选择具有高增益的放大器作为两级放大电路的核心。

高增益的放大器可以增强输入信号的幅度,从而扩大频率范围。

2. 使用带宽较宽的放大器:选择具有较宽带宽的放大器,可以使信号在更广泛的频率范围内保持较高的增益。

这样可以确保信号在整个频率范围内都能得到放大。

3. 使用负反馈:在两级放大电路中引入负反馈可以提高频率响应。

负反馈可以抑制非线性失真和频率响应的不均匀性,从而使放大电路在更广泛的频率范围内保持较好的性能。

4. 使用合适的耦合电容:在两级放大电路中,合适的耦合电容可以确保信号在不同级之间传递时频率响应的平坦性。

选择合适的耦合电容可以避免信号在频率范围内的衰减或失真。

5. 优化电路设计:通过优化电路的布局和元件选择,可以减少电路中的不良影响,提高频率响应。

例如,减少电路中的电容和电感的影响,选择高速的元件等。

需要注意的是,增加频率范围并不意味着放大电路可以放大所有频率的信号。

放大电路的频率范围仍然受到放大器本身的特性和元件的限制。

因此,在设计和选择放大电路时,需要根据具体应用需求和信号频率范围进行合理的选择和优化。

1。

学位论文—模拟电子技术报告--两级阻容耦合放大电路的设计与调试

模拟电子技术课程设计报告题目:两级阻容耦合放大电路的设计与调试学院电气工程学院专业班级12级电气3班学生姓名指导教师同组组员提交日期 2014年03月 07日电气工程学院专业课程设计评阅表学生姓名学生学号201230088063同组队员专业班级12电气3班题目名称两级阻容耦合放大电路的设计与调试一、学生自我总结二、指导教师评定目录目录一、设计目的 (5)二、设计要求和设计指标 (5)三、设计内容 (5)3.1.内容简介 (5)3.2.电路原理 (6)3.3参数确定 (7)3.4具体仿真电路 (7)3.5仿真结果与分析 (8)3.5.1设计要求 (8)3.5.2.技术指标 (8)3.5.3功能仿真及仿真图 (8)3.5.4. 测试电压 (9)3.5.5.频率失真图 (9)3.5.6.输出波形图 (10)3.5.7频响特性 (10)四、本设计改进建议 (4)五、总结(感想和心得等 (11)六、主要参考文献 (11)附录 (12)一、设计目的1.能够较全面地巩固和应用“模拟电子技术”课程中所学的基本理论和基本方法,并初步掌握电路设计的全过程(设计-仿真-PCB板制作-调试安装)。

2.能合理、灵活地应用分立元件或标准集成电路芯片实现规定的电路。

3. 培养独立思考、独立准备资料、独立设计规定功能的模拟电子系统的能力。

4.培养独立设计能力,熟悉EAD工具的使用,比如EWB(现在为Multisim系列)(仿真分析)及Protel(原理图和PCB版图的制作)等。

5.培养书写综合设计实验报告的能力。

二、设计要求和设计指标1.设计要求:1.根据性能指标要求,确定电路及器件型号,计算电路组件参数;2.在EWB中进行电路仿真,测量与调整电路参数,是满足设计计算要求。

3.测试性能指标,调整修改组件参数值,使其满足电路性能指标要求,将修改后的组件参数值标在设计原理图上。

4.上述各项完成后,在Protel软件中绘制电路原理图及其PCB版图。

实验报告多级放大电路

实验报告多级放大电路引言多级放大电路是电子工程学中非常常见且重要的实验之一。

在本次实验中,我们将设计和搭建一个多级放大电路,然后测试并分析其性能。

多级放大电路在信号处理、音频放大等领域具有广泛的应用。

实验目的1. 学习多级放大电路的基本工作原理。

2. 设计和搭建一个多级放大电路,并测试其信号放大性能。

实验原理多级放大电路是由多个级联的放大器构成的,每个放大器被称为一个放大级。

每个放大级的输出作为下一个放大级的输入,因此输出信号将会经过多次放大。

多级放大电路的基本工作原理如下:1. 输入信号经过第一级放大器放大,得到一级放大信号。

2. 一级放大信号作为输入信号,经过第二级放大器放大,得到二级放大信号。

3. 二级放大信号作为输入信号,经过第三级放大器放大,得到三级放大信号,以此类推。

4. 最后一级的输出信号即为多级放大电路的输出信号。

多级放大电路通常由两种类型的放大器组成:电压放大器和功率放大器。

电压放大器用于放大输入信号的电压大小,而功率放大器用于放大信号的功率。

实验步骤与结果1. 根据实验要求,设计和搭建一个三级放大电路,其中第一级为电压放大器,后两级为功率放大器。

2. 连接实验电路,并检查电路连接是否正确。

3. 输入一个信号,测试多级放大电路的输出信号大小。

4. 使用示波器监测电路的频率、相位等性能指标,并进行记录。

5. 分析实验结果,并与理论计算进行比较。

实验结果显示,多级放大电路能够将输入信号的电压和功率进行相应的放大。

输出信号的大小与输入信号的幅度差异很大,从而实现了对信号的放大处理。

同时,电路的频率和相位表现良好,没有明显的失真或偏移现象。

实验分析与讨论1. 多级放大电路的放大倍数会随着级数的增加而增加,从而达到更大的信号放大效果。

2. 电路中的放大器应具有足够的带宽,以确保输入信号的频率范围能够得到充分的放大。

3. 多级放大电路中放大器的稳定性对于整个电路的性能至关重要,应注意稳定性分析与设计。

实验三 两级运放原理图设计及仿真

输出摆幅≥ ±1V;

失调≤ ±10mV; 噪声≤ 200(1kHz时);

参考电路1:

VDD M3 x iref vin1 M1 Vn Id5 M8 3 M5 M2 vin2 CL M7 y M4 M6

?唐长文菅洪彦通信系统混合信号vlsi设计全差分运算放大器设计课程设计报告设计全差分运算放大器设计课程设计报告

实验三 两级CMOS运放的原理图设计及仿真

实验目的:

掌握采用cadence实现模拟IC原理图设计的方法; 掌握集成运算放大器设计的参数估算方法; 掌握集成运算放大器主要参数的仿真方法;

实验报告: 描述设计仿真过程;

描述参数估算过程; 描述性能参数仿真过程及结果,并进行分析;

• 设计指标要求:

开环增益≥60dB; 单位增益带宽≥50MHz; 摆率(Slew Rate)≥ 5V/us; 相位裕度≥50 ICMR ≥ ±0.8V; CMRR ≥50dB; PSRR ≥50dB;

实验内容 采用传统的集成运放设计参数估算方法设 计运放; 完成原理图设计并仿真验证;

实验步骤:

根据设计指标,选择电路结构; 根据设计指标及电路结构,估算电路参数; 采用cadence进行电路参数仿真; DC仿真,检查电路工作状态; AC仿真考察幅频特性、相频特性等; 瞬态仿真,观察输入输出波形; 调整电路参数。 引入相位补偿网络,提高电路的稳定性; 设计优化。

• 参考过程:

(1)选取电路结构; (2)确定工作点:由功耗、增益等要求选取各支路的工作电流; 如参考电路2:

g m 2 Cox (W / L ) I DS / 2 1 1 ro go I DS

运算放大器应用电路的设计与制作

运算放大器应用电路的设计与制作(一) 运算放大器 1.原理运算放大器是目前应用最广泛的一种器件,当外部接入不同的线性或非线性元器件组成输入和负反响电路时,可以灵敏地实现各种特定的函数关系。

在线性应用方面,可组成比例、加法、减法、积分、微分、对数等模拟运算电路。

运算放大器一般由4个局部组成,偏置电路,输入级,中间级,输出级。

图1运算放大器的特性曲线 图2运算放大器输入输出端图示图1是运算放大器的特性曲线,一般用到的只是曲线中的线性局部。

如图2所示。

U -对应的端子为“-〞,当输入U -单独加于该端子时,输出电压与输入电压U -反相,故称它为反相输入端。

U +对应的端子为“+〞,当输入U +单独由该端参加时,输出电压与U +同相,故称它为同相输入端。

输出:U 0= A(U +-U -) ; A 称为运算放大器的开环增益〔开环电压放大倍数〕。

在实际运用经常将运放理想化,这是由于一般说来,运放的输入电阻很大,开环增益也很大,输出电阻很小,可以将之视为理想化的,这样就能得到:开环电压增益A ud =∞;输入阻抗r i =∞;输出阻抗r o =0;带宽f BW =∞;失调与漂移均为零等理想化参数。

2.理想运放在线性应用时的两个重要特性输出电压U O 与输入电压之间满足关系式:U O =A ud 〔U +-U -〕,由于A ud =∞,而U O 为有限值,因此,U +-U -≈0。

即U +≈U -,称为“虚短〞。

由于r i =∞,故流进运放两个输入端的电流可视为零,即I IB =0,称为“虚断〞,这说明运放对其前级汲取电流极小。

上述两个特性是分析理想运放应用电路的根本原那么,可简化运放电路的计算。

3. 运算放大器的应用 (1)比例电路所谓的比例电路就是将输入信号按比例放大的电路,比例电路又分为反向比例电路、同相比例电路、差动比例电路。

(a) 反向比例电路反向比例电路如图3所示,输入信号参加反相输入端:图3反向比例电路电路图对于理想运放,该电路的输出电压与输入电压之间的关系为:为了减小输入级偏置电流引起的运算误差,在同相输入端应接入平衡电阻R ’=R 1 // R F 。

功率放大电路毕业设计(精华)

功率放大电路设计目录1、课程发展史第一章放大电路的性能指标1.1 放大倍数1.2 输入电阻Ri (3) 输出电阻Ro1.3 输出电阻Ro1.4 通频带1.5 失真度1.6 频率响应1.7 音调控制范围1.8 信噪比第二章功率放大电路概述2.1 功率放大电路的特点2.2 主要技术指标2.3 功率放大电路中的晶体管2.4 功率放大电路的分析方法第三章功率放大电路的组成3.1 为什么共射放大电路不宜用作功率放大电路3.2 变压器耦合功率放大电路3.3 无输出变压器的功率电路3.4 无输出电容的功率放大电路3.5 桥式推挽功率放大电路第四章互补功率放大电路4.1 OCL电路的组成及工作原理4.2 OCL电路的输出功率及效率4.3 OCL电路中晶体管的选择第五章集成功率放大电路5.1 集成功率放大电路分析5.2 集成功率放大电路的主要性能指标5.3 集成功率放大电路的应用第六章集成功率放大电路的应用6.1 放大电路的静态分析6.2 放大电路的动态图解分析6.3 三极管的低频小信号模型6.4 共射组态基本放大电路微变等效电路分析法6.5 共集组态基本放大电路6.6 共基组态基本放大电路放大电路中常见问题及答案本课题小结论心得致谢参考文献1、课程发展史模拟电子技术课程的开设近50年,每当电子科学和电子工业发展的关键时刻,教研组都在模拟电子技术课程内容体系上作重大的改革,并及时总结教学改革的经验,进行教材的更新,选用的教材均具有开创性,学科内容始终处于领先水平,在引导和推动我校电子技术教学体系和内容的改革中起着重要作用。

20世纪60年代初,童诗白主持编写了我国最早出版的电子学教材,从此结束了我国长期使用外国翻译教材的历史,将我国高等院校以大功率、整流技术为主的“工业电子学”课程内容体系,转变为以小功率、控制为主的整流-放大-振荡-脉冲的“电子技术基础”课程内容体系,完成了从工业电子学到电子技术基础的转换,课程名称也随之改变,为培养我国自动化方面的人才打下基础,20世纪70年代“文化大革命”期间,国外电子技术飞速发展,国内因政治动乱而停滞不前。

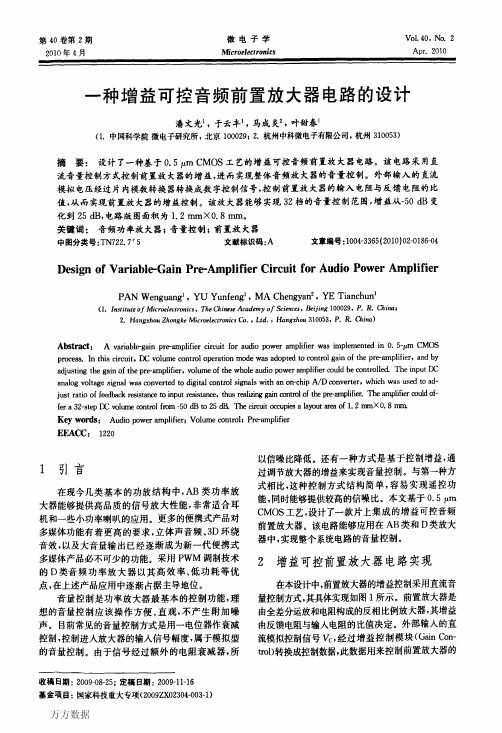

一种增益可控音频前置放大器电路的设计

图3增益控制结构 Fig.3 Structure of gain control module

外部输入的直流模拟控制信号%的电压范围

为O~‰。比较判决电路在每个时钟周期产生一

组数据,控制逻辑及可逆计数器模块根据该组数据 控制数模转换器(DAC),将相应的模拟电压反馈到 比较判决电路中,准备进行下一次比较。时序电路 为控制逻辑及可逆计数器电路提供时钟信号,由于 要适应人耳的反应时间,频率为60 Hz。 3.1 模拟控制信号输入缓冲级电路

Abstract:

A variable-gain pre-amplifier circuit for audio power amplifier was implemented in 0.5-t_£m CMOS

process.In this circuit,DC volume control operation mode was adopted to control gain of the pre-amplifier,and by

模拟输入缓冲级电路采用单位增益负反馈结构 的运放。由于外界输入信号范丽广(O~Vw),所以 运放的输入输出范围是设计的关键。设计中,采用 全摆幅的输入输出结构,以达到输入输fB的范同要 求。运放的具体结构如图4所示[2],第一级采用全 摆幅输入结构折叠共源共栅结构,提供大增益,第二 级采用共源极结构,达到最大的输出摆幅。为保持 闭环的稳定性,同样加入密勒补偿电容和调零电阻。

adjusting the gain of the pre-amplifier,volume of the whole audio power amplifier could be controlled.The input 13(3

analog voltage signal was convened to digital control signals with an on-chip A/D converter,which was used tO ad—

二级运放的米勒补偿

二级运放的米勒补偿1. 什么是二级运放?二级运放(Operational Amplifier,简称Op-Amp)是一种高增益、差分放大器。

它具有两个输入端(非反相和反相输入端)和一个输出端。

通过调节反馈电阻和输入电压,我们可以利用二级运放实现各种电路功能,如放大、滤波、比较等。

2. 米勒补偿的概念米勒补偿是一种用来提高二级运放频率响应的技术。

在某些情况下,二级运放的频率响应可能会受到内部电容的影响而产生不稳定性和失真。

为了解决这个问题,我们可以采取米勒补偿方法。

3. 米勒补偿原理米勒补偿通过引入额外的电容来抵消内部电容对频率响应的影响。

具体而言,当输入信号经过非反相输入端时,它会受到内部电容Cm1的影响。

这个内部电容会与反馈电阻Rf1形成一个低通滤波器。

为了抵消这个低通滤波器的影响,我们可以在反馈路径上引入一个额外的电容Cm2,使得它与Cm1形成一个高通滤波器。

这样,两个滤波器的效果可以相互抵消,从而提高二级运放的频率响应。

4. 米勒补偿电路示意图下面是一个典型的使用米勒补偿的二级运放电路示意图:+--------------+| || |R1 | Op-Amp |------|---■■■■■■------ RL| |Rf | |------|---+ || | Cm1 |+---┼──Rf1 || |┼ Cm2 |┼ |GND GND在这个电路中,R1和Rf分别为输入端和反馈路径上的电阻,RL为负载电阻。

Cm1和Cm2分别为内部电容和米勒补偿引入的电容。

5. 米勒补偿参数设计为了正确设计米勒补偿参数,我们需要考虑以下几个因素:•内部电容Cm1的大小:根据二级运放的规格书或数据手册可以获得该值。

•频率响应要求:根据具体应用需求确定所需频率范围。

•反馈电阻Rf1的大小:根据放大倍数和输入电阻来确定。

•补偿电容Cm2的大小:根据Cm1和Rf1来计算。

具体设计步骤如下:1.确定频率响应要求,例如希望在10Hz至100kHz范围内保持平坦响应;2.根据规格书或数据手册获得Cm1的值;3.根据放大倍数和输入电阻计算出Rf1的值;4.根据公式计算出补偿电容Cm2的值:Cm2 = Cm1 * (Rf1 / R1)。

两级放大电路的设计方案(参考版)

设计指标:A V >250,R i ≥10kΩ,R L =5.1kΩ,BW=50Hz~50kHz ,D<5% 。

设计条件:输入信号(正弦信号):2mV≤V i ≤5mV ,信号源内阻:R s =50Ω,电源电压:V CC =12V ;半导体三极管9013,参数:β=100,r bb ’=300Ω,C μ=5pF ,f T =150MHz ,3V≤V CC ≤20V ,P CM =625mW ,I CM =500mA ,V (BR)CEO =40V 。

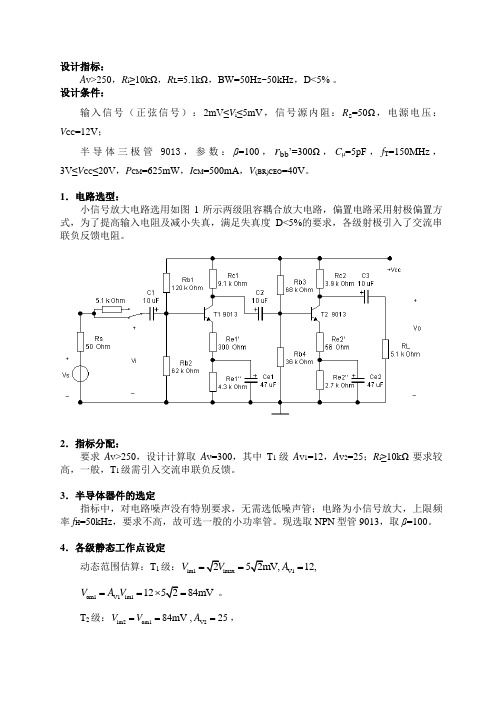

1.电路选型:小信号放大电路选用如图1所示两级阻容耦合放大电路,偏置电路采用射极偏置方式,为了提高输入电阻及减小失真,满足失真度D<5%的要求,各级射极引入了交流串联负反馈电阻。

2.指标分配:要求A V >250,设计计算取A V =300,其中T 1级A V1=12,A V2=25;R i ≥10kΩ要求较高,一般,T 1级需引入交流串联负反馈。

3.半导体器件的选定指标中,对电路噪声没有特别要求,无需选低噪声管;电路为小信号放大,上限频率f H =50kHz ,要求不高,故可选一般的小功率管。

现选取NPN 型管9013,取β=100。

4.各级静态工作点设定动态范围估算:T 1级:im1imax V112,V A ===om1V1im11284mV V A V ==⨯=。

T 2级:im2om1V284mV , 25V V A ===,om2V2im22584 2.1V V A V ==⨯=。

为避免饱和失真,应选:CEQ om CE(sat)C V V ≥+ ;可见 T 1级V CEQ1可选小些,T 2级V CEQ2可选大些。

CQ CQ CM CEQ CM T T I I I I I ≥+12取值考虑:设定主要根据,由于小信号电压放大电路较小;另从减小噪声及降低直流功率损耗出发,、工作电流应选小些。

T 1级静态工作点确定:TCQ1TCQ1T CQ1CQ1CQ1BQ1CEQ13k Ω, ',100'30026mV'100260.963mA30003000.7mA 0.07mA , V 2V>0.12VV r r r I V I r V r r I II I ββββ≥=+====-⨯≤=-====be1be1bb bb be1bb 取依可推得其中,,可求得选,T 2级静态工作点确定:一般应取CQ2CQ1I I > ,CEQ2CEQ1V V > 选 :CQ2CQ2BQ2CEQ21.2mA , 0.012mA , V 4V>3V I I I β====5.偏置电路设计计算(设BEQ 0.7V V =)T 1级偏置电路计算:Rb1BQ1BQ1CC 10100.0070.07mA 11124V33I I V V ==⨯===⨯=取故:CC BQ1b1b1124114.286k Ω0.07V V R I --=== 取标称值120kΩ 22Rb1b1b110.071200.588mW<W 8P I R ==⨯= 选b1R 120kΩ /1W 8BQ1b2Rb2Rb1BQ144463.492k Ω0.070.0070.063V R I I I =====-- 取标称值62kΩ22Rb2b2b210.063620.246mW<W 8P I R ==⨯= 选b2R 62kΩ /1W 8BQ1BEQ1BQ1BEQ1e1EQ1BQ140.7 3.3 4.67k Ω(1)1010.070.707V V V V R I I β---====≈+⨯22Rc1'EQ1c1'10.7070.30.15mW<W 8P I R ==⨯=22Rc1''EQ2c1''10.707 4.7 2.15mW<W 8P I R ==⨯=e1e111'/W ''/W 88R R ΩΩ选 300 选 4.3kCC CEQ1EQ1CC CEQ1BQ1BEQ1C1CQ1CQ1()12240.79.571k Ω0.7V V V V V V V R I I -------+====取标称值9.1kΩ22Rc1CQ1c110.79.1 4.46mW<W 8P I R ==⨯=选C1R 9.1kΩ /1W 8T 2级偏置电路计算:Rb3BQ3BQ2CC 10100.0120.12mA 11124V 33I I V V ==⨯===⨯=取故: CC BQ2b3Rb312466.67k Ω0.12V V R I --=== 取标称值68 kΩ 22Rb3Rb3b310.12680.979mW<W 8P I R ==⨯= 选b3R 68kΩ /1W 8BQ2BQ2b4Rb4Rb3BQ24437.04k Ω0.120.0120.108V V R I I I =====-- 取标称值36 kΩ22Rb4Rb4b410.108360.42mW<W 8P I R ==⨯= 选b4R 36kΩ /1W 8BQ2BEQ2BQ2BEQ2e2EQ2BQ2e2e2e2e2e140.7 3.32.723k Ω(1)1010.012 1.212'()'''56'' 2.7k ΩV V V V R I I R R R R R β---=====+⨯=Ω=分为交流负反馈、,取,22Rc2'EQ2c2'11.2120.0560.082mW<W 8P I R ==⨯=22Rc2''EQ2c2''11.2122.73.97mW<W 8P I R ==⨯=e2e211'/W ''/W 88R R ΩΩ选 56 选 2.7kCC CEQ2EQ2C2CQ212440.73.92k Ω1.2V V V R I ----+=== 取标称值3.9kΩ22Rc2CQ2c211.2 3.9 5.62mW<W 8P I R ==⨯=选C2R 3.9kΩ /1W 86.静态工作点的核算T 1级:b2CC BEQ1b1b2CQ1BQ1b1b2e162120.7120621000.67mA 12062//(1)101 4.612062R V V R R I I R R R βββ-⨯-++===⨯=⨯+++⨯+CQ1CEQ1CC CQ1c1e1(1)I V V I R R ββ=--+4.6 2.79V ⨯⨯⨯=0.67=12-0.679.1-101100符合设计要求。

运算放大器基本电路大全

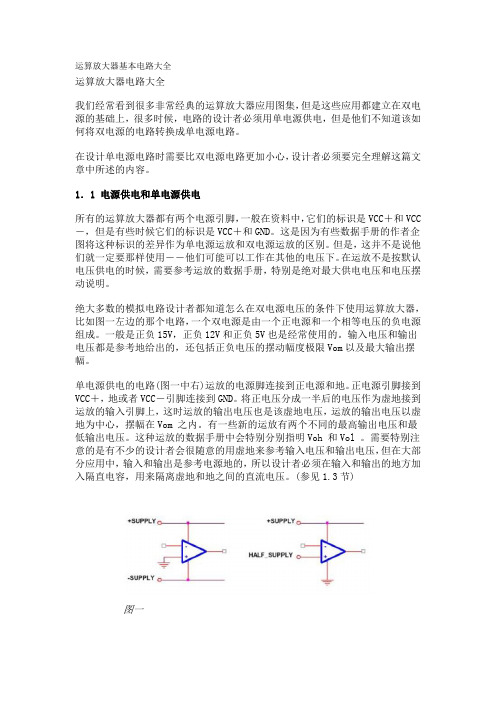

运算放大器基本电路大全运算放大器电路大全我们经常看到很多非常经典的运算放大器应用图集,但是这些应用都建立在双电源的基础上,很多时候,电路的设计者必须用单电源供电,但是他们不知道该如何将双电源的电路转换成单电源电路。

在设计单电源电路时需要比双电源电路更加小心,设计者必须要完全理解这篇文章中所述的内容。

1.1 电源供电和单电源供电所有的运算放大器都有两个电源引脚,一般在资料中,它们的标识是VCC+和VCC -,但是有些时候它们的标识是VCC+和GND。

这是因为有些数据手册的作者企图将这种标识的差异作为单电源运放和双电源运放的区别。

但是,这并不是说他们就一定要那样使用――他们可能可以工作在其他的电压下。

在运放不是按默认电压供电的时候,需要参考运放的数据手册,特别是绝对最大供电电压和电压摆动说明。

绝大多数的模拟电路设计者都知道怎么在双电源电压的条件下使用运算放大器,比如图一左边的那个电路,一个双电源是由一个正电源和一个相等电压的负电源组成。

一般是正负15V,正负12V和正负5V也是经常使用的。

输入电压和输出电压都是参考地给出的,还包括正负电压的摆动幅度极限Vom以及最大输出摆幅。

单电源供电的电路(图一中右)运放的电源脚连接到正电源和地。

正电源引脚接到VCC+,地或者VCC-引脚连接到GND。

将正电压分成一半后的电压作为虚地接到运放的输入引脚上,这时运放的输出电压也是该虚地电压,运放的输出电压以虚地为中心,摆幅在Vom 之内。

有一些新的运放有两个不同的最高输出电压和最低输出电压。

这种运放的数据手册中会特别分别指明Voh 和Vol 。

需要特别注意的是有不少的设计者会很随意的用虚地来参考输入电压和输出电压,但在大部分应用中,输入和输出是参考电源地的,所以设计者必须在输入和输出的地方加入隔直电容,用来隔离虚地和地之间的直流电压。

(参见1.3节)图一通常单电源供电的电压一般是5V,这时运放的输出电压摆幅会更低。

另外现在运放的供电电压也可以是3V 也或者会更低。

多级电压放大电路

实验项目:多级电压放大器的仿真研究一、实验目的1.进一步掌握多级放大器性能指标的分析方法。

2.掌握多级放大电路的调试及有关计算。

3.学习用Multisim软件研究放大电路的一般步骤。

二、实验仪器与设备三、实验原理与参考电路两级阻容耦合放大电路如图1所示:多级放大电路由u i 端输入信号,通过Q 1、Q 2两级放大后,从u o 端输出信号。

Q 1、Q 2构成二级基本电压放大器,晶体管工作状态通过R W1、R W2调整。

设计电路时,需要通过测量Q 1、Q 2的各极电位和Ic 电流来确定Q 1、Q 2工作在放大状态。

图1 两级阻容耦合放大电路1.直流工作点分析直流工作点分析用于确定电路的直流工作点,晶体管是否处于放大状态。

在multisim10工作界面中选择“simulate / Analysi / DC Operating Point”,设置分析类型为直流分析,放大器的直流工作点分析如图2所示。

通过晶体管各极电压值的测量确定Q1、Q2工作状态。

图2 电路各节点电压2. 动态分析(1)电压增益放大倍数的测量可以用虚拟数字示波器的A通道接输入信号电压与B通道接放大器的输出信号电压比表示,显示波形如图3所示。

图3 输入/输出波形(2)频率特性在实际电路中,通常要求放大器能够放大一定频率范围的信号。

我们把放大器的放大倍数和工作信号频率有关的特性称为幅频特性,其曲线则称为幅频频率特性曲线。

当放大倍数下降到中频的0.707倍时,低频区所对应的频点称为下限频率,用f L 表示,高频区所对应的频点称为上限频率,用f H 表示, f BW =f H -f L ,称为放大器的通频带,放大器输出信号的相移与频率的关系称为相频特性。

连接波特图仪,打开波特图仪面板,设置幅频特性参数即可测试幅频特性曲线,如4图所示。

图4 幅频特性测量(3)参数扫描分析研究耦合电容C 3参数的改变,对放大器频率特性的影响。

选择Analysis/Parameter Sweep 选项,打开参数扫描设置对话框,选择C 3输出耦合电容,从0.1uF 到100uF 按“Decade”扫描,Output node 节点选“11”,得到如图5所示的频率特性图,最下面选中的为C 3=0.1uF 曲线,其低频特性较差,最上面的为C 3=100uF 曲线,低频特性最好,但与C 3=10uF 的低频特性差别不大,所以一般耦合电容选择10uF 。

基于65-nm CMOS工艺的W波段两路电流合成型功率放大器的设计

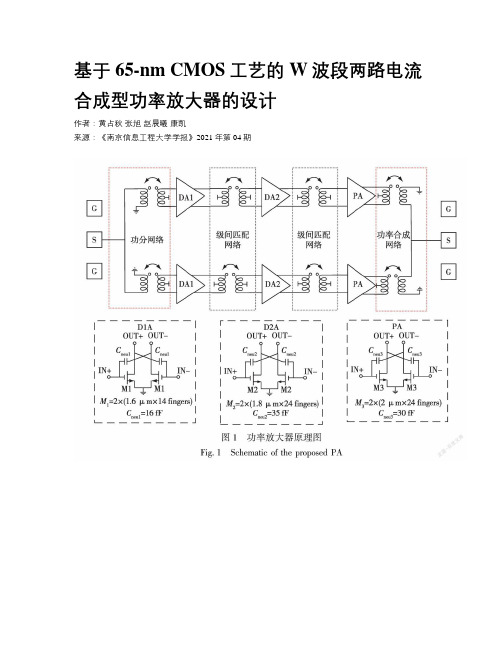

基于65-nm CMOS工艺的W波段两路电流合成型功率放大器的设计作者:黄占秋张旭赵晨曦康凯来源:《南京信息工程大学学报》2021年第04期摘要采用三級差分共源结构设计了一种基于65-nm CMOS工艺的W波段功率放大器,并利用两路电流型功率合成结构进行功率合成以提升输出功率.为了同时实现单差分转换、阻抗匹配、直流供电,匹配网络采用变压器结构.仿真结果显示,在1 V的电源电压下,该功率放大器的小信号增益为12.7~15.7 dB,3-dB带宽为84~104 GHz,饱和输出功率为14.6 dBm,峰值功率附加效率为9.7%.该功率放大器具有良好的大信号性能,且芯片的核心面积仅为0.115 mm2.关键词CMOS工艺;功率放大器;功率合成;W波段中图分类号TN43文献标志码A0 引言近年来人们对高速率无线通信的需求日益提升,频率较低的频带范围(<10 GHz)被蓝牙、Wi-Fi、4G、5G通信等应用占据,频谱资源已经消耗殆尽,而频率较高的毫米波频带范围具有充足的频谱资源,因此具有广泛的应用前景[1-2].W波段电磁波由于在大气中的衰减较小,且对云、雾、雨的穿透特性好,因此在全天候雷达系统中有着良好的应用背景[3-4].在W 波段的雷达系统中,功率放大器(Power Amplifier,PA)是一个十分关键的模块,其输出功率和效率直接决定了雷达系统的探测距离和功耗,因此设计高输出功率、高效率的功率放大器是一项十分必要的工作.通常W波段的功率放大器由基于Ⅲ-Ⅴ族的工艺实现,它具有高截止频率、高耐压的特性,因此能实现更高的增益和输出功率.但Ⅲ-Ⅴ族工艺不易与基于CMOS工艺的数字电路集成在一起,且生产成本高.CMOS工艺的优点是集成度高、成本低,而近年来它的工艺节点已经来到了深亚微米级,器件的最大振荡频率(fmax)超过200 GHz,因此非常适合毫米波相关应用,最近基于 CMOS 工艺的PA研究也越来越热门.2012年,Tsai等[5]基于65-nm CMOS工艺设计出了工作在W波段、带宽为27 GHz的PA,其饱和输出功率达到了14.8 dBm;同年,Gu等[6]采用65-nm CMOS工艺设计出了一款工作在101~107 GHz的功率放大器,饱和输出功率(Psat)为14.8 dBm,峰值功率附加效率(PAE)为9.4%;2018年,Vigilante等[7]采用28-nm CMOS工艺设计出了一款具有AM-PM失真补偿效果的超宽带PA,其小信号3-dB 带宽达到了29~57 GHz,通过调节补偿偏压,可以将工作频带内的AM-PM失真控制在1°以内,实现了很高的线性度;2019年,El-Aassar等[8]采用45-nm CMOS工艺设计了一款3-dB带宽为DC到108 GHz的超宽带分布式PA,采用堆叠式结构将PA的供电电压提升到6.6 V,最终实现了20.8 dBm的线性输出功率.为了实现高输出功率、高带宽以及高效率,本文采用65-nm CMOS工艺设计了一款工作在W波段的功率放大器,通过三级级联以提升PA的整体增益,采用两路功率合成来提升输出功率,所有匹配网络均采用变压器结构实现,以此来增大带宽及减小版图面积.仿真结果显示所设计PA的3-dB带宽达到了20 GHz(84~104 GHz),小信号增益12.7~15.7 dB,饱和输出功率14.6 dBm,峰值功率附加效率(PAE)为9.7%,电路核心面积仅为0.115 mm2.1 有源电路设计PA整体结构如图1所示,采用了两路差分功率合成的架构,通过三级基于中和电容的共源结构级联以实现高增益和稳定性.级间匹配网络和输入、输出匹配网络均采用变压器实现,大幅减小版图面积.共源级是PA常用的一种电路结构,其优点是输出端回波损耗会比较小,S22一般能做到-10 dB以下.然而由于CMOS工艺不提供背孔,因此其接地特性不好,而差分结构天然具有“虚地”特性,可以屏蔽掉芯片外围bonding线对电路性能的影响,因此CMOS功率放大器多用差分结构实现[9].图1显示所设计的PA有源电路采用差分共源结构.差分结构除了具有接地特性良好的优点外,还能将单端负载上的电压摆幅扩大为原来的两倍,从而提升输出功率[10].MOS 管的栅漏寄生电容CGD的存在会引入一个负反馈路径,降低信号从栅极到漏极的增益及隔离度,从而引起稳定性问题.Cneu为中和电容,将其交叉并接在差分MOS管的栅、漏极之间可以补偿CGD产生的负反馈效应,从而提升共源结构的增益和稳定性[11].图2为加入中和电容之后差分对的最大可用增益(Max Gain)和稳定性随电容值的变化曲线,它显示了适当容值的中和电容可以显著提升放大器的增益和稳定性,但若容值超过此区间,反而会降低稳定性.为了应对工艺、电压和温度的波动,电容容值的选取应留有足够的裕度,因此对于图2中的情况,容值选择为35 fF是一个比较好的选择,在此容值上下波动10%时放大器依然是无条件稳定的.为了获得较高的输出功率,功放级单个MOS管的总栅宽选择为96 μm,而为了减小大尺寸晶体管的寄生带来的增益恶化,往往需要将其划分为多个小尺寸晶体管的并联[12],因此这里将单个96 μm的MOS管替换为2个总栅宽为48 μm的MOS管并联,单指栅宽选择为2μm,指数为24,以此来获得单个MOS管的最佳性能.第2驱动级MOS管选择2个管子并联,每个管子有24 fingers,其单指栅宽为1.8 μm,总栅宽为2×1.8×24=86.4 μm.第1驱动级由于不需要提供高输出功率,故选择2个管子并联,每个管子有14 fingers,其单指栅宽为1.6 μm,总栅宽为2×1.6×14=44.8 μm,在节省功耗的同时提高增益.2 无源电路设计2.1 基于变压器的级间匹配网络的设计由于硅基工艺往往提供多层金属,例如65-nm CMOS工艺提供了M1~M9共9层金属用于走线,这为变压器的使用提供了便利.图3为采用M8和M9两层金属设计的一种变压器,这两层为顶层金属,具有最大的厚度和最低的电阻率,因此无源损耗较低.两层金属各自绕成一圈电感,在空间上呈垂直堆叠的状态,因此二者具有一定的电磁耦合,形成了具有一定耦合系数的变压器结构,初级线圈的能量可以通过电磁耦合传递到次级线圈.对于差分电路来说,变压器可以同时用来实现阻抗匹配和直流供電的作用[13].线圈中心抽头处是天然的虚地点,直流电压从该点馈入,不会影响变压器的性能.作为级间匹配网络使用时,初、次级线圈各自的两个端口分别与前级的差分输出端口和后级的差分输入端口相连,在阻隔直流信号的同时可以实现级间的阻抗匹配.变压器的两种简化的等效电路也显示在了图3中,L1、L2、M分别为初、次级线圈的电感量和互感量,M与耦合系数k的关系为k=ML1L2. (1)线圈的感量可以通过其尺寸大小进行相应调整,耦合系数则由初、次级线圈的空间相对位置决定.通过选取合适变压器结构和尺寸,可以得到所需的电感值和耦合系数,从而实现阻抗变换,达到阻抗匹配的效果.此外,由于变压器本身可以看作分布参数电路,初、次级线圈之间以及线圈与地之间都存在寄生电容,这些电容与线圈本身的电感形成一些高阶的LC谐振腔,因此可以实现较高的匹配带宽.2.2 基于变压器的功率分配、功率合成网络的设计由于输入输出信号都是单端信号,因此在输入和输出端口均需要巴伦进行信号的单-差分转换,将变压器次级线圈的一端接地即可实现巴伦的作用.以输入匹配网络为例,单端信号馈入输入PAD后,经传输线直接分为两路同相位的单端信号,即实现了功率分配的作用.由于功分后的两路信号是同相位的,不存在隔离度的问题,因此不需要采用威尔金森功分器结构进行功率分配.单端信号经过巴伦转换成差分信号后被MOS管放大,最后经结构相同的功率合成网络合成一路单端信号后传输到输出PAD上.图4显示了功率放大器的输出端功率合成网络的3D模型图及其等效电路.负载电阻为50 Ω,Csg为信号PAD的对地电容.末级一路PA需要的差分最佳负载阻抗Zopt为18.1+14j Ω,因此功率合成网络的作用是要将50 Ω的单端阻抗转换成末级PA所需要的差分最佳负载阻抗Zopt.变压器T1可以用其等效模型表示.A点为经过PAD看到的负载阻抗,B点为经过一段电感看到的阻抗,C点为功分后一路看到的阻抗,即为B点阻抗的两倍.D点为巴伦单端看到的阻抗,经变压器的阻抗变换后变为Zopt=18.1+14j Ω.阻抗变换的过程显示在图5所示的Smith 圆图中.3 仿真结果ANSYS HFSS进行3-D电磁仿真.电源电压采用1 V,末级PA的栅极偏压为0.7 V,驱动级的栅极偏压均为0.6 V,版图核心面积为230 μm×500 μm,总面积(包含PAD)为750 μm×560 μm,静态功耗为350 mW.图7a给出了PA的S参数后仿结果,在1 V的供电电压下,实现了84~104 GHz的3-dB 带宽,峰值增益为94.5 GHz处的15.7 dB.在90~100 GHz的频率范围内S11、S22均小于10 dB,实现了较好的匹配效果.图7b显示了PA在84、94和104 GHz处的大信号仿真结果,输出功率和效率均在94 GHz处达到了最大,Psat为14.6 dBm,OP 1-dB(输出1-dB压缩点)为11.3 dBm,峰值PAE为9.7%.为了与其他文献中的测试条件保持一致,将供电电压加大到1.2 V进行了仿真,供电电压的提升会使得MOS管漏极电压摆幅增大,从而提升输出功率和效率.仿真结果显示在94.5 GHz 处,输出功率和效率均有提升,输出1-dB压缩点上升到了12.7 dBm,Psat为16.3 dBm,对应的峰值PAE达到了10.7%.仿真结果如图8所示.与表1中其他文献对比,本文所设计的PA在输出功率、效率和芯片面积上都有一定的优势.4 结束语本文基于变压器的阻抗匹配和功率合成的思想,采用65-nm CMOS工艺设计了一种高增益、高输出功率的功率放大器.仿试验结果表明该放大器在84~104 GHz的范围内实现了大于12.7 dB的小信号增益,最大饱和输出功率达到了14.6 dBm,对应的PAE为9.7%,在增益、带宽、输出功率和效率上都表现出了良好的性能.参考文献References[1] Kang K,Lin F J,Pham D D,et al.A 60-GHz OOK receiver with an on-chip antenna in 90 nm CMOS[J].IEEE Journal of Solid-State Circuits,2010,45(9):1720-1731[2] Zhang X N,Chen D,Lu W,et al.A Ku band 4-element phased array transceiver in 180 nm CMOS[C]∥2017 IEEE MTT-S International Microwave Symposium (IMS).June 4-9,2017,Honololu,HI,USA.IEEE,2017:1595-1598[3] Tessmann A,Kudszus S,Feltgen T,et pact single-chip W-band FMCW radar modules for commercial high-resolution sensor applications[J].IEEE Transactions on Microwave Theory and Techniques,2002,50(12):2995-3001于走线,这为变压器的使用提供了便利.图3为采用M8和M9两层金属设计的一种变压器,这两层为顶层金属,具有最大的厚度和最低的电阻率,因此无源损耗较低.两层金属各自绕成一圈电感,在空间上呈垂直堆叠的状态,因此二者具有一定的电磁耦合,形成了具有一定耦合系数的变压器结构,初级线圈的能量可以通过电磁耦合传递到次级线圈.对于差分电路来说,变压器可以同时用来实现阻抗匹配和直流供电的作用[13].线圈中心抽头处是天然的虚地点,直流电压从该点馈入,不会影响变压器的性能.作为级间匹配网络使用时,初、次级线圈各自的两个端口分别与前级的差分输出端口和后级的差分输入端口相连,在阻隔直流信号的同时可以实现级间的阻抗匹配.变压器的两种简化的等效电路也显示在了图3中,L1、L2、M分别为初、次级线圈的电感量和互感量,M与耦合系数k的关系为k=ML1L2. (1)线圈的感量可以通过其尺寸大小进行相应调整,耦合系数则由初、次级线圈的空间相对位置决定.通过选取合适变压器结构和尺寸,可以得到所需的电感值和耦合系数,从而实现阻抗变换,达到阻抗匹配的效果.此外,由于变压器本身可以看作分布参数电路,初、次级线圈之间以及线圈与地之间都存在寄生电容,这些电容与线圈本身的电感形成一些高阶的LC谐振腔,因此可以实现较高的匹配带宽.2.2 基于变压器的功率分配、功率合成网络的设计由于输入输出信号都是单端信号,因此在输入和输出端口均需要巴伦进行信号的单-差分转换,将变压器次级线圈的一端接地即可实现巴伦的作用.以输入匹配网络为例,单端信号馈入输入PAD后,经传输线直接分为两路同相位的单端信号,即实现了功率分配的作用.由于功分后的两路信号是同相位的,不存在隔离度的问题,因此不需要采用威尔金森功分器结构进行功率分配.单端信号经过巴伦转换成差分信号后被MOS管放大,最后经结构相同的功率合成网络合成一路单端信号后传输到输出PAD上.图4显示了功率放大器的输出端功率合成网络的3D模型图及其等效电路.负载电阻为50 Ω,Csg为信号PAD的对地电容.末级一路PA需要的差分最佳负载阻抗Zopt为18.1+14j Ω,因此功率合成网络的作用是要将50 Ω的单端阻抗转换成末级PA所需要的差分最佳负载阻抗Zopt.变压器T1可以用其等效模型表示.A点为经过PAD看到的负载阻抗,B点为经过一段电感看到的阻抗,C点为功分后一路看到的阻抗,即为B点阻抗的两倍.D点为巴伦单端看到的阻抗,经变压器的阻抗变换后变为Zopt=18.1+14j Ω.阻抗变换的过程显示在图5所示的Smith 圆图中.3 仿真结果ANSYS HFSS进行3-D电磁仿真.电源电压采用1 V,末级PA的栅极偏压为0.7 V,驱动级的栅极偏压均为0.6 V,版图核心面积为230 μm×500 μm,总面积(包含PAD)为750 μm×560 μm,静态功耗为350 mW.图7a给出了PA的S参数后仿结果,在1 V的供电电压下,实现了84~104 GHz的3-dB 带宽,峰值增益为94.5 GHz处的15.7 dB.在90~100 GHz的频率范围内S11、S22均小于10 dB,实现了较好的匹配效果.图7b显示了PA在84、94和104 GHz处的大信号仿真结果,输出功率和效率均在94 GHz处达到了最大,Psat为14.6 dBm,OP 1-dB(输出1-dB压缩点)为11.3 dBm,峰值PAE为9.7%.为了与其他文献中的测试条件保持一致,将供电电压加大到1.2 V进行了仿真,供电电压的提升会使得MOS管漏极电压摆幅增大,从而提升输出功率和效率.仿真结果显示在94.5 GHz 处,输出功率和效率均有提升,输出1-dB压缩点上升到了12.7 dBm,Psat为16.3 dBm,对应的峰值PAE达到了10.7%.仿真结果如图8所示.与表1中其他文献对比,本文所设计的PA在输出功率、效率和芯片面积上都有一定的优势.4 结束语本文基于变压器的阻抗匹配和功率合成的思想,采用65-nm CMOS工艺设计了一种高增益、高输出功率的功率放大器.仿试验结果表明该放大器在84~104 GHz的范围内实现了大于12.7 dB的小信号增益,最大饱和输出功率达到了14.6 dBm,对应的PAE为9.7%,在增益、带宽、输出功率和效率上都表现出了良好的性能.参考文献References[1] Kang K,Lin F J,Pham D D,et al.A 60-GHz OOK receiver with an on-chip antenna in 90 nm CMOS[J].IEEE Journal of Solid-State Circuits,2010,45(9):1720-1731[2] Zhang X N,Chen D,Lu W,et al.A Ku band 4-element phased array transceiver in 180 nm CMOS[C]∥2017 IEEE MTT-S International Microwave Symposium (IMS).June 4-9,2017,Honololu,HI,USA.IEEE,2017:1595-1598[3] Tessmann A,Kudszus S,Feltgen T,et pact single-chip W-band FMCW radar modules for commercial high-resolution sensor applications[J].IEEE Transactions on Microwave Theory and Techniques,2002,50(12):2995-3001于走线,这为变压器的使用提供了便利.图3为采用M8和M9两层金属设计的一种变压器,这两层为顶层金属,具有最大的厚度和最低的电阻率,因此无源损耗较低.两层金属各自绕成一圈电感,在空间上呈垂直堆叠的状态,因此二者具有一定的电磁耦合,形成了具有一定耦合系数的变压器结构,初级线圈的能量可以通过电磁耦合传递到次级线圈.对于差分电路来说,变压器可以同时用来实现阻抗匹配和直流供电的作用[13].线圈中心抽头处是天然的虚地点,直流电压从该点馈入,不会影响变压器的性能.作为级间匹配网络使用时,初、次级线圈各自的两个端口分别与前级的差分输出端口和后级的差分输入端口相连,在阻隔直流信号的同时可以实现级间的阻抗匹配.变压器的两种简化的等效电路也显示在了图3中,L1、L2、M分别为初、次级线圈的电感量和互感量,M与耦合系数k的关系为k=ML1L2. (1)线圈的感量可以通过其尺寸大小进行相应调整,耦合系数则由初、次级线圈的空间相对位置决定.通过选取合适变压器结构和尺寸,可以得到所需的电感值和耦合系数,从而实现阻抗变换,达到阻抗匹配的效果.此外,由于变压器本身可以看作分布参数电路,初、次级线圈之间以及线圈与地之间都存在寄生电容,这些电容与线圈本身的电感形成一些高阶的LC谐振腔,因此可以实现较高的匹配带宽.2.2 基于变压器的功率分配、功率合成网络的设计由于输入输出信号都是单端信号,因此在输入和输出端口均需要巴伦进行信号的单-差分转换,将变压器次级线圈的一端接地即可实现巴伦的作用.以输入匹配网络为例,单端信号馈入输入PAD后,经传输线直接分为两路同相位的单端信号,即实现了功率分配的作用.由于功分后的两路信号是同相位的,不存在隔离度的问题,因此不需要采用威尔金森功分器结构进行功率分配.单端信号经过巴伦转换成差分信号后被MOS管放大,最后经结构相同的功率合成网络合成一路单端信号后传输到输出PAD上.图4显示了功率放大器的输出端功率合成网络的3D模型图及其等效电路.负载电阻为50 Ω,Csg为信号PAD的对地电容.末级一路PA需要的差分最佳负载阻抗Zopt为18.1+14j Ω,因此功率合成网络的作用是要将50 Ω的单端阻抗转换成末级PA所需要的差分最佳负载阻抗Zopt.变压器T1可以用其等效模型表示.A点为经过PAD看到的负载阻抗,B点为经过一段电感看到的阻抗,C点为功分后一路看到的阻抗,即为B点阻抗的两倍.D点为巴伦单端看到的阻抗,经变压器的阻抗变换后变为Zopt=18.1+14j Ω.阻抗变换的过程显示在图5所示的Smith 圆图中.3 仿真结果ANSYS HFSS进行3-D电磁仿真.电源电压采用1 V,末级PA的栅极偏压为0.7 V,驱动级的栅极偏压均为0.6 V,版图核心面积为230 μm×500 μm,总面积(包含PAD)为750 μm×560 μm,静态功耗为350 mW.图7a给出了PA的S参数后仿结果,在1 V的供电电压下,实现了84~104 GHz的3-dB 带宽,峰值增益为94.5 GHz处的15.7 dB.在90~100 GHz的频率范围内S11、S22均小于10 dB,实现了较好的匹配效果.图7b显示了PA在84、94和104 GHz处的大信号仿真结果,输出功率和效率均在94 GHz处达到了最大,Psat為14.6 dBm,OP 1-dB(输出1-dB压缩点)为11.3 dBm,峰值PAE为9.7%.为了与其他文献中的测试条件保持一致,将供电电压加大到1.2 V进行了仿真,供电电压的提升会使得MOS管漏极电压摆幅增大,从而提升输出功率和效率.仿真结果显示在94.5 GHz 处,输出功率和效率均有提升,输出1-dB压缩点上升到了12.7 dBm,Psat为16.3 dBm,对应的峰值PAE达到了10.7%.仿真结果如图8所示.与表1中其他文献对比,本文所设计的PA在输出功率、效率和芯片面积上都有一定的优势.4 结束语本文基于变压器的阻抗匹配和功率合成的思想,采用65-nm CMOS工艺设计了一种高增益、高输出功率的功率放大器.仿试验结果表明该放大器在84~104 GHz的范围内实现了大于12.7 dB的小信号增益,最大饱和输出功率达到了14.6 dBm,对应的PAE为9.7%,在增益、带宽、输出功率和效率上都表现出了良好的性能.参考文献References[1] Kang K,Lin F J,Pham D D,et al.A 60-GHz OOK receiver with an on-chip antenna in 90 nm CMOS[J].IEEE Journal of Solid-State Circuits,2010,45(9):1720-1731[2] Zhang X N,Chen D,Lu W,et al.A Ku band 4-element phased array transceiver in 180 nm CMOS[C]∥2017 IEEE MTT-S International Microwave Symposium (IMS).June 4-9,2017,Honololu,HI,USA.IEEE,2017:1595-1598[3] Tessmann A,Kudszus S,Feltgen T,et pact single-chip W-band FMCW radar modules for commercial high-resolution sensor applications[J].IEEE Transactions on Microwave Theory and Techniques,2002,50(12):2995-3001。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

设计指标:A V >250,R i ≥10kΩ,R L =5.1kΩ, BW=50Hz~50kHz ,D<5% 。

设计条件:输入信号(正弦信号):2mV≤V i ≤5mV ,信号源内阻:R s =50Ω,电源电压:V CC =12V ; 半导体三极管9013,参数:β=100,r bb ’=300Ω,C μ=5pF ,f T =150MHz ,3V≤V CC ≤20V , P CM =625mW ,I CM =500mA ,V (BR)CEO =40V 。

1.电路选型:小信号放大电路选用如图1所示两级阻容耦合放大电路,偏置电路采用射极偏置方式,为了提高输入电阻及减小失真,满足失真度D<5%的要求,各级射极引入了交流串联负反馈电阻。

2.指标分配:要求A V >250,设计计算取A V =300,其中T 1级A V1=12,A V2=25;R i ≥10kΩ要求较高,一般,T 1级需引入交流串联负反馈。

3.半导体器件的选定指标中,对电路噪声没有特别要求,无需选低噪声管;电路为小信号放大,上限频率f H =50kHz ,要求不高,故可选一般的小功率管。

现选取NPN 型管9013,取β=100。

4.各级静态工作点设定动态范围估算:T 1级:im1imax V1252mV, 12,V V A === om1V1im1125284mV V A V ==⨯=。

T 2级:im2om1V284mV , 25V V A ===, om2V2im22584 2.1V V A V ==⨯=。

为避免饱和失真,应选:CEQ om CE(sat)C V V ≥+ ;可见 T 1级V CEQ1可选小些,T 2级V CEQ2可选大些。

CQ CQ CM CEQ CM T T I I I I I ≥+12取值考虑:设定主要根据,由于小信号电压放大电路较小;另从减小噪声及降低直流功率损耗出发,、工作电流应选小些。

T 1级静态工作点确定:TCQ1TCQ1T CQ1CQ1CQ1BQ1CEQ13k Ω, ',100'30026mV'100260.963mA30003000.7mA 0.07mA , V 2V>0.12VV r r r I V I r V r r I II I ββββ≥=+====-⨯≤=-====be1be1bb bb be1bb 取依可推得其中,,可求得选,T 2级静态工作点确定:一般应取CQ2CQ1I I > ,CEQ2CEQ1V V > 选 :CQ2CQ2BQ2CEQ21.2mA , 0.012mA , V 4V>3V I I I β====5.偏置电路设计计算(设BEQ 0.7V V =)T 1级偏置电路计算:Rb1BQ1BQ1CC 10100.0070.07mA 11124V33I I V V ==⨯===⨯=取故:CC BQ1b1b1124114.286k Ω0.07V V R I --=== 取标称值120 kΩ 22Rb1b1b110.071200.588mW<W 8P I R ==⨯= 选b1R 120 kΩ /1W 8BQ1b2Rb2Rb1BQ144463.492k Ω0.070.0070.063V R I I I =====-- 取标称值62 kΩ22Rb2b2b210.063620.246mW<W 8P I R ==⨯= 选b2R 62 kΩ /1W 8BQ1BEQ1BQ1BEQ1e1EQ1BQ140.7 3.34.67k Ω(1)1010.070.707V V V V R I I β---====≈+⨯22Rc1'EQ1c1'10.7070.30.15mW<W 8P I R ==⨯=22Rc1''EQ2c1''10.707 4.7 2.15mW<W 8P I R ==⨯=e1e111'/W ''/W 88R R ΩΩ选 300 选 4.3kCC CEQ1EQ1CC CEQ1BQ1BEQ1C1CQ1CQ1()12240.79.571k Ω0.7V V V V V V V R I I -------+====取标称值9.1kΩ22Rc1CQ1c110.79.1 4.46mW<W 8P I R ==⨯= 选C1R 9.1 kΩ /1W 8T 2级偏置电路计算:Rb3BQ3BQ2CC 10100.0120.12mA 11124V 33I I V V ==⨯===⨯=取故: CC BQ2b3Rb312466.67k Ω0.12V V R I --=== 取标称值68 kΩ 22Rb3Rb3b310.12680.979mW<W 8P I R ==⨯= 选b3R 68 kΩ /1W 8BQ2BQ2b4Rb4Rb3BQ24437.04k Ω0.120.0120.108V V R I I I =====-- 取标称值36 kΩ22Rb4Rb4b410.108360.42mW<W 8P I R ==⨯= 选b4R 36 kΩ /1W 8BQ2BEQ2BQ2BEQ2e2EQ2BQ2e2e2e2e2e140.7 3.3 2.723k Ω(1)1010.012 1.212'()'''56'' 2.7k ΩV V V V R I I R R R R R β---=====+⨯=Ω=分为交流负反馈、,取,22Rc2'EQ2c2'11.2120.0560.082mW<W 8P I R ==⨯=22Rc2''EQ2c2''11.2122.73.97mW<W 8P I R ==⨯=e2e211'/W ''/W 88R R ΩΩ选 56 选 2.7kCC CEQ2EQ2C2CQ212440.73.92k Ω1.2V V V R I ----+=== 取标称值3.9kΩ22Rc2CQ2c211.2 3.9 5.62mW<W 8P I R ==⨯= 选C2R 3.9 kΩ /1W 86.静态工作点的核算T 1级:b2CC BEQ1b1b2CQ1BQ1b1b2e162120.7120621000.67mA 12062//(1)101 4.612062R V V R R I I R R R βββ-⨯-++===⨯=⨯+++⨯+CQ1CEQ1CC CQ1c1e1(1)I V V I R R ββ=--+4.6 2.79V ⨯⨯⨯=0.67=12-0.679.1-101100符合设计要求。

b3CC BEQ2b3b4CQ2BQ1b3b4e236120.76836100 1.144mA 6836//(1)101 2.7566836R V V R R I I R R R βββ-⨯-++===⨯=⨯+++⨯+CQ2CEQ2CC CQ2c2e2(1)I V V I R R ββ=--+2.756 4.354V ⨯⨯⨯=1.144=12-1.144 3.9-101100符合设计要求。

7.电容器的选择 C 1:T be bb'CQ1i1be e1'b b1b2b i1i b i1b i1S 1L S i 26300100 4.18k Ω0.67'(1) 4.181010.334.48k Ω12062'//40.88k Ω12062''40.8834.48'//'18.7k Ω''40.8834.4850Ω1(3~10)(3~2π()V r r I R r R R R R R R R R R R R R C f R R ββ=+=+⨯==++=+⨯=⨯===+⨯⨯====++=≥=+311110)2π50(0.05+18.7)10(3~10) 1.7 5.1μF~17μF 10μF 10μF/16VC C ⨯⨯⨯⨯=⨯==取选C 2:o1C1T be2bb'2CQ2i2be2e2'b b3b4i2b i22L o1i29.1k Ω26300100 2.573k Ω10144'(1) 2.5731010.0568.23k Ω6836''//23.54k Ω683623.548.23''//' 6.1k Ω2.548.231(3~10)(3~10)2π()R R V r r I R r R R R R R R R C f R R ββ===+=+⨯==++=+⨯=⨯===+⨯===+≥=⨯+32212π50(9.1+6.1)10(3~10) 1.99 5.97μF~19.9μF 10μF 10μF/16VC C ⨯⨯⨯=⨯==取选 C 3:33L e2L 3 3 11(3~10)(3~10)2π()2π50(3.9+5.1)10(3~10) 3.5410.62μF~35.4μF10μF 10μF/16VC f R R C C ≥=⨯+⨯⨯⨯=⨯==取选C e1:e13L e111(3~10)(3~10)2π''2π50 4.310(3~10)7.422.2μF~74μFC f R ≥=⨯⨯⨯⨯=⨯=取C e1=47μF 选C e1 47μF/16V C e2:e23L e211(3~10)(3~10)2π''2π50 2.710(3~10) 1.18 3.54μF~11.8μF C f R ≥=⨯⨯⨯⨯=⨯=取C e2=47μF 选C e2 47μF/16V8.指标核算R i =18..7k Ω>10k Ω 满足设计要求R L1=R i2=6.1k Ω'L1C i29.1 6.1// 3.652k 9.1 6.1R R R ⨯===Ω+'L1V1'i13.6521001134.48R A R β•=-=-⨯=-'L C2L 3.9 5.1// 2.21k 3.9 5.1R R R ⨯===Ω+'L V2'i2 2.2110026.858.23R A R β•=-=-⨯=-V V1V211(26.85)295250A A A •••=•=-⨯-=> 满足设计指标要求。

核算H f 、L f :L f :36L1S i 1'''''''S b be1S be1e1e1e1e1e1e1e13636L2C1i22e2()(0.0518.7)101010187.5ms//[()//][()//]110.342 4.310471014.89ms 0.342 4.3()(9.1 6.1)101010152ms[R R C R R r R r R R C R R C R R C ττββττ---=+=+⨯⨯⨯=++=+≈+++⨯=⨯⨯⨯=+=+=+⨯⨯⨯=='''e1b2b4be2e2e2e236363cL Lj ////()//]10.146 2.71047100.146 2.70.139104710 6.51ms 1111111()102π2π 1.152π 1.15187.514.89152 6.5132.2Hz < 50Hz R R R r R R C f βωτ--+++⨯=⨯⨯⨯+=⨯⨯⨯====+++⨯⨯⨯=∑满足设计要求H f :CQ1T CQ2T 0.6725.77ms V 261.14444msV 26I g I g ======m1m2'''310S b bb1e11312H110π1'm1L1''332010m1L1L130.65 3.88[//(1)]//10 3.444k Ω30.65 3.883.44410150100.5166μs'25.77 3.65294.112v1(1) 3.4441095.112 3.65210331.21R R R r R r R C g R R R g R R A πβτ-•⨯=+++=⨯=+==⨯⨯⨯==-=-⨯=-=++=⨯⨯+⨯=312H220μ1''''330C bbb2e22312H330π2'm2L '4030m2L28k Ω331.21810510 1.656μs12.519 2.273[//(1)]//10 1.924k Ω12.519 2.2731.92410150100.2886μs'44 2.2197.24v2(1R C R R R r R r R C g R R R g R A πτβτ--•==⨯⨯⨯=⨯=+++=⨯=+==⨯⨯⨯==-=-⨯=-=+'3L2312H240μ2HH 4Hjj=1)(1.92498.24 2.21)10191.224k Ω191.224105100.956μs1.15 1.151111()2π2π0.5166 1.6560.28860.9562π53.56kHz > 50kHz R R C f τωτ-+=⨯+⨯===⨯⨯⨯====+++=∑满足设计要求。