第三章+Nios+II体系结构+

NIOS简介

硬件平台

NIOS II 软件配置

• Quartus

– 建立项目、布局布线、分析综合、引脚配置

• SOPC Builder

– 配置处理器、外设、分配地址

• NIOS II IDE

– C头文件、编译、调试 PS:注意软件版本号要一致 :

简易开发流程

(3)

QuartusII *.sof 布局布线… 综合… 布局布线 综合

下载程序

Thank you

NIOS II 开发流程简介

zhaoliang0801@ 9/22/2008

提纲:

• • • • • • NIOS II简介 NIOS II 软件配置 硬件平台 简易开发流程 下载程序到flash 总结

NIOS II简介—What is NIOS II?

Nios II系列嵌入式处理器是Altera推出的第二代软核嵌入式处理器解决 方案。Nios II处理器内核是一个32位的RISC处理器,它具有共享的通用 指令集结构,专门针对Altera的主流FPGA系列进行了优化。 优点—— 灵活性: 根据您的应用需求,选择最合适的CPU、外设和存储器组合 高性能: 不用修改电路板设计或者增大功率预算便可以提高性能 低成本: 在单一芯片上实现多种功能,降低了系统成本和复杂度 较长的生命周期: 产品迅速面市,避免了处理器过时的风险

NIOS_ II软核处理学习资料

DSP是另外一种系统设计方法,与MCU专注于控制不同,DSP强调各种数字信号处理算法的快速实现。区别在于:

MCU采用的硬件结构是冯-诺依曼型,即在同一个存储空间取指令和数据,两者不能同时进行,因而地址总线和数据总线的宽度必须一致;DSP采用改进型哈佛结构,即指令和数据空间完全分开,并且有多个指令和数据空间,由于可以对程序和数据同时进行访问,所以提高了数据吞吐率,当然,地址总线和数据总线可以采用不同的宽度。除此之外,DSP具有专门的硬件乘法器,广泛采用流水线操作(即一条指令被执行时,允许下一条指令同时被取出),这些特性大大提高了DSP处理数据的能力。

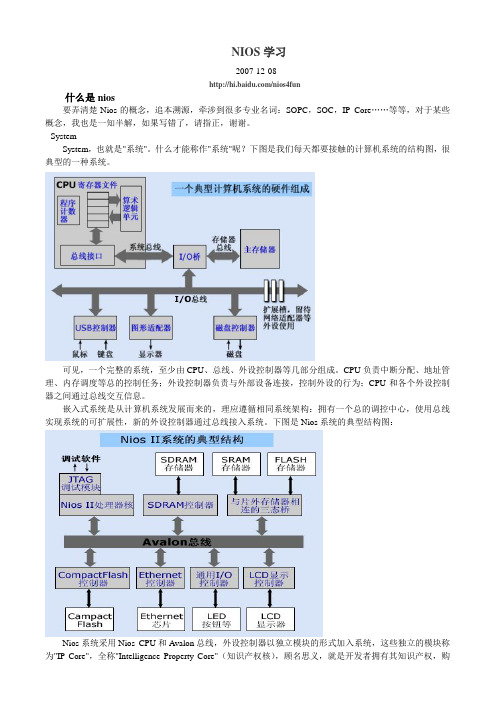

SOPC可以理解为SOC在可编程器件上的实现,如果硬件调试成功后直接投片生产成“固定结构的芯片”,则其为普通的SOC;如果其硬件就是基于FPGA的,也就是说它是“用FPGA做为最终实现”的,它在以后也可以随时进行硬件升级与调试的,我们就叫它为SOPC的设计方法,所以说SOPC是SOC的一种解决方案。

--硬核,软核

上面提到,FPGA由存放在片内RAM中的程序进行配置,MPU是System不可或缺的一部分,如果设计者用到的MPU产品是一段VHDL或Verilog HDL代码,那么他在使用的时候可以对MPU进行修改,以满足自己所需要的功能。这种MPU称为"软核",典型代表有Nios软核和MicroBlaze软核。

软核与硬核的优缺点是很明显的,如果追求性能的稳定和应用的简便,应该选择硬核;硬核固然有很多优势,但它在灵活性上还是受到了制约。道理很简单:一旦你在某个型号的FPGA中加入了一个硬核MPU,硬核MPU也就将其“不灵活”的属性带给了这个平台——MPU过时了,也就意味着平台过时了。因此,如果想追求更大限度的灵活性,设计者可以选择在FPGA中“写”入一个软核,而不是“固化”一个硬核。

NiosⅡ嵌入式处理器设计

并行计算

03

利用多个处理器核心同时处理多个数据,实现大规模数据处理。

动态调度技术

静态调度

在编译时确定指令的执行顺 序。

动态调度

在运行时根据指令的依赖关 系和资源冲突,动态调整指 令的执行顺序。

编译器优化

利用编译器对程序进行优化 ,减少冗余指令和优化指令 执行顺序。

05 NIOS II处理器应用实例

静态并行

通过编译器优化,将多个独立无依赖的指令并 行执行。

动态并行

在运行时根据指令之间的依赖关系,将无依赖 的指令并行执行。

超标量并行

通过增加硬件资源,同时执行多个指令,提高处理器的并行处理能力。

数据并行技术

单指令多数据流

01

在同一时刻对多个数据执行相同的操作,实现数据并行处理。

向量化

02

将数据分组,对每组数据执行相同的操作,提高数据处理速度。

高效能DSP算法

对于通信系统中的数字信号处理需求,如解调、调制、滤 波等,NIOS II处理器能够高效地实现各种DSP算法。

数字信号处理应用

数字信号处理应用

在数字信号处理领域,NIOS II处理器广泛应用于音频、视频、雷达、导航等信号处理 场景。它能够快速处理大量的数字信号数据,实现实时信号分析和处理。

感谢您的观看

调试与仿真工具

JTAG调试器

通过JTAG接口进行硬件调试,支持实时跟踪、断点、单步执行等 功能。

ModelSim仿真软件

用于模拟和验证硬件设计,支持多种硬件描述语言,如VHDL和 Verilog。

SOPC Builder

用于构建可定制的片上系统(SOPC),支持将多个IP核组合在一 起,并生成相应的硬件描述语言代码。

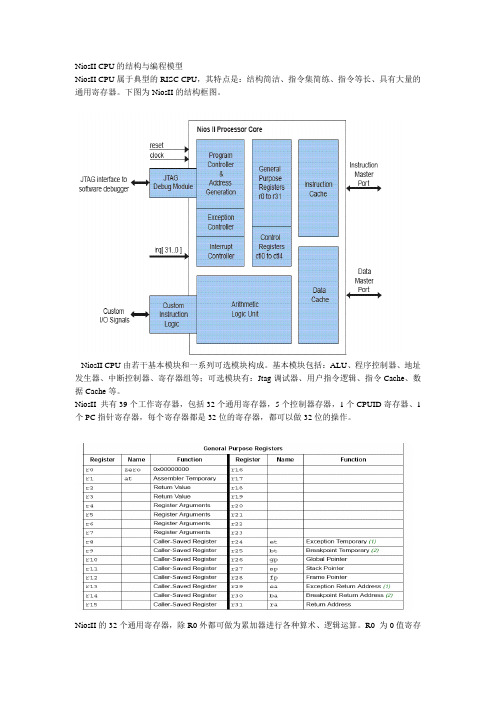

NiosII CPU的结构与编程模型

NiosII CPU的结构与编程模型NiosII CPU属于典型的RISC CPU,其特点是:结构简洁、指令集简练、指令等长、具有大量的通用寄存器。

下图为NiosII的结构框图。

NiosII CPU由若干基本模块和一系列可选模块构成。

基本模块包括:ALU、程序控制器、地址发生器、中断控制器、寄存器组等;可选模块有:Jtag调试器、用户指令逻辑、指令Cache、数据Cache等。

NiosII 共有39个工作寄存器,包括32个通用寄存器,5个控制器存器,1个CPUID寄存器、1个PC指针寄存器,每个寄存器都是32位的寄存器,都可以做32位的操作。

NiosII的32个通用寄存器,除R0外都可做为累加器进行各种算术、逻辑运算。

R0 为0值寄存器,对其进行读操作返回值是0,写操作对其没有影响,这一寄存器在指令集中有特殊的应用。

R24是中断处理程序专用寄存器,它是给中断处理程序专用的,虽然在用户程序中许访问,但不要用来保存数据,因为其中数据有可能被中断处理程序覆盖掉。

同样,R25是调试代理专用寄存器,也不要在用户程序中使用。

R29是PC指针的中断堆栈寄存器,当有中断发生时,这一寄存器用来保留一个返回地址,以便从中断处理程序返回到被中断的程序。

R30是PC指针的断点堆栈寄存器,用于系统调试。

当程序运行过程中遇到断点,这一寄存器中保留一个返回地址,以便从调试代理程序返回。

R31是PC指针的调用堆栈,用于子程序调用。

执行子程序调用指令时,这一寄存器中保留返回地址,以便从子程序返回。

R26、R27、R28在C开发系统中付予了一些特殊的应用,其中R27被作堆栈指针。

NiosII 有5个控制寄存器和一个CPUID寄存器。

Ctl0是程序状态字,目前只有BIT0、BIT1两位是有效的,高30位保留。

BIT0是全局中断控制位,用于中断的全局管理,1为允许,0为禁止。

BIT1是工作模式控制位。

当这一位为1时,系统工作于用户模式,当其为0时,系统工作于管理模式。

第3章NiosII体系结构

算术逻辑单元 (ALU)

数据 Cache

Nios II 处理器结构框图

紧耦合 指令存储器

紧耦合 指令存储器

指令总线 数据总线

紧耦合 数据存储器

紧耦合 数据存储器

Nios II采用哈佛结构,数据总线和指令 总线分开。

为了调试方便,Nios II处理器集成了一 个JTAG调试模块。

为了提高系统的整体性能,Nios II内核不仅 可以集成数据Cache和指令Cache,还带有 紧耦合存储器TCM接口。TCM可以使Nios II 处理器既能提高性能,又能获得可预测的实 时响应。

rr017或zero:

子程序要保存的寄存器

r总r11或8是a存t: 放0值,对子它程序读要写保无存的效寄。存器

这作N所r用r用个rr4212i90个临以~o,来来子sr寄时常r传传程I73I没:存变:用递递序有器量它44。个个专在。来r3非非门汇对存浮浮的子 子编寄放程程点点清程存返序序参参零序器回要要数数指中清保保值给给存存令常零的的的一一,用。高寄寄存存器器

算术逻辑单元 (ALU)

数据 Cache

Nios II 处理器结构框图

紧耦合 指令存储器

紧耦合 指令存储器

指令总线 数据总线

紧耦合 数据存储器

紧耦合 数据存储器

3.4 复位信号

CPU复位后,Nios II处理器将执行下列操作:

清除状态寄存器status,使之为0x0;

指令Cache与程序存储器的关联被置为无效, 处理器从固态程序存储器(比如Flash)中的reset地 址处取得第一条指令;

Nios II把外部硬件的中断事件交由中断控制器管理, 内核异常事件交由异常控制器管理。

Nios II的寄存器文件包括32个通用寄存器和6个控 制寄存器,Nios II结构允许将来添加浮点寄存器。

NIOS2完整教程

NIOS2完整教程NIOSII是一种32位可配置的软核处理器,支持使用硬件描述语言(HDL)进行快速设计和开发。

下面是一个完整的NIOSII教程,介绍了NIOSII的基本概念和使用方法。

第一部分:NIOSII概述(300字)NIOS II是Altera公司推出的一种可配置软核处理器。

它可以根据需要进行配置,包括选择处理器指令集的大小和功能,以及设置外设和存储器的接口。

NIOS II是基于经典的RISC架构,具有高性能和灵活性。

第二部分:NIOSII的基本构成(300字)NIOSII处理器由五个核心组件组成:指令集体系结构(ISA)、处理器核心、数据存储器、指令存储器和外设接口。

ISA定义了NIOSII支持的指令集,包括整数指令、浮点指令和多媒体指令。

处理器核心执行指令,并且可以执行单周期、多周期或流水线处理。

数据存储器用于存储数据,指令存储器用于存储程序指令。

外设接口用于连接NIOSII处理器和外部设备。

第三部分:NIOSII的配置和开发环境(300字)第四部分:NIOSII的应用场景(300字)NIOSII可用于各种应用场景,包括但不限于嵌入式系统、通信系统、工业自动化和军事应用。

NIOSII的可配置性使得它非常适合于各种需求和资源约束的项目。

NIOSII的性能和可扩展性使得它能够满足高带宽和实时性要求的应用。

此外,NIOSII的软件开发环境也非常成熟和易于使用,可以加快开发过程。

第五部分:NIOSII的优势和挑战(300字)NIOSII相对于其他软核处理器的主要优势在于其可配置性和性能。

NIOSII可以根据需求进行定制,并且可以实现高度优化的硬件和嵌入式软件系统。

然而,NIOSII的可配置性也带来了一些挑战,例如设计复杂性和调试困难。

此外,NIOSII的性能也受限于硬件资源的可用性和设计的质量。

总结(200字)在本教程中,我们介绍了NIOSII的基本概念和使用方法。

NIOSII是一种可配置的软核处理器,支持使用HDL进行快速设计和开发。

Nios II嵌入式Web服务器的实现

Nios II嵌入式Web服务器的实现引言嵌入式系统是指被嵌入到各种产品或工程应用中以微处理器或微控制器为核心的软硬件系统。

嵌入式系统与Internet技术相结合,形成的嵌入式Internet技术是近几年随着计算机网络技术的普及而发展起来的一项新兴技术。

工程技术人员、管理人员或调试人员通过Web而不用亲临现场就可以得到远程数据,并对测控仪器进行控制、校准等工作。

这里介绍利用嵌入式软核处理器Nios II及广泛应用的嵌入式操作系统uClinux来实现电网参数的远程测控服务器的功能。

1、功能及体系结构图1 是系统结构,其中嵌入式Web服务器和监控端位于现场,它们之间的连接可以用串行口、并行口、USB等实现。

现场监控端完成对目标地区电网参数(电压、电流、谐波等数据)的检测,并将检测结果实时传送至web界面,使得无论监控人员在哪里,只要连接至Internet网络,便可对目标区域电网参数实时观测。

其实现过程是:三相电压、电流分别通过电压互感器、电流互感器变换后,经电路调理送至AID 转换,每周期采样128点,DSP芯片对采样数据进行FIR数字滤波、FFT运算、计算各参数值、存储、显示等操作。

测量电路与Nios之间的通信通过串口传输,根据事先约定的通信协议(基于Modbus协议)可以方便地把所测数据发送至以Nios II处理器为核心的嵌入式服务器。

通过CGI技术,完成远程监控端的命令传输及将测量数据实时传送至远程监控端。

图1 系统结构图2、硬件结构系统的硬件结构如图2所示。

硬件系统的核心是构建于Ahera Cyclone FPGA中的Nios II嵌入式软核处理器。

Nios II系列嵌入式处理器是一款通用的RISC结构的CPU,它定位于广泛的嵌入式应用。

Nios II 处理器系列包括了三种核心:快速的(Nios II/f)、经济的(Nios II/e)和标准的(Nios II/s)内核,每种都针对不同的性能范围和成本而优化。

NOIS II简介资料

处理器内核 Nios II/s 0.74 127 165 MHz <1,400 5 2G字节 512字节到64K字节 可选 静态 可选 - Nios II/f 1.16 218 185 MHz <1,800 6 2G字节 512字节到64K字节 可选 动态 可选 512字节到64K字节

存储器流水线访问

NIOS II简介

江苏大学电气信息学院 版权者:赵不贿 主讲人:闫小喜

概述 Nios II处理器架构简介 编程模型

Nios II 采用流水技术和哈佛结构的通用精减指令 集计算机(RISC)

1.具有完整的32位指令集、32位数据通道和地址空间; 2.带有32个通用寄存器; 3.32个外部中断; 4.单指令的32位与32位乘和除的结果是32位;对于结果是64位或 128位的乘法提供专用指令; 5.带有单指令桶形(循环)移位寄存器; 6.可访问各种片内外设,提供与片外存储器和外设的接口;

Stratix 、 Stratix II、 Stratix III系列;

HardCopy、 HardCopyII、 HardCopy Stratix器件; HardCopy APEX三代。

Cyclone II EP2C系列片上资源

Stratix II EP2S系列片上资源

Nios II设计嵌入式系统的流程:

7.具有硬件辅助调试模块,可在IDE环境下执行开始、停止、单 步执行和追踪等操作;

8.软件集成环境基于GNU C/C++和Eclipse IDE;

9.所有NIOS CPU其指令集架构兼容;

10.处理器性能超过150DMIPS(每秒1亿5千万条整数运算指令)。

支持Nios II的FPGA

Cyclone 、 CycloneII、 CycloneIII系列;

嵌入式技术概述_NIOSⅡ处理器体系结构介绍

r6

r7

传递给函数的参数

传递给函数的参数

r22

r23

子程序要保存的寄存器

子程序要保存的寄存器

r8

r9 r10 r11 r12 r13 r14 r15

调用者要保存的寄存器

调用者要保存的寄存器 调用者要保存的寄存器 调用者要保存的寄存器 调用者要保存的寄存器 调用者要保存的寄存器 调用者要保存的寄存器 调用者要保存的寄存器

2013-8-6

OCEAN UNIVERSITY OF CHINA

12

工程学院 自动化及测控系

NIOSⅡ处理器的体系结构

clock reset cpu_resetrequest cpu_resettaken 软件调试 JTAG接口

NiosII 处理器核

紧耦合 指令存储器 通用寄存器 r0..r31 指令 紧耦合 指令存储器

用户定制指令:

NIOSⅡ处理器的ALU直接与用户定制指令逻辑相连,对用户定制指 令的访问等同于系统指令集的指令。

浮点指令:

NIOSⅡ支持符合IEEE STD754-1985规范的单精度浮点指令,浮点指 令以用户定制指令的方式实现。

2013-8-6

OCEAN UNIVERSITY OF CHINA

8

工程学院 自动化及测控系

&

程序控制器 JTAG调试模块 异常控制器 中断源[0..31] 中断控制器

通用寄存器 NIOSⅡ处理器核采用硬件实现,实现指令集并支持各 r0..r31 功能模块的工作,处理器核不包含外设和接口逻辑; 指令

NIOSⅡ体系结构定义了指令集,但并不是特定的硬件 Cache 指令存储器 实现,体系结构中的各功能模块可由硬件实现、软件 控制寄存器 实现、也可省去

NIOS II中结构体与联合体的用法

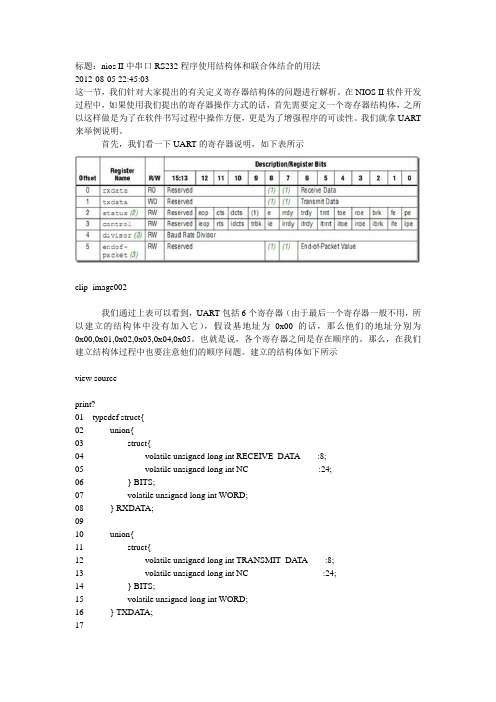

标题:nios II中串口RS232程序使用结构体和联合体结合的用法2012-08-05 22:45:03这一节,我们针对大家提出的有关定义寄存器结构体的问题进行解析。

在NIOS II软件开发过程中,如果使用我们提出的寄存器操作方式的话,首先需要定义一个寄存器结构体,之所以这样做是为了在软件书写过程中操作方便,更是为了增强程序的可读性。

我们就拿UART 来举例说明。

首先,我们看一下UART的寄存器说明,如下表所示clip_image002我们通过上表可以看到,UART包括6个寄存器(由于最后一个寄存器一般不用,所以建立的结构体中没有加入它),假设基地址为0x00的话,那么他们的地址分别为0x00,0x01,0x02,0x03,0x04,0x05。

也就是说,各个寄存器之间是存在顺序的。

那么,在我们建立结构体过程中也要注意他们的顺序问题。

建立的结构体如下所示view sourceprint?01 typedef struct{02 union{03 struct{04 volatile unsigned long int RECEIVE_DATA :8;05 volatile unsigned long int NC :24;06 } BITS;07 volatile unsigned long int WORD;08 } RXDATA;0910 union{11 struct{12 volatile unsigned long int TRANSMIT_DATA :8;13 volatile unsigned long int NC :24;14 } BITS;15 volatile unsigned long int WORD;16 } TXDATA;1718 union{19 struct{20 volatile unsigned long int PE :1;21 volatile unsigned long int FE :1;22 volatile unsigned long int BRK :1;23 volatile unsigned long int ROE :1;24 volatile unsigned long int TOE :1;25 volatile unsigned long int TMT :1;26 volatile unsigned long int TRDY :1;27 volatile unsigned long int RRDY :1;28 volatile unsigned long int E :1;29 volatile unsigned long int NC :1;30 volatile unsigned long int DCTS :1;31 volatile unsigned long int CTS :1;32 volatile unsigned long int EOP :1;33 volatile unsigned long int NC1 :19;34 } BITS;35 volatile unsigned long int WORD;36 } STATUS;3738 union{39 struct{40 volatile unsigned long int IPE :1;41 volatile unsigned long int IFE :1;42 volatile unsigned long int IBRK :1;43 volatile unsigned long int IROE :1;44 volatile unsigned long int ITOE :1;45 volatile unsigned long int ITMT :1;46 volatile unsigned long int ITRDY :1;47 volatile unsigned long int IRRDY :1;48 volatile unsigned long int IE :1;49 volatile unsigned long int TRBK :1;50 volatile unsigned long int IDCTS :1;51 volatile unsigned long int RTS :1;52 volatile unsigned long int IEOP :1;53 volatile unsigned long int NC :19;54 } BITS;55 volatile unsigned long int WORD;56 } CONTROL;5758 union{59 struct{60 volatile unsigned long int BAUD_RATE_DIVISOR :16;61 volatile unsigned long int NC :16;62 } BITS;63 volatile unsigned long int WORD;64 } DIVISOR;6566 }UART_STR;对于这样一个大的结构体,我们来逐层分析一下:第一,整个结构体由5个共用体组成,共同体的顺序是由寄存器的偏移量决定的,这一点前面已经有所叙述。

NOIS II简介

异常控制器:Nios II体系结构提供一个简单(jiǎndān)的非向量异常控

制器来处理运行时产生的所有类型的异常。一旦在程序运行过程中产

生了异常(包括硬件中断),CPU就会转到异常地址中运行异常处理

程序。异常处理程序判别异常产生的原因,并运行相应的服务子程序。

中断控制器:Nios II体系结构支持32个外部硬件中断,即

2.建立Quartus II工程,建立顶层实体;

3.调用SOPC Bulider生成用户定制的系统模块

(包括标准外设);

4.将SOPC系统模块集成到硬件工程中,并添加

其他模块;

5.在顶层实体中,将这些连接起来;

6.分配引脚和编译工程,生成硬件系统的配置

文件.sof和.pof文件;

第八页,共162页。

r17

子程序要保存的寄存器

r2习惯上,子程序必须保证

函数返回值(低32位)

r18

子程序要保存的寄存器

r3这些寄存器中的值在调用

函数返回值(高32位)

r19

子程序要保存的寄存器

r4

r20

子程序要保存的寄存器

r21

子程序要保存的寄存器

r22

子程序要保存的寄存器

r23

子程序要保存的寄存器

r1r16~r23:

at

前后保持不变,即要么在

传递给函数的参数

子程序执行时不使用它们

r5(tā men),要么使用前把

传递给函数的参数

r6它们(tā men)保存在堆栈

传递给函数的参数

r24或et:

中并在退出时恢复。

r7

传递给函数的参数

在异常处理时使用。使用时,

r25或bt:

nios2架构uclinux(nios2-linux-20080619开发包)的过程

nios2架构uclinux(nios2-linux-20080619开发包)的过程前言:最近在论坛上有一些朋友提出我上传的”nios2架构uclinux (nios2-linux-20080619开发包)的过程”是英文版的不好读.碰巧我最近整理资料就把架构过程重新整理了一篇.便于朋友参考. 对于英语阅读能力比较好的朋友建议参考我整理的英文版.内容比较详细.由于作者水平有限,在整理过程中难免会出现一些错误,望朋友们批评并指正.转贴的朋友请注明出处/chong_lang/ (本博客正在完善中欢迎交流学习)开发环境:在vmware 中安装centos5.2操作系统(在网上下载安装CentOS-52-i386-bin-DVD)本人所使用的开发板为: altera公司的ep2c35f672c6n宿主机windows开发平台为: windows xp sp3在宿主机上安装的linux开发平台为centos5.2 内核为: vmlinuz-2.6.18开发工具为:quartus7.2安装过程Ok! 现在开始niosii架构uclinux过程首先要在centos下挂载window 下的一个共享目录便于centos与宿主机传送文件,不会挂载的朋友google 一下linux 下mount命令的使用在centos操作系统上我的开发目录设在了/home/zhaozhilei[root@localhost ~]# cd /hom e/zhaozhilei安装架构uclinux时所需要的库[root@localhost zhaozhilei]# sudo yum install git-all make gcc ncurses-devel bison byacc flex \gawk gettext ccache zlib-devel gtk2-devel lzo-devel一.下载uclinux开发包[root@localhost zhaozhilei]#wgetftp:///outgoing/nios2-linux-20080619.tar二.解压nios2-linux-20080619.tar[root@localhost zhaozhilei]# tar xf nios2-linux-20080619.tar三.进入nios2-linux目录[root@localhost zhaozhilei]# cd nios2-linuxls # see what's inbinutils gcc3 README uClibc use_http_for_upda techeckout insight toolchain-build uClinux-distelf2flt linux-2.6 u-boot update四.检查文件是否齐全[root@localhost nios2-linux]#./checkout五.下载交差编译工具[root@localhost nios2-linux]# cd ..[root@localhost zhaozhilei]# wgetftp:///outgoing/nios2g...080203.tar.bz2六.解压文件[root@localhost zhaozhilei]#sudo tar jxf nios2gcc-20080203.tar.bz2-C /七.添加PATH路径[root@localhost zhaozhilei]#cd[root@localhost ~]# vim ./bash_profile添加:PATH=$PATH:/opt/nios2/bin (红颜色部分是要添加的部分)八.检查是否加入PATH[root@localhost ~]#echo $PATH结果应为:/usr/local/sbin:/usr/local/bin:/usr/sbin:/usr/bin:/sbin:/bin:/usr/gam es:/opt/nios2/bin十.检查交叉编译环境是否安装成功[root@localhost ~]#nios2-linux-uclibc-gcc –v结果应为:Reading specs from /opt/nios2/lib/gcc/nios2-linux-uclibc/3.4.6/specs Configured with:/root/buildroot/toolchain_build_nios2/gcc-3.4.6/configure--prefix=/opt/nios2 --build=i386-pc-linux-gnu --host=i386-pc-linux-gnu --target=nios2-linux-uclibc --enable-languages=c --enable-shared--disable-__cxa_atexit --enable-target-optspace --with-gnu-ld--disable-nls --enable-threads --disable-multilib--enable-cxx-flags=-staticThread model: posixgcc version 3.4.6十一. 编译内核和应用,进入到uclinux-dist目录[root@localhost ~i]#cd /hom e/zhaozhilei/nios2-linux[root@localhost nios2-linux]#cd uClinux-dist[root@localhost uClinux-dist]#make menuconfig确保选择以下内容Vendor/Product Selection --->--- Select the Vendor you wish to targetVendor (Altera) --->--- Select the Product you wish to targetAltera Products (nios2) --->Kernel/Library/Defaults Selection --->--- Kernel is linux-2.6.xLibc Version (None) --->[*] Default all settings (lose changes)[ ] Customize Kernel Settings[ ] Customize Vendor/User Settings[ ] Update Default Vendor Settings注意:在成功引导uclinux之前不要改变上面任何设置然后 <exit> <exit> <yes>十二 .编译硬件配置选择相应的cpu 和sdrma[root@localhost uClinux-dist]#make vendor_hwselect SYSPTF=/配件配置目录/your_system.ptf选择cpu出现如下图(如果是多cpu的话,根据实际情况选择)选择sdram如下图(在这里我选择的是1即ddr_sdram_0,其它根据实际情况)十三. 编译内核和应用[root@localhost uClinux-dis]# make (需要编译一段时间)十四. 将 zImage文件copy到宿主机上[root@localhost yanfa]# cp ./ images/zImage 你挂载的目录十五. 在宿主机上(windows)打开nios ii eds 7.2 command shell开始->程序->altera-> nios ii eds 7.2->nios ii eds 7.2 command shell 十六.下载你的sof文件到目标板十七. 下载zImage 到目标板十八. 打开nios终端.十九. Uclinux正确启动时应出现如下信息Using cable "USB-Blaster [USB 2-1.2]", device 1, instance 0x00 Pausing target processor: OKInitializing CPU cache (if present)OKDownloaded 1272KB in 7.7s (165.1KB/s)Verified OKStarting processor at address 0x00500000# nios2-terminalnios2-terminal: connected to hardware target using JTAG UART on cable nios2-terminal: "USB-Blaster [USB 2-1.2]", device 1, instance 0nios2-terminal: (Use the IDE stop button or Ctrl-C to terminate)Uncompressing Linux... Ok, booting the kernel.Linux version 2.6.26-rc6 (hippo@darkstar) (gcc version 3.4.6) #2 PREEMPT Mon Jun 16 14:30:09 CST 2008uClinux/Nios IIBuilt 1 zonelists in Zone order, mobility grouping off. Total pages: 8128 Kernel command line:PID hash table entries: 128 (order: 7, 512 bytes)Dentry cache hash table entries: 4096 (order: 2, 16384 bytes)Inode-cache hash table entries: 2048 (order: 1, 8192 bytes)Memory available: 30136k/2333k RAM, 0k/0k ROM (1552k kernel code, 781k data)Mount-cache hash table entries: 512net_namespace: 180 bytesNET: Registered protocol family 16NET: Registered protocol family 2IP route cache hash table entries: 1024 (order: 0, 4096 bytes)TCP established hash table entries: 1024 (order: 1, 8192 bytes)TCP bind hash table entries: 1024 (order: 0, 4096 bytes)TCP: Hash tables configured (established 1024 bind 1024)TCP reno registeredNET: Registered protocol family 1io scheduler noop registeredio scheduler deadline registered (default)ttyJ0 at MMIO 0x8009340 (irq = 8) is a Altera JTAG UARTconsole [ttyJ0] enabledttyS0 at MMIO 0x8008e00 (irq = 7) is a Altera UARTdm9000 Ethernet Driver, V1.30TCP cubic registeredNET: Registered protocol family 17RPC: Registered udp transport module.RPC: Registered tcp transport module.Freeing unused kernel memory: 572k freed (0x1b8000 - 0x246000)Shell invoked to run file: /etc/rcCommand: hostname uClinuxCommand: mount -t proc proc /procCommand: mount -t sysfs sysfs /sysCommand: mount -t usbfs none /proc/bus/usbmount: mounting none on /proc/bus/usb failed: No such file or directory Command: mkdir /var/tmpCommand: mkdir /var/logCommand: mkdir /var/runCommand: mkdir /var/lockCommand: mkdir /var/emptyCommand: ifconfig lo 127.0.0.1Command: route add -net 127.0.0.0 netmask 255.0.0.0 loCommand: cat /etc/motdWelcome to____ _ _/ __| ||_|_ _| | | | _ ____ _ _ _ _| | | | | | || | _ \| | | |\ \/ /| |_| | |__| || | | | | |_| |/| ___\____|_||_|_| |_|\____|\_/\_/| ||_|呵呵, 恭喜你成功运行了uclinux操作系统现在你可以根据自己的喜好从新配置内核啦!!如下操作:从新回到虚拟机下的uclinux-dist目录下[root@localhost uclinux-dist]#make menuconfigKernel/Library/Defaults Selection --->(linux-2.6.x) Kernel Version(None) Libc Version[ ] Default all settings (lose changes)[*] Customize Kernel Settings[*] Customize Vendor/User Settings[ ] Update Default Vendor SettingsThen <exit> <exit> <yes> .以下可以根据自己的喜好配置内核这里不再叙述小提示:在配置内核的过程中如果有朋友在编译内核加入iptables 时若出现如下错误:include/linux/netfilter_ipv4/ip_tables.h:18:28: linux/compiler.h: No such file or directorymake[3]: *** [iptables.o] 错误1make[3]: Leaving directory `/usr/local/yanfa/nios2-linux/uClinux-dist/user/iptables'make[2]: *** [iptables] 错误2make[2]: Leaving directory `/usr/local/yanfa/nios2-linux/uClinux-dist/user'make[1]: *** [all] 错误2make[1]: Leaving directory `/usr/local/yanfa/nios2-linux/uClinux-dist/user'make: *** [subdirs] 错误1解决方法:把/usr/home/zhaozhilei/nios2-linux/uClinux-dist/user/iptables/include/linux/netfilter_ipv4 中的ip_tables.h中的#include <linux/compiler.h> 注解掉可解决编译uclinux_dist内核时出现的加载iptables 的错误。

NiosII嵌入式处理器简介

NiosII嵌入式处理器简介Nios II嵌入式处理器简介Nios?II系列嵌入式处理器是一款通用的RISC结构的CPU,它定位于广泛的嵌入式应用。

Nios II处理器系列包括了三种核心——快速的(Nios II/f)、经济的(Nios II/e)和标准的(Nios II/s)内核——每种都针对不同的性能范围和成本而优化。

所有的这三种核都使用共同的32位的指令集结构(ISA)百分之一百的二进制代码兼容。

使用业界领先的设计软件——Altera的Quartus II?软件以及SOPC Builder工具,工程师可以轻松的将Nios II处理器嵌入到他们的系统中。

Nios II系列嵌入式处理器在不到三年的时间里,有超过12,000块Nios开发套件售出,第一代的16位Nios处理器已成为可编程逻辑设计中软核嵌入式处理器的标准。

32位的Nios II嵌入式处理器建立在成功的第一代的Nios 处理器的基础上,它不仅提供更高的性能、更低的成本(即更少的逻辑资源占用率),还提供了齐全的软件开发工具以及更高的系统灵活性。

表1列出了Nios II处理器的特性。

表2列出了Nios II系列成员。

表3列出了Nios II嵌入式处理器支持的FPGA系列。

可配置的软核嵌入式处理器的优势嵌入式开发人员面对的一个最大挑战就是如何选择一个适合他们应用需求的处理器。

现今已有数百种嵌入式处理器——每种都具备一组不同的外设、存储器、接口和性能特性,工程师很难做出一个合理的选择:要么选择在某些性能上多余的处理器(为了匹配实际应用所需的外设和接口要求等等),要么为了保持成本的需求而达不到原先预计的理想方案。

随着Nios II软核处理器的推出,工程师可以轻松创建一款“完美”的处理器,无论是外设、存储器接口、性能特性以及成本。

这些优势的都借助于在Altera的FPGA上创建一个定制的片上系统,或者,更精确的说是一个可编程单芯片系统(SOPC)。

nios2课程设计

nios2课程设计一、课程目标知识目标:1. 理解Nios II处理器的核心概念和原理,掌握其基本架构和运作机制。

2. 学习并掌握基于Nios II处理器的嵌入式系统设计流程和方法。

3. 掌握Nios II处理器的编程技术,包括汇编语言和C语言的编程。

技能目标:1. 能够运用Nios II处理器设计简单的嵌入式系统,进行硬件描述和软件编程。

2. 能够运用Nios II处理器的开发工具进行系统仿真、调试和优化。

3. 能够分析并解决基于Nios II处理器的嵌入式系统问题,提高实际工程应用能力。

情感态度价值观目标:1. 培养学生对嵌入式系统设计和开发的兴趣,激发创新意识和探索精神。

2. 培养学生良好的团队合作精神和沟通能力,提高解决实际问题的自信心。

3. 增强学生对我国嵌入式产业发展的认识,树立为国家和民族科技事业做贡献的价值观。

课程性质分析:本课程为电子信息类专业课程,以实践性为主,注重培养学生的动手能力和实际应用能力。

学生特点分析:学生具备一定的电子技术和编程基础,对嵌入式系统有一定了解,但Nios II处理器相关知识掌握较少。

教学要求:结合学生特点,采用理论与实践相结合的教学方法,以项目驱动为导向,使学生在实践中掌握Nios II处理器的相关知识,提高嵌入式系统设计和开发能力。

通过课程学习,实现上述课程目标,为后续相关课程和实际工作打下坚实基础。

二、教学内容1. Nios II处理器概述:介绍Nios II处理器的背景、特点和应用领域,使学生对其有一个全面的了解。

教材章节:第一章2. Nios II处理器架构:讲解Nios II处理器的硬件架构、指令集和存储器结构等内容。

教材章节:第二章3. 嵌入式系统设计流程:介绍基于Nios II处理器的嵌入式系统设计流程,包括硬件描述、软件编程、系统集成和调试等。

教材章节:第三章4. Nios II处理器编程技术:学习Nios II处理器的编程方法,包括汇编语言和C语言的编程技巧。

【翻译】NiosII处理器简介(NiosII)

【翻译】NiosII处理器简介(NiosII)处理器简介本⽂介绍的Altera Nios II处理器是⼀个可在Altera FPGA器件⾥实现的软核处理器。

主要讲述Nios II的基本架构和其指令集。

配合Quartus II 软件,使⽤Altera的SOPC Builder可以很容易的把Nios II处理器和它的内存及外围组件例化。

关于Nios II处理的完整描述请参阅《Nios II处理器参考⼿册》,在Altera官⽹的⽂献区可找到该⼿册。

SOPC Builder的简介在⼊门简介⾥有提供,也可在官⽹的⼤学计划板块找到。

本⽂包含的内容:⽬录Altera Nios II处理器是⼀个软核处理器,⽤硬件描述语⾔定义,使⽤Quartus II软件可在Altera的FPGA器件⾥实现。

本⽂为想要在Altera DE2开发板上实现⼀个基本Nios II系统的⽤户提供⼀个关于Nios II处理器的简介。

系统Nios II处理器可使⽤许多其他组件构成⼀个完整的系统。

这些组件包括许多标准外设之外,还可由⽤户⾃定义外设。

Altera DE2开发板含有⼏个可集成在Nios II系统⾥的组件。

图1就是⼀个这样的系统。

Nios II处理器和⽤来连接DE2上其他芯⽚的接⼝都在Cyclone II FPGA⾥实现。

这些组件通过Avalon 交换结构连接。

Cyclone II器件的内存块可为Nios II处理器提供⽚上内存。

它们可直接或通过Avalon⽹络与处理连接。

通过相应的接⼝访问DE2上的SRAM和SDRAM。

系统使⽤的I/O设备例化为I/O接⼝。

连接主机和DE2的USB线缆接⼝由⼀个特殊的JTAG UART接⼝提供。

这个接⼝电路和其相应的软件叫做USB_Blaster。

另⼀个名为JTAG Debug的模块,⽤来使主机控制Nios II处理器。

这样,就可以执⾏操作,⽐如,下载程序到内存⾥,启动和停⽌执⾏,设置程序断点,和搜集实时数据。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.7 Nios II的异常处理

3.8 存储器及I/O结构

3.9 存储器和外设访问

信号。

cpu_resetrequest:是一个可以 让CPU复位但不影响Nios II系统 其它外设的局部复位信号。

IO 口

中断源 [0 .. 31 ]

中断控制器

Nios II处理器结构框图

用户逻辑

算

第三章 目录

3.1 Nios II处理器结构

3.2 Nios II的寄存器文件

3.3 算数逻辑单元(ALU) 3.4 复位信号 3.5 Nios II处理器运行模式 3.6 异常和中断控制器

3.1 Nios II处理器结构

为了提高系统的整

体性能,Nios II内 核不仅可以集成数 据Cache和指令 Cache,还带有紧 耦合存储器TCM接 口。TCM可以使 Nios II处理器既能 提高性能,又能获 得可预测的实时响 应。

clock reset cpu _resetrequest cpu _resettaken 软件调 试接口 JTAG接口

3.3 算术逻辑单元(ALU)

Nios II ALU支持的操作

种 类 描 述 算术运算 关系运算 逻辑运算 移位运算 ALU支持有符号和无符号数的加、减、乘和除法 支持有符号和无符号数的等于、不等于、大于等于和小 于(==,!=,>=,<)关系运算 支持AND、OR、NOR和XOR逻辑运算 支持移位和循环移位运算,在每条指令中可以将数据移 位和环移0到31位。支持算术右移和算术左移,还支持左、 右循环移位

第三章 目录

3.1 Nios II处理器结构

3.2 Nios II的寄存器文件 3.3 算数逻辑单元(ALU) 3.4 复位信号 3.5 Nios II处理器运行模式 3.6 异常和中断控制器 3.7 Nios II的异常处理

3.8 存储器及I/O结构

3.9 存储器和外设访问

紧耦合 指令存储器 指令总线 数据总线 紧耦合 数据存储器

IO口

用户逻辑

算术逻辑单元 (ALU)

数据Cache 紧耦合 数据存储器

Nios II处理器结构框图

Nios II的寄存器文件包括32个通用寄存器和6个 控制寄存器,Nios II结构允许将来添加浮点寄存

器,其具体细节在下节介绍

第3章 目录

紧耦合 指令存储器 指令总线 数据总线 紧耦合 数据存储器

控制寄存器组 ctl0..ctl5

用户定制的逻辑电路与 Nios II内核。

IO口

用户逻辑

算术逻辑单元 (ALU)

数据Cache 紧耦合 数据存储器

Nios II处理器结构框图

Nios II采用哈佛结构,数据总线和指令总线分开。 为了调试方便,Nios II处理器集成了一个JTAG调试模块。

3.1 Nios II处理器结构

3.2 Nios II的寄存器文件

3.3 算数逻辑单元(ALU)

3.4 复位信号

3.5 Nios II处理器运行模式 3.6 异常和中断控制器 3.7 Nios II的异常处理 3.8 存储器及I/O结构

3.9 存储器和外设访问

3.2 Nios II的寄存器文件

NiosII 理器核 处 紧耦合 指令存储器

地址发生器 & 程序控制器

通用寄存器组 r0..r31 指令Cache

异常控制器 中断源 [0..31 ] 中断控制器

紧耦合 指令存储器 指令总线 数据总线 紧耦合 数据存储器

控制寄存器组 ctl0..ctl5

IO口

用户逻辑

算术逻辑单元 (ALU)

数据Cache 紧耦合 数据存储器

Nios II的通用寄存器

尽管硬件对寄存器的用法几乎没有规定,但

是它们在实际使用过程中还是遵循一些约定俗成

的惯例。

我们通过下面的通用寄存器一览表来了解

Nios II的32个通用寄存器。

r16~r23: 习惯上,子程序必须保证这 些寄存器中的值在调用前后 保持不变,即要么在子程序 执行时不使用它们,要么使 用前把它们保存在堆栈中并 在退出时恢复。 r24或et: 在异常处理时使用。使用时, r25或bt: 可以不恢复原来的值。该寄存 在程序断点处理时使用。使用 r26或gp: 器很少作用其它用途。 时,可以不恢复原来的值。该 它指向静态数据区中的一个运 r27或sp: 寄存器很少作其它用途。 行时临时决定的地址。这意味 堆栈指针。Nios II没有专门的 r28或fp: 着在存取位于gp值上下32KB范 出栈(POP)入栈(PUSH)指令, 帧指针,习惯上用于跟踪栈的 r29或ea: 围内的数据时,只需要一条以 在子程序入口处,sp被调整指 变化和维护运行时环境。 保存异常返回地址。 r30或ba: gp作为基指针的指令即可完成。 向栈底部,然后以sp为基址, 保存断点返回地址。 r31或ra: 用寄存器基址+偏移地址的方 保存函数返回地址。 式来访问栈中的数据。

clock reset cpu _resetrequest cpu _resettaken 软件调 试接口 JTAG接口 异常控制器 中断源 [0..31 ] 中断控制器 控制寄存 器组 0..ctl5 ctl NiosII 理器核 处 紧耦合 指令存储器 地址发生器 & 程序控制器 通用寄存器组 r0..r31 指令Cache

3.1 Nios II处理器结构

Nios II是一种软核(Soft-Core)处理器。

所谓软核,是指未被固化在硅片上,使用时

需要借助EDA软件对其进行配置并下载到可 编程芯片(比如FPGA)中的IP核。软核最大 的特点就是可由用户按需要进行配置。

3.1 Nios II处理器结构

Nios II软核处理器简介 Nios II 处理器系列包括三种内核

estatus、bstatus—都是status寄存器的影子寄存器: •发生断点或者异常时:保存status寄存器的值; 第1位U—反映计算机当前状态: •断点或异常处理返回时:恢复status寄存器的值。 ienable—中断允许寄存器: • 1表示处于用户态(User每一位控制一个中断通道。例如: mode); 第0位PIE—外设中断允许位: ipending—中断发生标志位: •第0位为1:表示允许第0号中断发生; • 1表示允许外设中断; • 0表示处于超级用户态 每一位反映一个中断发生。例如: •第0位为0:表示禁止第0号中断发生; • 0表示禁止外设中断。 (Supervisor Mode)。 •第0位为1:表示第0号中断发生; cpuid—此寄存器中装载着处理器的id号: •第0位为0:表示第0号中断未发生; 该id号在生成Nios II系统时产生。Id号在多 处理器系统中可以作为分辨CPU的标识。

3.2 Nios II的寄存器文件

Nios ห้องสมุดไป่ตู้I的控制寄存器

Nios II的控制寄存器共有6个,它们的读/写访

问只能在超级用户态(Supervisor Model)由专用

的控制寄存器读/写指令(rdctl和wrctl)实现。

通过控制寄存器一览表,来了解控制寄存器

各位的意义。

status—状态寄存器: 只有第1位和第0位有意义。

第三章 目录

3.1 Nios II处理器结构

3.2 Nios II的寄存器文件 3.3 算数逻辑单元(ALU) 3.4 复位信号 3.5 Nios II处理器运行模式 3.6 异常和中断控制器 3.7 Nios II的异常处理

3.8 存储器及I/O结构

3.9 存储器和外设访问

第三章 目录

3.1 Nios II处理器结构

3.2 Nios II的寄存器文件

3.3 算数逻辑单元(ALU) 3.4 复位信号 3.5 Nios II处理器运行模式 3.6 异常和中断控制器

3.7 Nios II的异常处理

3.8 存储器及I/O结构

3.9 存储器和外设访问

用户逻辑接口用来连接

clock reset cpu _resetrequest cpu _resettaken 软件调 试接口 JTAG接口

NiosII 理器核 处 紧耦合 指令存储器

地址发生器 & 程序控制器

通用寄存器组 r0..r31 指令Cache

异常控制器 中断源 [0..31 ] 中断控制器

Nios II处理器结构框图

3.1 Nios II处理器结构

Nios II把外部硬件 的中断事件交由中 断控制器管理,内 核异常事件交由异 常控制器管理。

clock reset cpu _resetrequest cpu _resettaken 软件调 试接口 JTAG接口 异常控制器 中断源 [0..31 ] 中断控制器 控制寄存器组 ctl0..ctl5 NiosII 理器核 处 紧耦合 指令存储器 地址发生器 & 程序控制器 通用寄存器组 r0..r31 指令Cache

Nios II/f (快速)

性能最高,但占用的逻辑资源最多。

Nios II

Nios II/e (经济)

占用的逻辑资源最少,但性能最低。

32位软核处理器

Nios II/s (标准)

平衡的性能和尺寸。NiosII/s内核比 第一代的Nios CPU更快,占用的资 源更少。

3.1 Nios II处理器结构

3.3 算术逻辑单元(ALU)

未实现的指令:Nios II 处理器核没有一些指令的 实现,如:mul,muli,div,divu等,那么这些指令就 被认为是未实现的。当处理器遇到未实现指令时, 会产生一个异常,异常管理器调用相应软件来模 拟该指令操作。 用户定制指令: Nios II ALU直接和定制指令逻辑 相连,使用户指令和Nios II指令一样被访问和使 用。 浮点指令:以定制指令的方式实现。