74HCT4046A参考手册

常用集成电路功能简介

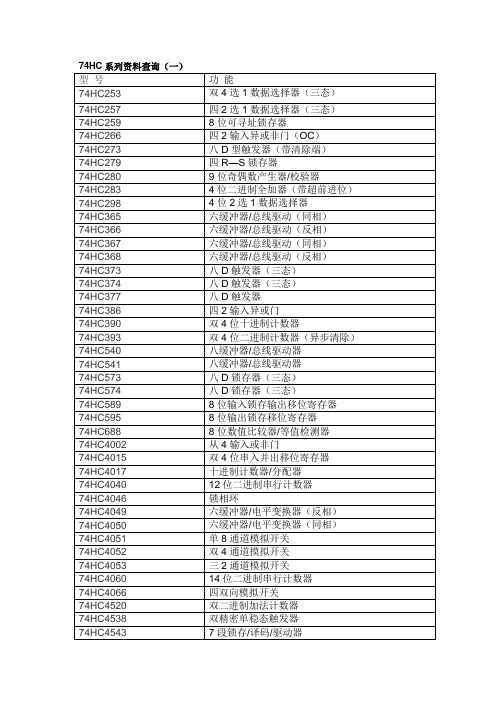

常用集成电路功能简介型号功能简述1710 视频信号处理集成电路2274 延迟集成电路2800 红外遥控信号接收集成电路4094 移位寄存串入、并出集成电路4260 动态随机存储集成电路4464 存储集成电路4558 双运算放大集成电路5101 天线开关集成电路15105 充电控制集成电路15551 管理卡升压集成电路31085 射频电源集成电路74122 可重触发单稳态集成电路85712 场扫描信号校正处理集成电路85713 行扫描信号校正集成电路0206A 天线开关集成电路03VFG9 发射压控振荡集成电路1021AC 发射压控振荡集成电路1097C 升压集成电路140N 电源取样比较放大集成电路14DN363 伺服控制集成电路1N706 混响延时集成电路20810-F6096 存储集成电路2252B 微处理集成电路24C01ACEA 存储集成电路24C026 存储集成电路24C04 存储集成电路24C64 码片集成电路24LC16B 存储集成电路24LC65 电可改写编程只读存储集成电路27C1000PC-12 存储集成电路27C2000QC-90 存储集成电路27C20T 存储集成电路27C512 电可改写编程只读存储集成电路28BV64 码片集成电路28F004 版本集成电路32D54 电源、音频信号处理集成电路32D75 电源、音频信号处理集成电路32D92 电源中频放大集成电路4066B 电子开关切换集成电路424260SDJ 存储集成电路4270351/91B9905 中频放大集成电路4370341/90M9919 中频处理集成电路4580D 双运算放大集成电路47C1638AN-U337 微处理集成电路47C1638AU-353 微处理集成电路47C432GP 微处理集成电路47C433AN-3888 微处理集成电路49/4CR1A 中频放大集成电路5G052 发光二极管四位显示驱动集成电路5G24 运算放大集成电路5W01 双运算放大集成电路649/CRIA70612 中频放大集成电路673/3CR2A 多模转换集成电路74HC04 逻辑与非门集成电路74HC04D 六反相集成电路74HC123 单稳态集成电路74HC125 端口功能扩展集成电路74HC14N 六反相集成电路74HC157A 多路转换集成电路74HC165 移相寄存集成电路74HC245 总线收发集成电路74HC32 或门四2输入集成电路74HC374八D 触发集成电路74HC573D 存储集成电路74HCT157 多路转换双输入集成电路74HCT4046A 压控振荡集成电路型号功能简述IAP722 调频高放、混频集成电路IFC380HC 图像中频放大集成电路IN065 二本振压控振荡集成电路IN706 数字混响延时集成电路IR2112 半桥式变换驱动集成电路IR2E01 发光二极管五位显示驱动集成电路IR2E02 发光二极管七位显示驱动集成电路IR3N06 调频中频放大集成电路IR3R15 音频前置放大集成电路IR3R18 双声道前置放大集成电路IR3R20A 自动选曲集成电路IR3R49 伺服控制集成电路IR3Y29AM 色度解码集成电路IRT1260 红外遥控信号发射集成电路IS61C256AH-15N 存储集成电路IS93C46 存储集成电路IX0035CE 场扫描输出集成电路IX0040AG 音频功率放大集成电路IX0040TA 音频功率放大集成电路IX0042CE 伴音制式切换6MHZ集成电路IX0052CE 伴音中频放大、鉴频及前置放大集成电路IX0062CE 图像中频放大、视频放大集成电路IX0064CE 图像中频放大、检波、视频放大集成电路IX0096CE 伴音信号处理集成电路IX0101SE 微处理集成电路IX0113 图像中频放大、检波、预视放集成电路IX0113CEZZ 图像中频放大、检波及预视放集成电路IX0118CE 视频放大集成电路IX0129CE 色度解码集成电路IX0132CE 液晶显示解码集成电路IX0147CE 电子选台集成电路IX0162GE 伺服控制集成电路IX0195CE 色度信号处理集成电路IX0203GE 频段转换集成电路IX0205CE 开关电源稳压集成电路IX0211CE 图像中频放大、视频信号处理集成电路IX0212G 高频、中频放大集成电路IX0214CE 音频控制集成电路IX0232CE 存储集成电路IX0237CE 微处理集成电路IX0238CEZZ 场扫描输出集成电路IX0241CE 音频控制集成电路IX0245CE 微处理集成电路IX0246CE 双向比较放大集成电路IX0247CE 开关电源稳压集成电路IX0250CE 音频功率放大集成电路IX0261CE 图像、伴音中频放大集成电路IX0304CE 色度解码及行场扫描处理集成电路IX0304CEZZ 色度解码及行场扫描处理集成电路IX0308CE 开关电源厚膜集成电路IX0310PAZZ 红外遥控信号接收集成电路IX0323CE 开关电源稳压集成电路IX0324CEN 视频、色度及行场扫描信号处理集成电路IX0365CE 伴音功率放大集成电路IX0371GE 磁头控制集成电路IX0388CE 中频放大集成电路IX0411CEN1 微处理集成电路IX0412CE 字符发生集成电路IX0438CE 红外遥控信号选台集成电路IX0439CE 存储集成电路IX0442CE 微处理集成电路IX0464CE 图像、伴音中频放大集成电路IX0464CEZZ 图像中频放大集成电路IX0479GEZZ 计数控制集成电路IX0508CE 开关电源稳压集成电路IX0512 开关电源厚膜集成电路型号功能简述QBE 供电集成电路QS7785 环绕声解码集成电路QTT533 电源复位稳压集成电路RC4558DQ 枕形校正集成电路RCA4053 电子开关切换集成电路RCDRS52 红外遥控传感集成电路REF05/10 基准电源稳压集成电路RF9117E6 功率放大集成电路RF9118E6 功率放大集成电路RFF 射频输出集成电路RFIC17 功率放大900MHz集成电路RGB2932 倍速扫描处理集成电路RMC1201 红外遥控信号接收集成电路RN4906 基带选择控制集成电路RN5RZ20BA-TR 电源稳压+2V集成电路RSC6416GW 寻呼机信号控制集成电路RSC646B 音频信号放大集成电路S13120C 电源稳压集成电路S1854 电源取样误差集成电路S1855FA-3 均衡集成电路S1D2140B3 视频信号处理110MHz集成电路S1D2503X01 视频信号处理200MHz集成电路S1D2512X01 偏转信号处理集成电路S24C01AFJ-TB-01 存储集成电路S24C08A 存储集成电路S24CO 存储集成电路S2754 系统控制处理集成电路S5D2501F 屏幕显示处理集成电路S5D2508A 屏幕显示处理集成电路S5D2509E 屏幕显示处理集成电路S6708A 开关电源稳压集成电路S8051ANR 电源复位稳压集成电路S80741AL 电源复位检测集成电路S80741AL-2 电源复位检测集成电路S9801 彩灯控制集成电路S9802 彩灯控制集成电路S9805 彩灯控制4组八段集成电路S9808 彩灯控制4组集成电路SA2007A 主轴电机驱动集成电路SA9613 解调集成电路SA9870 解码集成电路SAA1250 红外遥控信号发射集成电路SAA1280 微处理集成电路SAA1290 微处理集成电路SAA1293 微处理集成电路SAA1300 调谐切换集成电路SAA1351 微处理集成电路SAA3007 红外遥控信号发射集成电路SAA3010T 红外遥控信号发射集成电路SAA3028 代码转换集成电路SAA4955TJ 存储集成电路SAA4956TJ 存储集成电路SAA4961 梳状滤波集成电路SAA4977H 视频信号处理集成电路SAA4981 压缩处理16∶9集成电路SAA4991WP 扫描转换集成电路SAA5243 电视信号处理集成电路SAA5246 电视信号处理集成电路SAA5246A 电视信号处理集成电路SAA5261 电视信号处理集成电路SAA5281ZP 电视信号处理集成电路SAA5284 电视信号处理集成电路SAA5290ZP 微处理集成电路SAA5297 微处理集成电路SAA5565PS 微处理集成电路SAA5700GP 色度解码集成电路74HCT4538D 单稳态集成电路74HCT4538N 触发脉冲集成电路74HCT86D 异或门四2输入集成电路74HCU04 与非门集成电路74LS125 端口功能扩展集成电路74LS373 锁存集成电路74LS393 计数双四位二进制集成电路74LS74双D 触发集成电路78014DFP 系统控制处理集成电路811N 伴音阻容偏置集成电路83D33 压控振荡集成电路87C52 微处理集成电路87CK38N-3584 微处理集成电路87CK38N-3627 微处理集成电路89C52 系统控制处理集成电路89C55 系统控制处理集成电路93C66 电可改写编程只读存储集成电路93LC56 电可改写编程存储集成电路9821K03 系统控制集成电路A1642P 背景歌声消除集成电路A701 红外遥控信号接收集成电路A7950 场频识别集成电路A8772AN 色差信号延迟处理集成电路A9109 功率放大集成电路AAB 电源集成电路ACA650 色度信号解调集成电路ACFP2 色度、亮度信号分离集成电路ACP2371 多伴音、多语言改善集成电路ACVP2205 色度、亮度信号分离集成电路AD1853 立体声数/模转换集成电路AD1858 音频解调集成电路AD722 视频编码集成电路ADC2300E 音频数/模转换集成电路ADC2300J 音频数/模转换集成电路ADC2310E 音频数/模转换集成电路ADV7172 视频编码集成电路ADV7175A 视频编码集成电路AE31201 频率显示集成电路AJ7080 射频调制集成电路AK4321-VF-E1 音频数/模转换集成电路AN1319 双高速电压比较集成电路AN1358S 双运算放大集成电路AN1393 双运算放大集成电路AN1431T 稳压电源集成电路AN1452 音频前置放大集成电路AN1458S 双运算放大集成电路AN206 伴音中频及前置放大集成电路AN222 自动频率控制集成电路AN236 副载波信号处理集成电路AN239Q 图像、伴音中频放大集成电路AN247P 图像中频放大、AGC控制集成电路AN253P 调频/调幅中频放大集成电路AN262 音频前置放大集成电路AN2661NK 视频信号处理集成电路AN2663K 视频信号处理集成电路AN272 音频功率放大集成电路AN2751FAP 视频信号处理集成电路AN281 色度解码集成电路AN2870FC 多功能控制集成电路AN295 行、场扫描信号处理集成电路AN301 伺服控制集成电路AN305 视频自动增益控制集成电路AN306 色度自动相位控制集成电路AN318 直流伺服控制集成电路AN320 频率控制、调谐显示驱动集成电路AN3215K 视频信号处理集成电路AN3215S 视频信号处理集成电路IX0579GE 微处理集成电路IX0580GD 单片语音录放集成电路IX0581GE 微处理集成电路IX0602CE 图像、伴音中频行场扫描信号处理集成电路IX0603CE 视频、色度信号处理集成电路IX0605CE 微处理集成电路IX0607CE 电子开关切换集成电路IX0614CE 红外遥控信号接收集成电路IX0640CE 场扫描输出集成电路IX0689CE 开关电源稳压集成电路IX0711CEN1 图像伴音中频放大集成电路IX0712CEN1 亮度、同步分离及行场扫描信号处理集成电路IX0715CE 存储集成电路IX0718CE 中频信号处理集成电路IX0733PA 红外遥控信号发射集成电路IX0736CE 图像中频放大集成电路IX0773CE 红外遥控信号发射集成电路IX0776CE 伴音混频集成电路IX0812CE 开关电源厚膜集成电路IX0823GE 微处理集成电路IX0875CE 开关电源厚膜集成电路IX0933CE 微处理集成电路IX0948CE 场扫描输出集成电路IX0969 色度、亮度信号处理集成电路IX0981CEN1 微处理集成电路IX0981GE 伺服控制接口集成电路IX1194CEN2 微处理集成电路IX1461GE 射频前置放大集成电路IX1463GE 误差信号发生集成电路IX1473GE 伺服控制集成电路IX1474GE 解码、纠错集成电路IX1504AF 状态控制集成电路IX1763CEN1 视频、色度及行场扫描信号处理集成电路IX1807CE 微处理集成电路IX2164CE 微处理集成电路IX2249AF 系统控制处理集成电路IX2287CE 存储集成电路IX2341AF 伺服控制集成电路IX2372CE 微处理集成电路IX2915CE 色度、亮度及行场扫描信号处理集成电路IX3081CE2 微处理集成电路IZ0052CE 字符信号处理集成电路IZ0055CE 音频控制集成电路IZ0068CE 视频缓冲放大集成电路JCE4501 数/模转换集成电路JLC1562BF 输入/输出扩展接口集成电路JQ5544H 电子石英闹钟集成电路JRC4555D 双运算放大集成电路JRC6308B 话筒信号放大集成电路JU0005 视频输出厚膜集成电路JU0006 音质改善集成电路JU0026 电源稳压厚膜集成电路JU0027 视频输出厚膜集成电路JU0114 开关电源稳压厚膜集成电路K2959M 图像中频滤波集成电路K5T8257B 存储集成电路K6259K 滤波集成电路K6265K 滤波集成电路K6283K 图像中频特性形成集成电路K9450M 伴音中频带通滤波集成电路KA2101 伴音中频放大、鉴频及前置放大集成电路KA2103L 伴音静噪集成电路KA2107 音频控制集成电路KA2131 场扫描输出集成电路KA2133 行、场扫描信号处理集成电路KA2134 行、场扫描信号处理集成电路SAA7121H 视频信号处理集成电路SAA7185 数/模转换集成电路SAA7280 音频解码集成电路SAA7282ZP/M3 音频解码集成电路SAA7283 丽音解码集成电路SAA7283ZP 丽音解码集成电路SAA7320 数/模转换集成电路SAA7327 数字信号处理集成电路SAA7345GP/85 数字信号处理集成电路SAA7372GP 数字信号处理集成电路SAA9042 多标准图文信号处理集成电路SAA9050 色度解码集成电路SAA9051 色度解码集成电路SAA9055 色度解码集成电路SAA9057A 时钟信号发生集成电路SAA9058 取样变换集成电路SAA9060 数/模转换集成电路SAA9068 画中画控制集成电路SAA9069 数字信号处理集成电路SAA9079 数/模转换集成电路SAA9860 音频信号处理集成电路SAB3013 扩展集成电路SAB3035 频率同步环路控制集成电路SAB9077H 画中画控制集成电路SAF1032P 红外接收译码与发射集成电路SAS560S 触摸开关集成电路SB7700ML 解码集成电路SB7800ML 解码集成电路SB7830ML 解码集成电路SBX1692-01 梳状滤波集成电路SBX1765 梳状滤波集成电路SBX1836-01 色度、亮度信号分离集成电路SBX1981-11 红外遥控信号接收集成电路SBX-F201A 中放组件集成电路SBX-M002A 选台组件集成电路SC424689FU 系统控制、显示驱动集成电路SC430402CFC 微处理集成电路SC440301FU 系统控制、显示驱动集成电路SC608 自动频率微调集成电路SDA5273S 色度解码集成电路SDA9086-2 画中画锁相环集成电路SDA9087-5 数/模转换集成电路SDA9087XGEG 数/模转换集成电路SDA9088-2 画中画信号处理集成电路SDA9089XGEG 画中画信号处理集成电路SDA9187-2X 数/模转换集成电路SDA9188/3X 画中画信号处理集成电路SDA9189 画中画信号处理集成电路SDA9189XGEGA132 画中画信号处理集成电路SDA9205 数/模转换集成电路SDA9220 存储集成电路SDA9251 存储集成电路SDA9257 时钟信号发生集成电路SDA9280 显示处理集成电路SDA9288X 画中画信号处理集成电路SDA9290 图像信号处理集成电路SDA9361 偏转控制集成电路SDA9400 偏转控制集成电路SE013E 电源取样误差集成电路SE090 电源取样误差集成电路SE105 电源取样误差集成电路SE110N 电源取样误差集成电路SE115N 电源取样误差集成电路SE116 电源取样误差集成电路SE117M 电源取样误差集成电路SE120 电源取样误差集成电路SE130 电源取样误差集成电路AN3224K 磁头信号记录放大集成电路AN3248NK 亮度信号记录、重放处理集成电路AN331 视频信号处理集成电路AN3311K 磁头信号放大集成电路AN3313 磁头信号放大集成电路AN3321S 录像重放信号处理集成电路AN3331K 磁头信号处理集成电路AN3337NSB 磁头信号放大集成电路AN3380K 磁头信号处理集成电路AN3386NK 磁头信号处理集成电路AN3495K 色度、亮度信号降噪集成电路AN355 伴音中频放大、检波集成电路AN3581S 视频驱动集成电路AN366 调频/调幅中频放大集成电路AN3791 移位控制集成电路AN3792 磁鼓伺服控制接口集成电路AN3795 主轴伺服控制接口集成电路AN3814K 电机驱动集成电路AN4265 音频功率放大集成电路AN4558 运算放大集成电路AN5010 电子选台集成电路AN5011 电子选台集成电路AN5015K 电子选台集成电路AN5020 红外遥控信号接收集成电路AN5025S 红外遥控信号接收集成电路AN5026K 红外遥控信号接收集成电路AN5031 电调谐控制集成电路AN5034 调谐控制集成电路AN5036 调谐控制集成电路AN5043 调谐控制集成电路AN5071 频段转换集成电路AN5095K 电视信号处理集成电路AN5110 图像中频放大集成电路AN5130 图像中频、视频检波放大集成电路AN5138NK 图像、伴音中频放大集成电路AN5156K 电视信号处理集成电路AN5177NK 图像、伴音中频放大集成电路AN5179K 图像、伴音中频放大集成电路AN5183K 中频信号处理集成电路AN5195K 中频、色度、扫描信号处理集成电路AN5215 伴音信号处理集成电路AN5222 伴音中频放大集成电路AN5250 伴音中频放大、鉴频及功率放大集成电路AN5262 音频前置放大集成电路AN5265 音频功率放大集成电路AN5270 音频功率放大集成电路AN5273 双声道音频功率放大集成电路AN5274 双声道音频功率放大集成电路AN5275 中置、3D放大集成电路AN5285K 双声道前置放大集成电路AN5295NK 音频信号切换集成电路AN5312 视频、色度信号处理集成电路AN5313NK 视频、色度信号处理集成电路AN5342 图像水平轮廓校正集成电路AN5342FB 水平清晰度控制集成电路AN5344FBP 色度信号处理集成电路AN5348K 人工智能信号处理集成电路AN5385K 色差信号放大集成电路AN5410 行、场扫描信号处理集成电路AN5421 同步检测集成电路AN5422 行、场扫描信号处理集成电路AN5512 场扫描输出集成电路AN5515 场扫描输出集成电路AN5520 伴音中频放大及鉴频集成电路AN5521 场扫描输出集成电路AN5532 场扫描输出集成电路AN5534 场扫描输出集成电路KA2140B 视频信号放大130MHz 集成电路KA2141 视频信号放大85MHz集成电路KA2143B 视频信号处理110MHz集成电路KA2182 红外遥控信号接收集成电路KA2192B 切换开关集成电路KA2194D 视频编码集成电路KA2198BD 视频编码集成电路KA2202 伴音中频放大、鉴频及功率放大集成电路KA2203 音频功率放大1.2W集成电路KA2204 音频功率放大6W集成电路KA2206B 双声道音频功率放大集成电路KA2209 双声道功率放大集成电路KA2211 双声道音频功率放大集成电路KA2213 单片录、放音集成电路KA22131 双声道前置放大集成电路KA22233 双声道三段显示均衡集成电路KA2241B 双声道均衡放大集成电路KA22421 调幅接收集成电路KA22429 调频接收集成电路KA2243 调频/调幅中频放大集成电路KA2244 调频中频放大集成电路KA2248 调幅/调谐及中频放大集成电路KA22686 伴音信号处理集成电路KA2418 铃声放大集成电路KA2500 视频信号放大集成电路KA2504 视频信号放大85MHz集成电路KA2507 电子开关切换集成电路KA2913A 图像、伴音中频放大集成电路KA2915 图像、伴音中频放大集成电路KA2918D 视频编码集成电路KA2919 图像、伴音中频放大集成电路KA2922 图像、伴音中频放大集成电路KA2924 图像、伴音中频放大集成电路KA2S0680 电源厚膜集成电路KA331 频率转换集成电路KA3524 脉宽调制集成电路KA3882 开关电源控制集成电路KA7226 双声道均衡放大集成电路KA7630 开关电源控制集成电路KA8302 伺服控制集成电路KA8309B 伺服控制集成电路KA8310 电机驱动集成电路KA8330 电机驱动集成电路KA9201Q 伺服控制集成电路KA9220 伺服控制集成电路KA9258D 伺服驱动集成电路KA9259 伺服驱动集成电路KAIDA8803 微处理集成电路KB2502 视频信号放大集成电路KB2511B 偏转信号处理集成电路KB9223 伺服控制集成电路KC581C 场扫描输出集成电路KC582C 开关电源稳压集成电路KCM201 微处理集成电路KD12D 报警集成电路KD167 音乐发光集成电路KD8801 微处理集成电路KD9217 存储集成电路KD9300 音乐模拟集成电路KD9626A 微处理集成电路KDA0316LN 数/模转换集成电路KIA324P 四运算放大集成电路KIA4558 双运算放大集成电路KIA6003 调频中频放大集成电路KIA6043S 立体声解码集成电路KIA6280H 双声道音频功率放大集成电路KIA9127F 调频/调幅收音集成电路SE135N 电源取样误差集成电路SE139N 电源取样误差集成电路SE140 电源取样误差集成电路SECL810 音频信号控制集成电路SF1166 行扫描信号处理集成电路SF1205 调频/调幅中频放大集成电路SF214 音频功率放大集成电路SF357 运算放大集成电路SF404 音频功率放大集成电路SF810 音频功率放大集成电路SFH615A-3 光电耦合集成电路SG3524 开关电源稳压集成电路SG3525A 开关电源稳压集成电路SKP1103S 微处理集成电路SKW01-829A2202 微处理集成电路SL1274 数码显示驱动集成电路SL315 调频/调谐及中频放大集成电路SL322 发光二极管显示驱动集成电路SL33 音频功率放大集成电路SL345 音频功率放大集成电路SL349 音频功率放大集成电路SL36 双声道音频功率放大集成电路SM5840CS 数字滤波集成电路SM5856AIF 防震控制集成电路SM5871A 数/模转换集成电路SM5875BM 数/模转换集成电路SM5876AM 数/模转换集成电路SMM201N 微处理集成电路SMR62000 开关电源厚膜集成电路SN103832APG 选择转换集成电路SN74HC138ANS 地址解码集成电路SN74HC377 八D触发集成电路SN74HCU04 时钟信号发生集成电路SN74LS221N 行线性校正集成电路SN76003ND 场扫描输出集成电路SN76013 场扫描输出集成电路SN76298N 色度信号放大、振荡集成电路SN94096N 频道选择集成电路SNY425 数/模转换集成电路SP928 射频电源及充电控制集成电路SPS410-1 红外遥控信号接收集成电路SPS415-1 红外遥控信号接收集成电路SPU2220 色度信号处理集成电路SRM6116 存储集成电路SRS5250S 音频信号处理集成电路SS133P3720 伺服处理集成电路SSA9058 取样交换集成电路SSHK315-03 数据处理集成电路SSM2250 音频功率放大集成电路ST13400 解码集成电路ST24C01B1 节目存储集成电路ST24C02 存储集成电路ST275 微处理集成电路ST63156 微处理集成电路ST6356B1 微处理集成电路ST6367B1/FCB 微处理集成电路ST6368 微处理集成电路ST6369 微处理集成电路ST6371 微处理集成电路ST6378B4 微处理集成电路ST7272N5B1 微处理集成电路ST80000D 电源控制集成电路ST92196 微处理集成电路ST9291 微处理集成电路STA441C 场扫描输出厚膜集成电路STA8012 开关电源稳压集成电路STC6311 键控操作及显示驱动集成电路AN5551 枕形校正集成电路AN5560 场频识别集成电路AN5600K 中频、亮度、色度及扫描信号处理集成电路AN5601K 视频、色度、同步信号处理集成电路AN5607K 视频、色度、行场扫描信号处理集成电路AN5615 视频信号处理集成电路AN5620X 色度信号处理集成电路AN5621 场扫描输出集成电路AN5625 色度信号处理集成电路AN5633K 色度信号处理集成电路AN5635 色度解码集成电路AN5635NS 色度解码集成电路AN5637 色度解码、亮度延迟集成电路AN5650 同步信号分离集成电路AN5682K 基色电子开关切换集成电路AN5693K 视频、色度、行场扫描信号处理集成电路AN5712 图像中频放大、AGC控制集成电路AN5722 图像中频放大、检波集成电路AN5732 伴音中频放大、鉴频集成电路AN5743 音频功率放大集成电路AN5750 行自动频率控制及振荡集成电路AN5757S 行扫描电源电压控制集成电路AN5762 场扫描振荡、输出集成电路AN5764 光栅水平位置控制集成电路AN5765 电源稳压控制集成电路AN5767 同步信号处理集成电路AN5768 光栅倾斜校正控制集成电路AN5769 行、场会聚控制集成电路AN5790N 行扫描信号处理集成电路AN5791 同步脉冲相位与脉宽调整集成电路AN5803 双声道立体声解调集成电路AN5836 双声道前置放大集成电路AN5858K 视频信号控制集成电路AN5862 视频信号控制集成电路AN5862S-E1 视频信号开关控制集成电路AN5870K 模拟信号切换集成电路AN5891K 音频信号处理集成电路AN614 行枕形校正集成电路AN6210 双声道前置放大集成电路AN6306S 亮度信号处理集成电路AN6308 模拟电子开关集成电路AN6327 视频重放信号处理集成电路AN6341N 伺服控制集成电路AN6342N 基准分频集成电路AN6344 伺服控制集成电路AN6345 分频集成电路AN6346N 磁鼓伺服控制集成电路AN6350 磁鼓伺服控制集成电路AN6357N 主轴接口集成电路AN6361N 色度信号处理集成电路AN6367NK 色度信号处理集成电路AN6371S 自动相位控制集成电路AN6387 电机伺服控制集成电路AN6550 卡拉OK音频放大集成电路AN6554 四运算放大集成电路AN6561 双运算放大集成电路AN6562SG 双运算放大集成电路AN6609N 电机驱动集成电路AN6612 电机稳速控制集成电路AN6650 电机速度控制集成电路AN6651 电机速度控制集成电路AN6875 发光二极管五位显示驱动集成电路AN6877 发光二极管七位显示驱动集成电路AN6884 发光二极管五位显示驱动集成电路AN6886 发光二极管五位显示驱动集成电路AN6888 发光二极管显示驱动集成电路KM3509F 主轴电机驱动集成电路KM416C256BLJ-7 动态随机存储集成电路KM44C1000B 语音存储集成电路KM68FS1000TGI-12 存储集成电路KON266 微处理集成电路KS5308 微处理集成电路KS56C820-69A 系统控制处理集成电路KS57C2304 微处理集成电路KS5822 双音频、脉冲拨号集成电路KS5990B 数字信号处理集成电路KS88C0016 系统控制处理集成电路KS88C8424-13 微处理集成电路KS9211B 数字信号处理集成电路KS9241 电可改写编程只读存储集成电路KS9282B 数字信号处理集成电路KS9283 数字信号处理集成电路KS9284 数字信号处理集成电路KT8554N 编码、解码集成电路KY88C93 微处理集成电路KY88C94 微处理集成电路L296 开关电源调整集成电路L4960 开关电源稳压集成电路L4962 开关电源稳压集成电路L4970A 开关电源稳压集成电路L4990 开关电源稳压集成电路L64020 视频、音频解码集成电路L7106 模/数转换31/2位集成电路L7129 数/模转换41/2位集成电路L7660 电压转换集成电路L78LR05 复位电源稳压+5V集成电路L78MR05 复位电源稳压+5V集成电路L78VR05 复位电源稳压+5V集成电路LA1111P 音频放大集成电路LA1132 调幅/调谐及中频放大集成电路LA1135 调幅收音集成电路LA1150N 伴音信号检测集成电路LA1178M 调频前置放大集成电路LA1210 调频/调幅中频放大集成电路LA1231N 调频中频放大集成电路LA1240 调幅调谐集成电路LA1245 调幅调谐集成电路LA1260 调频/调幅中频放大集成电路LA1265 调频/调幅中频放大集成电路LA1267S 调频/调幅中频放大集成电路LA1357N 图像中频放大、检波、视频放大集成电路LA1362 音频信号处理集成电路LA1368 色度信号处理集成电路LA1387 行、场扫描信号处理集成电路LA1460 行、场扫描信号处理集成电路LA1816 单片收音集成电路LA1835 调频/调幅中频放大集成电路LA2000 自动选曲集成电路LA2110 调频噪声抑制集成电路LA2600 双声道电子音量控制集成电路LA2746 杜比降噪集成电路LA2785 音频解码集成电路LA3160 双声道均衡放大集成电路LA3220 双声道前置放大集成电路LA3225T 双声道前置放大集成电路LA3301 调频立体声解码集成电路LA3361 调频立体声解码集成电路LA3370 调频立体声解码集成电路LA3410 调频立体声解码集成电路LA3430 调频立体声解码集成电路LA3600 音调补偿五段集成电路LA4030P 音频功率放大集成电路STK2250 双声道音频功率放大集成电路STK392-110 会聚校正放大集成电路STK4028V 音频功率放大30W集成电路STK4036V 音频功率放大50W集成电路STK4038XI 音频功率放大60W集成电路STK4151 双声道音频功率放大集成电路STK4171-2S 音频功率放大集成电路STK4191 双声道音频功率放大50W集成电路STK420 音频功率放大集成电路STK4231 双声道音频功率放大100W×2集成电路STK4274 音频功率放大集成电路STK430 双声道音频功率放大集成电路STK433-105 双声道音频功率放大集成电路STK4352 双声道音频功率放大7W×2集成电路STK436A 双声道音频功率放大集成电路STK437 双声道音频功率放大集成电路STK4833 双声道音频功率放大25W×2集成电路。

74HC04数据手册

Hex inverter

FEATURES • Complies with JEDEC standard no. 8-1A • ESD protection: HBM EIA/JESD22-A114-A exceeds 2000 V MM EIA/JESD22-A115-A exceeds 200 V. • Specified from −40 to +85 °C and −40 to +125 °C. QUICK REFERENCE DATA GND = 0 V; Tamb = 25 °C; tr = tf ≤ 6.0 ns. DESCRIPTION

2003 Jul 23

5

Philips Semiconductors

Product specification

Hex inverter

DC CHARACTERISTICS Type 74HC04 At recommended operating conditions; voltages are referenced to GND (ground = 0 V). TEST CONDITIONS SYMBOL Tamb = 25 °C VIH HIGH-level input voltage 2.0 4.5 6.0 VIL LOW-level input voltage 2.0 4.5 6.0 VOH HIGH-level output voltage VI = VIH or VIL IO = −20 µA IO = −20 µA IO = −4.0 mA IO = −20 µA IO = −5.2 mA VOL LOW-level output voltage VI = VIH or VIL IO = 20 µA IO = 20 µA IO = 4.0 mA IO = 20 µA IO = 5.2 mA ILI IOZ ICC input leakage current VI = VCC or GND 3-state output OFF current VI = VIH or VIL; VO = VCC or GND quiescent supply current 2.0 4.5 4.5 6.0 6.0 6.0 6.0 − − − − − − − − 2.0 4.5 4.5 6.0 6.0 1.9 4.4 3.98 5.9 5.48 1.5 3.15 4.2 − − − PARAMETER OTHER VCC (V) MIN.

74系列芯片标准数字电路资料

74系列芯片标准数字电路资料-功能大全一.74系列芯片标准数字电路资料-功能大全二。

74系列芯片资料三.74HC/LS/HCT/F系列芯片的区别四.逻辑电平介绍TTL,CMOS五.74HC244与245作用与区别六.74芯片分类总汇一.74系列芯片标准数字电路资料-功能大全7400 TTL 2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器74645 TTL 三态输出八同相总线传送接收器74670 TTL 三态输出4×4寄存器堆7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双D触发器7476 TTL 带预置清除双J-K触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\\输出移位寄存器7497 TTL 6位同步二进制乘法器二。

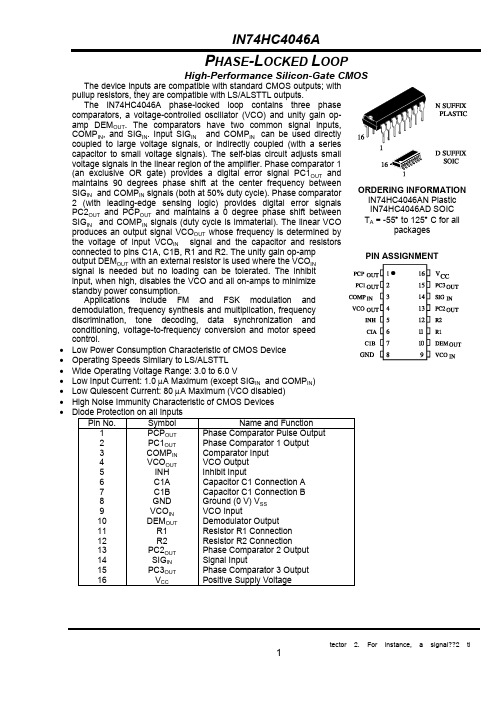

IN74HC4046A资料

PHASE-LOCKED LOOP

High-Performance Silicon-Gate CMOS

The device inputs are compatible with standard CMOS outputs; with pullup resistors, they are compatible with LS/ALSTTL outputs. The IN74HC4046A phase-locked loop contains three phase comparators, a voltage-controlled oscillator (VCO) and unity gain opamp DEMOUT. The comparators have two common signal inputs, COMPIN, and SIGIN. Input SIGIN and COMPIN can be used directly coupled to large voltage signals, or indirectly coupled (with a series capacitor to small voltage signals). The self-bias circuit adjusts small voltage signals in the linear region of the amplifier. Phase comparator 1 (an exclusive OR gate) provides a digital error signal PC1OUT and maintains 90 degrees phase shift at the center frequency between SIGIN and COMPIN signals (both at 50% duty cycle). Phase comparator 2 (with leading-edge sensing logic) provides digital error signals PC2OUT and PCPOUT and maintains a 0 degree phase shift between SIGIN and COMPIN signals (duty cycle is immaterial). The linear VCO produces an output signal VCOOUT whose frequency is determined by the voltage of input VCOIN signal and the capacitor and resistors connected to pins C1A, C1B, R1 and R2. The unity gain op-amp output DEMOUT with an external resistor is used where the VCOIN signal is needed but no loading can be tolerated. The inhibit input, when high, disables the VCO and all on-amps to minimize standby power consumption. Applications include FM and FSK modulation and demodulation, frequency synthesis and multiplication, frequency discrimination, tone decoding, data synchronization and conditioning, voltage-to-frequency conversion and motor speed control. Low Power Consumption Characteristic of CMOS Device Operating Speeds Similary to LS/ALSTTL Wide Operating Voltage Range: 3.0 to 6.0 V Low Input Current: 1.0 µA Maximum (except SIGIN and COMPIN) Low Quiescent Current: 80 µA Maximum (VCO disabled) High Noise Immunity Characteristic of CMOS Devices Diode Protection on all Inputs Pin No. Symbol Name and Function 1 PCPOUT Phase Comparator Pulse Output 2 PC1OUT Phase Comparator 1 Output 3 COMPIN Comparator Input 4 VCOOUT VCO Output 5 INH Inhibit Input 6 C1A Capacitor C1 Connection A 7 C1B Capacitor C1 Connection B 8 GND Ground (0 V) VSS 9 VCOIN VCO Input 10 DEMOUT Demodulator Output 11 R1 Resistor R1 Connection 12 R2 Resistor R2 Connection 13 PC2OUT Phase Comparator 2 Output 14 SIGIN Signal Input 15 PC3OUT Phase Comparator 3 Output 16 VCC Positive Supply Voltage

基于74HC4046新型频率跟踪电路的研究_车保川

74HC4046 的内部结构如图 4 所示, 他是由一 个 V CO 和 3 种鉴相器构成, 只要在外部增设 分频器和环 路滤波器 R 和 C, 就可以构成 PLL 频率合成 器。3 种 鉴相器 的工作 原理各不相同, 其中鉴相 器 PC1 是 异或 门鉴相 器, PC2 是 边沿触发器, PC3 是一 个 R, S 触发器门, 其输 出端分 别为 2, 13, 15。在 3 种鉴相器中, 最常用的是 PC2, PC1 和 PC3 鉴相器不能进行频率比 较, 锁相范 围较窄, 而 PC2 可 以进 行频率比较, 在 VCO 振荡 频率 的 全部 范 围内 进 行锁 相。 根据 74H C4046 的工作频率范围选择 外围电容、电 阻的参 数, 即 R 1 , R 2 和 C1 。电阻 R 1 和 C1 共同决定 振荡器的中心 频率。R2 可以改变压控振荡器的 自由振荡 频率并 改变振 荡器的频率控制范围。

目前常用的频率跟踪方法有: 人 工调节频率、声跟踪、 电跟踪和锁相式频 率自动 跟踪。前 三种实 现方 法都比 较 简单, 但他 们各自有 明显的 缺点: 人工 调节频 率不能实 现 实时跟踪, 频率的调 节需要 人工干预; 电跟踪 和声跟踪 都 是采用反馈的方式来实现频率跟踪, 反 馈信号的强度 很难 控制, 常会因换能器参数的变化而变 化。使用锁相环 的频

74VHC4046中文资料

74VHC4046中文资料TL F 1167574VHC4046CMOS Phase Lock LoopOctober 199574VHC4046CMOS Phase Lock LoopGeneral DescriptionThe 74VHC4046is a low power phase lock loop utilizing advanced silicon-gate CMOS technology to obtain high fre-quency operation both in the phase comparator and VCO sections This device contains a low power linear voltage controlled oscillator (VCO) a source follower and three phase comparators The three phase comparators have a common signal input and a common comparator input The signal input has a self biasing amplifier allowing signals to be either capacitively coupled to the phase comparators with a small signal or directly coupled with standard input logic levels This device is similar to the CD4046except that the Zener diode of the metal gate CMOS device has been replaced with a third phase comparatorPhase Comparator I is an exclusive OR (XOR)gate It pro-vides a digital error signal that maintains a 90phase shift between the VCO’s center frequency and the input signal (50%duty cycle input waveforms) This phase detector is more susceptible to locking onto harmonics of the input fre-quency than phase comparator I but provides better noise rejectionPhase comparator III is an SR flip-flop gate It can be used toprovide the phase comparator functions and is similar to the first comparator in performancePhase comparator II is an edge sensitive digital sequential network Two signal outputs are provided a comparator out-put and a phase pulse output The comparator output is a TRI-STATE output that provides a signal that locks the VCO output signal to the input signal with 0phase shift be-tween them This comparator is more susceptible to noise throwing the loop out of lock but is less likely to lock onto harmonics than the other two comparatorsIn a typical application any one of the three comparators feed an external filter network which in turn feeds the VCO input This input is a very high impedance CMOS input which also drives the source follower The VCO’s operating frequency is set by three external components connected to the C1A C1B R1and R2pins An inhibit pin is provided to disable the VCO and the source follower providing a meth-od of putting the IC in a low power stateThe source follower is a MOS transistor whose gate is con-nected to the VCO input and whose drain connects the De-modulator output This output normally is used by tying a resistor from pin 10to ground and provides a means of looking at the VCO input without loading down modifying the characteristics of the PLL filterFeaturesY Low dynamic power consumption (V CC e 4 5V)YMaximum VCO operating frequency 12MHz (V CC e 4 5V)YFast comparator response time (V CC e 4 5V)Comparator I 25ns Comparator II 30ns Comparator III 25ns Y VCO has highlinearity and high temperature stability YPin and function compatible with the 74HC4046Commercial Package Package Description Number 74VHC4046M M16A 16-Lead Molded JEDEC SOIC 74VHC4046N N16E16-Lead Molded DIPNote Surface mount packages are also available on Tape and Reel Specify by appending the suffix letter ‘‘X’’to the ordering codeTRI-STATE is a registered trademark of National Semiconductor Corporation C 1995National Semiconductor CorporationRRD-B30M125 Printed in U S ABlock and Connection DiagramsTL F 11675–1Pin Assignment forSOIC and PDIPTL F 11675–22Absolute Maximum Ratings(Notes1 2) Supply Voltage(V CC)b0 5to a7 0V DC Input Voltage(V IN)b1 5to V CC a1 5V DC Output Voltage(V OUT)b0 5to V CC a0 5V Clamp Diode Current(I IK I OK)g20mA DC Output Current per pin(I OUT)g25mA DC V CC or GND Current per pin(I CC)g50mA Storage Temperature Range(T STG)b65 C a150 C Power Dissipation(P D)(Note3)600mW S O Package only500mW Lead Temperature(T L)(Soldering10seconds)260 C Operating ConditionsMin Max Units Supply Voltage(V CC)26V DC Input or Output Voltage0V CC V (V IN V OUT)Operating Temp Range(T A)74VHC b40a85 C Input Rise or Fall Times(t r t f)V CC e2 0V1000ns V CC e4 5V500nsV CC e6 0V400nsDC Electrical Characteristics(Note4)T A e25 C 74VHCSymbol Parameter Conditions V CC T A eb40to85 C UnitsTyp Guaranteed LimitsV IH Minimum High Level Input2 0V1 51 5V Voltage4 5V3 153 15V6 0V4 24 2V V IL Maximum Low Level Input2 0V0 50 5V Voltage4 5V1 351 35V6 0V1 81 8V V OH Minimum High Level Output V IN e V IH or V ILVoltage l I OUT l s20m A2 0V2 01 91 9V4 5V4 54 44 4V6 0V6 05 95 9VV IN e V IH or V ILl I OUT l s4 0mA4 5V4 23 983 84Vl I OUT l s5 2mA6 0V5 75 485 34V V OL Maximum Low Level Output V IN e V IH or V ILVoltage l I OUT l s20m A2 0V00 10 1V4 5V00 10 1V6 0V00 10 1VV IN e V IH or V ILl I OUT l s4 0mA4 5V0 20 260 33Vl I OUT l s5 2mA6 0V0 20 260 33V I IN Maximum Input Current(Pins3 5 9)V IN e V CC or GND6 0V g0 1g1 0m A I IN Maximum Input Current(Pin14)V IN e V CC or GND6 0V205080m A I OZ Maximum TRI-STATE Output V OUT e V CC or GND6 0V g0 25g2 5m ALeakage Current(Pin13)I CC Maximum Quiescent Supply V IN e V CC or GND6 0V304065m ACurrent I OUT e0m AV IN e V CC or GND6 0V6007501200m APin14OpenNote1 Maximum Ratings are those values beyond which damage to the device may occurNote2 Unless otherwise specified all voltages are referenced to groundNote3 Power Dissipation temperature derating plastic‘‘N’’package b12mW C from65 C to85 CNote4 For a power supply of5V g10%the worst case output voltages(V OH and V OL)occur for VHC at4 5V Thus the4 5V values should be used when designing with this supply Worst case V IH and V IL occur at V CC e5 5V and4 5V respectively (The V IH value at5 5V is3 85V )The worst case leakage current(I IN I CC and I OZ)occur for CMOS at the higher voltage and so the6 0V values should be used3AC Electrical Characteristics V CC e2 0to6 0V CL e50pF t r e t f e6ns(unless otherwise specified )Symbol Parameters Conditions V CCT e25C74VHCUnits Typ Guaranteed LimitsAC Coupled C(series)e100pF2 0V25100150mVInput Sensitiv-f IN e500kHz4 5V50150200mVity Signal In6 0V135250300mV t r t f Maximum Output2 0V307595ns Rise and Fall4 5V91519nsTime6 0V81215ns C IN Maximum Input7pFCapacitancePhase Comparator It PHL t PLH Maximum Prop-3 3V65117146ns agation Delay4 5V254050ns6 0V203443ns Phase Comparator IIt PZL Maximum TRI-3 3V75130160ns STATE Enable4 5V254556nsTime6 0V223848ns t PZH t PHZ Maximum TRI-3 3V88140175ns STATE Enable4 5V304860nsTime6 0V254151ns t PLZ Maximum TRI-3 3V90140175ns STATE Disable4 5V324860nsTime6 0V284151ns t PHL t PLH Maximum Prop-3 3V100146180ns agation Delay4 5V345063nsHigh to Low6 0V274353nsto Phase PulsesPhase Comparator IIIt PHL t PLH Maximum Prop-3 3V75117146ns agation Delay4 5V254050ns6 0V223443nsC PD Maximum Power All Comparators130pFDissipation V IN e V CC and GNDCapacitanceVoltage Controlled Oscillator(Specified to operate from V CC e3 0V to6 0V)f MAX Maximum C1e50pFOperating R1e100X4 5V74 5MHzFrequency R2e%6 0V117MHzVCO in e V CCC1e0pF4 5V12MHzR1e100X6 014MHzVCO in e V CCDuty Cycle50% Demodulator OutputOffset Voltage R s e20k X4 5V0 751 31 5VVCO in–V demOffset R s e20k X4 5VVariation VCO in e1 75V0 65V2 25V0 12 75V0 754Typical Performance CharacteristicsTypical Center Frequencyvs R1 C1V CC e4 5VTL F 11675–3Typical Center Frequencyvs R1 C1V CC e6VTL F 11675–4Typical Offset Frequencyvs R2 C1V CC e4 5VTL F 11675–5Typical Offset Frequencyvs R2 C1V CC e6VTL F 11675–6 5Typical Performance Characteristics(Continued) VHC4046Typical VCO Power Dissipation Center Frequency vs R1TL F 11675–7VHC4046Typical VCO Power Dissipation f min vs R2TL F 11675–8VHC4046VCO in vs f out V CC e4 5VTL F 11675–9VHC4046VCO in vs f out V CC e4 5VTL F 11675–10VHC4046VCO out vsTemperature V CC e4 5VTL F 11675–11VHC4046VCO out vsTemperature V CC e6VTL F 11675–12 6Typical Performance Characteristics(Continued)VHC4046Typical Source Follower Power Dissipation vs RSTL F 11675–13Typical f max f min vs R2 R1V CC e 4 5V 6V f max f minTL F 11675–14VHC4046Typical VCO Linearity vs R1 C1TL F 11675–15VHC4046Typical VCO Linearity vs R1 C1TL F 11675–16VCO WITHOUT OFFSETR2e %VCO WITH OFFSET(a)TL F 11675–17FIGURE 17Comparator I Comparator II III R2e%R2i%R2e%R2i%–Given f0–Given f0and f L–Given f max–Given f min and f max –Use f0with curve titled–Calculate f min from the–Calculate f0from the–Use f min with curve titled center frequency vs R1 C equation f min e f o b f L equation f o e f max 2offset frequencyvs R2to determine R1and C1–Use f min with curve titled–Use f0with curve titled C to determine R2and C1offset frequency vs R2 C center frequency vs R1 C–Calculate f max f minto determine R2and C1to determine R1and C1–Use f max f min with curve–Calculate f max f min from titled f max f min vs R2 R1the equation f max f min e to determine ratio R2 R1f o a f L f o b f L to obtain R1–Use f max f min with curvetitled f max f min vs R2 R1to determine ratio R2 R1to obtain R1(b)FIGURE1(Continued)Detailed Circuit DescriptionVOLTAGE CONTROLLED OSCILLATOR SOURCEFOLLOWERThe VCO requires two or three external components to op-erate These are R1 R2 C1 Resistor R1and capacitor C1 are selected to determine the center frequency of the VCO R1controls the lock range As R1’s resistance decreases the range of f min to f max increases Thus the VCO’s gain decreases As C1is changed the offset(if used)of R2 and the center frequency is changed (See typical performance curves)R2can be used to set the offset frequency with0V at VCO input If R2is omitted the VCO range is from0Hz As R2is decreased the offset frequency is increased The ef-fect of R2is shown in the design information table and typi-cal performance curves By increasing the value of R2the lock rangeof the PLL is offset above0Hz and the gain (Volts rad )does not change In general when offset is de-sired R2and C1should be chosen first and then R1should be chosen to obtain the proper center frequency Internally the resistors set a current in a current mirror as shown in Figure1 The mirrored current drives one side ofTL F 11675–18FIGURE2 Logic Diagram for VCO8Detailed Circuit Description (Continued)the capacitor once the capacitor charges up to the thresh-old of the schmitt trigger the oscillator logic flips the capaci-tor over and causes the mirror to charge the opposite side of the capacitor The output from the internal logic is then taken to pin4The input to the VCO is a very high impedance CMOS input and so it will not load down the loop filter easing the filters design In order to make signals at the VCO input accessible without degrading the loop performance a source follower transistor is provided This transistor can be used by con-necting a resistor to ground and its drain output will follow the VCO input signalAn inhibit signal is provided to allow disabling of the VCO and the source follower This is useful if the internal VCO is not being used A logic high on inhibit disables the VCO and source followerThe output of the VCO is a standard high speed CMOS output with an equivalent LSTTL fanout of 10 The VCO output is approximately a square wave This output can ei-ther directly feed the comparator input of the phase compar-ators or feed external prescalers (counters)to enable fre-quency synthesis PHASE COMPARATORSAll three phase comparators share two inputs Signal In and Comparator In The Signal In has a special DC bias network that enables AC coupling of input signals If the signals are not AC coupled then this input requires logic levels the same as standard 74VHC The Comparator input is a stan-dard digital input Both input structures are shown in Figure 3The outputs of these comparators are essentially standard 74VHC voltage outputs (Comparator II is TRI-STATE )TL F 11675-19FIGURE 3 Logic Diagram for Phase Comparator I and the Common Input Circuit for All Three ComparatorsTL F 11675–20FIGURE 4 Typical Phase Comparator I Waveforms9Detailed Circuit Description(Continued)Thus in normal operation V CC and ground voltage levels are fed to the loop filter This differs from some phase detectors which supply a current output to the loop filter and this should be considered in the design (The CD4046also pro-vides a voltage ) Figure5shows the state tables for all three comparators PHASE COMPARATOR IThis comparator is a simple XOR gate similar to the 54 74HC86 and its operation is similar to an overdriven balanced modulator To maximize lock range the input fre-quencies musthave a50%duty cycle Typical input and output waveforms are shown in Figure4 The output of the phase detector feeds the loop filter which averages the out-put voltage The frequency range upon which the PLL will lock onto if initially out of lock is defined as the capture range The capture range for phase detector I is dependent on the loop filter employed The capture range can be as large as the lock range which is equal to the VCO frequency rangeTo see how the detector operates refer to Figure4 When two square wave inputs are applied to this comparator an output waveform whose duty cycle is dependent on the phase difference between the two signals results As the phase difference increases the output duty cycle increases and the voltage after the loop filter increases Thus in order to achieve lock when the PLL input frequency increases the VCO input voltage must increase and the phase difference between comparator in and signal in will increase At an input frequency equal f min the VCO input is at0V and this requires the phase detector output to be ground hence the two input signals must be in phase When the input frequen-cy is f max then the VCO input must be V CC and the phase detector inputs must be180 out of phaseThe XOR is more susceptible to locking onto harmonics of the signal input than the digital phase detector II This can be seen by noticing that a signal2times the VCO frequency results in the same output duty cycle as a signal equal the VCO frequency The difference is that the output frequency of the2f example is twice that of the other example The loop filter and the VCO range should be designed to prevent locking on to harmonics PHASE COMPARATOR IIThis detector is a digital memory network It consists of fourflip-flops and some gating logic a three state output and a phase pulse output as shown in Figure6 This comparator acts only on the positive edges of the input signals and is thus independent of signal duty cyclePhase comparator II operates in such a way as to force the PLL into lock with0phase difference between the VCO output and the signal input positive waveform edges Figure 7shows some typical loop waveforms First assume that the signal input phase is leading the comparator input ThisPhase Comparator State DiagramsTL F 11675–21FIGURE5 PLL State Tables10Detailed Circuit Description(Continued)TL F 11675–22FIGURE6 Logic Diagram for Phase Comparator IITL F 11675–23FIGURE7 Typical Phase Comparator II Output Waveforms11Detailed Circuit Description (Continued)means that the VCO’s frequency must be increased to bring its leading edge into proper phase alignment Thus the phase detector II output is set high This will cause the loop filter to charge up the VCO input increasing the VCO fre-quency Once the leading edge of the comparator input is detected the output goes TRI-STATE holding the VCO input at the loop filter voltage If the VCO still lags the signal then the phase detector will again charge up to VCO input for the time between the leading edges of both waveformsIf the VCO leads the signal then when the leading edge of the VCO is seen the output of the phase comparator goes low This discharges the loop filter until the leading edge of the signal is detected at which time the output TRI-STATE itself again This has the effect of slowing down the VCO to again make the rising edges of both waveform coincident When the PLL is out of lock the VCO will be running either slower or faster than the signal input If it is running slower the phase detector will see more signal rising edges and so the output of the phase comparator will be high a majority of the time raising the VCO’s frequency Conversely if the VCO is running faster than the signal the output of the de-tector will be low most of the time and the VCO’s output frequency will be decreasedAs one can see when the PLL is locked the output of phase comparator II will be almost always TRI-STATE except for minor corrections at the leading edge of the waveforms When the detector is TRI-STATE the phase pulse output is high This outputcan be used to determine when the PLL is in the locked condition This detector has several interesting characteristics Over the entire VCO frequency range there is no phase differ-ence between the comparator input and the signal input The lock range of the PLL is the same as the capture rangeMinimal power is consumed in the loop filter since in lock the detector output is a high impedance Also when no sig-nal is present the detector will see only VCO leading edges and so the comparator output will stay low forcing the VCO to f min operating frequencyPhase comparator II is more susceptible to noise causing the phase lock loop to unlock If a noise pulse is seen on the signal input the comparator treats it as another positive edge of the signal and will cause the output to go high until the VCO leading edge is seen potentially for a whole signal input period This would cause the VCO to speed up during that time When using the phase comparator I the output of that phase detector would be disturbed for only the short duration of the noise spike and would cause less upset PHASE COMPARATOR IIIThis comparator is a simple S-R Flip-Flop which can func-tion as a phase comparator Figure 8 It has some similar characteristics to the edge sensitive comparator To see how this detector works assume input pulses are applied to the signal and comparator inputs as shown in Figure 9 When the signal input leads the comparator input the flop is set This will charge up the loop filter and cause the VCO to speed up bringing the comparator into phase with the sig-nal input When using short pulses as input this comparator behaves very similar to the second comparator But one can see that if the signal input is a long pulse the output of the comparator will be forced to a one no matter how manycomparator input pulses are received Also if the VCO input is a square wave (as it is)and the signal input is pulse then the VCO will force the comparator output low much of the time Therefore it is ideal to condition the signal and com-parator input to short pulses This is most easily done by using a series capacitorTL F 11675–24FIGURE 8 Phase Comparator III Logic DiagramTL F 11675–25FIGURE 9 Typical Waveforms for Phase Comparator III12Ordering InformationThe device number is used to form part of a simplified purchasing code where the package type and temperature range are defined as followsTL F 11675–26 Physical Dimensions inches(millimeters)16-Lead(0 150 Wide)Molded Small Outline Package JEDEC Order Number74VHC4046MNS Package Number M16A1374V H C 4046C M O S P h a s e L o c k L o o pPhysical Dimensions inches (millimeters)(Continued)Molded Dual-In-Line Package (N)Order Number 74VHC4046N NS Package Number N16ELIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION As used herein 1 Life support devices or systems are devices or 2 A critical component is any component of a life systems which (a)are intended for surgical implant support device or system whose failure to perform can into the body or (b)support or sustain life and whose be reasonably expected to cause the failure of the life failure to perform when properly used in accordance support device or system or to affect its safety or with instructions for use provided in the labeling can effectivenessbe reasonably expected to result in a significant injury to the userNational Semiconductor National Semiconductor National Semiconductor National Semiconductor Corporation EuropeHong Kong LtdJapan Ltd1111West Bardin RoadFax (a 49)0-180-530858613th Floor Straight Block Tel 81-043-299-2309。

ST 74VHCT00A 数据手册

1/11December 2004s HIGH SPEED: t PD = 5 ns (TYP.) at V CC = 5V sLOW POWER DISSIPATION:I CC = 2 µA (MAX.) at T A =25°CsCOMPATIBLE WITH TTL OUTPUTS:V IH = 2V (MIN.), V IL = 0.8V (MAX)sPOWER DOWN PROTECTION ON INPUTS & OUTPUTSsSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 8 mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsOPERATING VOLTAGE RANGE:V CC (OPR) = 4.5V to 5.5VsPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 00s IMPROVED LATCH-UP IMMUNITY sLOW NOISE: V OLP = 0.8V (MAX.)DESCRIPTIONThe 74VHCT00A is an advanced high-speed CMOS QUAD 2-INPUT NAND GATE fabricated with sub-micron silicon gate and double-layer metal wiring C 2MOS technology.The internal circuit is composed of 3 stages including buffer output, which provides high noise immunity and stable output.Power down protection is provided on all inputs and outputs and 0 to 7V can be accepted on inputs with no regard to the supply voltage. This device can be used to interface 5V to 3V since all inputs are equipped with TTL threshold.All inputs and outputs are equipped with protection circuits against static discharge, giving them 2KV ESD immunity and transient excess voltage.74VHCT00AQUAD 2-INPUT NAND GATEFigure 1: Pin Connection And IEC Logic SymbolsTable 1: Order CodesPACKAGE T & R SOP 74VHCT00AMTR TSSOP74VHCT00ATTR74VHCT00A2/11Figure 2: Input Equivalent CircuitTable 2: Pin DescriptionTable 3: Truth TableTable 4: Absolute Maximum RatingsAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions isnot implied 1) V CC = 0V2) High or Low StateTable 5: Recommended Operating Conditions1) V CC = 0V2) High or Low State 3) V INfrom 0.8V to 2VPIN N°SYMBOL NAME AND FUNCTION 1, 4, 9, 121A to 4A Data Inputs 2, 5, 10, 131B to 4B Data Inputs 3, 6, 8, 111Y to 4Y Data Outputs 7GND Ground (0V)14V CCPositive Supply VoltageA B Y L L H L H H H L H HHLSymbol ParameterValue Unit V CC Supply Voltage -0.5 to +7.0V V I DC Input Voltage-0.5 to +7.0V V O DC Output Voltage (see note 1)-0.5 to +7.0V V O DC Output Voltage (see note 2)-0.5 to V CC + 0.5V I IK DC Input Diode Current - 20mA I OK DC Output Diode Current ± 20mA I ODC Output Current± 25mA I CC or I GND DC V CC or Ground Current± 50mA T stgStorage Temperature -65 to +150°C T LLead Temperature (10 sec)300°CSymbol ParameterValue Unit V CC Supply Voltage 4.5 to 5.5V V I Input Voltage0 to 5.5V V O Output Voltage (see note 1)0 to 5.5V V O Output Voltage (see note 2)0 to V CC V T op Operating Temperature-55 to 125°C dt/dvInput Rise and Fall Time (see note 3) (V CC = 5.0 ± 0.5V)0 to 20ns/V74VHCT00A3/11Table 6: DC SpecificationsTable 7: AC Electrical Characteristics (Input t r = t f = 3ns)(*) Voltage range is 5.0V ± 0.5VTable 8: Capacitive Characteristics1) C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CC /4 (per gate)SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V IH High Level Input Voltage4.5 to5.5222V V IL Low Level Input Voltage4.5 to5.50.80.80.8V V OH High Level Output Voltage4.5I O =-50 µA 4.4 4.54.4 4.4V 4.5I O =-8 mA 3.943.83.7V OL Low Level Output Voltage4.5I O =50 µA 0.00.10.10.1V 4.5I O =8 mA 0.360.440.55I I Input Leakage Current0 to 5.5V I = 5.5V or GND ± 0.1± 1.0± 1.0µA I CC Quiescent Supply Current5.5V I = V CC or GND 22020µA +I CCAdditional Worst Case Supply Current5.5One Input at 3.4V, other input at V CCor GND 1.35 1.5 1.5mA I OPDOutput Leakage CurrentV OUT = 5.5V0.55.05.0µA SymbolParameterTest ConditionValue UnitV CC (*)(V)C L (pF)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.t PLH t PHLPropagation Delay Time5.015 5.07.0 1.08.0 1.08.0ns 5.0505.58.01.09.01.09.0SymbolParameterTest ConditionValue UnitT A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance 4101010pF C PDPower Dissipation Capacitance (note 1)10.5pF74VHCT00A4/11Table 9: Dynamic Switching Characteristics1) Worst case package.2) Max number of outputs defined as (n). Data inputs are driven 0V to 3.0V, (n-1) outputs switching and one output at GND.3) Max number of data inputs (n) switching. (n-1) switching 0V to 3.0V. Inputs under test switching: 3.0V to threshold (V ILD ), 0V to threshold (V IHD ), f=1MHz.Figure 3: Test CircuitC L =15/50pF or equivalent (includes jig and probe capacitance)R T = Z OUT of pulse generator (typically 50Ω)SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V OLP Dynamic Low Voltage Quiet Output (note 1, 2) 5.0C L = 50 pF0.40.8VV OLV-0.8-0.4V IHD Dynamic High Voltage Input (note 1, 3) 5.02.0V ILDDynamic Low Voltage Input (note 1, 3)5.00.874VHCT00A Figure 4: Waveform - Propagation Delays (f=1MHz; 50% duty cycle)5/1174VHCT00A6/11DIM.mm.inchMIN.TYP MAX.MIN.TYP.MAX.A 1.35 1.750.0530.069 A10.10.250.0040.010 A2 1.10 1.650.0430.065 B0.330.510.0130.020 C0.190.250.0070.010 D8.558.750.3370.344 E 3.8 4.00.1500.157 e 1.270.050H 5.8 6.20.2280.244 h0.250.500.0100.020 L0.4 1.270.0160.050 k0°8°0°8°ddd0.1000.004SO-14 MECHANICAL DATA0016019D74VHCT00A7/11DIM.mm.inchMIN.TYPMAX.MIN.TYP.MAX.A 1.20.047A10.050.150.0020.0040.006A20.81 1.050.0310.0390.041b 0.190.300.0070.012c 0.090.200.0040.0089D 4.95 5.10.1930.1970.201E 6.2 6.4 6.60.2440.2520.260E1 4.34.4 4.480.1690.1730.176e 0.65 BSC0.0256 BSCK 0˚8˚0˚8˚L0.450.600.750.0180.0240.030TSSOP14 MECHANICAL DATAcEbA2A E1D1PIN 1 IDENTIFICATIONA1LKe0080337D74VHCT00ATape & Reel SO-14 MECHANICAL DATAmm.inch DIM.MIN.TYP MAX.MIN.TYP.MAX.A33012.992 C12.813.20.5040.519 D20.20.795N60 2.362T22.40.882 Ao 6.4 6.60.2520.260 Bo99.20.3540.362 Ko 2.1 2.30.0820.090 Po 3.9 4.10.1530.161 P7.98.10.3110.3198/1174VHCT00A Tape & Reel TSSOP14 MECHANICAL DATAmm.inchDIM.MIN.TYP MAX.MIN.TYP.MAX.A33012.992C12.813.20.5040.519D20.20.795N60 2.362T22.40.882Ao 6.7 6.90.2640.272Bo 5.3 5.50.2090.217Ko 1.6 1.80.0630.071Po 3.9 4.10.1530.161P7.98.10.3110.3199/1174VHCT00ATable 10: Revision HistoryDate Revision Description of Changes 16-Dec-20044Order Codes Revision - pag. 1.10/1174VHCT00A Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is grantedby implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are notauthorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronicsAll other names are the property of their respective owners© 2004 STMicroelectronics - All Rights ReservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America11/11。

74门电路系列芯片资料图表

74HC00 四 2 输入与非门国际通用符号54/7400 , 54/74H00 , 54L 00 , 54/74S00 , 54/74LS00 , 54/74ALS00 , 54/ 74F 00 ,54/74HC00 , 54/ 74AC 00 , 54/74HCT00 , 54/74ACT00 , 54/74AHC00 , 54/74AHCT00 ,74LV00 , 74LVC00。

74HC02 四 2 输入或非门国际通用符号54/7402 , 54L 02 , 54/74S02 , 54/74LS02 , 54/74AS02 , 54/74ALS02 , 54/ 74F 02 ,54/74HC02 , 74AC 02 , 54/74HCT02 , 54/74ACT02 , 54/74AHC02 , 54/AHCT02 , 74LV02 ,74LVC02。

74HC04 六反相器国际通用符号54/7404 , 54L 04 , 54/74H04 , 54/74S04 , 54/74LS04 , 54/74AS04 , 54/74ALS04 ,54/ 74F 04 , 54/74HCU04 , 54/74HC04 , 54/ 74AC 04 , 54/74HCT04 , 54/74ACT04 ,54/74AHC04 , 54/74AHCT04 , 74LV04 , 74LVC04 , 54/74AHCU04 , 74LVU04 , 74LVCU04。

74HC08 四 2 输入与门国际通用符号54/7408 , 54/74S08 , 54/74LS08 , 54/74AS08 , 54/74ALS08 , 54/ 74F 08 , 54/74HC08 ,54/74HCT08 , 54/ 74AC 08 , 54/74ACT08 , 54/74AHC08 , 54/74AHCT08 , 74LV08 , 74LVC08。

cc4046及转速仪应用

-66-《国外电子元器件》2002年第10期2002年10月CC4046锁相环电路及其在转速仪中的应用珠海格力小家电有限公司罗平CC4046P LL and Its A pp lication in the T achometerLuo P in g摘要:简要介绍了CM OS单片锁相环(P LL)电路CC4046的工作原理,给出了锁相环的具体应用实例,同时结合60倍速转速检测仪的实用线路进行了相关的设计分析。

关键词:锁相环(P LL);倍速;采样;测试;转速仪;CC4046分类号:T N761.3文献标识码:B文章编号:1006-6977(2002)10-0066-03●主题论文1锁相环的工作原理锁相就是相位同步的自动控制,完成两个电信号相位的自动控制系统称为锁相环(简称P LL),锁相环技术在信号处理和数字系统中有着广泛的应用,如频率调制、频率锁定、时钟同步、频率合成等等都要用到锁相环技术,下面是CM OS单片锁相电路CC4046的工作原理。

一般情况下,CM OS锁相环由三个基本单元构成:相位比较器、电压控制振荡器和低通滤波器。

由于CC4046内部只包含前面两个单元,因此,使用时需要外接低通滤波器(阻、容元件)来构成完整的锁相环(P LL),图1为其功能框图。

在CC4046的工作过程中,施加于相位比较器的信号有输入信号V I(t)和VCO输出信号V o(t)。

相位比较器的输出信号为V e(t),它正比于V I(t)和V o(t)的相位差,V e(t)经低通滤波器后可得到一个平均电压V d(t),反过来,这个V e(t)电压又控制着压控振荡器(VCO)的频率变化,以使输入与输出信号的频率之差不断减小,直到最后为零,这时我们称之为锁定。

当锁相环锁定时,压控振荡器(VCO)能使其输出信号频率跟随输入信号的频率变化。

其锁定范围以f LR表示。

而锁相环能“捕捉”的输入信号频率称为捕捉范围,以f CR表示。

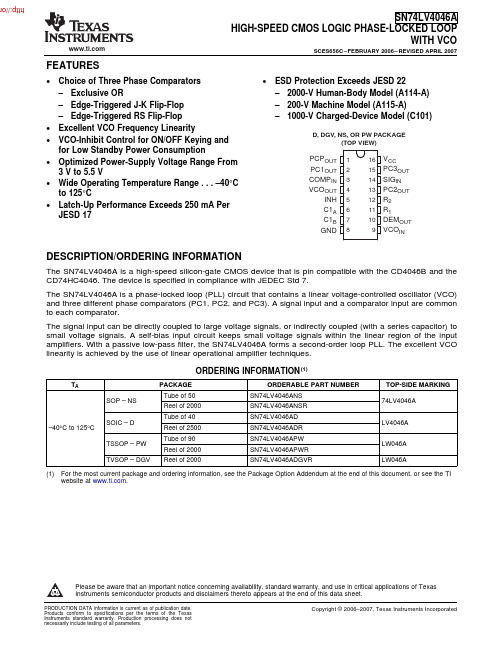

cd74hct4046英文使用手册

Data sheet acquired from Harris Semiconductor SCHS204JFeatures•Operating Frequency Range-Up to 18MHz (Typ) at V CC = 5V-Minimum Center Frequency of 12MHz at V CC = 4.5V •Choice of Three Phase Comparators -EXCLUSIVE-OR-Edge-Triggered JK Flip-Flop -Edge-Triggered RS Flip-Flop •Excellent VCO Frequency Linearity•VCO-Inhibit Control for ON/OFF Keying and for Low Standby Power Consumption •Minimal Frequency Drift•Operating Power Supply Voltage Range-VCO Section . . . . . . . . . . . . . . . . . . . . . . . . . .3V to 6V -Digital Section . . . . . . . . . . . . . . . . . . . . . . . .2V to 6V •Fanout (Over Temperature Range)-Standard Outputs. . . . . . . . . . . . . . .10 LSTTL Loads -Bus Driver Outputs . . . . . . . . . . . . .15 LSTTL Loads •Wide Operating Temperature Range . . .-55o C to 125o C •Balanced Propagation Delay and Transition Times •Significant Power Reduction Compared to LSTTL Logic ICs •HC Types-2V to 6V Operation-High Noise Immunity: N IL = 30%, N IH = 30% of V CC at V CC = 5V •HCT Types- 4.5V to 5.5V Operation-Direct LSTTL Input Logic Compatibility,V IL = 0.8V (Max), V IH = 2V (Min)-CMOS Input Compatibility, I l ≤ 1µA at VOL, VOHApplications•FM Modulation and Demodulation •Frequency Synthesis and Multiplication •Frequency Discrimination •Tone Decoding•Data Synchronization and Conditioning •Voltage-to-Frequency Conversion •Motor-Speed ControlDescriptionThe ’HC4046A and ’HCT4046A are high-speed silicon-gate CMOS devices that are pin compatible with the CD4046B of the “4000B”series.They are specified in compliance with JEDEC standard number 7.The ’HC4046A and ’HCT4046A are phase-locked-loop circuits that contain a linear voltage-controlled oscillator (VCO)and three different phase comparators (PC1,PC2and PC3).A signal input and a comparator input are common to each comparator.The signal input can be directly coupled to large voltage signals,or indirectly coupled (with a series capacitor)to small voltage signals.A self-bias input circuit keeps small voltage signals within the linear region of the input amplifiers.With a passive low-pass filter,the 4046A forms a second-order loop PLL.The excellent VCO linearity is achieved by the use of linear op-amp techniques.Ordering InformationPART NUMBER TEMP. RANGE(o C)PACKAGE CD54HC4046AF3A -55 to 12516 Ld CERDIP CD54HCT4046AF3A -55 to 12516 Ld CERDIP CD74HC4046AE -55 to 12516 Ld PDIP CD74HC4046AM -55 to 12516 Ld SOIC CD74HC4046AMT -55 to 12516 Ld SOIC CD74HC4046AM96-55 to 12516 Ld SOIC CD74HC4046ANSR -55 to 12516 Ld SOP CD74HC4046APWR -55 to 12516 Ld TSSOP CD74HC4046APWT -55 to 12516 Ld TSSOP CD74HCT4046AE -55 to 12516 Ld PDIP CD74HCT4046AM -55 to 12516 Ld SOIC CD74HCT4046AMT -55 to 12516 Ld SOIC CD74HCT4046AM96-55 to 12516 Ld SOICNOTE:When ordering,use the entire part number.The suffixes 96and R denote tape and reel.The suffix T denotes a small-quantity reel of 250.February 1998 - Revised December 2003CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.CD54HC4046A, CD74HC4046A,CD54HCT4046A, CD74HCT4046AHigh-Speed CMOS Logic Phase-Locked Loop with VCOPinoutCD54HC4046A, CD54HCT4046A (CERDIP)CD74HC4046A (PDIP, SOIC, SOP, TSSOP)CD74HCT4046A (PDIP, SOIC)TOP VIEWFunctional Diagram14151691312111012345768PCP OUTPC1OUTCOMP INVCO OUTINHC1AGNDC1BV CCSIG INPC2OUTR2R1DEM OUTVCO INPC3OUT104VCO OUTDEM OUT56712C1AR1VCO ININH911C1BR2151132PC1OUTPC3OUTPC2OUTPCP OUT 143COMP INSIG INφVCOPin DescriptionsPIN NUMBER SYMBOL NAME AND FUNCTION 1PCP OUT Phase Comparator Pulse Output2PC1OUT Phase Comparator 1 Output3COMP IN Comparator Input4VCO OUT VCO Output5INH Inhibit Input6C1A Capacitor C1 Connection A7C1B Capacitor C1 Connection B8GND Ground (0V)9VCO IN VCO Input10DEM OUT Demodulator Output11R1Resistor R1 Connection12R2Resistor R2 Connection13PC2OUT Phase Comparator 2 Output14SIG IN Signal Input15PC3OUT Phase Comparator 3 Output16V CC Positive Supply VoltageGeneral DescriptionVCOThe VCO requires one external capacitor C1(between C1A and C1B )and one external resistor R1(between R 1and GND)or two external resistors R1and R2(between R 1and GND,and R 2and GND).Resistor R1and capacitor C1determine the frequency range of the VCO.Resistor R2enables the VCO to have a frequency offset if required.See logic diagram, Figure 1.The high input impedance of the VCO simplifies the design of low-pass filters by giving the designer a wide choice of resistor/capacitor ranges.In order not to load the low-pass filter,a demodulator output of the VCO input voltage is provided at pin 10(DEM OUT ).In contrast to conventional techniques where the DEM OUT voltage is one threshold voltage lower than the VCO input voltage,here the DEM OUT voltage equals that of the VCO input.If DEM OUT is used,a load resistor (R S )should be connected from DEM OUT to GND;if unused,DEM OUT should be left open.The VCO output (VCO OUT )can be connected directly to the comparator input (COMP IN ),or connected via a frequency-divider.The VCO output signal has a specified duty factor of 50%.A LOW level at the inhibit input (INH)enables the VCO and demodulator,while a HIGH level turns both off to minimize standby power consumption.Phase ComparatorsThe signal input (SIG IN )can be directly coupled to the self-biasing amplifier at pin 14,provided that the signal swing is between the standard HC family input logic levels.Capacitive coupling is required for signals with smaller swings.Phase Comparator 1 (PC1)This is an Exclusive-OR network.The signal and comparator input frequencies (f i )must have a 50%duty factor to obtain the maximum locking range.The transfer characteristic of PC1, assuming ripple (f r = 2f i ) is suppressed, is:V DEMOUT =(V CC /π)(φSIG IN -φCOMP IN )where V DEMOUT is the demodulator output at pin 10;V DEMOUT =V PC1OUT (via low-pass filter).The average output voltage from PC1,fed to the VCO input via the low-pass filter and seen at the demodulator output at pin 10(V DEMOUT ),is the resultant of the phase differences of signals (SIG IN )and the comparator input (COMP IN )as shown in Figure 2.The average of V DEM is equal to 1/2V CC when there is no signal or noise at SIG IN ,and with this input the VCO oscillates at the center frequency (f o ).T ypical waveforms for the PC1loop locked at f o are shown in Figure 3.FIGURE 1.LOGIC DIAGRAMDEM OUTR212R1R51110C1R3C2PC2OUT13pnGNDV CC PCP OUT1152PC3OUTPC1OUTDOWN R DQQ DCP R DQQ DCP UPV C CV CCR DQ QS DINH 59VCO IN VCO-+V C O O U TCOMP IN-+SIG INC1BC1AV REFR2R1674314-+The frequency capture range (2f C )is defined as the frequency range of input signals on which the PLL will lock if it was initially out-of-lock.The frequency lock range (2f L )is defined as the frequency range of input signals on which the loop will stay locked if it was initially in lock.The capture range is smaller or equal to the lock range.With PC1,the capture range depends on the low-pass filter characteristics and can be made as large as the lock range.This configuration retains lock behavior even with very noisy input signals.Typical of this type of phase comparator is that it can lock to input frequencies close to the harmonics of the VCO center frequency.Phase Comparator 2 (PC2)This is a positive edge-triggered phase and frequency detector.When the PLL is using this comparator,the loop is controlled by positive signal transitions and the duty factors of SIG IN and COMP IN are not important.PC2comprises two D-type flip-flops,control-gating and a three-state output stage.The circuit functions as an up-down counter (Figure 1)where SIG IN causes an up-count and COMP IN a down-count.The transfer function of PC2,assuming ripple (f r = f i ) is suppressed, is:V DEMOUT =(V CC /4π)(φSIG IN -φCOMP IN )where V DEMOUT is the demodulator output at pin 10;V DEMOUT =V PC2OUT (via low-pass filter).The average output voltage from PC2,fed to the VCO via the low-pass filter and seen at the demodulator output at pin 10(V DEMOUT ),is the resultant of the phase differences of SIG IN and COMP IN as shown in Figure 4.Typical waveforms for the PC2 loop locked at f o are shown in Figure 5.When the frequencies of SIG IN and COMP IN are equal but the phase of SIG IN leads that of COMP IN ,the p-type output driver at PC2OUT is held “ON”for a time corresponding to the phase difference (φDEMOUT ).When the phase of SIG IN lags that of COMP IN , the n-type driver is held “ON”.When the frequency of SIG IN is higher than that of COMP IN ,the p-type output driver is held “ON”for most of the input signal cycle time,and for the remainder of the cycle both n-and p-type drivers are “OFF”(three-state).If the SIG IN frequency is lower than the COMP IN frequency,then it is the n-type driver that is held “ON”for most of the cycle.Subsequently,the voltage at the capacitor (C2)of the low-pass filter connected to PC2OUT varies until the signal and comparator inputs are equal in both phase andFIGURE 2.PHASE COMPARATOR 1:AVERAGE OUTPUTVOLTAGE vs INPUT PHASE DIFFERENCE:V DEMOUT = V PC1OUT = (V CC /π) (φSIG IN -φCOMP IN );φDEMOUT =(φSIG IN -φCOMP IN )V CCV DEMOUT (AV)1/2 V CC00o90oφDEMOUT 180oFIGURE 3.TYPICAL WAVEFORMS FOR PLL USING PHASECOMPARATOR 1, LOOP LOCKED AT f oSIG INCOMP IN VCO OUTPC1OUTVCO INV CCGNDFIGURE 4.PHASE COMPARATOR 2: AVERAGE OUTPUTVOLTAGE vs INPUT PHASE DIFFERENCE:V DEMOUT = V PC2OUT= (V CC /4π) (φSIG IN -φCOMP IN );φDEMOUT =(φSIG IN -φCOMP IN )V CCV DEMOUT (AV)1/2 V CC0-360o0oφDEMOUT 360oFIGURE 5.TYPICAL WAVEFORMS FOR PLL USING PHASECOMPARATOR 2, LOOP LOCKED AT f oSIG IN COMP IN VCO OUTPC2OUTVCO IN V CC GNDPCP OUTHIGH IMPEDANCE OFF - STATEfrequency.At this stable point the voltage on C2remains constant as the PC2output is in three-state and the VCO input at pin9is a high impedance.Also in this condition, the signal at the phase comparator pulse output(PCP OUT) is a HIGH level and so can be used for indicating a locked condition.Thus,for PC2,no phase difference exists between SIG IN and COMP IN over the full frequency range of the VCO. Moreover,the power dissipation due to the low-passfilter is reduced because both p-and n-type drivers are“OFF”for most of the signal input cycle.It should be noted that the PLL lock range for this type of phase comparator is equal to the capture range and is independent of the low-passfilter. With no signal present at SIG IN,the VCO adjusts,via PC2, to its lowest frequency.Phase Comparator 3 (PC3)This is a positive edge-triggered sequential phase detector using an RS-type flip-flop.When the PLL is using this comparator,the loop is controlled by positive signal transitions and the duty factors of SIG IN and COMP IN are not important.The transfer characteristic of PC3, assuming ripple (f r = f i) is suppressed, is:V DEMOUT=(V CC/2p)(fSIG IN-fCOMP IN)where V DEMOUT is the demodulator output at pin10;V DEMOUT = V PC3OUT (via low-pass filter).The average output from PC3,fed to the VCO via the low-pass filter and seen at the demodulator at pin10 (V DEMOUT),is the resultant of the phase differences of SIG IN and COMP IN as shown in Figure 6.Typical waveforms for the PC3loop locked at f o are shown in Figure 7.The phase-to-output response characteristic of PC3 (Figure6)differs from that of PC2in that the phase angle between SIG IN and COMP IN varies between0o and360o and is180o at the center frequency.Also PC3gives a greater voltage swing than PC2for input phase differences but as aconsequence the ripple content of the VCO input signal is higher.With no signal present at SIG IN,the VCO adjusts,via PC3,to its highest frequency.The only difference between the HC and HCT versions is the input level specification of the INH input.This input disables the VCO section.The comparator’s sections are identical,so that there is no difference in the SIG IN(pin14)or COMP IN (pin 3) inputs between the HC and the HCT versions.FIGURE6.PHASE COMPARATOR3:AVERAGE OUTPUT VOLTAGE vs INPUT PHASE DIFFERENCE:V DEMOUT = V PC3OUT= (V CC/2π) (φSIG IN -φCOMP IN);φDEMOUT = (φSIG IN -φCOMP IN)V CCV DEMOUT (AV)1/2 V CC0o180oφDEMOUT360oFIGURE7.TYPICAL WAVEFORMS FOR PLL USING PHASE COMPARATOR 3, LOOP LOCKED AT f o SIG INCOMP INVCO OUTPC3OUTVCO INV CCGNDCD54HC4046A, CD74HC4046A, CD54HCT4046A, CD74HCT4046AAbsolute Maximum Ratings Thermal InformationDC Supply Voltage, V CC. . . . . . . . . . . . . . . . . . . . . . . .-0.5V to 7V DC Input Diode Current, I IKFor V I < -0.5V or V I > V CC + 0.5V. . . . . . . . . . . . . . . . . . . . . .±20mA DC Output Diode Current, I OKFor V O < -0.5V or V O > V CC + 0.5V . . . . . . . . . . . . . . . . . . . .±20mA DC Drain Current, per Output, I OFor -0.5V < V O < V CC + 0.5V. . . . . . . . . . . . . . . . . . . . . . . . . .±25mA DC Output Source or Sink Current per Output Pin, I OFor V O > -0.5V or V O < V CC + 0.5V . . . . . . . . . . . . . . . . . . . .±25mA DC V CC or Ground Current, I CC . . . . . . . . . . . . . . . . . . . . . . . . .±50mA Operating ConditionsTemperature Range, T A . . . . . . . . . . . . . . . . . . . . . .-55o C to 125o C Supply Voltage Range, V CCHC T ypes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2V to 6V HCT T ypes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V DC Input or Output Voltage, V I, V O . . . . . . . . . . . . . . . . .0V to V CC Input Rise and Fall Time2V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1000ns (Max) 4.5V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .500ns (Max) 6V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .400ns (Max)Package Thermal Impedance,θJA(see Note 1):E (PDIP) Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67o C/W M (SOIC) Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73o C/W NS (SOP) Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64o C/W PW (TSSOP) Package. . . . . . . . . . . . . . . . . . . . . . . . . . 108o C/W Maximum Junction T emperature. . . . . . . . . . . . . . . . . . . . . . .150o C Maximum Storage Temperature Range . . . . . . . . . .-65o C to 150o C Maximum Lead T emperature (Soldering 10s). . . . . . . . . . . . .300o C (SOIC - Lead Tips Only)CAUTION:Stresses above those listed in“Absolute Maximum Ratings”may cause permanent damage to the device.This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.NOTE:1.The package thermal impedance is calculated in accordance with JESD 51-7.DC Electrical SpecificationsPARAMETER SYMBOLTESTCONDITIONS VCC(V)25o C-40o C TO 85o C-55o C TO125o CUNITS V I(V)I O(mA)MIN TYP MAX MIN MAX MIN MAXHC TYPES VCO SECTIONINH High Level Input Voltage V IH--3 2.1-- 2.1- 2.1-V4.5 3.15-- 3.15 - 3.15-V6 4.2-- 4.2- 4.2-VINH Low Level Input Voltage V IL--3--0.9-0.9-0.9V4.5-- 1.35- 1.35- 1.35V6-- 1.8- 1.8- 1.8VVCO OUT High Level Output Voltage CMOS Loads V OH V IH or V IL-0.023 2.9-- 2.9- 2.9-V -0.02 4.5 4.4-- 4.4 - 4.4-V-0.026 5.9-- 5.9- 5.9-VVCO OUT High Level Output VoltageTTL Loads---------V -4 4.5 3.98-- 3.84- 3.7-V -5.26 5.48-- 5.34- 5.2-VVCO OUT Low Level Output Voltage CMOS Loads V OL V IH or V IL0.022--0.1-0.1-0.1V0.02 4.5--0.1-0.1-0.1V0.026--0.1-0.1-0.1VVCO OUT Low Level Output Voltage TTL Loads---------V4 4.5--0.26-0.33-0.4V5.26--0.26-0.33-0.4VC1A, C1B Low Level Output Voltage (Test Purposes Only)V OL V IL or V IH4 4.5--0.40-0.47-0.54V5.26--0.40-0.47-0.54VINH VCO IN Input Leakage Current I I V CC orGND-6--±0.1-±1-±1µAR1 Range (Note 2)--- 4.53-300----kΩR2 Range (Note 2)--- 4.53-300----kΩC1 Capacitance Range ---3--NoLimit----pF4.5------pF6------pFVCO IN Operating Voltage Range -Over the rangespecified for R1forLinearity See Figure10, and 34 - 37(Note 3)3 1.1- 1.9----V4.5 1.1- 3.2----V6 1.1- 4.6----VPHASE COMPARATOR SECTIONSIG IN, COMP IN DC Coupled High-Level Input Voltage V IH--2 1.5-- 1.5- 1.5-V4.5 3.15-- 3.15- 3.15-V6 4.2-- 4.2- 4.2-VSIG IN, COMP IN DC Coupled Low-Level Input Voltage V IL--2--0.5-0.5-0.5V4.5-- 1.35- 1.35- 1.35V6-- 1.8- 1.8- 1.8VPCP OUT, PCn OUT High-Level Output VoltageCMOS Loads V OH V IL or V IH-0.022 1.9-- 1.9- 1.9-V4.5 4.4-- 4.4- 4.4-V6 5.9-- 5.9- 5.9-VPCP OUT, PCn OUT High-Level Output VoltageTTL Loads V OH V IL or V IH-4 4.5 3.98-- 3.84- 3.7-V -5.26 5.48-- 5.34- 5.2-VPCP OUT, PCn OUT Low-Level Output VoltageCMOS Loads V OL V IL or V IH0.022--0.1-0.1-0.1V4.5--0.1-0.1-0.1V6--0.1-0.1-0.1VPCP OUT, PCn OUT Low-Level Output VoltageTTL Loads V OL V IL or V IH4 4.5--0.26-0.33-0.4V5.26--0.26-0.33-0.4VSIG IN,COMP IN Input Leakage Current I I V CC orGND-2--±3-±4-±5µA3--±7-±9-±11µA4.5--±18-±23-±29µA6--±30-±38-±45µAPC2OUT Three-StateOff-State CurrentI OZ V IL or V IH-6--±0.5-±5-±10µASIG IN,COMP IN Input Resistance R I V I at Self-BiasOperation Point:∆V I = 0.5V,See Figure 103-800-----kΩ4.5-250-----kΩ6-150-----kΩDEMODULATOR SECTIONResistor Range R S at R S > 300kΩLeakage CurrentCan InfluenceV DEMOUT350-300----kΩ4.550-300----kΩ650-300----kΩPARAMETER SYMBOLCONDITIONS VCC(V)25o C-40o C TO 85o C-55o C TO125o CUNITS V I(V)I O(mA)MIN TYP MAX MIN MAX MIN MAXOffset Voltage VCO INto V DEMV OFF V I = V VCO IN =Values T aken OverR S RangeSee Figure 233-±30-----mV 4.5-±20-----mV 6-±10-----mVDynamic Output Resistance at DEM OUT R D V DEMOUT=3-25-----Ω4.5-25-----Ω6-25-----ΩQuiescent Device Current I CC Pins 3, 5 and 14at V CC Pin 9 atGND, I1 at Pins 3and 14 to beexcluded6--8-80-160µAHCT TYPES VCO SECTIONINH High Level Input Voltage V IH-- 4.5 to5.52--2-2-VINH Low Level Input Voltage V IL-- 4.5 to5.5--0.8-0.8-0.8VVCO OUT High LevelOutput VoltageCMOS LoadsV OH V IH or V IL-0.02 4.5 4.4-- 4.4- 4.4-VVCO OUT High LevelOutput VoltageTTL Loads-4 4.5 3.98-- 3.84- 3.7-VVCO OUT Low LevelOutput VoltageCMOS LoadsV OL V IH or V IL0.02 4.5--0.1-0.1-0.1VVCO OUT Low LevelOutput VoltageTTL Loads4 4.5--0.26-0.33-0.4VC1A, C1B Low LevelOutput Voltage(Test Purposes Only)V OL V IH or V IL4 4.5--0.40-0.47-0.54VINH VCO IN Input Leakage Current I I Any VoltageBetween V CC andGND5.5-±0.1-±1-±1µAR1 Range (Note 2)--- 4.53-300----kΩR2 Range (Note 2)--- 4.53-300----kΩC1 Capacitance Range --- 4.50-NoLimit----pFVCO IN Operating Voltage Range -Over the rangespecified for R1forLinearity See Figure10, and 34 - 37(Note 3)4.5 1.1- 3.2----VPHASE COMPARATOR SECTIONSIG IN, COMP IN DC Coupled High-Level Input Voltage V IH-- 4.5 to5.52--2-2-VPARAMETER SYMBOLCONDITIONS VCC(V)25o C-40o C TO 85o C-55o C TO125o CUNITS V I(V)I O(mA)MIN TYP MAX MIN MAX MIN MAXV CC2V CC2SIG IN , COMP IN DC Coupled Low-Level Input VoltageV IL-- 4.5 to 5.5--0.8-0.8-0.8VPCP OUT , PCn OUT High-Level Output VoltageCMOS Loads V OH V IL or V IH- 4.5 4.4-- 4.4- 4.4-VPCP OUT , PCn OUT High-Level Output Voltage TTL LoadsV OH V IL or V IH- 4.5 3.98-- 3.84- 3.7-VPCP OUT , PCn OUT Low-Level Output VoltageCMOS Loads V OL V IL or V IH- 4.5--0.1-0.1-0.1VPCP OUT , PCn OUT Low-Level Output Voltage TTL LoadsV OL V IL or V IH- 4.5--0.26-0.33-0.4VSIG IN ,COMP IN Input Leakage CurrentI IAny Voltage Between V CC and GND - 5.5--±30±38±45µAPC2OUT Three-State Off-State Current I OZ V IL or V IH- 5.5--±0.5±5--±10µA SIG IN ,COMP IN Input ResistanceR IV I at Self-Bias Operation Point:∆V I = 0.5V,See Figure 10 4.5-250-----k ΩDEMODULATOR SECTION Resistor RangeR Sat R S > 300k ΩLeakage Current Can Influence V DEM OUT 4.55-300----k ΩOffset Voltage VCO IN to V DEMV OFFV I = V VCO IN =Values taken overR S Range See Figure 23 4.5-±20-----mVDynamic Output Resistance at DEM OUTR DV DEM OUT = 4.5-25-----ΩQuiescent Device CurrentI CC V CC or GND - 5.5--8-80-160µA Additional Quiescent Device Current Per Input Pin: 1 Unit Load ∆I CC (Note 4)V CC -2.1Excluding Pin 5-4.5 to5.5-100360-450-490µANOTES:2.The value for R1 and R2 in parallel should exceed 2.7k Ω.3.The maximum operating voltage can be as high as V CC -0.9V, however, this may result in an increased offset voltage.4.For dual-supply systems theoretical worst case (V I = 2.4V, V CC =5.5V) specification is 1.8mA.PARAMETER SYMBOL CONDITIONSV CC (V)25o C-40o C TO 85o C -55o C TO 125o C UNITS V I (V)I O (mA)MIN TYP MAX MIN MAX MIN MAX V CC 2V CC 2HCT Input Loading TableINPUT UNIT LOADSINH1NOTE:Unit load is∆I CC limit specific in DC Electrical Specifications Table, e.g., 360µA max. at 25o C.Switching Specifications C L = 50pF, Input t r, t f= 6nsPARAMETER SYMBOLTESTCONDITIONS V CC(V)25o C-40o C TO85o C-55o C TO125o CUNITSMIN TYP MAX MIN MAX MIN MAXHC TYPESPHASE COMPARATOR SECTIONPropagation Delay t PLH, t PHLSIG IN, COMP IN to PCI OUT2--200-250-300ns4.5--40-50-60ns6--34-43-51ns SIG IN, COMP IN to PCP OUT2--300-375-450ns4.5--60-75-90ns6--51-64-77ns SIG IN, COMP IN to PC3OUT2--245-305-307ns4.5--49-61-74ns6--42-52-63ns Output Transition Time t THL, t TLH2--75-95-110ns4.5--15-19-22ns6--13-16-19nsOutput Enable Time, SIG IN, COMP IN to PC2OUT t PZH, t PZL2--265-330-400ns4.5--53-66-80ns6--45-56-68nsOutput Disable Time, SIG IN, COMP IN to PC2OUT t PHZ, t PLZ2--315-395-475ns4.5--63-79-95ns6--54-67-81nsAC Coupled Input Sensitivity (P-P) at SIG IN or COMP IN V I(P-P)3-11-----mV4.5-15-----mV6-33-----mVVCO SECTIONFrequency Stability with Temperature Change ∆f∆TR1 = 100kΩ,R2 =∞3-0.11-----%/o C4.5-0.11-----%/o C6-0.11-----%/o CMaximum Frequency f MAX C1 = 50pFR1 = 3.5kΩR2 =∞3-24-----MHz 4.5-24-----MHz 6-24-----MHzC1 = 0pF R1 = 9.1kΩR2 =∞3-38-----MHz 4.5-38-----MHz 6-38-----MHzCenter Frequency C1 = 40pFR1 = 3kΩR2 =∞VCO IN =VCC/23710-----MHz 4.51217-----MHz 61421-----MHzFrequency Linearity∆f VCO R1 = 100kΩR2 =∞C1 = 100pF3-0.4-----% 4.5-0.4-----% 6-0.4-----%Offset Frequency R2 = 220kΩC1 = 1nF3-400-----kHz 4.5-400-----kHz 6-400-----kHzDEMODULATOR SECTIONV OUT V S f IN R1 = 100kΩR2 =∞C1 = 100pFR S = 10kΩR3 = 100kΩC2 = 100pF3-------mV/kHz 4.5-330-----mV/kHz 6-------mV/kHzHCT TYPESPHASE COMPARATOR SECTIONPropagation Delay t PHL,t PLHSIG IN, COMP IN to PCI OUT C L = 50pF 4.5--45-56-68ns SIG IN, COMP IN to PCP OUT t PHL,t PLH C L = 50pF 4.5--68-85-102ns SIG IN, COMP IN to PC3OUT t PHL,t PLH C L = 50pF 4.5--58-73-87ns Output Transition Time t TLH, t THL C L = 50pF 4.5--15-19-22ns Output Enable Time, SIG IN,COMP IN to PC2OUTt PZH, t PZL C L = 50pF 4.5--60-75-90pFOutput Disable Time, SIG IN,COMP IN to PCZ OUTt PHZ, t PLZ C L = 50pF 4.5--68-85-102pFAC Coupled Input Sensitivity(P-P) at SIG IN or COMP IV I(P-P) 4.5-15-----mV VCO SECTIONFrequency Stability with Temperature Change ∆f∆TR1 = 100kΩ,R2 =∞4.5-0.11-----%/o CMaximum Frequency f MAX C1 = 50pFR1 = 3.5kΩR2 =∞4.5-24-----MHzC1 = 0pFR1 = 9.1kΩR2 =∞4.5-38-----MHzCenter Frequency C1 = 40pFR1 = 3kΩR2 =∞VCO IN =VCC/24.51217-----MHzFrequency Linearity∆f VCO R1 = 100kΩR2 =∞C1 = 100pF 4.5-0.4-----%PARAMETER SYMBOLTESTCONDITIONS V CC(V)25o C85o C125o CUNITSMIN TYP MAX MIN MAX MIN MAXOffset FrequencyR 2 = 220k ΩC 1 = 1nF4.5-400-----kHzDEMODULATOR SECTION V OUT V S f INR 1 = 100k ΩR 2 =∞C 1 = 100pF R S = 10k ΩR 3 = 100k ΩC 2 = 100pF4.5-330-----mV/kHzPARAMETERSYMBOLTEST CONDITIONS V CC (V)25o C85o C 125o C UNITS MIN TYP MAX MIN MAX MIN MAX Test Circuits and WaveformsFIGURE 8.INPUT TO OUTPUT PROPAGATION DELAYS ANDOUTPUT TRANSITION TIMESFIGURE 9.THREE STATE ENABLE AND DISABLE TIMES FORPC2OUTV S t PHLt PHLt TLHt TLHV SSIG IN COMP IN INPUTSPCP OUT PC1OUT PC3OUT OUTPUTSV SSIG IN t PZHV S V St PZH90%INPUTSCOMP IN INPUTSPC2OUT OUTPUTt PZLt PZL10%Typical Performance CurvesFIGURE 10.TYPICAL INPUT RESISTANCE CURVE AT SIG IN ,COMP INI IV I∆V ISELF-BIAS OPERATING POINTFIGURE 11.HC4046A TYPICAL CENTER FREQUENCY vs R1,C1 (V CC = 4.5V)FIGURE 12.HC4046A TYPICAL CENTER FREQUENCY vs R1,C1 (V CC = 6V)FIGURE 13.HC4046A TYPICAL CENTER FREQUENCY vs R1,C1 (V CC = 3V, R2 = OPEN)FIGURE 14.HCT4046A TYPICAL CENTER FREQUENCY vs R1,C1 (V CC = 4.5V)FIGURE 15.HCT4046A TYPICAL CENTER FREQUENCY vs R1,C1 (V CC = 5.5V)FIGURE 16.HC4046A TYPICAL VCO FREQUENCY vs VCO IN(R1 = 1.5M Ω, C1 = 50pF)108107106105104103102101110102103104105106CAPACITANCE, C1 (pF)C E N T E R F R E Q U E N C Y (H z )VCO IN = 0.5 V CC V CC = 4.5VR1 = 2.2K R1 = 22K R1 = 220K R1 = 2.2M R1 = 11M 108107106105104103102101110102103104105106CAPACITANCE, C1 (pF)C E N T E R F R E Q U E N C Y (H z )VCO IN = 0.5 V CC V CC = 6.0VR1 =3K R1 = 30K R1 =330K R1 = 3M R1 = 15M108107106105104103102101110102103104105106CAPACITANCE, C1 (pF)C E N T E R F R E Q U E N C Y (H z )VCO IN = 0.5 V CC V CC = 3.0V R2 = OPENR1 = 1.5K R1 = 15K R1 = 150K R1 = 1.5M R1 = 7.5M 108107106105104103102101110102103104105106CAPACITANCE, C1 (pF)C E N T E R F R E Q U E N C Y (H z )VCO IN = 0.5 V CC V CC = 4.5VR1 = 2.2K R1 = 22K R1 = 220K R1 = 2.2M R1 = 11M108107106105104103102101110102103104105106CAPACITANCE, C1 (pF)C E N T E R F R E Q U E N C Y (H z )VCO IN = 0.5 V CC V CC = 5.5VR1 = 3K R1 = 30K R1 = 300K R1 = 3M R1 = 15M140120100806040200123456VCO IN (V)V C O F R E Q U E N C Y (k H z )C1 = 50pF R1 = 1.5MV CC = 3VV CC = 4.5VV CC = 6VFIGURE 17.HC4046A TYPICAL VCO FREQUENCY vs VCO IN(R1 = 1.5M Ω, C1 = 0.1µF)FIGURE 18.HC4046A TYPICAL VCO FREQUENCY vs VCO IN(R1 = 150k Ω, C1 = 0.1µF)FIGURE 19.HC4046A TYPICAL VCO FREQUENCY vs VCO IN(R1 = 5.6k Ω, C1 = 0.1µF)FIGURE 20.HC4046A TYPICAL VCO FREQUENCY vs VCO IN(R1 = 150k Ω, C1 = 50pF)FIGURE 21.HC4046A TYPICAL VCO FREQUENCY vs VCO IN(R1 = 5.6k Ω, C1 = 50pF)FIGURE 22.HC4046A TYPICAL CHANGE IN VCO FREQUENCYvs AMBIENT TEMPERATURE AS A FUNCTION OF R1 (V CC = 3V)90706050403020100123456VCO IN (V)V C O F R E Q U E N C Y (H z )C1 = 0.1µF R1 = 1.5MV CC = 3VV CC = 4.5VV CC = 6V80800600500400300200100123456VCO IN (V)V C O F R E Q U E N C Y (H z )C1 = 0.1µF R1 = 150KV CC = 3VV CC = 4.5VV CC = 6V7001814121086420123456VCO IN (V)V C O F R E Q U E N C Y (k H z )C1 = 0.1µF R1 = 5.6kV CC = 3VV CC = 4.5VV CC = 6V1614001000800600400200123456VCO IN (V)V C O F R E Q U E N C Y (k H z )C1 = 50pF R1 = 150KV CC = 3VV CC = 4.5VV CC = 6V1200201612840123456VCO IN (V)V C O F R E Q U E N C Y (M H z )C1 = 50pF R1 = 5.6KV CC = 3VV CC = 4.5VV CC = 6V24R1 = 1.5MR1 = 150KR1 = 3KR1 = 1.5KVCO IN = 0.5 V CC C1 = 50pF, V CC = 3V R2 = OPEN241612840-4V C O F R E Q U E N C Y C H A N G E ,∆f (%)20-75-50-250255075AMBIENT TEMPERATURE, T A (o C)100125150-8-12-16。

74HC4046参考手册