台湾硬件工程师15年layout资料

一位PCB Layout工程师的十年心路历程

一位PCB Layout工程师的十年心路历程转眼已经毕业十年,从事PCB layout的工作也有很多年了,很多人把十年比作一个里程碑,确实,人生能有几个十年呢?况且,毕业后的这一个十年是人生中最充实最美好的十年,我想每个人都应该珍惜和铭记这个十年。

下面是我对自己这十年来的一个小结,没有功成名就,也没有锦衣玉食,我所收获的,是让我的生命充满阳光、乐观和喜悦。

希望大家看完这篇帖子后,能有一些感悟,让自己的心态和生活都能得到一些小小的改善。

刚毕业之时,有幸进到一家国内较有名气的家电公司,实习完之后就被分配到PCB layout这个岗位,虽然以前在学校时接触过这个东西,但那时只是一个初步的认识,没有太深的了解。

所以刚分配到这个岗位上来,感觉还是蛮新鲜的。

当时我们主要是做家电类产品的PCB Layout。

我们从电路原理、EDA软件、设计规则、生产工艺等一项项的学习、练习、熟悉,随着一块块小板在自己的精心打理之后,变为具有实际生产力意义的一件产品,内心是相当的满足,经常说的个人价值,仿佛就这样被体现出来了。

在这样的小成就心态中,劲头十足的干了一两年。

而随着时间的推移,渐渐的感觉心态开始变了,完全不是当初的感觉了,枯燥、纠结、迷惘等等是此时所有的想法,总感觉自己就是一个比EDA软件更智能一些的布线软件,一个靠饭和水来补给能量的肉体机器。

另外由于PCB layout的性质,总是要听从于硬件工程师或结构工程师的,感觉与他们相比,自己低一个等级,加上当时工资也不是很高,内心逐渐产生自卑心理。

当时一度想换一个职业,或是换一个行业,但在大公司工作过几年的人应该知道,当你熟悉了那个环境,并产生一定依赖感之后,就像温水里的青蛙一样,贪图安定的生活、享受轻松的工作环境,想要跳出来是何等的艰难抉择。

就这样痛苦挣扎了很久很久之后,终于还是狠下心决定离开。

不干PCB layout之后,感觉浑身都轻松不少,再也不用理会那些密密麻麻的飞线和挤的“头破血流”的元器件了,一切都成往事随风而去,我要开始新的生活。

layout硬件设计流程

layout硬件设计流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!1. 系统规划确定硬件系统的功能和性能要求。

制定设计规格和技术指标。

硬件工程师就业发展经历

硬件工程师就业发展经历

硬件工程师的就业发展经历通常包括以下几个阶段:

1. 基础技术岗位:刚入行的硬件工程师通常会从基础的技术岗位开始,如电路设计助理、PCB Layout 工程师等。

在这个阶段,他们主要负责电路板的布线和设计,以及协助高级工程师完成更复杂的任务。

2. 初级工程师岗位:在积累了一定的经验和技术后,硬件工程师通常会晋升到初级工程师的岗位。

在这个阶段,他们将开始独立承担一些项目,并与其他团队成员合作,如软件工程师和产品经理等。

3. 中级工程师岗位:随着经验的增加和技术的提升,硬件工程师将进一步晋升到中级工程师的岗位。

在这个阶段,他们将负责更复杂的项目和产品,并需要承担一定的团队管理职责,如领导一个小组或负责某个特定的产品线。

4. 高级工程师岗位:在达到高级工程师的岗位后,硬件工程师将具备丰富的技术经验和项目管理能力。

他们将负责制定技术战略和方向,领导跨部门的硬件开发团队,并与其他高级管理人员合作,以确保公司硬件产品的成功开发和上市。

5. 技术管理岗位:一些硬件工程师在职业发展过程中可能会选择进入技术管理的岗位。

在这个阶段,他们将不再直接参与硬件开发工作,而是负责管理整个硬件团队的工作,制定技术战略和规划,以及协调与其他部门的合作。

总体来说,硬件工程师的就业发展经历是一个不断学习和成长的

过程。

他们需要保持对新技术和新趋势的关注,不断提升自己的技能和知识水平,以适应不断变化的市场需求和行业竞争。

同时,他们也需要具备良好的沟通能力和团队合作精神,以更好地与同事和客户进行合作。

硬件Layout元器件布线规范篇

硬件Layout元器件布线规范篇目录概述 (3)1.1.C OMMON R OUTING R ULE (3)1.2.PWM的布线 (15)1.3.CLK的布线 (21)1.4.RJ45 TO T RANSFORMER的布线 (25)1.5.SFP的布线XFP的布线 (28)1.6.SGMII,GMII(RGMII),MII的走线(MAC TO PHY端) (33)1.7.POE部分的布线 (38)1.8.RS485布线 (46)1.9.CPU子系统的布线 (47)概述本文是用来描述硬件研发部元器件布线设计规范手册,从EMI,散热,噪声,信号完整性,电源完整性,等角度,来规范元器件布线设计。

此部分的Check应该Layout 布线阶段执行,并在Layout Review阶段做Double Check,若升级时Key Component 有更改,需要对以下内容再次Check。

Common Routing Rule1.1.1传输线传输线分为2种:微带线(Microstrip)和带状线(stripline)微带线(Microstrip):一般走在外层的Trace.带状线(stripline):一般走内层的 Trace.微带线与带状线的特征阻抗不一样,必须避免不同形态的传输线存在于不同的层面上。

1.1.2跨Plane高频信号走线必须注意不跨不同的Power Plane的问题,否则会因为回流路径不好造成信号完整性的问题。

铜箔在VCC GND Plane 层面尽量避免有连续的破孔出现,如有,请确认不会造成对电源完整性,和参考平面有影响。

如下图所示:图1第一层有2个不同的Plane AGND&DGND,图2 CLK Trace 同时跨在AGND与DGND,此信号严重会受到干扰。

所以此类问题一定要检查一下!1.1.3绕线1, Serpentine Trace (蛇形线):一般在BUS和CLK应用上,为了要求等长,必须较短的Trace要求绕线增加长度,方能达到所需的要求。

DDR3-硬件设计和-Layout-设计

冲和下冲等)。

终端匹配方案

设计者应该采用主流的终端匹配方案,像商业电脑主板那样的设计,ODT 终端匹配被应用在

数据总线上,地址/命令和控制线也应通过电阻连接到 VTT。当然,其它的终端匹配也是有

效的,但最好通过仿真来验证,确保信号质量满足要求。

3

终端匹配电阻的选择,其功耗是否满足芯片制造商的要求。

功耗计算 Power = x RT

4

假如数据线组增加了外部终端匹配电阻,请查看数据线组是否与其他 DDR3

信号组远离/隔离。

注:因为在 DDR3 数据组中通常优先选用内部 ODT 终端匹配,额外电阻是不

需要的。当然,假如不用 ODT 电阻,那么就需要增设外部电阻器了。

5

请查看 VTT 电阻 RT 布局是否正确,RT 终端电阻应该直接连接到 DDR 总线末端

4 / 13

序号

27

28 29 30

描述

该在同一层布线,并且保证过孔数量的一致性。

注:一些 DDR 芯片数据线接口是 32 位的。

通道 0:MDQ(7:0),MDM(0),MDQS(0),

(0)

通道 1:MDQ(15:8),MDM(1),MDQS(1),

(1)

通道 2:MDQ(23:16),MDM(2),MDQS(2),

VREF 是否合理去耦,源端和终端都应布置一个 0.1uF 电容。

VREF 参考源是否会随 VDDQ、温度、噪声变化,这个变化是否满足 JEDEC 要求。

VREF 电流是否满足系统(DDR 和处理器)需求。

如果采用电阻分压网络产生 VREF,那么请保证电阻阻值和至少 1%的精度。

Routing

建议 DDR3 布线顺序如下:

版图设计工程师(layout)岗位职责职位要求

版图设计工程师(layout)岗位职责职位要求

岗位职责:

1. 与项目经理、客户代表和设计团队协作,负责电气、机械、

计算机硬件等领域的版图设计和审查工作。

2. 根据客户需求和项目要求,制定和实施各种版图设计方案,

并做必要的修改和调整。

3. 确保版图符合相关设计标准和指南,以及符合制造和装配过

程中的技术要求和限制。

4. 协助设计团队完成产品原型的制造和测试,确保产品具有良

好的功能和性能。

5. 维护版图库和文档,确保版本管理和更新等工作的顺利进行。

职位要求:

1. 至少本科学位或同等学历,电气、机械、计算机等相关专业

优先。

2. 对版图设计工具(如OrCAD、PADS等)有丰富的经验和熟练

操作能力。

3. 熟悉电路设计和PCB设计的基本流程和方法,掌握相关技术

和规范。

4. 具有良好的沟通和协作能力,能与团队成员、客户和合作伙

伴建立良好的关系。

5. 具有高度的自我管理和组织能力,能够在高压力和短时间内

完成任务。

6. 熟悉国内外电气、机械、计算机硬件产品设计和行业发展趋势。

7. 具有优秀的英语听说读写能力,具备跨文化沟通的能力。

2024年layout工程岗位职责13篇

2024年layout工程岗位职责13篇目录第1篇pcb layout工程师岗位职责、要求第2篇硬件layout工程师岗位职责硬件layout工程师职责任职要求第3篇版图工程师layout岗位职责第4篇高级layout工程师岗位职责第5篇pcblayout工程师岗位职责职位要求第6篇版图设计工程师(layout)岗位职责职位要求第7篇layout设计工程师岗位职责第8篇layout电子工程师岗位职责第9篇模拟layout工程师岗位职责第10篇工程师layout岗位职责第11篇硬件layout工程师岗位职责第12篇高级layout工程师岗位职责职位要求第13篇layout工程师岗位职责高级layout工程师岗位职责高级pcb layout工程师同为数码深圳市同为数码科技股份有限公司,同为数码,同为股份工作职责:1、独立进行公司产品pcb layout设计;2、和pcb板厂沟通,回复pcb板厂的相关工程资料沟通函;3、能独立完成从导入网表到出gerber文件工作;4、解决产品emc的问题;任职资格:1、本科及以上学历,电子通信相关专业;2、至少5年以上同等工作经验,具备较强的理论知识,有非常丰富的pcb layout经验,资深级别工程师;3、熟悉pcb生产工艺,做事责任心强,有pcb封装建库经验;4、熟悉smt制作流程及工艺,能和smt车间就相关问题进行明晰沟通,促进smt高效生产;5、熟练使用pcb layout工具—allegro 16.3及以上版本 ,熟练使用原理图设计工具or cad ,能看懂结构图以及拼板使用。

硬件layout工程师岗位职责硬件工程师— layout 江苏科曜能源科技有限公司江苏科曜能源科技有限公司,科曜职责描述:1、负责pcsbmsems等产品的pcb布板;2、负责维护元器件标准库及制定产品pcb设计规范;3、负责针对pcb布局、走线规则、可制造性等提出解决方案;4、负责layout的输出文档,制作gerber file及钢网文件等资料;5、负责pcb打样及smt过程,配合其他部门解决问题。

电子硬件工程师工作职责

电子硬件工程师工作职责

1、负责电路硬件设计工作,原理图设计,PCB layout设计

2、负责电路焊接与调试,样机制作,熟悉材料参数和性能

3、负责电子材料的选型与测试确认,会一种以上开关电源设计

4、负责相关设计文档编制,测试文档编制。

1负责无人机挂载产品项目规划分析制定实施方案分解控制进度;

2负责arm硬件及单片机开发设计,进行产品架构设计与方案选型;

3产品开发过程主体框架,具体流程设计及相关技术文档编写和输出;

4产品开发整个过程的研究设计底层开发调试集成验证等管理协调工作;

1、负责医疗仪器产品电子系统设计开发调试;

2、负责电子器件选型,PCB设计,layout,及文档编写;

3、负责电子物料的采购申请检验测试;

4、负责仪器电子系统在产品周期中的维护和改进。

5、完成上级交代的`工作任务,保证项目进度;

1、参与产品需求分析,提出硬件设计解决方案;

2、完成硬件电路原理图、选型、PCB设计、硬件调试、系统联调等工作;

3、编写硬件电路生产调试用的技术工艺文件;

4、参与研发项目管理以及产品改进工作。

1参与项目需求分析,参与方案的.设计,BOM报价;

2负责电控系统元器件选型和原理图PCB设计;

4参与样机生产调试工作;

5负责完成产品电控文档的撰写;

6对产品的组装生产调试进行技术指导。

LAYOUT规范

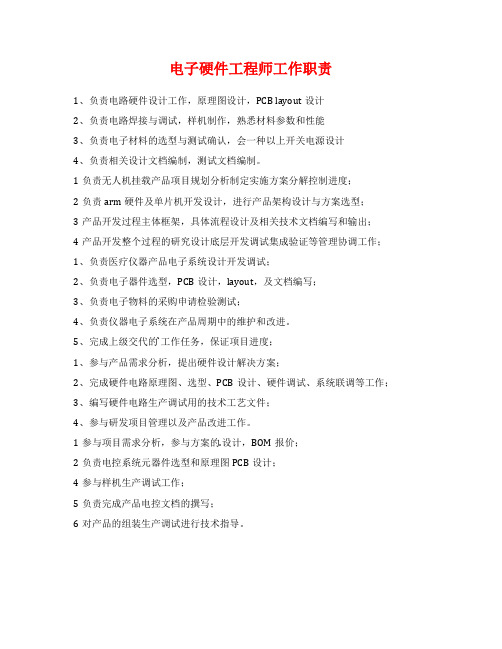

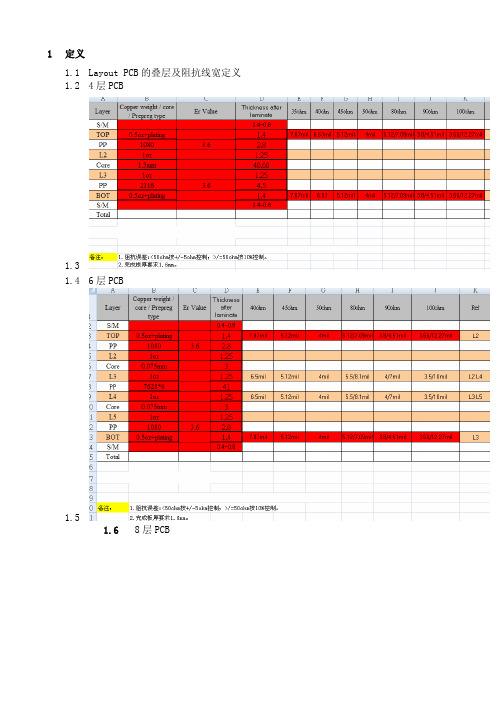

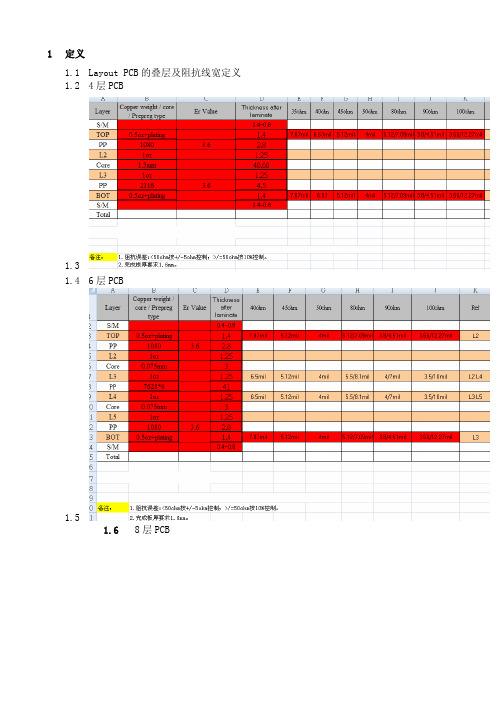

1定义1.1Layout PCB的叠层及阻抗线宽定义1.24层PCB1.31.46层PCB1.51.68层PCB1.7.2要求2.1设计流程:2.1.1 评审通过后的原理图2.1.2 网表2.1.3 PCB 架构(外形尺寸,螺丝孔,定位孔及禁布区)2.1.4 如有增加新器件,需提供新的封装资料(PCB FOOTPRINT)2.1.5 根据单板结构图或对应的标准板框, 创建PCB设计文件2.1.6 布局及布线2.1.7 工艺设计要求2.1.8 设计评审2.2元件的布局:2.2.1创建网络表2.2.1.1 网络表是原理图与PCB的接口文件,PCB设计人员应根据所用的原理图和PCB设计工具的特性,选用正确的网络表格式,创建符合要求的网络表。

2.2.1.2 创建网络表的过程中,应根据原理图设计工具的特性,积极协助原理图设计者排除错误。

保证网络表的正确性和完整性。

2.2.1.3 确定器件的封装(PCB FOOTPRINT).2.2.1.4 创建PCB板 根据单板结构图或对应的标准板框, 创建PCB设计文件;注意正确选定单板坐标原点的位置,原点的设置原则:单板右边和下边的延长线交汇点。

板框四周倒圆角,倒角半径5mm。

特殊情况参考结构设计要求。

2.2.2 布局前设置2.2.2.1 根据结构图设置板框尺寸,按结构要素布置安装孔、接插件等需要定位的器件,并给这些器件赋予不可移动属性。

按工艺设计规范的要求进行尺寸标注。

2.2.2.2 根据结构图和生产加工时所须的夹持边设置印制板的禁止布线区、禁止布局区域。

根据某些元件的特殊要求,设置禁止布线区。

2.2.2.3 综合考虑PCB性能和加工的效率选择加工流程。

加工工艺的优选顺序为:元件面单面贴装——元件面贴、插混装(元件面插装焊接面贴装一次波峰成型)——双面贴装——元件面贴插混装、焊接面贴装。

2.3 布局规则2.3.1遵照“先大后小,先难后易”的布置原则,即重要的单元电路、核心元器件应当优先布局.2.3.2 布局中应参考原理框图,根据单板的主信号流向规律安排主要元器件.2.3.3 布局应尽量满足以下要求:总的连线尽可能短,关键信号线最短;高电压、大电流信号与小电流,低电压的弱信号完全分开;模拟信号与数字信号分开;高频信号与低频信号分开;高频元器件的间隔要充分.2.3.4 相同结构电路部分,尽可能采用“对称式”标准布局;2.3.5 按照均匀分布、重心平衡、版面美观的标准优化布局;2.3.6 器件布局栅格的设置,一般IC器件布局时,格点应为50 mil,小型表面安装器件,如表面贴装元件布局时,格点设置应不少于10mil。

LAYOUT规范

1定义1.1Layout PCB的叠层及阻抗线宽定义1.24层PCB1.31.46层PCB1.51.68层PCB1.7.2要求2.1设计流程:2.1.1 评审通过后的原理图2.1.2 网表2.1.3 PCB 架构(外形尺寸,螺丝孔,定位孔及禁布区)2.1.4 如有增加新器件,需提供新的封装资料(PCB FOOTPRINT)2.1.5 根据单板结构图或对应的标准板框, 创建PCB设计文件2.1.6 布局及布线2.1.7 工艺设计要求2.1.8 设计评审2.2元件的布局:2.2.1创建网络表2.2.1.1 网络表是原理图与PCB的接口文件,PCB设计人员应根据所用的原理图和PCB设计工具的特性,选用正确的网络表格式,创建符合要求的网络表。

2.2.1.2 创建网络表的过程中,应根据原理图设计工具的特性,积极协助原理图设计者排除错误。

保证网络表的正确性和完整性。

2.2.1.3 确定器件的封装(PCB FOOTPRINT).2.2.1.4 创建PCB板 根据单板结构图或对应的标准板框, 创建PCB设计文件;注意正确选定单板坐标原点的位置,原点的设置原则:单板右边和下边的延长线交汇点。

板框四周倒圆角,倒角半径5mm。

特殊情况参考结构设计要求。

2.2.2 布局前设置2.2.2.1 根据结构图设置板框尺寸,按结构要素布置安装孔、接插件等需要定位的器件,并给这些器件赋予不可移动属性。

按工艺设计规范的要求进行尺寸标注。

2.2.2.2 根据结构图和生产加工时所须的夹持边设置印制板的禁止布线区、禁止布局区域。

根据某些元件的特殊要求,设置禁止布线区。

2.2.2.3 综合考虑PCB性能和加工的效率选择加工流程。

加工工艺的优选顺序为:元件面单面贴装——元件面贴、插混装(元件面插装焊接面贴装一次波峰成型)——双面贴装——元件面贴插混装、焊接面贴装。

2.3 布局规则2.3.1遵照“先大后小,先难后易”的布置原则,即重要的单元电路、核心元器件应当优先布局.2.3.2 布局中应参考原理框图,根据单板的主信号流向规律安排主要元器件.2.3.3 布局应尽量满足以下要求:总的连线尽可能短,关键信号线最短;高电压、大电流信号与小电流,低电压的弱信号完全分开;模拟信号与数字信号分开;高频信号与低频信号分开;高频元器件的间隔要充分.2.3.4 相同结构电路部分,尽可能采用“对称式”标准布局;2.3.5 按照均匀分布、重心平衡、版面美观的标准优化布局;2.3.6 器件布局栅格的设置,一般IC器件布局时,格点应为50 mil,小型表面安装器件,如表面贴装元件布局时,格点设置应不少于10mil。

layout工程师个人年终总结

Layout工程师个人年终总结过去的一年,作为Layout工程师,我参与了多项重要工程项目,通过实践和学习,不断提升自己的专业技能。

本文旨在对过去一年的工作进行总结,分析自己在工作中的得与失,并提出改进措施,以便更好地为未来的工作做好准备。

一、工作成果1.项目完成情况:在过去的一年里,我参与了X个重要工程项目,其中包括X个大型集成电路设计和X个PCB板级设计。

在所有项目中,我均按照项目进度要求完成了Layout设计任务,确保了项目的顺利进行。

2.专业技能提升:通过参与实际项目,我对Layout设计流程、工具使用以及团队协作等方面有了更深入的理解。

在解决问题的过程中,我不断积累经验,提高了自己的专业技能水平。

3.团队协作:在项目中,我与电路设计工程师、硬件工程师以及项目经理等多个团队成员紧密合作,共同推进项目进度。

通过与团队成员的沟通交流,我提高了自己的团队协作能力,也增进了彼此的了解与信任。

4.创新尝试:在过去的一年中,我努力尝试新的设计方法和工具,以提高设计效率和质量。

例如,在某个项目中,我成功应用了一种新的自动布线算法,有效减少了布线时间和错误率。

二、问题分析尽管在过去的一年中取得了一些成果,但我也意识到自己在工作中存在一些问题。

具体表现在以下几个方面:1.时间管理:在某些项目中,由于时间管理不当,导致项目进度受到了一定影响。

我需要加强时间管理能力的培养,合理安排工作和生活时间。

2.沟通效率:在与团队成员沟通时,有时会出现信息传递不畅或者误解的情况。

我需要更加注重沟通技巧的提升,确保信息准确、及时地传递。

3.细节把控:在Layout设计过程中,有时会因为疏忽导致一些细节问题没有被及时发现和处理。

我需要加强自己的细心程度,提高对细节的把控能力。

4.持续学习:随着技术的不断发展,我需要保持对新技术、新工具的学习和应用,以便更好地适应未来的工作需求。

三、改进措施针对以上问题,我提出以下改进措施:1.制定详细的时间管理计划:在项目开始前,制定详细的时间管理计划,合理分配各个阶段的任务和时间。

高级硬件工程师任职要求

高级硬件工程师任职要求

高级硬件工程师的任职要求包括以下几点:

1. 学历要求:本科及以上学历,电子信息工程、通信工程等相关专业。

2. 经验要求:具备5年以上的硬件开发经验,有实际产品设计经验,能够独立进行原理图设计和PCB layout。

3. 技能要求:有扎实的电路专业理论基础,有嵌入式系统和模拟电路设计经验。

精通TP、屏、摄像头、电池、电源等部件中的至少一个的原理以及应用。

熟悉硬件设计的各种设计软件,熟练使用各种测试仪器和工具,熟悉智能终端可靠性测试指标。

4. 其他要求:具备良好的沟通能力、执行能力和团队合作精神,工作态度端正,专注于工作,以结果为导向。

具体要求可能会根据不同的公司有所差异,建议根据具体岗位和公司进行查询。

硬件layout工程师岗位职责

硬件layout工程师岗位职责硬件Layout工程师是指在设计硬件电路板时负责进行电路板布局的专业人员。

他们的主要职责包括以下几个方面:1.电路板设计:Layout工程师负责制作电路板的设计方案,尤其是对于大规模复杂的电路板,需要对整个系统的结构进行全面考虑,编制电路板布线图和器件布置图,并制定相应的规范和标准,在此基础上制作出满足系统要求的可靠的电路板设计。

2.电路板布线:Layout工程师需要根据电路板设计方案进行电路板布线,设计电路板布线样式,并保证布线的规范和可靠性。

同时,在制定布线技术方案时,要考虑电路板布局的紧密程度、信号传输的速度和信号的稳定性,以满足系统的性能要求。

3.器件选型:Layout工程师需要根据设计要求合理选择电路板器件,参与电路板原理性设计,同时对电路板器件的尺寸、引脚等进行优化,使之前后兼容、占用空间最小,并能满足应用要求,提高电路板的设计效率与可靠性。

4.测试调试:Layout工程师需要参与电路板测试、调试和故障排除工作,确保电路板的正常运行和可靠性,并提供相应的技术支持和常规维护。

5.规范标准:Layout工程师要负责制定公司的电路板布局规范和标准,旨在保证公司每一位Layout工程师的电路板设计质量,提高公司的电路板设计标准,规范员工的工作流程。

总之,硬件Layout工程师作为电子设计领域的专业人员,他们不仅需要具备深厚的电子设计理论知识,还需要有较强的团队协作和沟通能力,能够与其他相关工程师协同工作,共同推进项目进度。

同时,Layout工程师在电路设计过程中需要保持高度的责任心和专注力,以确保协作的其他工程师能够得到满意的产品。

台湾硬件工程师15年layout经验总结

台湾硬件⼯程师15年layout经验总结LAYOUT REPORT⽬录Ver.0.2 LAYOUT REPORT (1)⽬录 (1)1.PCB LAYOUT 术语解释(TERMS) (2)2.Test Point : ATE 测试点供⼯⼚ICT 测试治具使⽤ (2)3. 基准点 (光学点) -for SMD: (4)4.标记 (LABEL ING) (5)5.VIA HOLE PAD (5)6.PCB Layer 排列⽅式 (5)7.零件布置注意事项 (PLACEMENT NOTES) (5)8.PCB LAYOUT 设计 (6)9.Transmission Line ( 传输线 ) (8)10.General Guidelines – 跨Plane (8)11.General Guidelines – 绕线 (9)12.General Guidelines – Damping Resistor (10)13.General Guidelines - RJ45 to Transformer (10)14.Clock Routing Guideline (12)15.OSC & CRYSTAL Guideline (12)16.CPU -+ RAM-+FLASH (14)17.General Guidelines –Decoupling Capacitor (14)18.POWER 部分 (15)19.GND & Vcc Plan 切割 (17)20.DRC : Design Rule Check (19)21. CAM 输出/输出⽂件(参考gerber file 流程图) (20)22. 其他注意事项 (21)23.PCB 制作规范填写注意事项 (23)1.PCB LAYOUT 术语解释(TERMS)1. COMPONENT SIDE(零件⾯、正⾯)︰⼤多数零件放置之⾯。

2.SOLDER SIDE(焊锡⾯、反⾯)。

硬件工程师必备layout_check

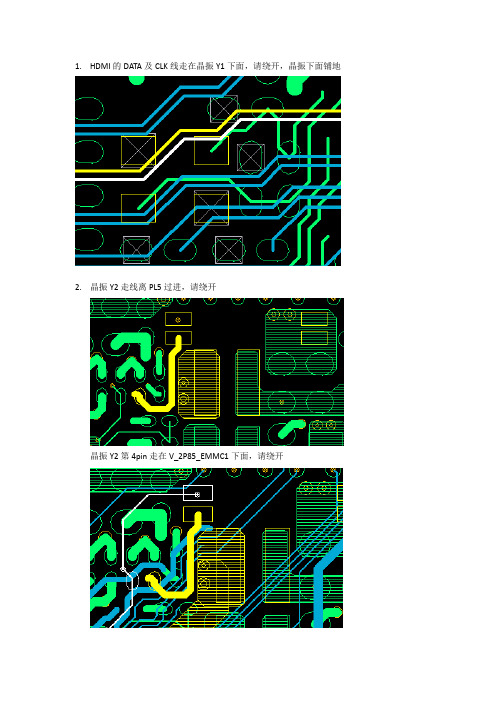

1.HDMI的DATA及CLK线走在晶振Y1下面,请绕开,晶振下面铺地2.晶振Y2走线离PL5过进,请绕开晶振Y2第4pin走在V_2P85_EMMC1下面,请绕开晶振Y2下面有PMIC_SPI_DEBUG,DISP_SEC_BKLT_PWM走线,请绕开。

3.晶振Y3下面届时请铺地4.晶振Y4下面届时请铺地5. 5. 晶振Y5下面届时请铺地6.WIFI天下下面禁止走线B_CAM_DN/USB_CAM_D 走线线宽线距请按规则走FB1/FB2走在LVDS上面的部分需要绕开+V3.3S,PU6,VLED的power’网络下走有LVDS差分线,要绕开N23265612这条网络往上拉一下,避开LVDS的走线。

U3的power net +VSYS目前15mil,都加宽至20mil。

3G的如下CN3 pin1/3/5/7/9/11/13/15每个power走线,都加宽至20milVUSB_PHY网络都加宽至少15mil。

最好能到20milOSC_CLK_OUT_0与JTAG2_TDO这段走线的间距加大至10mil以下4路CLK的线宽线距至少保持1:3,请加大间距OSC_CLK_OUT_0/OSC_CLK_OUT_1OSC_CLK_OUT_2/OSC_CLK_OUT_3V_1P80_DEBUG与I2C_0_SCL的间距拉开V_1P80_DEBUG与SLP_CLK2距离拉开V_3P30_DEBUG与V_1P80_DEBUG在此处走在一起,请处理HDMI_CLK_DP/ HDMI_CLK_DN走在晶振Y1下面,需要绕开。

晶振Y3供电pin第4pin下面的CSB_SNSCLK3请绕开晶振Y6下面铺地USBPORT_DP0距离BATP过近,加大间距USB_CAM_DP/USB_CAM_DN+V3.3A到EMMC的供电部分加宽至20mil+V3.3A到EMMC的供电部分加宽至20mil此处VCC加打一个VIA将SPI_1_CLK该处拉直(R62右下),在此处打一个via将TOP,GND03,GND05,GND08连接起来此处的GND(C62下面)继续打到GND05和GND08此处(PC43)2个via请打通TOP,GND03,GND05,GND08。

硬件工程师手册(全)

§2.2.1 §2.2.2

第三节

与硬件开发相关的流程文件介绍-------------------------------------------- 11

§2.3.1 §2.3.2 §2.3.3 §2.3.4 §2.3.5 §2.3.6

第三章 第一节 第二节

硬件 EMC 设计规范--- --- ---- ---- ---- --- ---- ---- ---- --- ---- ---- ---- --- ---- ---- --- 13 CAD 辅助设计--------------------------------------------------------------------- 14 可编程器件的使用-------------------------------------------------------------- 19

硬件开发的基本过程----------------------------------------------------------------- 4 硬件开发的规范化-------------------------------------------------------------------- 4 硬件工程师职责----------------------------------------------------------------------- 4 硬件工程师基本素质与技术---------------------------------------------------标准: 串口设计: 并口设计及总线设计: RS-232 接口总线 RS-422 和 RS-423 标准接口联接方法 RS-485 标准接口与联接方法 20mA 电流环路串行接口与联接方法

硬件工程师必备layout_check

1.HDMI的DATA及CLK线走在晶振Y1下面,请绕开,晶振下面铺地2.晶振Y2走线离PL5过进,请绕开晶振Y2第4pin走在V_2P85_EMMC1下面,请绕开晶振Y2下面有PMIC_SPI_DEBUG,DISP_SEC_BKLT_PWM走线,请绕开。

3.晶振Y3下面届时请铺地4.晶振Y4下面届时请铺地5. 5. 晶振Y5下面届时请铺地6.WIFI天下下面禁止走线B_CAM_DN/USB_CAM_D 走线线宽线距请按规则走FB1/FB2走在LVDS上面的部分需要绕开+V3.3S,PU6,VLED的power’网络下走有LVDS差分线,要绕开N23265612这条网络往上拉一下,避开LVDS的走线。

U3的power net +VSYS目前15mil,都加宽至20mil。

3G的如下CN3 pin1/3/5/7/9/11/13/15每个power走线,都加宽至20milVUSB_PHY网络都加宽至少15mil。

最好能到20milOSC_CLK_OUT_0与JTAG2_TDO这段走线的间距加大至10mil以下4路CLK的线宽线距至少保持1:3,请加大间距OSC_CLK_OUT_0/OSC_CLK_OUT_1OSC_CLK_OUT_2/OSC_CLK_OUT_3V_1P80_DEBUG与I2C_0_SCL的间距拉开V_1P80_DEBUG与SLP_CLK2距离拉开V_3P30_DEBUG与V_1P80_DEBUG在此处走在一起,请处理HDMI_CLK_DP/ HDMI_CLK_DN走在晶振Y1下面,需要绕开。

晶振Y3供电pin第4pin下面的CSB_SNSCLK3请绕开晶振Y6下面铺地USBPORT_DP0距离BATP过近,加大间距USB_CAM_DP/USB_CAM_DN+V3.3A到EMMC的供电部分加宽至20mil+V3.3A到EMMC的供电部分加宽至20mil此处VCC加打一个VIA将SPI_1_CLK该处拉直(R62右下),在此处打一个via将TOP,GND03,GND05,GND08连接起来此处的GND(C62下面)继续打到GND05和GND08此处(PC43)2个via请打通TOP,GND03,GND05,GND08。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LAYOUT REPORT目錄Ver.0.2 LAYOUT REPORT (1)目錄 (1)1. PCB LAYOUT 術語解釋(TERMS) (2)2. Test Point : ATE測試點供工廠ICT測試治具使用 (2)3. 基準點 (光學點) -for SMD: (4)4. 標記 (LABEL ING) (5)5. VIA HOLE PAD (5)6. PCB Layer排列方式 (5)7.零件佈置注意事項 (PLACEMENT NOTES) (5)8. PCB LAYOUT設計 (6)9. Transmission Line ( 傳輸線 ) (8)10.General Guidelines – 跨Plane (8)11. General Guidelines – 繞線 (9)12. General Guidelines – Damping Resistor (10)13. General Guidelines - RJ45 to Transformer (10)14. Clock Routing Guideline (12)15. OSC & CRYSTAL Guideline (12)16. CPU Î RAMÎFLASH (14)17. General Guidelines –Decoupling Capacitor (14)18.POWER部分 (15)19. GND & Vcc Plan 切割 (17)20. DRC : Design Rule Check (19)21. CAM輸出/輸出文件(參考gerber file流程圖) (20)22. 其他注意事項 (21)23.PCB製作規範填寫注意事項 (23)1. PCB LAYOUT 術語解釋(TERMS)PONENT SIDE(零件面、正面)︰大多數零件放置之面。

2.SOLDER SIDE(焊錫面、反面)。

3.SOLDER MASK(止焊膜面)︰通常指Solder Mask Open之意。

4.TOP PAD︰在零件面上所設計之零件腳PAD,不管是否鑽孔、電鍍。

5.BOTTOM PAD:在銲錫面上所設計之零件腳PAD,不管是否鑽孔、電鍍。

6.POSITIVE LAYER:單、雙層板之各層線路;多層板之上、下兩層線路及內層走線皆屬之。

7.NEGATIVE LAYER:通常指多層板之電源層。

8.INNER PAD:多層板之POSITIVE LAYER內層PAD。

9.ANTI-PAD:多層板之NEGATIVE LAYER上所使用之絕緣範圍,不與零件腳相接。

10.THERMAL PAD:多層板內NEGATIVE LAYER上必須零件腳時所使用之PAD,一般稱為散熱孔或導通孔。

11.PAD (銲墊):除了SMD PAD外,其他PAD之TOP PAD、BOTTOM PAD及INNER PAD之形狀大小皆應相同。

12.Moat : 不同信號的 Power& GND plane 之間的分隔線13.Grid : 佈線時的走線格點2. Test Point : ATE測試點供工廠ICT測試治具使用ICT 測試點 LAYOUT注意事項:PCB的每條TRACE都要有一個作為測試用之TEST PAD(測試點),其原則如下:1.一般測試點大小均為30-35mil,元件分布較密時,測試點最小可至30mil.測試點與元件PAD的距離最小為40mil。

2.測試點與測試點間的間距最小為50-75mil,一般使用75mil。

密度高時可使用50mil,3.測試點必須均勻分佈於PCB上,避免測試時造成板面受力不均。

4.多層板必須透過貫穿孔(VIA)將測試點留於錫爐著錫面上(Solder Side)。

5.測試點必需放至於Bottom Layer6.輸出test point report(.asc檔案powerpcb v3.5)供廠商分析可測率7.測試點設置處:SetupÆpadsÆstacks點選此處新建一個pad設置pad大小新增加測試點名稱8.自動載入測試點100%:TOOLS ÆDFT Audit Æ下圖3. 基準點 (光學點) -for SMD:為了PICK & PLACE 機器自動放置SMD 零件之基準設定,因此必須在板子四周加上光學點。

1.在SOLDER MASK 範圍內不可有任何TRACE, SILK SCREEN 及VIA,並且在下 一層之相同位置必須為全部銅箔。

2. PCB 光學校正點應以圓形做法為準,以便於SMT 機器的定位。

四邊有 PIN 之IC pin1及其對角端各作一個基準點,此基準點為1.0mm 圓形 PAD,其SOLDER MASK 為3.0mm 圓形;此SOLDER MASK 內不可有其他之* 自動100加入%Test Point 設置 使用此項TRACE、SILK-SCREEN、VIA 及開孔。

3. 光學點之位置,必須與SMD 零件同一面(即零件面),如為雙面SMD 板,則 雙面亦須作光學點。

4. 光學點需放在SMD 板四角落,DOT 中心點距離板邊至少5.0mm。

5.1. PCB V-CUT Î做在突出的零件邊(RJ45),寬度8mm,距離V-CUT 邊緣往板內X、Y 軸5‚5mm 處放置孔徑4mm 固定孔5.2.若是pcb RJ45處空間足夠,需放置在實際板框邊緣往內X,Y 軸5‚5mm 處。

4. 標記 (LABEL ING)每一種PCB 之設計均須將“板名、R Logo 一定要放在TOP 層、生產日期、字令貼紙Label ”作在pcb SILK SCREEN 上。

需注意後加在PCB 中的圖形(如一般標示線)是否會造成信号短路。

5. VIA HOLE PAD一般製程 VIA HOLE PAD 大小(使用圓形PAD)6. PCB Layer 排列方式7.零件佈置注意事項 (PLACEMENT NOTES)1. 位置固定之零件,必須依機構圖上所標示之位置擺放,方向及腳位亦須注意。

2. 機構圖上雖有標示位置,但非固定位置之零件,可依LAYOUT 之需要加以調整,但須經過本公司相關人員之許可。

3. PLACEMENT 時請注意機構圖上之各種限制區域,例如:零件高度、可插拔零件(JUMPER、CONNECTOR 等)之限制區域…等。

4. 所有零件之方向必須垂直或水平於板邊置放,而相同包裝類型之零件方向請保持一致。

5. 注意可插拔零件四周之空間是否不致妨礙人工插拔動作。

VIA 孔徑 PAD 直徑 ANTIPAD Pcb 層數 10mil 20mi 30mil 4層板 12mil 24mil 32mil 2層板14mil26mil32milGND Via(all pcb)6.過錫爐方向性的考量: PCB LAYOUT時所有元件應儘量依同一方向配置7.a.上下層零件PAD邊緣距離板邊至少4MM,(下限3MM)b.下層SMD零件距離DIP零件的PAD至少3MM(邊對邊)c.H4定位孔與RJ-45同方向, 且距離板邊X=5 ,Y =5MM,d.RJ-45下層零件距離板邊7MM8. PCB LAYOUT設計1.佈局前的準備 :先將layout軟體單位設置為mm, 避免載入機構圖時因單位不同產生比例問題 ; FileÆimportÆ.dxf ,將載入的機構圖放置於LAYER27(Assembly Drawing Top),2.畫出版框 : Draftin IconÆBoardoutline3.確定定位孔 : 螺絲孔定位4.板內元件局部高度控制: 繪製出禁止區Æ Draftin Icon ÆKeepout5.固定有條件限制的元件:先擺關鍵元件,面積比較大的元件,零散的元件6.輸入NETLIST : FileÆimport .asc ,import後出現的.err檔案必須逐一檢查問題直到出現 Import no error7.參照線路圖,結合機構,進行佈局8.對層定義﹑線寬﹑線距﹑過孔﹑全局參數等作設置z層定義: SetupÆlayer Definitionz線寬﹑線距﹑過孔 SetupÆdesign rules規則設置處:9.擺放零件時數位電路零與類比電路零件分開,尤其數位電路要遠離磁性元件,佈局同時把數位地與類比地先規劃雛形,避免走綫時再做大幅修改層定義設定處: SetupÆlayer Definition變更層數ON/OFF層面z手工佈線:參照線路圖進行欲佈線,檢查佈線是否符合要求,修改布線,並符合相應要求。

z走線規律:1、走線方式 ,盡量走短线,特别是小信号。

2、走線形狀同一層走線改變方向時,應走斜線(轉45度 )禁止走直角。

3、電源線與地線的設計40-100mil,高頻線用地線屏蔽。

4、多層板走線方向相互垂直,層間耦合面積最小;禁止層與層間平行走线。

5、VIA設計的控制。

9. Transmission Line ( 傳輸線 )z 傳輸線分2種 : Microstrip 及Stripline。

z Microstrip :一般走在外層的Trace 屬於Microstrip, 例如 Component size 及soldersize 的Trace。

z Stripline :一般走在內層的Trace 屬於Stripline。

z Microstrip& Stripline 的特性阻抗不一樣,必須避免不同型態的傳輸線存在於不同的層面上。

10.General Guidelines – 跨Planez 高頻訊號走線須注意不跨不同Power Plan 的問題,否則會因Return Path 不好造成信號不好。

z 銅箔在VCC GND Plan 層面盡量避免有連續破孔情形出現,z 如下圖:第2層有兩個不同Plane AGND 及DGND,圖(二)Clock trace 同時跨在 AGND 及DGND,此信號一定不好11. General Guidelines – 繞線● Serpentine trace (蛇行線):一般在Bus 或clock 應用上,常為了要求等長, 必須將較短的Trace 要求繞線增加長度,方能達到所要求的長度。

● 繞線須注意那些事項:首先要注意繞線本身的間距S,S間距越小,decouple效應越明顯,信號越差,所以S越大越好,但因空間有限,依3-W原則,S必須為2倍線寬為佳。

z何為3-W法則:例如當訊號寬度為5mils(W)時,則Trace兩旁的Space需為10mils(2W),如此可降低2線之件的Crosstalk效應,一般針對高頻訊號(例如CLK)而言,經常運用3-W法則來降低Crosstalk,或是用GND作屏敝。