第三章 TMS320VC5402 DSK的硬件结构与硬件设计

第三章 5402DSK硬件设计

5402DSK 硬件设计SMC34C60并行接口芯片功能说明:完成并行打印机接口信号与AT总线之间的转换,支持SPP、EPP、ECP并行接口,可与8位或16位外设接口,可将8比特或16比特的ISA数据分解为4比特或8比特的并口数据块。

在DSK中的作用是将并行口信号转化为能够与TBC 74ACT8990相连接的总线信号。

包括以下信号类型:数据总线:SD15—SD0地址总线:SA4—SA0控制总线:PP_SRDPP_SWRTBC_CSHPI_CSPP_CS2……74ACT8990测试总线控制器(TBC)功能说明:符合IEEE标准1149.1(JTAG标准)的主控器,带16比特的通用主机接口,’ACT8990测试总线控制器是TI测试集成电路的成员之一,支持IEEEE标准1149.1—1990(JTAG)边界扫描以帮助复杂电路板的生产制造,功能是控制JTAG串行测试总线。

JTAG串行测试总线需要的信号有:测试时钟(TCK),测试模式选择(TMS),测试数据输入(TDI),测试数据输出(TDO),这些信号可以直接连接到目标器件而不需要附加逻辑,TBC产生TMS和TDI信号给目标器件,从目标接收TDO信号,将测试时钟输入(TCKI)缓冲至测试时钟输出(TCKO)给目标器件使用,TMS、TDI和TDO信号可以直接或经过最多31bits延迟的流水线连接到目标,因为TBC可以配置为最多产生6个单独的TMS信号[TMS (5~0)],可以用来控制最多6个并接在一起的目标扫描路径(共享公共的TCK、TDI和TDO 信号)。

TBC最常见的操作是同步TCKI,测试关闭(TOFF\)输入信号用于目标接口的输出控制,测试复位(TRST\)输入用于TBC的硬件/软件复位。

另外,四个事件[EVENT(3—0)]I/O用于与目标装置的异步通信。

每个事件有自己的事件产生/检测逻辑,检测到的事件可用两个16bit 计数器进行计数,TBC在主处理器/控制器的控制下通过5bit地址总线[ADRS(4—0)]和16bit 读/写数据总线[DATA(15—0)]进行操作,读(RD)和写(WR)选通信号由严格的主机接口定时完成而与TCKI周期无关。

基于TMS320VC5402的DSP基本系统的设计

基于TMS320VC5402的DSP基本系统的设计Ξ姜 滨(华中科技大学光电子工程系 武汉 430074)摘 要本文以美国Texas Instruments(TI)公司C5000TM系列DSP中TMS320VC5402为例,介绍用Flash Rom和SRAM构建DSP基本应用系统的硬件设计方法,以及DSP硬件设计中应注意的几个问题。

关键词:DSP FPG A CPLD中图法分类号:TP391The Design of DSP B asic System based on TMS320VC5402Jiang Bin(Photoelectron Engineering Department,HUST,Wuhan430074)Abstract:This paper introduces the hardware design of DSP basic system constructed by Flash Rom and SRAM,taking TMS320VC5402of C5000TM serial from Texas Instruments(TI)for example,and proposes some is2 sues which we shall pay attention to in hardware design.K ey w ords:DSP,FPG A,CPLDClass number:TP391 数字信号处理(DSP)芯片以其高速、低功耗和高集成度在军事、航天等领域大显身手;随着半导体工艺的进步和工业民用领域的大量采用,近几年来,DSP价格大幅下调(某些品种价格已与单片机相当),而性能却不断提高,现已广泛应用于通信、工业控制和消费领域,DSP正日益成为现代信息产业的重要基石。

根据TI公司预测,DSP和Ana2 log器件将成为因特网时代的主导。

1 TI公司TMS320系列DSP目前,TI公司力推的主流DSP为C24X TM、C54X TM和C6000TM,C24X TX系列是16位定点DSP,以较高的性价比广泛应用于马达控制、工业数字控制、信息家电等方面; C54X TM系列是C5000TM中的第二代产品,其特点是高速、低功耗,最适合用于便携式设备(如手机、数码相机、PDA等)和对功耗有严格要求的地方;C6000TM是一个32位高性能的DSP,它包括C62xx、C64xx、C67xx三个系列(其中C67xx为点DSP),采用了Veloci TT 超长指令字(VL IW)结构,C62xx、C64xx、C67xx的单片处理速度最高可分别达到2400M IPS、4800M IPS和1GFLOPS,主要用Ξ收到本文时间:2002年11月19日于无线基站、网络、视频和图像处理领域,需要注意的是它的功耗较大和对PCB的设计、制板工艺要求较高。

TMS320VC5402的并行引导装载方案的研究与设计

TMS320VC5402的并行引导装载方案的研究与设计摘要:介绍了TMS320VC5402并行Bootloader的原理,分析了设计过程中需要考虑的重点问题并提出了解决问题的可靠的电路方案,设计的电路具有良好的可扩展性。

关键词:TMS320VC5402 Bootloader CPLD EPROMTMS320VC5402(以下简称C5402)是德州仪器公司1999年10月推出的性价比极高的定点数字信号处理器(DSP)。

与TMS32054X系列的其它芯片相比,C5402以其独有的高性能、低功耗和低价格特性,使得一推出就受到业内用户的欢迎。

它大多应用在如机顶盒(STB)、数字无线通信等要求能脱机运行的内嵌式系统中。

但它的内部结构和片内掩模的引导装载 (Bootloader)程序与C54X系列的其它DSP处理器有较大差异。

C5402为脱机运行提供了五种启动装载模式:HPI端口启动模式、标准串口启动模式、I/O口启动模式、串口EEPROM启动模式和并行启动方式。

对于以C5402为核心的独立系统中,并口加载方案被认为是最佳的。

因为前三种方案只适用于由其它处理器为C5402提供运行代码的多处理器系统中,后两种方案虽然都可以适应以C5402为核心的独立系统,但是串口EEPROM 启动模式中只支持价格偏高的SPI端口EEPROM,而并口启动模式却可以采用EPROM,而且并行EPROM和FLASH种类很多,有的价格较低,因而可以充分体现系统的性价比优势。

基于实践经验,本文详细介绍并行Bootloader的实现方法和方案设计重点,并介绍一种方便可靠的可扩展EPROM Bootloader方案。

1 C5402的Bootloader原理C5402的Bootloader在系统加电时把外部源程序传送到内部存储器或内部程序空间。

它允许程序被存放在外部慢速的存储器中,并调到高速的存储器中运行。

这可大大减小C5402内部RAM掩模的需要,降低电路设计的成本。

基于TMS320C5402的语音压缩与解压缩系统的设计

基于TMS320C5402的语音压缩与解压缩系统的设计摘要:根据TMS320C5402能实现语音压缩与解压缩的特点并结合外围的电路,设计了一个基于DSP芯片和单片机的语音录放系统,主要研究了硬件实现、调试和软件设计流程。

一、设计要求采用DSP芯片TMS320C5402及一些外围器件,设计一个语音压缩与解压缩系统——基于TMS320C5402的语音录放系统。

二、方案论证该系统主要是通过对语音信号进行压缩,以实现高效率数字录音,可用于电话留言、语音应答等场合。

数字录音相比较传统的磁带录音,优点突出,不仅查找速度快,而且对录音信息进行编辑整理也非常方便,更为方便的是数字录音信息可以转存在计算机硬盘等存储设备上以便长期保存。

但是,数字录音的缺点是要实现长时间录音需要很大的存储空间,因此,该系统一方面采用存储量为16MB的单片闪速存储器,另一方面采用2.0Kb/s的速率对语音进行压缩,以达到尽可能好的效果。

三、总体设计整个系统能实现对语音信号转换的功能。

采样芯片MCl4LC5480对语音信号进行采集,由性价比较高的DSP芯片TMS320C5402对语音信号进行处理,通过语音压缩算法实现语音压缩存储,由单片机AT89C51主控制器完成系统的控制和键盘处理、显示等功能。

该系统的工作过程如下:系统加电后,AT89C51复位后控制TMS320C5402复位。

TMS320C5402复位后,通过内部固化的自引导程序(Boot)将存于EPROM的程序和数据搬至高速RAM。

其录音过程是,由话筒将采集的模拟语音信号经A/D转换为要处理的数字信号,并将其存入DSP中的缓存区中,然后TMS320C5402开始运行语音压缩算法,对缓存区的语音信号进行压缩存储;其放音过程与之相反。

整个系统由AT89C51实现录放的控制操作。

四、原理分析1.元件选择1)DSP芯片TMS320C5402是TI公司推出的高性能16位定点DSP。

其高性能和低功耗成为各种无线和有线通信的理想器件。

基于TMS320C5402的多功能IP电话机的设计

基于TMS320C5402的多功能IP电话机的设计IP电话是指利用IP协议通过分组交换网络进行话音通信的通信方式。

因特网是采用统计复用信道技术的分组网络,与传统的的电路交换网络相比,因其带宽合并和业务综合等特性使其传输设备和信道利用率大大提高,从而降低了系统运营成本。

1. IP电话的发展趋势IP电话是指利用IP协议通过分组交换网络进行话音通信的通信方式。

因特网是采用统计复用信道技术的分组网络,与传统的的电路交换网络相比,因其带宽合并和业务综合等特性使其传输设备和信道利用率大大提高,从而降低了系统运营成本。

IP电话也因此作为因特网的一个应用得到了迅速发展。

特别是VoIP技术与其它互联网应用技术(如Web)的结合,并借助智能网技术,可以方便地实现许多智能业务,如基于web的呼叫中心。

这些先进的业务应用正刺激着传统的电话通信向真正的基于IP网络的电话通信转移。

目前IP电话的接入方式是使用普通电话拨入ITSP (Internet Telephony Service Provider)提供的IP电话网关,然后经过一系列认证,再进行呼叫、接通和通话。

造成这种情况的原因是因为目前的网络环境尚不完善,如带宽不足,网络接口尚不能直达用户等。

但随着因特网的不断扩展和新技术的出现,我们认为这种IP电话的接入方式会逐渐被淘汰,用户将直接通过IP电话机拨打电话,而这种IP电话机可能是一个直接连接到因特网的一个独立设备,也可能是一台移动电话的手机,还可能是普通桌面PC的外设,甚至于是一台连接到因特网的智能家用电器的一个附件。

我们所说的这种IP电话的普及首先会出现在大型跨区域公司的企业网内部。

目前各大公司都已经部署了公司内部的LAN,有些公司还采用的先进的交换式以太网技术,或者ATM 交换机。

这样如果这些公司部署IP电话系统,不仅无需重新架设电话布线系统,而且可以大量节省公司各分部之间的长途通话费用。

其次,只要公司内部LAN(也可能是一个跨地区的VPN)的网络规划做得好,合理划分网段,合理分配流量,应该不会出现QOS问题,甚至可以保证话音达到长途质量。

TMS320vc5402最小系统的设计

毕业论文DSP最小系统的设计与开发摘要DSP 由于运算速度快,具有可编程特性及接口灵活的特点,使得它在电子产品的研制中,发挥着越来越大的作用。

采用DSP器件来实现数字信号处理系统更是成了当前的发展趋势。

如何以最短的开发周期,开发出适于自己应用的高性能低成本的DSP板,己经成为广大DSP工程技术人员共同关心的问题。

DSP最小系统板硬件设计是本次论文的主要任务。

在介绍TMS320VC5402基本特点的基础上,运用DSP技术和硬件电路设计知识进行了DSP最小系统设计,包括DSP芯片选型、电源设计、复位电路设计、时钟电路设计、存储器设计、JTAG 接口等。

在软件方面,本文使用Protel99SE设计电路板。

首先绘制电路原理图,完成原理图后生成网络表。

然后对最小系统的高速PCB板进行了设计,并完成板卡的检测、制作、安装和硬件调试。

最后,以自行设计的高速DSP板为硬件平台,使用CCS2软件,编写测试程序。

经过多次软硬件调试和测试,验证了DSP最小系统板卡能正常运行,能满足基本信号处理的要求。

关键词:DSP;TMS320VC5402 ;最小系统;PCB;Protel99SEAB STRACTDSP has become more and more important in electronic product design because of its fast operation rate,programmability,and flexible inter face.It will be a developing trend to design digital signa l system with DSP devices.But there is a common issuefo r most DSP engineers to develop DSP boards with high quality and low cost in the shortest time.The ma in goal is to design a DSP minimum system board for this paper.After introducing the basic character ist ics of tms320vc5402chip,this paper uses DSP technology and hardware designing knowledge to design the minimum DSP system, which includes DSP chip select ion,power design,clock circuit design,reset circuit design,memor y design,JTAG inter face and etc.This paper uses Protel99SE to design the circuit board in software.It firstly draws circuit schematic,and generates the network table according to the schematic.Thenthe high-speed PCB board of the minimum system is designed,and the detecting,ma nufactur ing,insta llting and hardware debugging are accomplished.Finally,the test programs are writed using the CCS software on the paltfor m of the high-speed DSP board designed by myself.After the debugging and testing of many times,the DSP minimum system board can run commonly,and can satisty the basic requiremen ts of the signal processing.Key wordss:DSP;TMS320VC5402;Minimum System;PCB;Protel99SE目 录前 言 (1)第一章 绪 论 (2)1.1DSP 的应用领域........................................................................................ 1.2DSP 特点及国内外发展现状.................................................................... 2 2 1.3 1.2.1DSP 的特点......................................................................................2 1.2.2 国内外DSP 的发展........................................................................3 各章安排...................................................................................................4 第二章 总体设计 (5)2.1 2.2 2.3 2.4 系统要实现的功能...................................................................................5 系统的设计流程.......................................................................................5 原理框图 (7)最小系统主芯片介绍 (7)2.4.1TMS320VC5402 的软件资源.........................................................7 2.4.2TMS320VC5402 的硬件资源.........................................................8 第三章 DSP 最小系统硬件设计............................................................................... 3.1PROTEL 工具简介 (14)14 3.2 3.3 使用 Protel 99 SE 进行电路设计的流程...............................................14 电路原理图设计.....................................................................................15 3.4TMS320VC5402 最小系统设计 15 3.4.1 电源模块 .............................................................. 15 3.4.2 .......................................................................................复位、拨码开关和时钟电路 (16)3.5 扩展电路设计......................................................................................... 3.5.1CPLD 电路 1919 3.6 ..................................................................................... 3.5.2 FLASH 的扩展..............................................................................19 3.5.3SRAM 的扩展................................................................................21 印刷电路板的设计流程.........................................................................243.7.1 印刷电路板的结构 (27)3.7.2 3.7.3 3.7.4 零件封装 (27)铜膜导线 (28)焊点和导孔 (28)3.8 设计印刷电路板的注意事项 (28)3.9 最小系统PCB图和系统板 (29)3.10 印刷电路板硬件调试的问题和体会 (31)第四章系统性能测试 (33)3.1 3.2 仿真实现的软件工具 (33)系统的工作原理和测试步骤 (34)结论3.3DSP存储空间的配置.............................................................................. 3.4测试程序................................................................................................. 3.5测试的注意事项.....................................................................................34353637 ..........................................................................................................................参考文献 (38)附录 (39)谢辞 (50)大学本科毕业论文前言前言DSP有两种涵义,一种是Digital Signal Processing,指的是数字信号处理技术;一种是Digital Signal Processor,指的是数字信号处理器。

TMS320VC5402硬件系统简介

SZU-TI DSPs Lab 30

通用串口、并口及ADC/DAC 通用串口、并口及ADC/DAC

TMS320VC5402不带有通用串口、并口及 ADC/DAC,只能根据需要在外部扩展。可以选择 的器件很多,应根据性能要求选择。 一般通串口、并口过外部总线扩展。ADC/DAC 则可以通过McBSP或是外部总线扩展。

复位电路

复位电路可以输出稳定的复位信号,常见的 复位芯片一般还带有电源检测及看门狗等功能。

复位电路实例

SZU-TI DSPs Lab 10

复位电路

TPS3707-33D内部功能图 - 内部功能图

SZU-TI DSPs Lab 11

JTAG口 JTAG口

JTAG是Joint test Action Group的简称, 又称JTAG口,它是一符合IEEE Std 1149.1边 界扫描逻辑标准的标准接口。它主要用于在硬 件上对DSP进行实时在线仿真测试和DSP程序的 下载,它提供对所连接设备的边界扫描,同时 也可以用来测试引脚到引脚的连续性,以及进 行DSP芯片的外围器件的操作测试。

SZU-TI DSPs Lab 31

通用串口

通用串口实例

SZU-TI DSPs Lab 32

并口

并口实例

SZU-TI DSPs Lab 33

ADC

ADC实例 实例

SZU-TI DSPs Lab 34

印刷电路板( 印刷电路板(PCB)设计 )

PCB是英文(Printed Circuie Board)印制线路 板的简称。通常把在绝缘材上,按预定设计, 制成印制线路、印制元件或两者组合而成的导 电图形称为印制电路。而在绝缘基材上提供元 器件之间电气连接的导电图形,称为印制线路。 这样就把印制电路或印制线路的成品板称为印 制线路板,亦称为印制板或印制电路板。

dsp课程设计(TMS320VC5402 最小系统 存储器扩展设计)

摘要我为我问问我问问问问我我问问问问问我我问一个完整的DSP系统通常是由DSP芯片和其他相应的外围器件构成。

本设计主要介绍DSP最小硬件系统设计,包括电源电路、复位电路、时钟电路、存储器接口等。

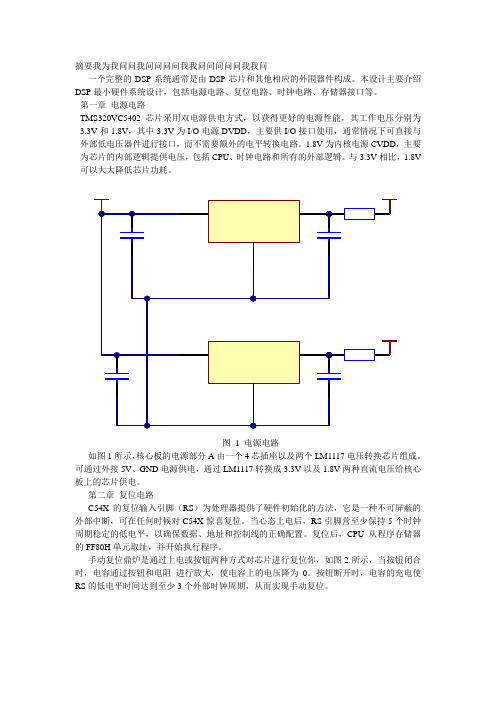

第一章电源电路TMS320VC5402芯片采用双电源供电方式,以获得更好的电源性能,其工作电压分别为3.3V和1.8V,其中3.3V为I/O电源DVDD,主要供I/O接口使用,通常情况下可直接与外部低电压器件进行接口,而不需要额外的电平转换电路。

1.8V为内核电源CVDD,主要为芯片的内部逻辑提供电压,包括CPU、时钟电路和所有的外部逻辑。

与3.3V相比,1.8V 可以大大降低芯片功耗。

图 1 电源电路如图1所示,核心板的电源部分A由一个4芯插座以及两个LM1117电压转换芯片组成。

可通过外接5V、GND电源供电,通过LM1117转换成3.3V以及1.8V两种直流电压给核心板上的芯片供电。

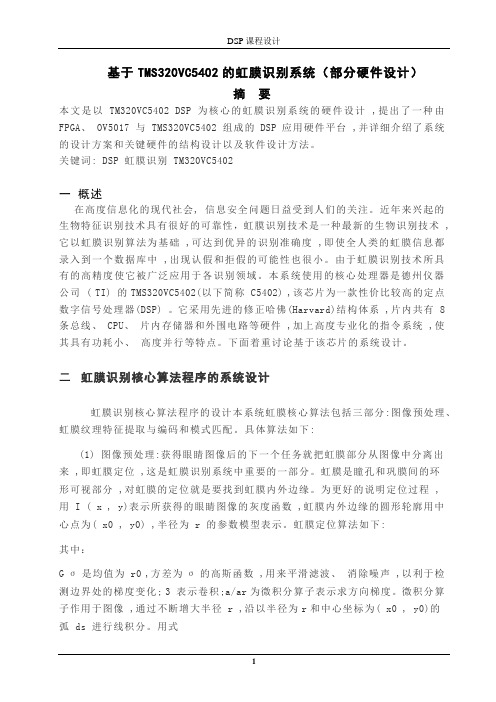

第二章复位电路C54X的复位输入引脚(RS)为处理器提供了硬件初始化的方法,它是一种不可屏蔽的外部中断,可在任何时候对C54X惊喜复位。

当心态上电后,RS引脚营至少保持5个时钟周期稳定的低电平,以确保数据、地址和控制线的正确配置。

复位后,CPU从程序存储器的FF80H单元取址,并开始执行程序。

手动复位鼎炉是通过上电或按钮两种方式对芯片进行复位你,如图2所示,当按钮闭合时,电容通过按钮和电阻进行放大,使电容上的电压降为0。

按钮断开时,电容的充电使RS的低电平时间达到至少3个外部时钟周期,从而实现手动复位。

图2 复位电路第三章时钟电路时钟电路用来为TMS320VC5402芯片体制时钟信号,可以利用DSP芯片内部的振荡器构成时钟电路,连接方式如图3所示。

在芯片的X1和X2引脚之间介入夜歌晶体,用于启动内部振荡器。

图3 时钟电路第四章DSP芯片的存储器接口第一节内部存储器TMS320VC5402的芯片设计有丰富的内部快速存储器可以全速运行,达到芯片最高速度。

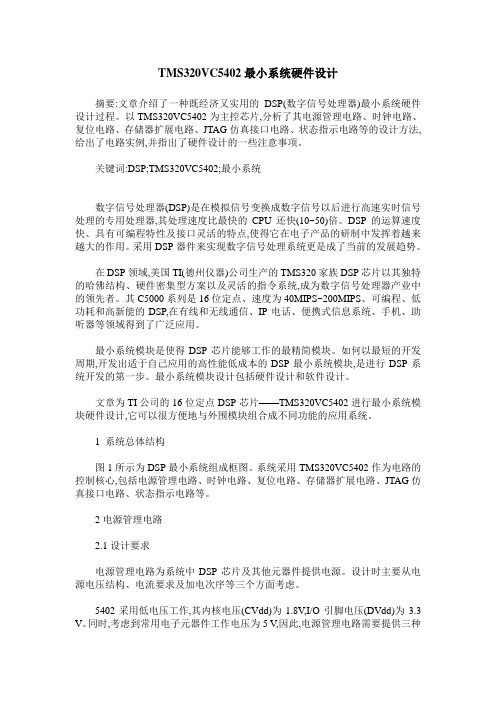

基于TMS320VC5402的虹膜识别系统(部分硬件设计)

基于TMS320VC5402的虹膜识别系统(部分硬件设计)摘要本文是以TM320VC5402 DSP 为核心的虹膜识别系统的硬件设计 ,提出了一种由FPGA、 OV5017 与 TMS320VC5402 组成的DSP应用硬件平台 ,并详细介绍了系统的设计方案和关键硬件的结构设计以及软件设计方法。

关键词: DSP 虹膜识别 TM320VC5402一概述在高度信息化的现代社会, 信息安全问题日益受到人们的关注。

近年来兴起的生物特征识别技术具有很好的可靠性,虹膜识别技术是一种最新的生物识别技术 ,它以虹膜识别算法为基础 ,可达到优异的识别准确度 ,即使全人类的虹膜信息都录入到一个数据库中 ,出现认假和拒假的可能性也很小。

由于虹膜识别技术所具有的高精度使它被广泛应用于各识别领域。

本系统使用的核心处理器是德州仪器公司 ( TI) 的TMS320VC5402(以下简称 C5402) ,该芯片为一款性价比较高的定点数字信号处理器(DSP) 。

它采用先进的修正哈佛(Harvard)结构体系 ,片内共有 8条总线、 CPU、片内存储器和外围电路等硬件 ,加上高度专业化的指令系统 ,使其具有功耗小、高度并行等特点。

下面着重讨论基于该芯片的系统设计。

二虹膜识别核心算法程序的系统设计虹膜识别核心算法程序的设计本系统虹膜核心算法包括三部分:图像预处理、虹膜纹理特征提取与编码和模式匹配。

具体算法如下:(1) 图像预处理:获得眼睛图像后的下一个任务就把虹膜部分从图像中分离出来 ,即虹膜定位 ,这是虹膜识别系统中重要的一部分。

虹膜是瞳孔和巩膜间的环形可视部分 ,对虹膜的定位就是要找到虹膜内外边缘。

为更好的说明定位过程 ,用 I ( x , y)表示所获得的眼睛图像的灰度函数 ,虹膜内外边缘的圆形轮廓用中心点为( x0 , y0) ,半径为 r 的参数模型表示。

虹膜定位算法如下:其中:G σ是均值为 r0 ,方差为σ的高斯函数 ,用来平滑滤波、消除噪声 ,以利于检测边界处的梯度变化; 3 表示卷积;a/ar为微积分算子表示求方向梯度。

TMS320VC5402最小系统硬件设计

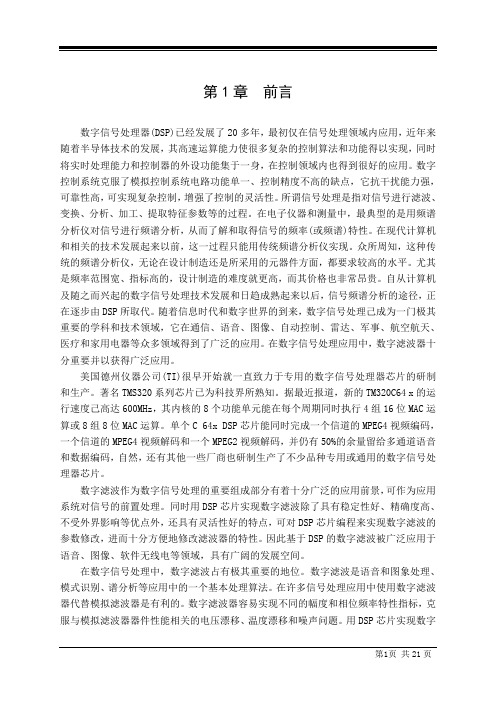

TMS320VC5402最小系统硬件设计摘要:文章介绍了一种既经济又实用的DSP(数字信号处理器)最小系统硬件设计过程。

以TMS320VC5402为主控芯片,分析了其电源管理电路、时钟电路、复位电路、存储器扩展电路、JTAG仿真接口电路、状态指示电路等的设计方法,给出了电路实例,并指出了硬件设计的一些注意事项。

关键词:DSP;TMS320VC5402;最小系统数字信号处理器(DSP)是在模拟信号变换成数字信号以后进行高速实时信号处理的专用处理器,其处理速度比最快的CPU还快(10~50)倍。

DSP 的运算速度快、具有可编程特性及接口灵活的特点,使得它在电子产品的研制中发挥着越来越大的作用。

采用DSP器件来实现数字信号处理系统更是成了当前的发展趋势。

在DSP领域,美国TI(德州仪器)公司生产的TMS320家族DSP芯片以其独特的哈佛结构、硬件密集型方案以及灵活的指令系统,成为数字信号处理器产业中的领先者。

其C5000系列是16位定点、速度为40MIPS~200MIPS、可编程、低功耗和高新能的DSP,在有线和无线通信、IP电话、便携式信息系统、手机、助听器等领域得到了广泛应用。

最小系统模块是使得DSP芯片能够工作的最精简模块。

如何以最短的开发周期,开发出适于自己应用的高性能低成本的DSP最小系统模块,是进行DSP系统开发的第一步。

最小系统模块设计包括硬件设计和软件设计。

文章为TI公司的16位定点DSP芯片——TMS320VC5402进行最小系统模块硬件设计,它可以很方便地与外围模块组合成不同功能的应用系统。

1 系统总体结构图1所示为DSP最小系统组成框图。

系统采用TMS320VC5402作为电路的控制核心,包括电源管理电路、时钟电路、复位电路、存储器扩展电路、JTAG仿真接口电路、状态指示电路等。

2电源管理电路2.1设计要求电源管理电路为系统中DSP芯片及其他元器件提供电源。

设计时主要从电源电压结构、电流要求及加电次序等三个方面考虑。

TMS320C5402DSP课程设计要点

第1章前言数字信号处理器(DSP)已经发展了20多年,最初仅在信号处理领域内应用,近年来随着半导体技术的发展,其高速运算能力使很多复杂的控制算法和功能得以实现,同时将实时处理能力和控制器的外设功能集于一身,在控制领域内也得到很好的应用。

数字控制系统克服了模拟控制系统电路功能单一、控制精度不高的缺点,它抗干扰能力强,可靠性高,可实现复杂控制,增强了控制的灵活性。

所谓信号处理是指对信号进行滤波、变换、分析、加工、提取特征参数等的过程。

在电子仪器和测量中,最典型的是用频谱分析仪对信号进行频谱分析,从而了解和取得信号的频率(或频谱)特性。

在现代计算机和相关的技术发展起来以前,这一过程只能用传统频谱分析仪实现。

众所周知,这种传统的频谱分析仪,无论在设计制造还是所采用的元器件方面,都要求较高的水平。

尤其是频率范围宽、指标高的,设计制造的难度就更高,而其价格也非常昂贵。

自从计算机及随之而兴起的数字信号处理技术发展和日趋成熟起来以后,信号频谱分析的途径,正在逐步由DSP所取代。

随着信息时代和数字世界的到来,数字信号处理己成为一门极其重要的学科和技术领域,它在通信、语音、图像、自动控制、雷达、军事、航空航天、医疗和家用电器等众多领域得到了广泛的应用。

在数字信号处理应用中,数字滤波器十分重要并以获得广泛应用。

美国德州仪器公司(TI)很早开始就一直致力于专用的数字信号处理器芯片的研制和生产。

著名TMS320系列芯片已为科技界所熟知。

据最近报道,新的TM320C64 x的运行速度己高达600MHz,其内核的8个功能单元能在每个周期同时执行4组16位MAC运算或8组8位MAC运算。

单个C 64x DSP芯片能同时完成一个信道的MPEG4视频编码,一个信道的MPEG4视频解码和一个MPEG2视频解码,并仍有50%的余量留给多通道语音和数据编码,自然,还有其他一些厂商也研制生产了不少品种专用或通用的数字信号处理器芯片。

数字滤波作为数字信号处理的重要组成部分有着十分广泛的应用前景,可作为应用系统对信号的前置处理。

TMS320C5402芯片基本硬件设计

TMS320C5402芯片基本硬件设计杨明远1,2 陈明义1(1.中南大学信息科学与工程学院,湖南长沙410008;2.湖南商务职业技术学院,湖南长沙410205)摘 要:讨论了TMS320C5402芯片的时钟电路、电源电路、复位电路等基本硬件电路的设计方法,并给出了接线图。

关键词:TMS320C5402;时钟电路;电源电路;复位电路中图分类号:TP303 文献标识码:A1 TMS320C5402芯片的CPU与外设C54x的CPU结构包括:40比特的ALU,其输入来自16比特立即数、16、暂时存储器、T 中的16比特数、数据存储器中两个16比特字、数据存储器中32比特字、累加器中40比特字;2个40比特的累加器,分为三个部分,保护位(39-32比特)、高位字(31-16比特)、低位字(15-0比特);桶型移位器,可产生0到31比特的左移或0到16比特的右移;17×17比特的乘法器,40比特的加法器;比较选择和存储单元CSSU;数据地址产生器DA2 GEN程序地址产生器PA GEN。

C54x的片内外设包括:通用I/O引脚XF和;两个定时器Timer0和Timer1;片内锁相环PLL;8比特HPI口;多通道缓冲存串口McBSP;可编程等待状态产生器;可编程bank2 switching模块;外部总线接口;IEEE1149.1标准J T AG口。

2 TMS320C5402芯片时钟电路的设计TMS320C5402时钟引脚为96脚(X1)、97脚(X2/ CL KIN),图1和图2分别是采用无源晶振和有源晶振的接线图。

对于晶振频率大小的选定没有特别的要求,因为X2/ CL KIN管脚上输入的时钟还要乘以PLL产生的一个系数才是CPU的工作时钟。

图1 无源晶振接线图 图2 有源晶振接线图TMS320C5402复位时77脚(CL KMD1)、78脚(CL KMD2)、79脚(CL KMD3)决定了时钟方式寄存器CL K2 MD的值和时钟方式,如表1所示。

(完整版)TMS320VC5402最小系统原理图设计

1.DSP简介1.1 DSP 的应用领域在近 20 多年时间里,DSP 芯片的应用已经从军事、航空航天领域扩大到信号处理、通信、雷达、消费等许多领域。

主要应用有信号处理、通信、语音、图形、图像、军事、仪器仪表、自动控制、医疗、家用电器等。

DSP 主要应用市场为3C 领域,占整个市场需求的 90%。

数字蜂窝电话是 DSP最为重要的应用领域之一。

由于 DSP 具有强大的计算能力,使得移动通信的蜂窝电话重新崛起,并创造了一批诸如 GSM、CDMA 等全数字蜂窝电话网。

在Modem 器件中,DSP 更是成效卓著,不仅大幅度提高了传输速率,且具有接收动态图像能力。

另外,可编程多媒体 DSP 是 PC 领域的主流产品。

以XDSL Modem为代表的高速通信技术与 MPEG 图像技术相结合,使得高品位的音频和视频形式的计算机数据有可能实现实时交换。

目前的硬盘空间相当大,这主要得益于CDSP(可定制 DSP)的巨大作用。

预计在今后的 PC 机中,一个 DSP 即可完成全部所需的多媒体处理功能。

DSP 也是消费类电子产品中的关键器件。

由于 DSP的广泛应用,数字音响设备的更新换代周期变得非常短暂。

用于图像处理的 DSP,一种用于 JPEG 标准的静态图像数据处理;另一种用于动态图像数据处理。

1.2 DSP的特点DSP 芯片是模拟信号变换成数字信号以后进行高速实时处理的专用微处理器,其处理速度比最快的 CPU 还快 10-50 倍,具有处理速度高、功能强、性能价格比好以及速度功耗比高等特点,被广泛应用于具有实时处理要求的场合。

DSP 系统以 DSP 芯片为基础,具有以下优点。

1.高速性,DSP 运行速度高达 1000MIPS 以上2.编程方便,可编程DSP 可使设计人员在开发过程中灵活方便的对软件进行修改和升级。

3.稳定性好,DSP 系统以数字处理为基础,受环境温度及噪声的影响比较小,可靠性高。

4.可重复性好,数字系统的性能基本上不受元器件参数性能的影响,便于测试、调试和大规模生产。

TMS320VC5402主机接口引导方案的设计

摘要本文主要介绍了DSP TMS320VC5402芯片的主机接口引导装载的实现方案。

在此设计中用户程序代码存放在主机中,DSP处理器上电后能通过主机接口将程序引导入DSP的程序存储区,正常进入用户程序代码。

Bootlooader(引导装载程序)是在出厂前固化在DSP芯片内ROM 中的一段程序代码,其主要功能是在上电或复位时将用户程序从外部加载至程序存储器(片内RAM或扩展的RAM)中,以便实现高速运行。

因此,用这种方法可以以较低成本实现高速运行。

不同型号的DSP,其Bootlooader也不同。

关键词 :DSP 主机接口引导TMS320VC5402目录摘要 (I)第一章 TMS320VC5402 (1)第一节芯片介绍 (1)第二节几种引导装载方法 (3)第二章系统硬件电路设计 (5)第一节HPI自举加载的过程 (5)第二节系统硬件电路设计 (6)第三章系统的软件设计 (11)第一节用户初始化程序 (11)第二节主机通过HPI引导程序到目标DSP (13)心得体会 (14)参考文献 (15)附录 (15)1 TMS320VC54021.1 芯片介绍TMS320VC5402(以下简称C5402)是德州仪器公司(TI)1999年10月推出的性价比极高的定点数字信号处理器(DSP)。

C5402主要特点如下[1]: ·操作速率达100MIPS;·具有先进的多总线结构,三条16位数据存储器总线和一条程序存储器总线;·40位算术逻辑单元(ALU),包括一个40位桶形移位器和两个40位累加器;·一个17×17乘法器和一个40位专用加法器,允许16位带/不带符号的乘法;·整合维特比加速器,用于提高维特比编译码的速度;·单周期正规化及指数译码;·8个辅助寄存器及一个软件栈,允许使用业界最先进的定点DSP C 语言编译器;·数据/程序寻址空间1M×16bit,内置4K×16bit ROM和16K×16bit RAM;·内置可编程等待状态发生器、锁相环(PLL)时钟产生器、两个多通道缓冲串行口、一个8位并行与外部处理器通信的HPI口、2个16位定时器以及6通道DMA控制器;·低功耗,工作电源有3V和1.8V(内核),特别适合电池供电设备。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

JTAG 插座

• 在DSK 上包括一个14 管脚的排针J1,它支持外部的 XDS510 仿真器连接。二个TI CBT 四组2:1 多路复用 器(SN74CBT3257)用来提供+5V 到+3.3V 的转换, TBC 到VC5402以及内部与外部JTAG 仿真之间的选择 也需要这样的转换。 • JTAG与VC5402之间的接口包括7个信号: ��� TMS ��� TDO TDI ��� TCLK TRST��� EMU1��� EMU0 • 2个四封装多路复用器SN74CBT3257用来转换这7个信 号。CBT的使用也允许+3.3V或+5V外部仿真器的连接。

2、DSK的组成(续)

• 外部存储器接口(EMIF):DSP通过它的16bit外部存 储器接口连接器(EMIF)连接外部SRAM、FLASH 存储 器和扩展存储器或连接扩展板。 • RAM:DSK 有一组64k x 16bit 的SRAM(在管脚相同情 况下,可以扩展到256k*16),当工作频率为100MHz 时,它运行过程有1个等待状态。 • FLASH :DSK 有1个256k*16bit 的FLASH存储器。 • 麦克风/耳机音频接口:通过AD50AIC来提供麦克/耳机 音频接口。AD50AIC与DSP的McBSP1相连接。McBSP0接 口连接到扩展连接器。

2、DSK的组成

• DSK的电源:+5V 电源。板上的线性电源稳压器提供 1.8VDC 核电压、3.3VDC 数字电压和5VDC 模拟电压。 • DSK 内嵌了一个仿真器,DSK内嵌的JTAG 仿真器是由 测试总线控制器(TBC)提供的,并且可以通过符合 IEEE-1284 的并行接口来访问DSP主机接口(HPI)。 它满足IEEE 标准1149.1(JTAG),并且与代码调试器 (Code Composer debugger)兼容。 另外,也可以使用外部XDS510仿真器来调试DSK板,仿 真器连接到板上的JTAG 连接器J1。

外部数据存储器(续)

• 如果MP/MC = 1 并且 OVLY = 0,那么0x0000~0xFFFF 空间是分配给外部存储器( FLASH 或SRAM )。 • 在70ns FLASH 存储器的情况下(FLASHENB=1),总线 的速率为100MHz,需要7个等待状态。 • 在SRAM 情况下(FLASHENB=0),总线速率为100MHz 时,需要1 个等待状态。 • 因为SRAM 和FLASH 共享同一个等待状态产生器, 5402 内部的等待状态产生器将必须从访问SRAM 的一 个等待状态转换到访问FALSH 的7个等待状态。 • 如果MP/MC = 1并且OVLY = 1,则只有x4000~0xFFFF 是映射到外部存储器的。

3、DSK的结构

DSP

• DSK 支持TMS320VC5402 DSP,工作频率可以高 达100MHz,工作的核电压为1.8V,I/O 电压为 3.3V • DSK 包括电源稳压器PS767D318,它为DSP提供 3.3V I/O 电压和1.8/2.5V 核电压。

外部程序存储器

• 外部程序存储器的可用大小是取决于OVLY 位的设置和 MP/MC 跳线的设置。 • 如果 OVLY 位=0 并且MP/MC=0,那么程序存储器的 空间0x0000~0xEFFF(60K words)映射到外部存储器, 是FLASH 还是SRAM 决定于控制寄存器的FLASHENB 状 态位。在上电状态,FLASHENB位置位是为了允许从 FLASH 引导。然后软件清除此位,使具有1个等待状态 的SRAM 使用这个相同的存储器空间。 • 如果MP/MC=0,那么0xF000~0xFFFF 是保留给片内ROM 和中断矢量表,并且外部程序存储器在0页是不可用的, 但是在其它页可以使用,这些取决于OVLY 位的设置。

I/O 存储器映射

• 外部存储器存取控制寄存器位 CPLD-Based Control Register Bits: –DM_SEL = DMCTRL bit 7

DSP HPI 接口

• VC5402 DSP 的HPI 接口是8 位并行接口。 • 因为VC5402 DSP不能接受+5V信号,所以使用2个TI CBT缓冲器,把PPC34C60的输出转换到+3.3V兼容的 信号。类似的是,2个CBT多路复用器是用来转换+5V TBC的输出的,同时也提供TBC与外部仿真端口之间 的选择。

DSK并行接口功能

• • • • • 连接DSP的HPI 端口 提供软件复位控制 控制TBC(为JTAG 控制) 访问一些CPLD 的内部寄存器 主机能够访问HPI或TBC,但是不能同时访问。

JTAG 仿真

• DSK提供了内嵌的JTAG仿真,它是通过IEEE-1284并行 接口来访问的,同时DSK也支持一个外部的仿真器 XDS510。 • 选择的JTAG方式是自动的。当你连接外部XDS510仿真 器的时候,DSK从内嵌的JTAG转换到外部,当你不连接 XDS510仿真器的时候,可以使用内嵌的仿真器。 • TI SN74ACT8990 JTAG测试总线控制器(TBC)用来提 供板上JTAG边界扫描链的映射存储器的控制。在没有 外部仿真器的情况下,它允许TMS320VC5402的源调试 器使用DSK。 • TBC提供给PC主机软件作为24个存储器映射寄存器,这 是通过IEEE-1284并行端口和PPC34C60来提供的。

麦克风和耳机接口

• 音频接口使用了2 个标准的3.5mm 的连接器: 一个连接麦克风(J5)的音频输入 ��� 一个连接耳机(J6)的音频输出 • 音频输入是交流耦合的,并包括: ��� 1 个固定增益为10dB 的放大器 ��� 实现单端到差分的转换 ��� 电压偏置(支持电池电源和驻极体麦克风) ��� 被动滤波(在DSK 的音频插口和CODEC 之间)用 来增强性能

硬件跳线

• JP1: 耳机输出跳线 Pins 1 to 2:无缓冲的(AD50)输出 Pins 2 to 3:缓冲的输出 • J4:引导模式跳线 连接的: HPI引导选择 非连接的:FLASH引导模式 • J9:MP/MC模式控制跳线 连接的: MC模式 非连接的:MP模式

DSK 中断

• DSK支持主机和DSP外部中断。DSP通过写HPI控制寄存 器(HPIC)的HINT位,能够中断主机。 • DSP有4个外部可屏蔽中断INT0~INT3。 中断名称 使用描述 EXT_INT0 扩展板 EXT_INT1 扩展板 EXT_INT2 DSP选择引导模式控制 或扩展板产生 EXT_INT3 DSP选择主板 或扩展板产生

外部程序存储器(续)

• DSK 外部程序空间由外部存储器存取控制寄存器位来 控制(CPLD-Based Control Register Bits): –DM_SEL = DMCTRL bit 7 –FLASHENB = CNTL2 bit 5 • 外部程序存储器的I/O 空间是由2部分组成,一个是系 统基于CPLD 控制空间,另一个是扩展板存储器空间。 DM_SEL 位能够控制I/O 空间的访问。如果DSP 向此位 写1,那么扩展板存储器的I/O 空间是不能被访问的。 如果向此位写0,那么扩展板存储器的I/O 空间是可以 被访问的。

扩展接口

• 一个扩展连接器J7提供对DSP的异步EMIF和DSP的外设 和控制/状态信号的访问。并且为扩展板提供了电源和 地。 • 大部分的扩展连接器信号经过了缓冲处理,这样扩展 板就不直接影响DSK板的运行。 • 5V电压的缓冲器和CBT接口设备的使用允许在扩展板上 使用+5V或+3.3V器件。 • 扩展存储器接口提供DSP到扩展板存储器接口信号。外 部的异步存储器和存储器映射设备可以加入到DSK上, 包括复位时用于引导DSK的非易失性存储器。

并口功能描述

• PC机和DSK的通信是通过一个符合IEEE-1284标准的并 行接口来实现的。使用一个标准DB-25的连接器。 • 主机接口可以支持DSP主机接口(HPI)和JTAG测试 总线控制器(TBC)的访问,TBC是用来进行DSP仿真 控制的。也支持对几个内部CPLD寄存器的访问。 • 并行接口是采用了PPC34C60芯片外设一侧的并行接口。 这个集成电路可以提供一个符合IEEE-1284标准的并行 接口连接到PC(包括标准、EPP、ECP模式),和一 个类似于PC ISA接口总线接到TBC和DSP的主机端口。

Sቤተ መጻሕፍቲ ባይዱED5402 DSK的硬件结构 和硬件设计

北京交通大学电工电子基地 DSP实验室

本章主要内容

一、SEED5402 DSK的组成及结构 二、TMS320VC5402 DSP的硬件设计

一、SEED5402 DSK的组成及结构

1、概述

DSK 包括: 100 MHz VC5402 DSP 外部、1个软件等待的64K word的SRAM 256K word FLASH存储器 用于仿真的JTAG测试总线控制器和一个连接到PC机并 口的主机端接口HPI 麦克风/耳机音频接口 扩展板接口

扩展板存取地址的范围

存取 数据 I/O 地址范围 0x8000-0xFFFF 0x8000-0xFFFF 条件 DMSEL=1 DMSEL= 0 ; A15为高电平

扩展外设接口

扩展外设接口包括: • McBSP0串口的6个信号——由CLKX、FSX、 DX、CLKR、FSR、DR组成。 • 定时器输出信号——DSP定时器0的输出信号 TOUT。 • 中断和中断响应——1个外部DSP中断INT1# , 和DSP的中断响应(IACK)。 • DSP通用I/O信号——DSP的XF 和BIO信号。 • 3个异步的存储器控制信号。这些信号包括: PS#、IS#、IOSTRB#、DS#、MSTRB# 。

外部数据存储器

• 可以使用的外部数据存储器的大小取决于DROM 的设置。 如果DROM=0,那么0x4000~0xFFFF(48K words)的空 间是外部存储器(FLASH 或SRAM)。如果DROM=1,外 部存储器只能使用0x4000~0xEFFF。 • 是否可以访问板上或扩展板存储器取决于DMSEL 控制 寄存器位。如果DMSEL=0(缺省),那么可以使用板 上的数据存储器。如果DMSEL=1,那么可以使用扩展 板存储器,并且地址开始于0x8000。数据存储器空间 资源也取决于MP/MC 状态。