数字集成电路分析与设计 第二章答案

集成电路分析与设计

第一章集成电路的发展1.何谓集成电路(Integrated Circuits)?集成电路:指通过一系列特定的加工工艺, 将晶体管,二极管等有源器件和电阻,电容,电感等无源器件,按照一定的电路互连,”集成”在一块半导体晶片上,封装在一个外壳内,执行特定电路或系统功能的一种器件.2.什么是摩尔定律(Moore’s Law)?它对集成电路的发展有什么作用?集成度:大约每三年翻两番,特征尺寸:每六年缩小近一倍事实上,摩尔定律并不是一个物理定律,而是一种预言,一张时间表。

它鞭策半导体产业界不断进步,并努力去实现它。

从根本上讲,摩尔定律是一种产业自我激励的机制,它让人们无法抗拒,并努力追赶,谁跟不上,谁就可能被残酷地淘汰。

摩尔定律已成为一盏照亮全球半导体产业前进方向的明灯。

3.IC发展水平的指标是什么?随着IC工业的发展,这些指标如何变化?集成规模(Integration scale)和特征尺寸(Feature size) 单个芯片上已经可以制作含有几百万个晶体管的一个完整的数字系统或数模混合的电子系统,集成电路的特征尺寸也已发展到深亚微米水平,0.18μm工艺已经走向规模化生产.4.什么是IDM、Fabless和Foundry?理解他们之间的关系。

IDM:集成电路发展的前三十年中,设计、制造和封装都是集中在半导体生产厂家内进行的,称之为一体化制造(IDM,Integrated Device Manufacturer)的集成电路实现模式。

无生产线(Fabless)集成电路设计提供了条件,为微电子领域发展知识经济提供了条件。

Fabless:1.设计公司拥有设计人才和设计技术,但不拥有生产线2.芯片设计公司不拥有生产线而存在和发展,而芯片制造单位致力于工艺实现(代客户加工,简称代工)3.设计单位与代工单位以信息流和物流的渠道建立联系Foundry:Foundry(代客户加工)第二章PN结的形成1.P型、N型半导体的形成及其能带结构图(EF与掺杂的关系)在纯净的硅晶体中掺入三价元素(如硼),使之取代晶格中硅原子的位置,此时自由电子和空穴浓度远远小于由于掺杂带来的空穴浓度,因此自由电子的导电基本可以忽略,这样的半导体叫做P型半导体。

《集成电路设计(第2版)》习题答案1-5章

9. MOSFET 存在哪些二阶效应?分别是由什么原因引起的? P.70-73 沟道长度调制效应,体效应,亚阈值效应 10.说明 MOSFET 噪声的来源、成因及减小的方法。 噪声来源:热噪声和闪烁噪声。热噪声是由沟道内载流子的无规则热运动造成的,可通 过增加 MOS 管的栅宽和偏置电流减少热噪声。闪烁噪声是由沟道处二氧化硅与硅界面上电 子的充放电引起的,增加栅长栅宽可降低闪烁噪声。

CH3

1. 写出晶体外延的意义,列出三种外延生长方法,并比较各自的优缺点。 意义:用同质材料形成具有不同掺杂种类及浓度而具有不同性能的晶体层。外延方法: 液态生长,气相外延生长,金属有机物气相外延生长 2.写出掩膜在 IC 制造过程中的作用,比较整版掩膜和单片掩膜的区别,列举三种掩膜的制 造方法。P28,29 3.写出光刻的作用,光刻有哪两种曝光方式? 作用: 把掩膜上的图形转换成晶圆上的器 件结构。曝光方式有接触与非接触两种。 4.X 射线制版和直接电子束直写技术替代光刻技术有什么优缺点? X 射线(X-ray)具有比可见光短得多的波长,可波长很短,分辨率很高 5. 说出半导体工艺中掺杂的作用,举出两种掺杂方法,并比较其优缺点。 热扩散掺杂和离子注入法。与热扩散相比,离子注入法的优点如下:1.掺杂的过程可通 过调整杂质剂量与能量来精确控制杂质分布。2.可进行小剂量的掺杂。3.可进行极小深度的 掺杂。4.较低的工业温度,故光刻胶可用作掩膜。5.可供掺杂的离子种类较多,离子注入法 也可用于制作隔离岛。缺点:价格昂贵,大剂量注入时,半导体晶格会遭到严重破坏且难以 恢复 6.列出干法和湿法氧化法形成 SiO2 的化学反应式。 干氧 Si O2 SiO2 湿氧 Si 2 H 2 O SiO2 2 H 2

怎样的条件下金属与半导体形成肖特基接接触区半导体重掺杂可实现欧姆接触金属与掺杂半导体接触形成肖特基接触4

数字电路基础知识部分(第二章)

练习一、一、填空题1、 模拟信号是在时间上和数值上都是 变化 的信号。

2、 脉冲信号则是指极短时间内的 电信号。

3、 广义地凡是 规律变化的,带有突变特点的电信号均称脉冲。

4、 数字信号是指在时间和数值上都是 的信号,是脉冲信号的一种。

5、 常见的脉冲波形有,矩形波、 、三角波、 、阶梯波。

6、 一个脉冲的参数主要有 、tr 、 、T P 、T 等。

7、 数字电路研究的对象是电路的 之间的逻辑关系。

8、 电容器两端的电压不能突变,即外加电压突变瞬间,电容器相当于 。

9、 电容充放电结束时,流过电容的电流为0,电容相当于 。

10、 通常规定,RC 充放电,当t = 时,即认为充放电过程结束。

11、 RC 充放电过程的快慢取决于电路本身的 ,与其它因素无关。

12、 RC 充放电过程中,电压,电流均按 规律变化。

13、 理想二极管正向导通时,其端电压为0,相当于开关的 。

14、 在脉冲与数字电路中,三极管主要工作在 和 。

15、 三极管输出响应输入的变化需要一定的时间,时间越短,开关特性 。

16、 选择题1 若逻辑表达式F A B =+,则下列表达式中与F 相同的是( ) A 、F A B = B 、F AB = C 、F A B =+2 若一个逻辑函数由三个变量组成,则最小项共有( )个。

A 、3 B 、4 C 、83 图9-1所示是三个变量的卡诺图,则最简的“与或式”表达式为( ) A 、A B A C B C ++B 、A B BC AC ++ C 、AB BC AC ++4 下列各式中哪个是三变量A 、B 、C 的最小项( ) A 、A B C ++ B 、A B C + C 、ABC 5、模拟电路与脉冲电路的不同在于( )。

A 、模拟电路的晶体管多工作在开关状态,脉冲电路的晶体管多工作在放大状态。

B 、模拟电路的晶体管多工作在放大状态,脉冲电路的晶体管多工作在开关状态。

C 、模拟电路的晶体管多工作在截止状态,脉冲电路的晶体管多工作在饱和状态。

《数字电子技术基础》课后习题答案

《数字电路与逻辑设计》作业教材:《数字电子技术基础》(高等教育出版社,第2版,2012年第7次印刷)第一章:自测题:一、1、小规模集成电路,中规模集成电路,大规模集成电路,超大规模集成电路5、各位权系数之和,1799、01100101,01100101,01100110;11100101,10011010,10011011二、1、×8、√10、×三、1、A4、B练习题:、解:(1) 十六进制转二进制: 4 5 C0100 0101 1100二进制转八进制:010 001 011 1002 13 4十六进制转十进制:(45C)16=4*162+5*161+12*160=(1116)10(2) 十六进制转二进制: 6 D E . C 80110 1101 1110 . 1100 1000 二进制转八进制:011 011 011 110 . 110 010 0003 3 3 6 . 6 2十六进制转十进制:()16=6*162+13*161+14*160+13*16-1+8*16-2=()10所以:()16=()2=()8=()10(3) 十六进制转二进制:8 F E . F D1000 1111 1110. 1111 1101二进制转八进制:100 011 111 110 . 111 111 0104 3 7 6 . 7 7 2十六进制转十进制:(8FE.FD)16=8*162+15*161+14*160+15*16-1+13*16-2=(2302.98828125)10 (4) 十六进制转二进制:7 9 E . F D0111 1001 1110 . 1111 1101二进制转八进制:011 110 011 110 . 111 111 0103 6 3 6 . 7 7 2十六进制转十进制:(79E.FD)16=7*162+9*161+14*160+15*16-1+13*16-2=(1950. 98828125)10 所以:()16.11111101)2=(363)8=(1950.98828125)10、解:(74)10 =(0111 0100)8421BCD=(1010 0111)余3BCD(45.36)10 =(0100 0101.0011 0110)8421BCD=(0111 1000.0110 1001 )余3BCD(136.45)10 =(0001 0011 0110.0100 0101)8421BCD=(0100 0110 1001.0111 1000 )余3BCD (374.51)10 =(0011 0111 0100.0101 0001)8421BCD=(0110 1010 0111.1000 0100)余3BCD、解(1)(+35)=(0 100011)原= (0 100011)补(2)(+56 )=(0 111000)原= (0 111000)补(3)(-26)=(1 11010)原= (1 11101)补(4)(-67)=(1 1000011)原= (1 1000110)补第二章:自测题:一、1、与运算、或运算、非运算3、代入规则、反演规则、对偶规则二、2、×4、×三、1、B3、D5、C练习题:2.2:(4)解:(8)解:2.3:(2)证明:左边=右式所以等式成立(4)证明:左边=右边=左边=右边,所以等式成立(1)(3)2.6:(1)2.7:(1)卡诺图如下:BCA00 01 11 100 1 11 1 1 1所以,2.8:(2)画卡诺图如下:BC A 0001 11 100 1 1 0 11 1 1 1 12.9:如下:CDAB00 01 11 1000 1 1 1 101 1 111 ×××10 1 ××2.10:(3)解:化简最小项式:最大项式:2.13:(3)技能题:2.16 解:设三种不同火灾探测器分别为A、B、C,有信号时值为1,无信号时为0,根据题意,画卡诺图如下:BC00 01 11 10A0 0 0 1 01 0 1 1 1第三章:自测题:一、1、饱和,截止7、接高电平,和有用输入端并接,悬空;二、1、√8、√;三、1、A4、D练习题:、解:(a)Ω,开门电阻3kΩ,R>R on,相当于接入高电平1,所以(e) 因为接地电阻510ΩkΩ,R<R off,相当于接入高电平0,所以、、解:(a)(c)(f)、解: (a)、解:输出高电平时,带负载的个数2020400===IH OH OH I I N G 可带20个同类反相器输出低电平时,带负载的个数78.1745.08===IL OL OL I I NG反相器可带17个同类反相器EN=1时,EN=0时,根据题意,设A为具有否决权的股东,其余两位股东为B、C,画卡诺图如下,BC00 01 11 10A0 0 0 0 01 0 1 1 1则表达结果Y的表达式为:逻辑电路如下:技能题::解:根据题意,A、B、C、D变量的卡诺图如下:CD00 01 11 10AB00 0 0 0 001 0 0 0 0 11 0 1 1 1 10 0 0 0 0电路图如下:第四章:自测题:一、2、输入信号,优先级别最高的输入信号7、用以比较两组二进制数的大小或相等的电路,A>B 二、 3、√ 4、√ 三、 5、A 7、C练习题:4.1;解:(a),所以电路为与门。

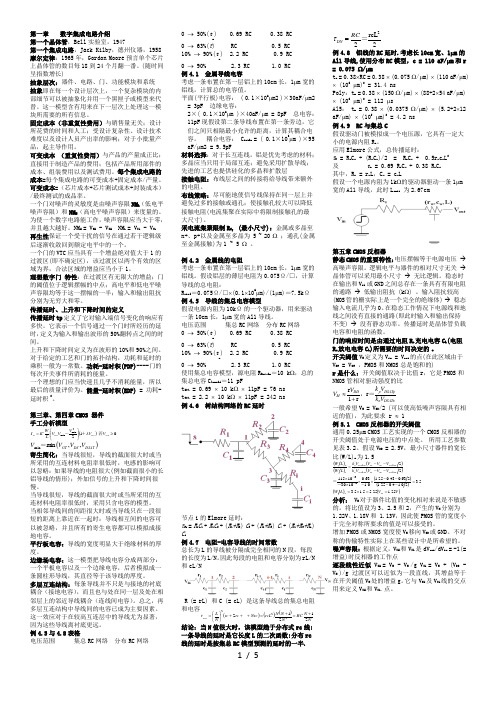

数字集成电路分析与设计 第三章答案

CHAPTER 3P3.1. The general approach for the first two parameters is to figure out which variables shouldremain constant, so that when you have two currents, you can divide them, and every variable but the ones you want to calculate remain. In this case, since the long-channel transistor is in saturation for all values of V GS and V DS , only one equation needs to be considered:()()2112DS N OX GS T DS W I C V V V Lμλ=-+ For the last two parameters, now that you have enough values, you can just choose oneset of numbers to compute their final values.a. The threshold voltage, V T0, can be found by choosing two sets of numbers with the same V DS ’s but with different V GS ’s. In this case, the first two values in the table can be used.()()()()()()211122222201022001121121.2 1.210000.82800.8DS N OX GS T DS DS N OX GS T DS T DS T DS T T W I C V V V L W I C V V V LV I V I V V μλμλ=-+=-+-⎛⎫-===⎪--⎝⎭ 00.35V T V ∴=b. The channel modulation parameter, λ, can be found by choosing two sets of numberswith the same V GS ’s but with different V DS ’s. In this case, the second and third values in the table can be used.()()221 1.225010.8247DS DS I I λλ+==+ -10.04V λ∴=c. The electron mobility, µn , can now be calculated by looking at any of the first three sets of numbers, but first, let’s calculate C OX .631062-31m 10μm22?.210μm1m 10 0.0351 1.610/2.210OX OX t C F cm--=⨯⨯===⨯Now calculate the mobility by using the first set of numbers.()()()()()()()()()()()()22111021262101111 1.21 1.222210002cm 348V-s 1.610(4.75)1.20.3510.04 1.21DS N OX GS T DS N OX T DS N OX GS T DS W W I C V V V C V L LA I W C V V V L μλμλμμλ-=-+=-+===⨯-+-+d. The body effect coefficient gamma, γ, can be calculated by using the last set of numbers since it is the only one that has a V SB greater than 0V.()()()()244124414411221 1.20.468VDS N OX GS T DS DS GS T N OX DS GS T T GS W I C V V V LI V V W C V LV V V V μλμλ=-+-=+-==-==12000.6VT T T T V V V V γγγ=+-====P3.2. The key to this question is to identify the transistor’s region of operation so that gatecapacitance may be assigned appropriately, and the primary capacitor that will dischargedat a rate of V It C ∂∂= by the current source may be identified. Then, because the nodes arechanging, the next region of operation must be identified. This process continues until the transistor reaches steady state behavior. Region 1:Since 0V GS V = the transistor is in the cutoff region. The gate capacitance is allocated to GB C . Since no current will flow through the transistor, all current will come from the source capacitor and the drain node remains unchanged.68-151010V V 6.67100.6671510s nsSB V I I t C C -∆⨯====⨯=∆⨯ The source capacitor will discharge until 1.1V GS T V V == when the transistor enters thesaturation region. This would require that the source node would be at 3.3 1.1 2.2V S G GS V V V =-=-=.()15961510 3.3 2.2 1.6510s 1.65ns 1010C t V I ---⨯∆=∆=-=⨯=⨯ Region 2:The transistor turns on and is in saturation. The current is provided from the capacitor atthe drain node, while the source node remains fairly constant. The capacitance at the drain node is the same as the source node so the rate of change is given by:68-151010V V 6.67100.6671510s nsSB V I I t C C -∆⨯====⨯=∆⨯ Since the transistor is now in the saturation region, GS V can be computed based on thecurrent flowing through the device.()22 1.1 1.37V 3.3 1.37 1.93VGS T GST S G GS kW I V V LV V V V V =-==+==-=-=This is where the source node settles. This means that most of the current is discharged through the transistor until the drain voltage reaches a value that puts the transistor at the edge of saturation.3.3 1.1 2.2VDS GS TD G T V V V V V V =-=-=-=If we assume that all the current comes from the transistor, and the source node remains fixed, the drain node will then discharge at a rate equal to that of the source node in the first region. Region 3:The transistor is now in the linear region the gate capacitance is distributed equally to both GS C and GD C . and both capacitors will discharge at approximately the same rate.-151510V0.28621510510nsV I A t C μ-∆===∆⨯⨯+⨯The graph is shown below.00.511.522.533.5024681012Time (ns)V o l t a g e (V )P3.3. The gate and drain are connected together so that DS GS V V = which will cause thetransistor to remain in saturation. This is a dc measurement so capacitances are not required. Connect the bulk to ground and run SPICE. P3.4. Run SPICE. P3.5. Run SPICE. P3.6. Run SPICE. P3.7. Run SPICE.P3.8. First, let’s look at the various parameters and identify how they affect V T .∙ L – Shorter lengths result in a lower threshold voltage due to DIBL. ∙ W – Narrow width can increase the threshold voltage.∙ V SB – Larger source-bulk voltages (in magnitude) result in a higher threshold voltage. ∙ V DS –Larger drain-source voltages (in magnitude) result in a lower threshold voltage due to DIBL. The transistor with the lowest threshold voltage has the shortest channel, larger width, smallest source-bulk voltage and largest drain-source voltage. This would be the first transistor listed.The transistor with the highest threshold voltage has the longest channel, smallest width,largest source-bulk voltage and smallest drain-source voltage. This would be the last transistor listed. P3.9. Run SPICE.P3.10. Run SPICE. The mobility degradation at high temperatures reduces I on and the increasemobile carriers at high temperatures increase I off . P3.11. The issues that prompted the switch from Al to Cu are resistance and electromigration.Copper wires have lower resistances and are less susceptible to electromigration problems. Copper on the other hand, reacts with the oxygen in SiO 2 and requires cladding around the wires to prevent this reaction.For low-k dielectrics, the target value future technologies is 2.High-k dielectrics are being developed as the gate-insulator material of MOSFET’s. This is because the current insulator material, SiO 2, can not be scaled any longer due to tunneling effects.P3.12. Self-aligned poly gates are fabricated by depositing oxide and poly before the source anddrain regions are implanted. Self-aligned silicides (salicides) are deposited on top of the source and drain regions using the spacers on the sides of the poly gate. P3.13. To compute the length, simply use the wire resistance equation and solve for L .LR TWRTWL ρρ==First convert the units of ρ to terms of μm. Aluminum:2.7μΩρ=cm 6Ω10μΩ⨯610μm100cm ⨯()()()0.027Ωμm1000.812963μm 2.96mm0.027RTWL ρ=====Copper:1.7μΩρ=cm 6Ω10μΩ⨯610μm100cm ⨯()()()0.017Ωμm1000.814706μm 4.71mm0.017RTWL ρ=====P3.14. Generally, the capacitance equation in terms of permittivity constants and spacing is:k C WL tε=a. 4k = ()()()()230048.8510 3.541100SiO k k C WL TL t S S Sεε-====b. 2k = ()()()()30028.8510 1.771100k k C WL TL t S SSεε-====The plots are shown below.Capacitance vs. Spacing01234567800.511.522.533.544.555.5Spacing (um)C a p a c i t a n c e (f F)。

数字电路与系统设计实验

第二章 实验基本仪器

数字系统设计实验所需设备有: 直流稳压电源,示波器,基于CPLD的 数字电路实验系统,万用表,信号源, 计算机。

一、直流稳压电源

二、示波器

示波器是一种用来测量电信号波形的 电子仪器。用示波器能够观察电信号 波形,测量电信号的电压大小,周期 信号的频率和周期大小。双踪示波器 能够同时观察两路电信号波形。

能块相对集中地排列器件 3.布线顺序 VCC,GND,输入/输出,控制线 4. 仪器检测(电源,示波器,信号源) 5.实验 测试、调试与记录

6.撰写实验总结报告

(1)实验内容 (2)实验目的 (3)实验设备 (4)实验方法与手段 (5)实验原理图 (6)实验现象(结果)记录分析 (7)实验结论与体会

(((四三一)))、、、实实验实验目验的提内示容

•• 11..注测1意试.掌被T握T测LT器T器L件、件H7的CT4引和L脚HS7C器0和件4引的一脚传个输1特非4性门分。的别传接输地特和 十性5。V2。.掌握万用表的使用方法。

•• •

(2连为输23特二.接 被 入)..性将测测、123到 测 电。实试 试...被 非 压六六六验验HH反反反测 门 值所CC台相相相T器用非 的 。上器器器器件器门输4件777件7的入.444774输电LHH4KH入压SCCHΩC00T端。电C4400,旋位T片片44转R器0片T一电LR4的个T位一L输非的器个出门电改非端的压变门电传输非的压输出门传作特端的输性。

四、数字电路测试及故障查找、排除

1.数字电路测试

数字电路静态测试指的是给定数字电路若干组静态输 入值,测定数字电路的输出值是否正确。

数字电路课后习题答案第二章

2.8

(a)

(b)

2.9

(a)

(b)

2.10 (a)

(b)

(c)

2.11 decimal signed-magnitude two’s-magnitude one’s-complement 2.12 (a)

11010100 (b) 101110011 (c) 01011101 (d) 00100110 + 10101011 + 11010110 + 00100001 + 01011010 ------------------------------------------------------------------------------------------------------------------------01111111 10001111 01111101 10000000 yes no no yes

2.6

(a) (c) (e) (g) (i)

125 10 = 1111101 2 209 10 = 11010001 2 132 10 = 1000100 2 727 10 = 10402 5 1435 10 = 2633 8 1100010 110101 + 11001 ------------------------1001110 110000 110101 - 11001 -----------------------011100 1372 + 4631 ------------------6223 1372 + 4631 ------------------59A3 (b)

2.7

(a)

111111110 (d) 11000000 1011000 (c) 11011101 101110 1110010 + 1100011 + 100101 + 1101101 ------------------------------------------------------------------------------------101000000 1010011 11011111 0011010 000010 (c) 11000100 (d) 1110010 11011101 101110 - 1101101 - 1100011 - 100101 ------------------------------------------------------------------------------------0000101 01111010 001001 47135 + 5125 ------------------54262 4F1A5 + B8D5 ---------------------5AA7A + 18 00010010 00010010 00010010 (c) 175214 (d) 110321 + 152405 + 56573 ---------------------------------------------347621 167114 F35B + 27E6 -------------------11B41 + 115 01110011 01110011 01110011 (d) 1B90F + C44E --------------------27D5D +79 01001111 01001111 01001111 –49 10110001 11001111 11001110 –3 10000011 11111101 11111100 –100 11100100 10011100 10011011

数字电子技术基础课后习题答案第2章习题答案

思考题:题2.1.1 答:肖特基二极管(SBD)、分流。

题2.1.2 答:基区、滞后。

题2.1.3 答:(A)、(B) 。

题2.1.4 答:对。

题2.2.1 答:A、B。

题2.2.2 答:C、D。

题2.2.3 答:4ns。

题2.2.4 答:(A)、(C)、。

题2.2.5 答:降低、降低。

题2.2.6 答:0、1和三态题2.2.7 答:若一个输出高电平,另一个输出低电平时,会在T4和T5间产生一个大电流,烧毁管子。

OC门“线与”在输出接一电阻和一5-30V电源电压。

题2.2.8 答:能、分时。

题2.2.9 答:1. 为了缩短传输延迟时间,电路中使用肖特基管和有源泄放电路,另外,还将输入级的多发射极管改用SBD代替,由于SBD没有电荷存储效应,因此有利于提高电路的工作速度。

电路中还接入了D3和D4两个SBD,当电路的输出端由高电平变为低电平时,D4经T2的集电极和T5的基极提供了一条通路,一是为了加快负载电容的放电速度,二是为了加速T5的导通过程。

另外,D3经T2的集电极为T4的基极提供了一条放电通路,加快了T4的截止过程。

2. 为降低功耗,提高了电路中各电阻的阻值,将电阻R5原来接地的一端改接到输出端,以减小T3导通时电阻R5上的功耗。

题2.3.1 答:A。

题2.3.2 答:A。

题2.3.3 答:A。

题2.3.4 答:导通。

题2.3.5 答:B、C。

思考题:题2.4.1 答:(A)分流。

题2.4.2 答:(B) 内部电阻和容性负载。

题2.4.3 答:(B) 3.3V;(C)5V;(D) 30V。

题2.4.4 答:CMOS反相器和CMOS传输门。

题2.4.5 答:加入缓冲器保证输出电压不抬高或者降低,正逻辑变负逻辑或者相反,与非变成或非,或者或非变为与非。

题2.4.6 答:(C)低、高。

题2.4.7答:(A) OD门;(B) OC门;(C)三态门。

16题2.4.8 答:(A)驱动大负载;(B)电平移位。

数字集成电路设计与系统分析答案

懂得1、Please illustrate the meaning of its voltage transfer characteristic to a logic gate, and describe the static behaviors showed in the voltage transfer characteristic curves.The electrical function of a gate is best expressed by its voltage transfer characteristic (VTC),which plots the output voltage as a function of the input voltage Vout=f(Vin).The high and low nominal voltage Voh and Vol;The gate or switching threshold voltage Vm,that is define as Vm=f(Vm)(The gate threshold voltage presents the midpoint of the switching characteristics,which is obtained when the output of a gate is short circuited to the input);The high and low input voltage Vih and Vil are defined by the point where the gain (=dVout/dVin)of the VTC equals -12、Please draw the voltage transfer characteristic curve of the inverter and label the static operation points in the VTC.3、Please describe the definition of noise margin and its physical significance(物理意义), then draw the figure of definition of noise margins.The noise margins represent the levels of noise that can be sustained(所允许的) when gates are cascaded. A measure of the sensitivity of a gate to noise is given by the noise margins NML(noise margin low) and NMH(noise margin high), which quantize the size of the legal “0” and “1”, respectively, and set a fixed maximum threshold on the noise value4、Please describe the meaning of the regenerative property and the conditions of a gate with regenerative property.A gate with regenerative property ensures that a disturbed signal converges back to a nominal voltage level after passing through a number of logical stages. The VTC should have a transient region (or undefined region) with a gain greater than 1 in absolute value, bordered by the two legal zones, where the gain should be less than 1 in absolute value5、What are the definitions of the fan-out and fan-in properties?The number that can be driven is termed the fan-out of circuit, that denotes the number of load gates N that are connected to the output of the driving gate. The fan-in of a gate is defined as the number of independent input nodes to the gate.6、How to describe the performance of a digital IC? Please illustrate the parameters used to characterize the transient performance of a logic family, and draw the associated figure of the definition of these parP ropagation delay time and rise/fall time can be used to characterize the transient performance of a logic family .Propagation delay time of a gate expresses the delay experienced by a signal when passing through a gate,which represent how quickly the gate responds to the changes at its inputs.Rise/fall time express how fast a signal transits between the different levels. Propagation delay time is defined as the period between the 50%transition points of the input and output signals.Rise/fall time is defined as the period between the 10% and 90% points of the total voltage transition at the output waveforms.1、Illustrate the basic structure and simple operation principle of MOS transistor.Four terminals:source, drain, gate, body; Vertical Structure: gate electrode, insulator, semiconductor substrate; Horizontal Structure: source region, channel region, drain region2、Illustrate the basic function of each terminal of MOS device, and describe the general terminal connections of NMOS and PMOS transistor, respectively.The source and the drain are the electrodes conducting the current. The gate electrode is thecontrolling terminal. The function of the body is secondaryIn NMOS devices, the source is defined as the n+ region which has a lower potential(电势) than the other n+ region, the drain. The source is the terminal with the higher potential in PMOS devices, The body is generally connected to a DC supply that is identical for all devices of the same type (GND for NMOS, VDD for PMOS).3、What does the transition (or input) characteristic of MOS transistor mean? And what conclusions we can find from the characteristic curve?It describes the relationship between the gate-source voltage and the drain-source current with the certain drain-source voltage .When the gate-source voltage is less than the threshold voltage, the conducting current is zero, that is, the NMOS transistor is in cutoff operation. When is larger than, the NMOS transistor is on.4、What does the current-voltage (or output) characteristic of MOS transistor mean? And what conclusions we can find from the I-V characteristic curve?.It describes the relationship between the drain-source voltage and the drain-source current with a certain gate-source voltageVgs > Vt , 0<VDS <VGS -VT : Linear modeThe inversion layer forms a continuous current path between the source and the drain.A drain current proportional to Vds will flow from the drain to the source through the conducting channel. The channel region acts as a voltage-controlled linear resister.5、Describe the operation modes of NMOS and PMOS transistors respectively, and define the corresponding ideal current equations.1、Explain the channel-length modulation, sub-threshold conduction, short-channel effect and narrow-channel effect. And illustrate their corresponding chief impacts on the device.This simple current equation prescribes a linear drain-bias dependence for the current in MOS transistors, determined by the empirical model parameter λ, called the channel-length modulation coefficientOne typical condition, which is due to the two-dimensional nature of channel current flow, is the sub-threshold conduction in small-geometry MOS transistors.As a working definition, a MOS transistor is called a short-channel device if its channel length is on the same order of magnitude as the depletion region thicknesses of the source and drain junctions.The short-channel effects that arise in this case are attributed to two physical phenomena: the limitations imposed on electron drift characteristics in the channel; the modification of the threshold voltage due to the shortening channel lengthMOS transistor that have channel widths on the same order of magnitude as the maxium depletion region thickness are defined as narrow channel devices.For MOSFET with small channel widths,the actual threshold voltage increases as a result of this extra depletion charge of the fringe depletion region.This fact is called narrow channel effect.2、Describe the three main components of the load capacitanceCL, when a logic gate is driving other fan-out gates. And sketch the capacitance model of NMOS transistor.Gate capacitances (of other inputs connected to out)Diffusion(or junction) capacitances (of drain/source regions)Routing capacitances (output to other inputs)1,Describe the basic structure and operation of a static CMOS inverter. Then draw theassociated transistor schematicThis structure consists of an enhancement-type NMOS transistor and an enhancement-type PMOS transistor, operating in complementary mode. So this configuration is called Complementary MOS (CMOS). The gate terminals of the PMOS and NMOS transistors are connected to form the inverter input. The drain terminals of the PMOS and NMOS transistors are connected to form the inverter output. The source and the substrate of the NMOS transistor are connected to the ground, while the source and body of PMOS transistor are connected to VDD The circuit topology is complementary push-pull in the sense that: For high input the NMOS transistor drives (pulls down) the output node while the PMOS transistor acts as the load, and for low input the PMOS transistor drives (pulls up) the output node while the NMOS transistor acts as the load.When the input is at VDD: The NMOS is on (conducting) while the PMOS is off (cut-off). A direct path exists between Vout and the ground node, resulting in a steady-state value of 0V at the output. When the input is at ground:The NMOS is off while the PMOS is on. A direct path exists between VDD and Vout, yielding a high output voltage (equal to VDD).Static CMOS logic:structure:The static CMOS style is really an extension of the static CMOS inverter to multiple inputs. A logic function in static CMOS must be implemented in both NMOS and PMOS transistors. It is the combination of the pull-up network(PUN) and the pull-down network(PDN). Each input always connects to PUN and PDN simultaneously. The function of the PUN is to provide a connection between the output and VDD anytime the output of the logic gate is meant to be 1 (based on the inputs). The function of the PDN is to connect the output to VSS when the output of the logic gate is meant to be 0.Opreation: The pull-down net should be “on” when the pull-up net is “off” and vice versa. For any given input combination, the output is connected either to VDD or to ground via a low-resistance path. A DC current path between the VDD and ground is not established for any of the input combinations. With the complementary nature of NMOS and PMOS, the pull-up or the pull-down is “on” alternately to implement the logic operation.Discuss the main problems for high fan-in static CMOS gates and the associated techniques for fast complex gates.tpHL = 0.69 Reqn(C1+2C2+3C3+4CL); Propagation delay deteriorates(恶化) rapidly as a function of fan-in quadratically in the worst case, Gates with a fan-in greater than 4 become excessively slow and must be avoided.tPLH increases linearly due to the linearly increasing value of the diffusion capacitance;tPHL increase quadratically due to the simultaneous increase the resistance and internal capacitance in serial part.Transistor sizing: as long as fan-out capacitance dominatesProgressive transistor sizing: This approach reduces the dominant resistance, while keeping the increase in capacitance within boundsTransfer gate:Configuration:The source and drain nodes serve as inputs and outputs, while the gate node serves as the control input, the body node is connected to the power/ground Operation: For NMOS transfer gate,it turns on while the gate control terminal goes high, and the input signal will be delivered to the output node; it turns off while the gate control terminal goes low, and the output node will be impedance.CMOS transmission gate:Configuration: The CMOS transmission gate consists of one NMOS and one PMOS transistor, with the source and drain connected in parallel; The gate voltages appliedto these two transistors are also set to be complementary signals. The substrate terminal of the NMOS transistor is connected to ground and the substrate terminal of the PMOS transistor is connected to Vdd.Operation: If the control signal C is logic-high (equal to Vdd), then both transistors are turned on and provide a low-resistance current path between the input and output nodes. If the control signal C is logic-low, then both transistors will be off, and the path between the input and output nodes will be in the high-impedance state. The weakness of one device is overcome by the strength of the other device, whether the output is transmitting a high or low value. This is a clear advantage of the CMOS transfer gate over the single transistor counterpart.DCVLS:Operation: Assume now that, for a given set of inputs, PDN1 conducts while PDN2 does not, and that Out and out are initially high and low, respectively. Turning on PDN1: Causes Out to be pulled down (below VDD−|VTP |); Out is in a high impedance state, as M2 and PDN2 are both turned off. At the point M2 turns on and starts charging out非to VDD — eventually turning off M1; This in turn enables Out to discharge all the way to GND.XOR/XNOR: When the signals A and B have the same values, there is one conducting path either AB or A非B非; Then the output F is pulled down;At the same time, the other pull-down paths connected to the F非are both turned off. When F is pulled down below VDD−|VTP |, M2 t urns on and starts charging F非to VDD —eventually turning off M1 and pulling down F to Gnd. When the signals A and B have the different values, there is one conducting path either AB非or A非B; Then the output F非is pulled down; At the same time, the other pull-down paths connected to the F are both turned off. When F非is pulled down below VDD−|VTP |, M1 turns on and starts charging F to VDD —eventually turning off M2 and pulling down F非to Gnd.Precharge-Evaluate dynamic CMOS:Operation: Precharge (when the clock signal Φ= 0):The PMOS precharge transistor MP is conducting while the complementary NMOS transistor MN is off. The output load capacitance is precharged to VDD by MP, then VOH=VDD;The input voltages have no influence yet upon the output level since the complementary NMOS transistor MN is off. Evaluate (when the clock signal Φ=1):The precharge transistor MP turns off while the NMOS evaluate transistor MN turns on. The output node voltage may now remain at the logic-high level or drop to a logic low, depending on the input voltage levels: If the input signals create a conducting path between the output node and the ground, PDN is on, and the output capacitance will discharge toward VOL=0;Otherwise, when PDN is off, the output voltage remains at VOH= VDD.Domino dynamic CMOS logic:When Φ=0, during precharge: The output of the n-type dynamic gate is charged up to VDD, and the output of the inverter is set to 0. When Φ=1, during evaluation: The dynamic gate conditionally discharges, and there are two possibilities: The output node of the dynamic CMOS stage is either discharged to a low level through the NMOS circuitry (1 to 0 transition), or it remains high. Consequently, the inverter output voltage can also make at most one transition during the evaluation phase, from 0 to 1.TSPC dynamic CMOS logic:Configuration:If one constrains a NORA stage to have only n-precharge gates, and not static gates, then a p-channel transistor can be eliminated from the clocked latch; The dynamic circuit technique to be presented in that it uses only one-phase clock signal, so no clock skew problem exists. The NORA design style can be simplified so that a single clock is sufficient. For the doubled n-C2MOS latch, when φ= 1, the latch is in the transparent evaluate mode and corresponds to 2 cascaded inverters (non-inverting); For the doubled n-C2MOS latch, when φ= 0, both inverters are disabled (hold mode) -- only the pull-up network is still active.Pipelined NORA dynamic CMOS system:Configuration: Consists of an np-CMOS logic sequence and a clocked CMOS output buffer; A pipelined system can be constructed by simply cascading alternating φ-section and φ -section, meaning that evaluation occurs during active φ and φ respectively;Operation:φ=0, during hold mode :N block performs the precharge operation and pulls node Out1 up to VDD through the p-type device Mp1, while p block performs the discharge operation and pulls the node Out2 down to zero through the n-type device Mn2; The clocked CMOS latch will not be in operation and the previous output voltage will be stored on the output load capacitor CL. φ=1, during evaluate mode:All cascaded NMOS and PMOS blocks evaluate output levels one after the other, and then the signal Out2 will be inversed to the output node by the clocked CMOS latch in operation;Operation Mode: Evaluate―Hold: All logic stages perform the precharge-discharge operation when the clock is high, and all stages evaluate output levels when the clock is low. Therefore, wewill call this circuit a section, meaning that evaluation occurs during active .Clocked CMOS dynamic circuit:Basic Structure:A pair of PMOS and NMOS transistors controlled by the complementary clock signals are cascaded in the pullup and pulldown paths of the static CMOS gate, respectively, then a CMOS logic gate can be synchronized with a clock. Operation: φ=1, during evaluation mode:The transistors Mp1 and Mp2 are both turned on, then this gate can evaluate normally as a CMOS inverter to generate the logic output In非; φ=0 , during hold mode: Both transistors Mp1 and Mp2 are off, decoupling the output from the input. The CMOS circuit cannot conduct and evaluate, then the output Q retains its previous value stored on the output capacitor CL.Sequential logic:Virtually all useful systems require storage of state information, leading to another class of circuits called sequential logic circuits. In these circuits, the output not only depends upon the current values of the inputs, but also upon preceding output values. In other words, a sequential circuit remembers some of the past history of the system; A sequential circuit consists of a combinational circuit and a memory block in the feedback loop.Combination logic:In all logic circuits described so far, the output is directly related to the input. Typically, there are no feedback loops between the output and the input in these circuits (also classified as non-regenerative circuits), so the outputs are always a logical combination of the inputs. As a class, these circuits are known as combinational logic circuits. Combinational logic circuits, described earlier, have the property that the output of a logic block is only a function of the current input values, assuming that enough time has elapsed for the logic gates to settle. Static storage:preserve state as long as the power is on;are built using positive feedback or regeneration with an intentional connection between the output and the input;useful when updates are infrequent (clock gating)Dynamic storage:store state on parasitic capacitors;only hold state for short periods of time (milliseconds);require periodic refresh to annihilate charge leakage;usually simpler, so higher speed and lower power;useful in datapath circuits that require high performance levels and are periodically clockedLatch: level sensitive circuit that passes inputs to Q when the clock is high (or low);input sampledon the falling edge of the clock is held stable when clock is low (or high)Register or Flip-flops (edge-triggered): edge sensitive circuits that only sample the inputs on a clock transitionpositive edge-triggered: 0- 1negative edge-triggered: 1 -0built using latches (e.g., master-slave flip-flops)。

(完整版)数电1-10章自测题及答案(2)

第一章绪论一、填空题1、根据集成度的不同,数字集成电路分位以下四类:小规模集成电路、中规模集成电路、大规模集成电路、超大规模集成电路。

2、二进制数是以2为基数的计数体制,十六体制数是以16为基数的计数体制。

3、二进制数只有0和1两个数码,其计数的基数是2,加法运算的进位规则为逢二进一。

4、十进制数转换为二进制数的方法是:整数部分用除2取余法,小数部分用乘2取整法,十进制数23.75对应的二进制数为10111.11。

5、二进制数转换为十进制数的方法是各位加权系数之和,二进制数10110011对应的十进制数为179。

6、用8421BCD码表示十进制时,则每位十进制数可用四位二进制代码表示,其位权值从高位到低位依次为8、4、2、1。

7、十进制数25的二进制数是11001,其对应的8421BCD码是00100101。

8、负数补码和反码的关系式是:补码=反码+1。

9、二进制数+1100101的原码为01100101,反码为01100101,补码为01100101。

-1100101的原码为11100101,反码为10011010,补码为10011011。

10、负数-35的二进制数是-100011,反码是1011100,补码是1011101。

二、判断题1、二进制数有0~9是个数码,进位关系为逢十进一。

()2、格雷码为无权码,8421BCD码为有权码。

(√)3、一个n位的二进制数,最高位的权值是2^n+1。

(√)4、十进制数证书转换为二进制数的方法是采用“除2取余法”。

(√)5、二进制数转换为十进制数的方法是各位加权系之和。

(√)6、对于二进制数负数,补码和反码相同。

()7、有时也将模拟电路称为逻辑电路。

()8、对于二进制数正数,原码、反码和补码都相同。

(√)9、十进制数45的8421BCD码是101101。

()10、余3BCD码是用3位二进制数表示一位十进制数。

()三、选择题1、在二进制技术系统中,每个变量的取值为(A)A、0和1B、0~7C、0~10D、0~F2、二进制权值为(B )A、10的幂B、2的幂C、8的幂D、16的幂3、连续变化的量称为(B )A、数字量B、模拟量C、二进制量D、16进制量4、十进制数386的8421BCD码为(B)A、0011 0111 0110B、0011 1000 0110C、1000 1000 0110D、0100 1000 01105、在下列数中,不是余3BCD码的是(C )A、1011B、0111C、0010D、10016、十进制数的权值为(D )A、2的幂B、8的幂C、16的幂D、10的幂7、负二进制数的补码等于(D )A、原码B、反码C、原码加1D、反码加18、算术运算的基础是 ( A )A 、加法运算B 、减法运算C 、乘法运算D 、除法运算9、二进制数-1011的补码是 ( D )A 、00100B 、00101C 、10100D 、1010110、二进制数最高有效位(MSB )的含义是 ( A )A 、最大权值B 、最小权值C 、主要有效位D 、中间权值第二章 逻辑代数基础一、填空题1、逻辑代数中三种最基本的逻辑运算是与运算、或运算、非运算。

数字电路分析与设计_浙江大学中国大学mooc课后章节答案期末考试题库2023年

数字电路分析与设计_浙江大学中国大学mooc课后章节答案期末考试题库2023年1.若对8个特定对象进行编制,应该选择位二进制编码器。

参考答案:32.使逻辑函数【图片】为1的最小项有个参考答案:7##%_YZPRLFH_%##七3.条件中不可能出现的组合称为任意项,条件中不允许出现的组合称为约束项,约束项和任意项统称为无关项。

参考答案:正确4.将逻辑函数L=AB+AC+BC用卡诺图表示为:【图片】参考答案:正确5.和逻辑式【图片】相等的是参考答案:B6.已知N的反码为10110011,则补码为01001101。

参考答案:错误7.十进制数(-10)10的二进制补码表示为:参考答案:(10110)28.判断对错:D/A转换器输出模拟量的大小只取决于输入的数字量。

参考答案:错误9.执行Quartus II的______命令,可以检查设计电路错误。

参考答案:Compiler10.CPLD和FPGA器件______。

参考答案:在系统加电时可以对器件的内容进行重构11.某中规模集成计数器74HCXX的功能表和简化逻辑符号如下所示。

【图片】用该集成计数器连接而成的电路如下图所示。

该电路是(同步/异步)、(加法/减法)计数器;其中74HCXX(I)片连接成进制计数器;整个电路是进制计数器。

(答案间用中文分号隔开)【图片】参考答案:异步;加法;10;4412.已知集成计数器74HC193的功能表和引脚图如下所示,若利用反馈置数法设计一个余3码编码的10进制加计数器,则需要在输出Q3Q2Q1Q0=()时使置数端【图片】置为(),并将数据输入端D3D2D1D0置为()。

(答案间用中文分号隔开)【图片】【图片】参考答案:1101;0;001113.下列A/D转换器速度最快的是()。

参考答案:并行比较型A/D转换器14.用4选一的数据选择器扩展成16选一的数据选择器,若不加其它门电路,则最少需要()片4选一数据选择器。

参考答案:515.用中规模集成计数器74LS192构成的电路如图所示,则该电路功能为进制法(加/减)计数器。

数字集成电路设计与分析

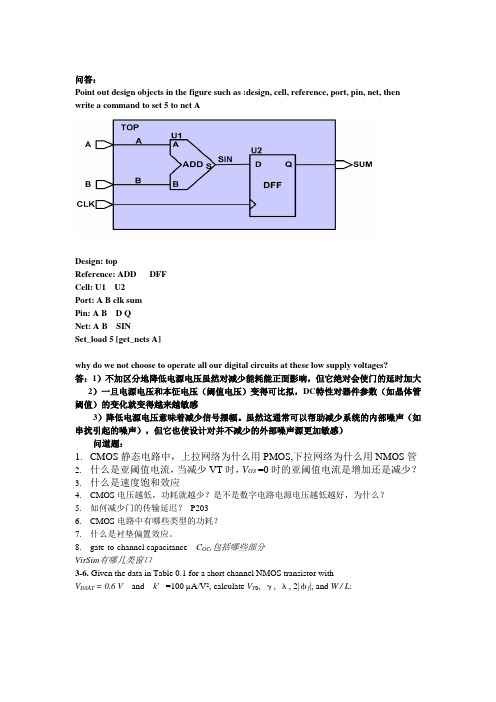

问答:Point out design objects in the figure such as :design, cell, reference, port, pin, net, then write a command to set 5 to net ADesign: topReference: ADD DFFCell: U1 U2Port: A B clk sumPin: A B D QNet: A B SINSet_load 5 [get_nets A]why do we not choose to operate all our digital circuits at these low supply voltages?答:1)不加区分地降低电源电压虽然对减少能耗能正面影响,但它绝对会使门的延时加大2)一旦电源电压和本征电压(阈值电压)变得可比拟,DC特性对器件参数(如晶体管阈值)的变化就变得越来越敏感3)降低电源电压意味着减少信号摆幅。

虽然这通常可以帮助减少系统的内部噪声(如串扰引起的噪声),但它也使设计对并不减少的外部噪声源更加敏感)问道题:1. CMOS静态电路中,上拉网络为什么用PMOS,下拉网络为什么用NMOS管2. 什么是亚阈值电流,当减少VT时,VGS =0时的亚阈值电流是增加还是减少?3. 什么是速度饱和效应4. CMOS电压越低,功耗就越少?是不是数字电路电源电压越低越好,为什么?5. 如何减少门的传输延迟? P2036. CMOS电路中有哪些类型的功耗?7. 什么是衬垫偏置效应。

8. gate-to-channel capacitance CGC,包括哪些部分VirSim有哪几类窗口3-6. Given the data in Table 0.1 for a short channel NMOS transistor withVDSAT = 0.6 V and k′=100 µA/V2, calculate VT0, γ, λ, 2|φf|, and W / L:解答:对于短沟道器件:在选择公式的时候,首先要确定工作区域,表格中的所有VDS均大于VDSAT,所以不可能工作在线性区域。

数字集成电路--电路、系统与设计(第二版)复习资料

第一章 数字集成电路介绍第一个晶体管,Bell 实验室,1947第一个集成电路,Jack Kilby ,德州仪器,1958 摩尔定律:1965年,Gordon Moore 预言单个芯片上晶体管的数目每18到24个月翻一番。

(随时间呈指数增长)抽象层次:器件、电路、门、功能模块和系统 抽象即在每一个设计层次上,一个复杂模块的内部细节可以被抽象化并用一个黑匣子或模型来代替。

这一模型含有用来在下一层次上处理这一模块所需要的所有信息。

固定成本(非重复性费用)与销售量无关;设计所花费的时间和人工;受设计复杂性、设计技术难度以及设计人员产出率的影响;对于小批量产品,起主导作用。

可变成本 (重复性费用)与产品的产量成正比;直接用于制造产品的费用;包括产品所用部件的成本、组装费用以及测试费用。

每个集成电路的成本=每个集成电路的可变成本+固定成本/产量。

可变成本=(芯片成本+芯片测试成本+封装成本)/最终测试的成品率。

一个门对噪声的灵敏度是由噪声容限NM L (低电平噪声容限)和NM H (高电平噪声容限)来度量的。

为使一个数字电路能工作,噪声容限应当大于零,并且越大越好。

NM H = V OH - V IH NM L = V IL - V OL 再生性保证一个受干扰的信号在通过若干逻辑级后逐渐收敛回到额定电平中的一个。

一个门的VTC 应当具有一个增益绝对值大于1的过渡区(即不确定区),该过渡区以两个有效的区域为界,合法区域的增益应当小于1。

理想数字门 特性:在过渡区有无限大的增益;门的阈值位于逻辑摆幅的中点;高电平和低电平噪声容限均等于这一摆幅的一半;输入和输出阻抗分别为无穷大和零。

传播延时、上升和下降时间的定义传播延时tp 定义了它对输入端信号变化的响应有多快。

它表示一个信号通过一个门时所经历的延时,定义为输入和输出波形的50%翻转点之间的时间。

上升和下降时间定义为在波形的10%和90%之间。

对于给定的工艺和门的拓扑结构,功耗和延时的乘积一般为一常数。

《数字电路-分析与设计》1--10章习题及解答(部分)_北京理工大学出版社

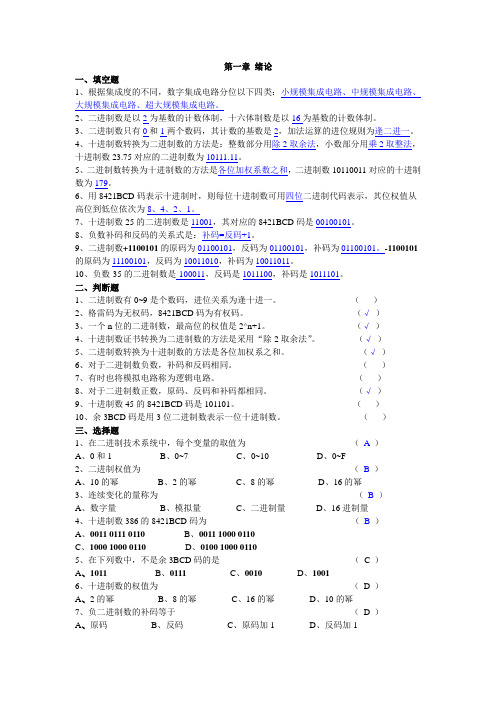

第五章习题5-1 图题5-1所示为由或非门组成的基本R-S 锁存器。

试分析该电路,即写出它的状态转换表、状态转换方程、状态图、驱动转换表和驱动方程,并画出它的逻辑符号,说明S 、R 是高有效还是低有效。

解:状态转换表:状态转换驱动表5-2 试写出主从式R-S 触发器的状态转换表、状态转换方程、状态图、驱动转换表和驱动方程,注意约束条件。

解:与R-S 锁存器类似,但翻转时刻不同。

5-3 试画出图5.3.1所示D 型锁存器的时序图。

解:G=0时保持,G=1时Q=D 。

图题5-1 或非门组成的基本R-S 锁存器S R状态转换方程:Q n+1Q n+1=S+RQ n状态转换图: S =Q n+1R=Q n+1 状态转换驱动方程: 逻辑符号: 输入高有效 G D Q图题5-3 D 型锁存器的时序图5-4试用各种描述方法描述D锁存器:状态转换表、状态转换方程、时序图、状态转换驱动表、驱动方程和状态转换图。

5-5锁存器与触发器有何异同?5-6试描述主从式RS触发器,即画出其功能转换表,写出状态方程,画出状态表,画出逻辑符号。

5-7试描述JK、D、T和T'触发器的功能,即画出它们的逻辑符号、状态转换表、状态转换图,时序图,状态转换驱动表,写出它们的状态方程。

5-8试分析图5.7.1(a) 所示电路中虚线内电路Q’与输入之间的关系。

5-9试分析图5.7.1(b)所示电路的功能,并画出其功能表。

5-10试用状态方程法完成下列触发器功能转换:JK→D, D→T, T→D, JK→T, JK→T’, D→T’。

解:JK→D:Q n+1=JQ+KQ,D:Q n+1=D=DQ+DQ。

令两个状态方程相等:D=DQ+DQ =JQ+KQ。

对比Q、Q的系数有:J=D,K=D逻辑图略。

5-11试用驱动表法完成下列触发器功能转换:JK→D, D→T, T→D, JK→T, JK→T’, D→T’。

解:略。

5-12用一个T触发器和一个2-1多路选择器构成一个JK触发器。

《数字电子技术基础》课后习题答案

《数字电路与逻辑设计》作业教材:《数字电子技术基础》(高等教育出版社,第2版,2012年第7次印刷)第一章:自测题:一、1、小规模集成电路,中规模集成电路,大规模集成电路,超大规模集成电路5、各位权系数之和,1799、01100101,01100101,01100110;11100101,10011010,10011011二、1、×8、√10、×三、1、A4、B练习题:1.3、解:(1)十六进制转二进制:45 C010*********二进制转八进制:010*********2134十六进制转十进制:(45C)16=4*162+5*161+12*160=(1116)10所以:(45C)16=(10001011100)2=(2134)8=(1116)10(2)十六进制转二进制:6D E.C8011011011110.11001000二进制转八进制:011011011110.1100100003336.62十六进制转十进制:(6DE.C8)16=6*162+13*161+14*160+13*16-1+8*16-2=(1758.78125)10所以:(6DE.C8)16=(011011011110. 11001000)2=(3336.62)8=(1758.78125)10(3)十六进制转二进制:8F E.F D100011111110.11111101二进制转八进制:100011111110.1111110104376.772十六进制转十进制:(8FE.FD)16=8*162+15*161+14*160+15*16-1+13*16-2=(2302.98828125)10所以:(8FE.FD)16=(100011111110.11111101)2=(437 6.772)8=(2302.98828125)10 (4)十六进制转二进制:79E.F D011110011110.11111101二进制转八进制:011110011110.1111110103636.772十六进制转十进制:(79E.FD)16=7*162+9*161+14*160+15*16-1+13*16-2=(1950. 98828125)10所以:(8FE.FD)16=(011110011110.11111101)2=(3636.772)8=(1950.98828125)101.5、解:(74)10 =(0111 0100)8421BCD=(1010 0111)余3BCD(45.36)10 =(0100 0101.0011 0110)8421BCD=(0111 1000.0110 1001 )余3BCD(136.45)10 =(0001 0011 0110.0100 0101)8421BCD=(0100 0110 1001.0111 1000 )余3BCD (374.51)10 =(0011 0111 0100.0101 0001)8421BCD=(0110 1010 0111.1000 0100)余3BCD1.8、解(1)(+35)=(0 100011)原= (0 100011)补(2)(+56 )=(0 111000)原= (0 111000)补(3)(-26)=(1 11010)原= (1 11101)补(4)(-67)=(1 1000011)原= (1 1000110)补第二章:自测题:一、1、与运算、或运算、非运算3、代入规则、反演规则、对偶规则 二、 2、×4、× 三、 1、B 3、D5、C练习题:2.2:(4)解:Y =AB̅+BD +DCE +A D =AB̅+BD +AD +A D +DCE =AB̅+BD +D +DCE =AB̅+D (B +1+CE ) =AB̅+D (8)解:Y =(A +B ̅+C )(D ̅+E ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅(A +B ̅+C +DE ) =[(A +B ̅+C )̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅+(D ̅+E ̅)̅̅̅̅̅̅̅̅̅̅](A +B ̅+C +DE ) =(ABC +DE )(ABC ̅̅̅̅̅̅+DE ) =DE2.3:(2)证明:左边=A +A (B +C)̅̅̅̅̅̅̅̅̅̅̅̅ =A +A +(B +C)̅̅̅̅̅̅̅̅̅̅ =A +B̅C ̅ =右式所以等式成立(4)证明:左边= (A B +AB̅)⨁C = (A B +AB ̅)C + (A B +AB̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅C = (A BC +AB ̅C )+A B ̅̅̅̅⋅AB̅̅̅̅⋅C =A BC +AB̅C +(A +B ̅)(A +B )C =A BC +AB̅C +(AB +A B ̅)C =A BC +AB̅C +ABC +A B ̅C 右边= ABC +(A +B +C )AB̅̅̅̅⋅BC ̅̅̅̅⋅CA ̅̅̅̅ =ABC +(A +B +C )[(A +B̅)(B ̅+C )(C +A )]=ABC +(A +B +C )(A B̅+A C +B ̅+B ̅C )(C +A ) =ABC +(A +B +C )(A B̅C +A C +B ̅C +A B ̅) =ABC +AB̅C +A BC +A B ̅C 左边=右边,所以等式成立 2.4(1)Y ′=(A +B̅C )(A +BC) 2.5(3)Y ̅=A B ̅̅̅̅(C +D ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅ C D ̅̅̅̅̅(A +B ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅ 2.6:(1)Y =AB +AC +BC=AB (C +C̅)+AC (B +B ̅)+BC (A +A ̅) =ABC +ABC̅+AB ̅C +A ̅BC 2.7:(1)Y =A B̅+B ̅C +AC +B ̅C 卡诺图如下:所以,Y =B2.8:(2)画卡诺图如下:Y(A,B,C)=A +B̅+C2.9:(1)画Y (A,B,C,D )=∑m (0,1,2,3,4,6,8)+∑d(10,11,12,13,14)如下:Y (A,B,C,D )=A B̅+D ̅2.10:(3)解:化简最小项式:Y =AB +(A B +C )(A B̅+C ) =AB +(A B A B̅+A BC +A B ̅C +C C ) =AB (C +C )+A BC +A B̅C =ABC +ABC ̅+A BC +A B ̅C =∑m (0,3,6,7)最大项式:Y =∏M(1,2,4,5)2.13:(3)Y =AB̅+BC +AB ̅C +ABC D ̅ =AB̅(1+C )+BC (1+AD ̅) =AB ̅+BC =AB ̅+BC ̿̿̿̿̿̿̿̿̿̿̿̿ = AB ̅̅̅∙BC ̅̅̅̅̅̅̅̅̅̅̅技能题:2.16 解:设三种不同火灾探测器分别为A 、B 、C ,有信号时值为1,无信号时为0,根据题意,画卡诺图如下:Y =AB +AC +BC =AB +AC +BC ̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿ =AB ̅̅̅̅⋅AC̅̅̅̅⋅BC ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ =(A +B ̅)(A +C )(B ̅+C )̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ =A +B ̅̅̅̅̅̅̅̅+A +C ̅̅̅̅̅̅̅̅+B ̅+C̅̅̅̅̅̅̅̅第三章:自测题:一、1、饱和,截止7、接高电平,和有用输入端并接,悬空; 二、 1、√ 8、√; 三、 1、A 4、D练习题:3.2、解:(a)因为接地电阻4.7k Ω,开门电阻3k Ω,R>R on ,相当于接入高电平1,所以Y =A B 1̅̅̅̅̅̅=A +B +0=A +B (e) 因为接地电阻510Ω,关门电0.8k Ω,R<R off ,相当于接入高电平0,所以、 Y =A +B +0̅̅̅̅̅̅̅̅̅̅̅̅̅=A ̅⋅B ̅∙1̅̅̅̅̅̅̅̅̅̅=A +B +0=A +B3.4、解:(a) Y 1=A +B +0̅̅̅̅̅̅̅̅̅̅̅̅̅=A +B ̅̅̅̅̅̅̅(c) Y 3=A +B +1̅̅̅̅̅̅̅̅̅̅̅̅̅=1̅=0(f) Y 6=A ⋅0+B ⋅1̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅=B̅3.7、解:(a) Y 1=A⨁B ⋅C =(A B +AB̅)C =A B C +AB ̅C3.8、解:输出高电平时,带负载的个数2020400===IH OH OH I I N G 可带20个同类反相器输出低电平时,带负载的个数78.1745.08===IL OL OL I I N G 反相器可带17个同类反相器3.12EN=1时,Y 1=A , Y 2=B̅ EN=0时,Y 1=A̅, Y 2=B3.17根据题意,设A 为具有否决权的股东,其余两位股东为B 、C ,画卡诺图如下,则表达结果Y 的表达式为:Y =AB +AC =AB +AC ̿̿̿̿̿̿̿̿̿̿̿=AB ̅̅̅̅⋅AC̅̅̅̅̅̅̅̅̅逻辑电路如下:技能题:3.20:解:根据题意,A 、B 、C 、D 变量的卡诺图如下:Y =ABC +ABD =ABC +ABD ̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿=ABC̅̅̅̅̅̅⋅ABD ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅电路图如下:第四章:自测题:一、2、输入信号,优先级别最高的输入信号7、用以比较两组二进制数的大小或相等的电路,A>B 二、 3、√ 4、√ 三、 5、A 7、C练习题:4.1;解:(a) Y =A⨁B +B ̅̅̅̅̅̅̅̅̅̅̅̅̅=A B +AB ̅+B ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅=A B +B ̅̅̅̅̅̅̅̅̅̅̅=A +B ̅̅̅̅̅̅̅̅=AB ,所以电路为与门。

数字集成电路分析和设计第四章答案

P4.1. Problem should refer to Figure P4.2.a. All inverters but the CMOS inverter consume static power then the output is high.Notice that in the first three inverters when the input is high, there is always a directconnection from V DD to G ND .b. None of the static inverters consumes power when the input is low because there is nopath from V DD to G ND .c. All inverters but the saturated enhancement inverter has a V OH of 1.2 V.d. Only the CMOS inverter has a V OL of 0 V.e. Except for the CMOS inverter, all the other inverte rs’ functionality depend on therelative sizes of the transistors.P4.2. Problem should refer to Figure P4.1a. Resistive loadb. Saturated-enhancement loadIterate to produce:To compute V OL we can ignore body effect and equate currents:Solve for 0.03OL V V ≈c. Linear-enhancement loadIterate to produce:This tells us that V GG should have been above 1.6V <closer to 1.7 V>.To compute V OL we can ignore body effect and equate currents. Note that the load issaturated even though we call it a linear-enhancement load. The driver is alsosaturated due to the device sizes used.Solve for 0.69V OL V ≈d. CMOSP4.3. For this problem, you are required to use the formulae:We already know that V OH =1.2 V and V OL =0 V. For V S use:Next V IL and V IH are estimated as follows:ThereforeWhen we cut the size of the PMOS device in half, the VTC shifts to the left. So V IL , V S , and V IH will all shift to the left. The recalculation of the switching threshold produces V S =0.566V. We can compute V IL to be roughly 0.533V and V IH to be roughly 0.667V.ThereforeP4.4. Similar approach as in P4.3. Run SPICE to check results.P4.5. First, set up the equation.Now solve for χ.This implies that a very large <W/L>P is needed to reach the desired value. It also reveals the limitations of the models. SPICE would be needed to obtain an acceptable solution if the switching threshold of 0.9V is truly desired.P4.6. SPICEP4.7. The advantages of the pseudo-PMOS is that it can reach a V OH of V DD while the pseudo-NMOS V OH can never reach that value. Additionally, the pseudo-NMOS’s V OH dependson the relative sizings of the inverters.The disadvantage is the dual of its advantage. The pseudo-PMOS inverter can never reach a V OL of 0 V. In addition, the pseudo-PMOS device will have to be approximately twice as large as a pseudo-NMOS device with comparable characteristics. This is due to the unequal mobility of holes and electrons. The pseudo-PMOS’s NMOS pull -down device is twice as strong as the pseudo-NMOS’s PMOS pull -up device, that means that the pseudo-PMOS’s PMOS wi ll have to be bigger than the NMOS device in a pseudo-NMOS.P4.8. a> Circuit is a buffer with degraded outputs.Output swing calculation:When IN DD V V =, output voltage is OH DD TN V V V =-. Since the source of NMOS transistor is not connected to substrate <ground>, we must take into account body effect.When 0IN V V =, output voltage is ||OL TP V V =. Since the source of PMOS transistor is not connected to substrate <V DD >, we must take into account body effect.Therefore the output swing is DD TN V V - to ||TP V with full accounting for body effect.b> Assume that the input is at 0 and the output is at |V TP |. As the input is increased, the output will stay constant until the NMOS device turns on. That will occur at V IN =|V TP |+V TN . The upper transistor behaves as a source follower and will pull the output along as the input rises until the output reaches V DD -V TN . However, as the input is reduced in value the output stays at its highvalue until the PMOS device turns on. This occurs at V IN=V DD-< |V TP|+V TN>. Then the PMOS device acts as a source follower and the output drops linearly to |V TP| as the input is reduced.c> The gain of the circuit is close to unity but slightly below this value. The circuit has poor noise rejection properties as it lacks the regenerative properties <this is a consequence of low gain>.d> SPICE run.P4.9.Resistive Load inverter:Saturated Enhancement Load inverter <ignoring body-effect>:Linear Enhancement Load inverter <ignoring body-effect>:The linear enhancement load inverter requires the largest pull-down device since it has the strongest pull up device. The resistive load inverter is next and the saturated enhancement load requires the smallest pull-down device.P4.10.We will illustrate the process and estimate the solutions for this problem.We already know that V OH=1.2 V and V OL=0 V. For V S use:Next V IL and V IH are estimated as follows:We can compute V IL to be roughly 0.533V.We can compute V IH to be roughly 0.667V.When we double the size of the PMOS device, the VTC shifts to the right. So V IL, V S, and V IH will all shift to the right. The recalculation of the switching threshold produces V S=0.6V.We can compute V IL to be roughly 0.55V and V IH to be roughly 0.65V.P4.11.The peak current would occur when both devices are in saturation and when V out=V in=V S.We can easily compute V S as:P4.12.As the required V OL becomes smaller, the W D/W L ratio becomes larger.P4.13.SPICEP4.14.The expression for the switching threshold of a CMOS inverter is:Solving for χ.Now solving for the ratio of sizes.Solving for χ.Now solving for the ratio of sizes.In the first case <0.6S DD V V >, the PMOS is much larger than the NMOS, so t PLH issmaller and t PHL is larger. The reverse is true for the second case.P4.15 <a> It does not have the regenerative property since the gain is less than one.<b> The last inverter would have an output of about 0.8V.<c> It is not possible to define the noise margin for this gate. Even a properinput eventually produces the incorrect output.P4.16 Both gates would work as a tristate buffer. However, as we shall find out in Chapter 7, the second one is prone to charge-sharing. That is, when the output is high and the EN signal is low, if the input goes high, the output may drop slightly in value due to loss of charge to the adjacent internal node.。

《数字电路与逻辑设计》第二章答案

选 RL=1K 2-6 已知题图 2-6 中各个门电路都是 74H 系列 TTL 电路,试写出各门电路的 输出状态(0,1 或 Z)

Vcc ViH NO_ INPUT

&

Y1

ViL

≥1ViH Y2& NhomakorabeaY3

0

≥1

Vcc ViL EN=1

1

10K

0

ViL

Y4

& Y5

Vcc

1K

=

Y6

100

1

1

0

题图 2-6 2-7 已知 TTL 三态门电路及控制信号 C1 ,C2 的波形如题图 2-7 所示,试分析 此电路能否正常工作。

vI2= vI1 =0.14V

(5)vI1 经 10K 电阻接地 2-3

vI2=1.4V

已知 TTL 门的参数是 VOH=3.5V, VOL=0.1V, VIHmin=2.4V, VILmax =0.3V,IIH=20

μA,IIS=1.0mA, IOH=360μA,IOL=8mA,求题图 2-3 中 R 的取值范围.

A B

100Ω ≥1

A F1 B

& F2

10K

(a) 题图 2-10

(b)

2-11 CMOS 门电路如题图 2-11 所示,试写出各门的输出电平。

题图 2-11 答案:(a)VDD 2-12 (b )0 (c)0

CMOS 与或非门不使用的输入端应如何连接?

答案:当在一起的两个输入端都不使用时,它们同时接地; 当在一起的两个输入端只有一个不使用时,它通过电阻接电源。

cmos的或非门电路可以得到当或非门的个输入端并接到高电平时三个并接的nmos管导通而三个串接的pmos管都截止所以其输入高电平总电流为3iih05167ohihcmos的与非门电路可以得到当与非门的个输入端并接到高电平时三个串接的nmos管都截止所以其输入高电平总电流为3iih05167ohihcmos的或非门电路可以得到当或非门的个输入端并接到低电平时三个并接的nmos管都截止而三个串接的pmos管导通所以其输入低电平总电流为3iil05167ohihcmos的与非门电路可以得到当与非门的个输入端并接到低电平时三个串接的nmos管都截止而三个并接的pmos管导通所以其输入低电平总电流为3iil05167olil总结以上结果对电路a能够驱动167个三输入端或非门对电路b能够驱动167个三输入端与非门

数字集成电路设计与分析

问答:Point out design objects in the figure such as :design, cell, reference, port, pin, net, then write a command to set 5 to net ADesign: topReference: ADD DFFCell: U1 U2Port: A B clk sumPin: A B D QNet: A B SINSet_load 5 [get_nets A]why do we not choose to operate all our digital circuits at these low supply voltages?答:1)不加区分地降低电源电压虽然对减少能耗能正面影响,但它绝对会使门的延时加大2)一旦电源电压和本征电压(阈值电压)变得可比拟,DC特性对器件参数(如晶体管阈值)的变化就变得越来越敏感3)降低电源电压意味着减少信号摆幅。

虽然这通常可以帮助减少系统的内部噪声(如串扰引起的噪声),但它也使设计对并不减少的外部噪声源更加敏感)问道题:1.CMOS静态电路中,上拉网络为什么用PMOS,下拉网络为什么用NMOS管2.什么是亚阈值电流,当减少VT时,V GS =0时的亚阈值电流是增加还是减少?3.什么是速度饱和效应4.CMOS电压越低,功耗就越少?是不是数字电路电源电压越低越好,为什么?5.如何减少门的传输延迟?P2036.CMOS电路中有哪些类型的功耗?7.什么是衬垫偏置效应。

8.gate-to-channel capacitance C GC,包括哪些部分VirSim有哪几类窗口3-6. Given the data in Table 0.1 for a short channel NMOS transistor withV DSAT = 0.6 V and k′=100 µA/V2, calculate V T0, γ, λ, 2|φf|, and W / L:解答:对于短沟道器件:2'min min [()](1)2DGS T DS V WI k V V V V L λ=--+ min min[(),,]GS T DS DSAT V V V V V =-在选择公式的时候,首先要确定工作区域,表格中的所有V DS 均大于V DSA T ,所以不可能工作在线性区域。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CHAPTER 2P2.1. a) The solution for the NMOS case is based on Example 2.4: The equation for V T0 is: 02BT FB F OXQ V V C φ=-- Calculate each individual component.1710()1362OX 077200611196310ln 0.026ln 0.44 V 1.4100.440.550.99 V 4 3.510 F/cm1.610 F/cm 310310/0.188 V 1.610610 1.6100.1.610i FpA GC Fp G gate OXB B OX OX OX n kT q NC Q Q C cmC Q C φφφφεε-------⨯==-=-⨯=-=--=-==⨯=⨯⨯=⨯==⨯⨯⨯⨯==⨯TO 06 V V 0.99(0.88)(0.188)0.0600.018 V=------=+ For the PMOS device:1710()77200611196TO 310ln 0.026ln 0.44 V 1.4100.440.550.99 V 310310/0.188 V1.610610 1.6100.06 V 1.610V 0.99(0.88)(0.188)0.0600.138 D Fn i GC Fn G gate B B OX OX OX N kT q n Q Q C cmC Q C φφφφ-----⨯===⨯=-=+=+⨯=⨯==⨯⨯⨯⨯==⨯=---=-Vb) The magnitude of V T0 would be higher. Since the device is PMOS this means that V T0 islowered. Since the only thing that’s been changed is the doping of the gate, only G φ changes. The new V T0 then becomes:00.110.880.1880.6 1.24V T V =----=-c) Since V T0 will be adjusted with implanted charge (Q I ):60.40.0180.382(1.610)(0.382)IOXIOXI Q C Q V C Q V -=-==⨯To calculate the threshold implant level N I :I I I I qN Q Q N q==For the NMOS device from part(a):6122190.610 3.8210/1.610I I Q N ions cm q --⨯=-=-=⨯⨯ (p-type) For the PMOS device from part(a):612219(1.610)(0.40.138)2.6210/1.610I I Q N ions cm q --⨯-=-=-=⨯⨯ (n-type) For the PMOS device from part(b):612219(1.610)(1.240.4)8.410/1.610I I Q N ions cm q --⨯-=-=-=⨯⨯ (p-type)d) The advantage of having the gate doping be n + for NMOS and p + for PMOS could be seen from analysis above. Doping the gates in such a way leads to devices with lower threshold voltages, but enables the implant adjustment with the same kind of impurities that used in the bulk (p-type for NMOS and n-type for PMOS). If we were to use the same kind of doping in gate as in the body (i.e. n + for PMOS and p + for NMOS) that would lead to higher un-implanted threshold voltages. Adjusting them to the required lower threshold voltage would necessitate implantation of the impurities of the opposite type near the oxide-Si interface. This is not desirable. Also, the doping of the poly gate can be carried out at the same time as the source and drain and therefore does not require an extra step.P2.2. First, convert ox t to units of cm:810100cm222210cm 10ox t -=⨯=ÅÅNow, using the mobility equation:()()20 1.8568130/V70cm0.8114102210pep nGS T ox cm V s V V t μμθ--==≈⎛⎫⎛⎫-+ ⎪⎪+ ⎪⎝⎭⎝⎭P2.3. a) For each transistor, derive the region of operation. In our case, for 0V,0.4V GS V =, thetransistor is in the cutoff region and there is no current. For 0.8V,1.2V GS V =, firstcalculate the saturation voltage Dsat V using:()GS T C DSAT GS T C V V E L V V V E L-=-+For our transistors, this would be:Next, we derive the IV characteristics using the linear and saturation current equations,we get the graphs shown below.IV Characteristic of NMOS01020304050607000.20.40.60.811.2Volts (V)C u r r e n t (u A )IV Characteristic of PMOSVolts (V)C u r r e n t (u A )To plot DS I vs. GS V , first identify the region of operation of the transistor. For GS T V V <, the transistor is in the cutoff region, and there is negligible current. For GS T V V > and GS DS V V ≤, the transistor is in the saturation region and saturation current expression should be used. The graphis shown below. Clearly, it is closer to the linear model.Ids vs. Vgs of NMOS010********607000.20.40.60.811.21.4Vgs (V)I d s (V )P2.4. For each transistor, first determine if the transistor is in cutoff by checking to see if V GS isless than or greater than V T . V T may have to be recalculated if the source of the transistor isn’t grounded. If V GS is less than V T , then it is in cutoff, otherwise, it is in either triode or saturation.To determine if it is in the triode saturation region, check to see if V DS is less than or greater than V DSAT . If V DS is less than V DSAT , then it is in triode, otherwise, it is in saturation. a. Cutoff00.200.2V0.4V GS G S T T GS TV V V V V V V =-=-===∴<b. Cutoff01.2 1.20V0.4V GS G S T T GS TV V V V V V V =-=-===∴<c. Linear01.20 1.2V0.4V GS G S T T GS TV V V V V V V =-=-===∴>The transistor is not in the cutoff region.()()()()()()1.20.460.20.48V 1.20.460.20.2V GS T C DSATGS T C DS DS DSATV V E L V V V E L V V V --===-+-+=∴<d. Saturation: In this case, because D G V V > the transistor is in the saturation region. To see this, recognize that in a long-channel transistor if D G V V >, the transistor is in saturation. Since the saturation drain voltage Dsat V is smaller in a velocity-saturated transistor than in a long-channel transistor, if the long-channel saturation region equation produces a saturated transistor, than the velocity-saturated saturation region equation will also.P2.5. In both cases, the first step it to calculate the maximum value of X V given G V . If thevoltage at the drain is higher than this maximum value, then ,max X X V V =, otherwise,X D V V =. The maximum value of X V is G T V V - but 0T T V V ≠ because of body effect andwe consider its effect.(),max 0001.20.40.988X G T G T G T G T V V V V V V V V V γγγγ=-=-+=--=--+=--=-There are two ways to calculate this, either through iteration or through substitution. Iteration:For the iteration method, we need a starting value for V X,max . A good starting value would be 0 1.20.40.8V G T V V -=-=. We plug this value on the RHS of the equation, calculate a new V X,max and repeat until we reach a satisfactory converged value.Old Vx,max New Vx,max 0.800 0.728 0.728 0.734 0.734 0.734In this, only three iterations are needed to reach 0.734V. Substitution:The term makes things a bit tricky, we get around this by making the following substitution:2,max 2,max 0.880.88X X x V V x =+∴=-Therefore:,max 220.9880.880.98800.2 1.87X V x x x =--=-=+-2,max 1.27, 1.470.880.733,1.28X x V x ===-=-= We use the first value since second value is above V DD . a. Since ,max D X V V >, ,max 0.733V X X V V ==. b. Since ,max D X V V <, ,max 0.6V X X V V ==. P2.6.a. Initially, when 0V in V =, the transistor is in the cutoff region and 0V X V =. Thisvalue is constant until V in exceeds V t 0. From then, X in T V V V =- and body effect must be taken into account. This trend continues until 0.7V X D V V ==, and the value of V inat that point must be calculated. From then on, 0.7V X D V V ==. To plot V X in the second region, we first derive an expression for V X vs. V in.(),max 0000.40.212X G T G T in T in T in in V V V V V V V V V V V γγγγ=-=-+=---=--=--=--Substituting:2,max2,max 0.880.88X X x V V x =+∴=-Therefore:,max 220.2120.880.21200.20.66X in in in V V x V x x V =---=--=+--220.880.88XxV x====-=-⎝⎭Since this is a quadratic function, there will be two graphs of V X. Only one of thesegraphs intersects with V X in the first region. In this case, plug 0.4inV= and see which one gives 0V. In our case, it would be the ‘+’ version of the quadratic.To see where region 3 begins, we simply isolate V in:()()()22220.880.2 2.710.2 2.71440.2 2.711.16V4XinVV=-⎝⎭-+-==+-==The final graph is shown in Figure 错误!未找到引用源。