FPGA各管脚简介

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AW AKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE 是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

fpga中各引脚的功能

分配fpga管脚时该怎么选择,引脚有什么属性需要考虑,quartus2中引脚有几个属性:Reserved,Group,I/O Bank,Vref Group,I/O standard( 3.3-VLVTTL(default) )分别是什么意思,要怎么设置?谢谢Totag 的回答,你看我的理解对不对:IO standard是根据你所要输入的电平来设置,Group是根据所分配的信号端口自动确定,而每个引脚的IO Bank本身已经确定!另外,分配的引脚所属的IO Bank不同有关系吗?引脚的分配除了要考虑专用引脚和用户引脚的区别外,还要考虑什么因素?首先说IO standard:这个是用于支持对应不同的电平标准。

FPGA IO口的电压由IO bank上的VCC引入。

一个bank上引入3.3V TTL电平,那么此时整个bank上输出3.3V的TTL电平。

设置这个第一是为了和current strength一起计算功率。

第二个是用于在IO口上加载正确的上拉/下拉电阻。

只要你设置完成,Quartus会按照你的电平标准自动布线。

第二是IO Bank:你在quartus pin planner 的top view下右键然后点击show IO banks,这个时候就会看到FPGA的管脚被几种颜色划分开了。

一种颜色下的IO 口代表一组bank。

你在吧管脚的location约束完成以后。

IO Bank会自动填充完毕的。

第三是Group:Group就是你所输出的信号的名字啦。

比如你有一组信号叫cnt。

你对cnt的某一根赋值,那么。

这里的Group会自动填充为cnt 。

第四是Reserved:这个是对管脚内部的IO逻辑进行约束的,你在下面可以看到一些值。

介绍几个吧。

bidrectional:双向,tri-state:三态等等。

这个约束的是FPGA 在IO端的输入输出区域的逻辑。

比如你选择tri-state。

那么这个时候,在你IO 口前部的IO区,quartus会自动给你生成一个三态门。

AlteraFPGA和Xilinx-FPGA-引脚功能详解解读

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O 口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE 被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

xilinxfpga引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

FPGA各管脚简介

用户I/O:不用解释了。

配置管脚:MSEL[1:0] 用于选择配置模式,比如AS、PS等。

DATA0 FPGA串行数据输入,连接到配置器件的串行数据输出管脚。

DCLK FPGA串行时钟输出,为配置器件提供串行时钟。

nCSO(I/O)FPGA片选信号输出,连接到配置器件的nCS管脚。

ASDO(I/O)FPGA串行数据输出,连接到配置器件的ASDI管脚。

nCEO 下载链期间始能输出。

在一条下载链中,当第一个器件配置完成后,此信号将始能下一个器件开始进行配置。

下载链上最后一个器件的nCEO悬空。

nCE 下载链器件始能输入,连接到上一个器件的nCEO,下载链的最后一个器件nCE接地。

nCNFIG 用户模式配置起始信号。

nSTATUS 配置状态信号。

CONF_DONE 配置结束信号。

电源管脚:VCCINT 内核电压。

130nm为1.5V,90nm为1.2VVCCIO 端口电压。

一般为3.3V,还可以支持多种电压,5V、1.8V、1.5VVREF 参考电压GND 信号地时钟管脚:VCC_PLL PLL管脚电压,直接连VCCIOVCCA_PLL PLL模拟电压,截止通过滤波器接到VCCINT上GNDA_PLL PLL模拟地GNDD_PLL PLL数字地CLK[n] PLL时钟输入PLL[n]_OUT PLL时钟输出特殊管脚:VCCPD 用于寻则驱动VCCSEL 用于控制配置管脚和PLL相关的输入缓冲电压PROSEL 上电复位选项NIOPULLUP 用于控制配置时所使用的用户I/O的内部上拉电阻是否工作TEMPDIODEN 用于关联温度敏感二极管******************************************************************************** ****************************************************1/1.I/O, ASDO在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用。

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍之马矢奏春创作注:技术交流用,希望对年夜家有所帮手.IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能.Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口.在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚酿成输出口.配置完成后,这些引脚又作为普通用户引脚.D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bitserial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位.D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs.An:O,A[25:0]为BPI模式的地址位.配置完成后,酿成用户I/O口.AWAKE:O,电源保管挂起模式的状态输出引脚.SUSPEND是一个专用引脚,AWAKE是一个多功能引脚.除非SUSPEND模式被使能,AWAKE被用作用户I/O.MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据.FCS_B:O,BPI flash 的片选信号.FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号.在SPI模式下,为SPI flsah片选信号.IRDY1/2,TRDY1/2:O,在PCI设计中,以LogiCORE IP方式使用.DOUT_BUSY:O,在SelectMAP模式下,BUSY暗示设备状态;在位串口模式下,DOUT提供配置数据流.RDWR_B_VREF:I,在SelectMAP模式下,这是一个低电平有效的写使能信号;配置完成后,如果需要,RDWR_B可以在BANK2中做为Vref.HSWAPEN:I,在配置之后和配置过程中,低电平使用上拉.INIT_B:双向,开漏,低电平暗示配置内存已经被清理;坚持低电平,配置被延迟;在配置过程中,低电平暗示配置数据毛病已经发生;配置完成后,可以用来指示POST_CRC状态.SCPn:I,挂起控制引脚SCP[7:0],用于挂起多引脚唤醒特性.CMPMOSI,CMPMISO,CMPCLK:N/A,保管.M0,M1:I,配置模式选择.M0=并口(0)或者串口(1),M1=主机(0)或者从机(1).CCLK:I/O,配置时钟,主模式下输出,从模式下输入.USERCCLK:I,主模式下,可行用户配置时钟.GCLK:I,这些引脚连接到全局时钟缓存器,在不需要时钟的时候,这些引脚可以作为惯例用户引脚.VREF_#:N/A,这些是输入临界电压引脚.当外部的临界电压不需要时,他可以作为普通引脚.当作作bank内参考电压时,所有的VRef都必需被接上.3.多功能内存控制引脚M#DQn:I/O,bank#内存控制数据线D[15:0]M#LDQS:I/O,bank#内存控制器低数据选通脚M#LDQSN:I/O,bank#中内存控制器低数据选通NM#UDQS:I/O,bank#内存控制器高数据选通脚M#UDQSN:I/O,bank#内存控制器高数据选通NM#An:O,bank#内存控制器地址线A[14:0]M#BAn:O,bank#内存控制bank地址BA[2:0]M#LDM:O,bank#内存控制器低位掩码M#UDM:O,bank#内存控制器高位掩码M#CLK:O,bank#内存控制器时钟M#CLKN:O,bank#内存控制器时钟,低电平有效M#CASN:O,bank#内存控制器低电平有效行地址选通M#RASN:O,bank#内存控制器低电平有效列地址选通M#ODT:O,bank#内存控制器外部内存的终端信号控制M#WE:O,bank#内存控制器写使能M#CKE:O,bank#内存控制器时钟使能M#RESET:O,bank#内存控制器复位4.专用引脚DONE_2:I/O,DONE是一个可选的带有内部上拉电阻的双向信号.作为输出,这个引脚说明配置过程已经完成;作为输入,配置为低电平可以延迟启动.PROGRAM_B_2:I,低电平异步复位逻辑.这个引脚有一个默认的弱上拉电阻.SUSPEND:I,电源呵护挂起模式的高电平有效控制输入引脚.SUSPEND是一个专用引脚,而AWAKE是一个复用引用.必需通过配置选项使能.如果挂起模式没有使用,这个引脚接地.TCK:I,JTAG鸿沟扫描时钟.TDI:I,JTAG鸿沟扫描数据输入.TDO:O,JTAG鸿沟扫描数据输出.TMS:I,JTAG鸿沟扫描模式选择5.保管引脚NC:N/A,CMPCS_B_2:I,保管,不接或者连VCCO_26.其它GND:VBATT:RAM内存备份电源.一旦VCCAUX应用了,VBATT可以不接;如果KEY RAM没有使用,推荐把VBATT接到VCCAUX或者GND,也可以不接.VCCAUX:辅助电路电源引脚VCCINT:内部核心逻辑电源引脚VCCO_#:输出驱动电源引脚VFS:I,(LX45不成用)编程时,key EFUSE电源供电引脚.当不编程时,这个引脚的电压应该限制在GND到 3.45V;当不使用key EFUSE时,推荐把该引脚连接到VCCAUX或者GND,悬空也可以.RFUSE:I,(LX45不成用)编程时,key EFUSE接地引脚.当不编程时或者不使用key EFUSE时,推荐把该引脚连接到VCCAUX或者GND,然而,也可以悬空.7.GTP 引脚MGTAVCC:收发器混合信号电路电源引脚MGTAVTTTX,MGTAVTTRX:发送,接收电路电源引脚MGTAVTTRCAL:电阻校正电路电源引脚MGTAVCCPLL0,MGTAVCCPLL1:锁相环电源引脚MGTREFCLK0/1P,MGTREFCLK0/1N:差分时钟正负引脚MGTRREF:内部校准终真个精密参考电阻引脚MGTRXP[1:0],MGTRXN[1:0]:差分接收端口MGTTXP[1:0],MGTTXN[1:0]:差分发送端口• 1. Spartan6系列封装概述Spartan6系列具有低本钱、省空间的封装形式,能使用户引脚密度最年夜化.所有Spartan6 LX器件之间的引脚分配是兼容的,所有Spartan6 LXT器件之间的引脚分配是兼容的,可是Spartan6 LX和Spartan6 LXT器件之间的引脚分配是不兼容的.表格 1Spartan6系列FPGA封装2. Spartan6系列引脚分配及功能详述Spartan6系列有自己的专用引脚,这些引脚是不能作为Select IO使用的,这些专用引脚包括:专用配置引脚,表格2所示 GTP高速串行收发器引脚,表格3所示表格 2Spartan6 FPGA专用配置引脚注意:只有LX75, LX75T, LX100, LX100T, LX150, and LX150T器件才有VFS、VBATT、RFUSE引脚.表格 3Spartan6器件GTP通道数目注意:LX75T在FG(G)484 和 CS(G)484中封装4个GTP通道,而在FG(G)676中封装了8个GTP通道;LX100T在FG(G)484 和 CS(G)484中封装4个GTP通道,而在FG(G)676 和FG(G)900中封装了8个GTP通道.如表4,每一种型号、每一种封装的器件的可用IO引脚数目不尽相同,例如对LX4 TQG144器件,它总共有引脚144个,其中可作为单端IO引脚使用的IO个数为102个,这102个单端引脚可作为51对差分IO使用,另外的32个引脚为电源或特殊功能如配置引脚.表格 4Spartan6系列各型号封装可用的IO资源汇总表格 5引脚功能详述3. Spartan6系列GTP Transceiver引脚如表6所示,对LX25T,LX45T而言,只有一个GTP Transceiver通道,它的位置是X0Y0,所再Bank号为101;其他信号GTP Transceiver的解释类似.表格 6GTP Transceiver所在Bank编号关于XILINX FPGA中VRP/VRN管脚的使用XILINX公司的Virtex系列FPGA芯片上,每个BANK都有一对VRP/VRN管脚.VRP/VRN管脚是一对多功能管脚,当一个BANK使用到某些DCI(Digitally Controlled Impedance)接口电平标准时,需要通过该BANK的VRP/VRN管脚接入参考电阻.此时,VRN通过一个参考电阻R上拉到Vcco,VRP通过一个参考电阻R下拉到地.VRP/VRN管脚提供一个参考电压供DCI内部电路使用,DCI内部电路依据此参考电压调整IO输出阻抗与外部参考电阻R匹配.当使用到DCI级联时,仅主BANK(master)需要通过VRP/VRN提供参考电压,从BANK(slave)不需要使用VRP/VRN,从BANK的VRP/VRN管脚可当作普通管脚使用.当VRP/VRN不用于DCI功能时,可用于普通管脚.不需要VRP/VRN外接参考电阻的DCI输出接口电平标准有:HSTL_I_DCIHSTL_III_DCIHSTL_I_DCI_18HSTL_III_DCI_18SSTL2_I_DCISSTL18_I_DCISSTL15_DCI不需要VRP/VRN外接参考电阻的DCI输入接口电平标准有:LVDCI_15LVDCI_18LVDCI_25LVDCI_DV2_15LVDCI_DV2_18LVDCI_DV2_25。

xilinxfpga引脚功能详细介绍

注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

在SPI模式下,为SPI flsah片选信号。

FPGA管脚分配图

169

FLAS H_ CS

156

音频 CODEC 模块(大板)

信号名称

对应 FPGA 引脚

SDIN

27

SCLK

33

CS

28

音频 CODEC 模块(小板)

信号名称

对应 FPGA 引脚

SDIN

93

SCLK

94

CS

88

音源模块

RESET

86

DATA

84

BUS Y

153

时钟源模块

信号名称 CLOCK(大板) CLOCK(小板)

216 VGA 接口(大板)

对应 FPGA 引脚

R

58

G

59

B

60

HS

61

VS 信号名称

62 VGA 接口(小板)

对应 FPGA 引脚

R

239

G

238

B

237

HS

235

VS 信号名称

236 PS/2 接口(大板上)

对应 FPGA 引脚

CLOCK

49

DATA 信号名称

82 PS/2 接口(大板下)

对应 FPGA 引脚

98

DB2

95

DB3

143

DB4

141

DB5

140

DB6

139

DB7

138

DB8

136

DB9

135

DB10

134

DB11

133

DB12

132

DB13

131

DB14

128

DB15

127

DB16

116

DB17

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能具体介绍之杨若古兰创作注:技术交流用,但愿对大家有所帮忙.IO_LXXY_# 用户IO引脚XX代表某个Bank内独一的一对引脚,Y=[P|N]代表对上升沿还是降低沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能.Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口.在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚酿成输出口.配置完成后,这些引脚又作为普通用户引脚.D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bitserial模式下,DIN是旌旗灯号数据的输入;在SPI模式下,MISO 是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位.D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs.An:O,A[25:0]为BPI模式的地址位.配置完成后,变成用户I/O口.AWAKE:O,电源保管挂起模式的形态输出引脚.SUSPEND是一个公用引脚,AWAKE是一个多功能引脚.除非SUSPEND模式被使能,AWAKE被用感化户I/O.MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平无效的片选旌旗灯号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一名数据.FCS_B:O,BPI flash 的片选旌旗灯号.FOE_B:O,BPI flash的输出使能旌旗灯号FWE_B:O,BPI flash 的写使用旌旗灯号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选旌旗灯号.在SPI模式下,为SPI flsah片选旌旗灯号.IRDY1/2,TRDY1/2:O,在PCI设计中,以LogiCORE IP方式使用.DOUT_BUSY:O,在SelectMAP模式下,BUSY暗示设备形态;在位串口模式下,DOUT提供配置数据流.RDWR_B_VREF:I,在SelectMAP模式下,这是一个低电平无效的写使能旌旗灯号;配置完成后,如果须要,RDWR_B可以在BANK2中做为Vref.HSWAPEN:I,在配置以后和配置过程中,低电平使用上拉.INIT_B:双向,开漏,低电平暗示配置内存曾经被清理;坚持低电平,配置被延迟;在配置过程中,低电平暗示配置数据错误曾经发生;配置完成后,可以用来唆使POST_CRC形态.SCPn:I,挂起控制引脚SCP[7:0],用于挂起多引脚唤醒特性.CMPMOSI,CMPMISO,CMPCLK:N/A,保存.M0,M1:I,配置模式选择.M0=并口(0)或者串口(1),M1=主机(0)或者从机(1).CCLK:I/O,配置时钟,主模式下输出,从模式下输入.USERCCLK:I,主模式下,可行用户配置时钟.GCLK:I,这些引脚连接到全局时钟缓存器,在不须要时钟的时候,这些引脚可以作为惯例用户引脚.VREF_#:N/A,这些是输入临界电压引脚.当内部的临界电压不须要时,他可以作为普通引脚.当做作bank内参考电压时,所有的VRef都必须被接上.3.多功能内存控制引脚M#DQn:I/O,bank#内存控制数据线D[15:0]M#LDQS:I/O,bank#内存控制器低数据选通脚M#LDQSN:I/O,bank#中内存控制器低数据选通NM#UDQS:I/O,bank#内存控制器高数据选通脚M#UDQSN:I/O,bank#内存控制器高数据选通NM#An:O,bank#内存控制器地址线A[14:0]M#BAn:O,bank#内存控制bank地址BA[2:0]M#LDM:O,bank#内存控制器低位掩码M#UDM:O,bank#内存控制器高位掩码M#CLK:O,bank#内存控制器时钟M#CLKN:O,bank#内存控制器时钟,低电平无效M#CASN:O,bank#内存控制器低电平无效行地址选通M#RASN:O,bank#内存控制器低电平无效列地址选通M#ODT:O,bank#内存控制器内部内存的终端旌旗灯号控制M#WE:O,bank#内存控制器写使能M#CKE:O,bank#内存控制器时钟使能M#RESET:O,bank#内存控制器复位4.公用引脚DONE_2:I/O,DONE是一个可选的带有内部上拉电阻的双向旌旗灯号.作为输出,这个引脚说明配置过程曾经完成;作为输入,配置为低电平可以延迟启动.PROGRAM_B_2:I,低电平异步复位逻辑.这个引脚有一个默认的弱上拉电阻.SUSPEND:I,电源呵护挂起模式的高电平无效控制输入引脚.SUSPEND是一个公用引脚,而AWAKE是一个复用援用.必须通过配置选项使能.如果挂起模式没有使用,这个引脚接地.TCK:I,JTAG鸿沟扫描时钟.TDI:I,JTAG鸿沟扫描数据输入.TDO:O,JTAG鸿沟扫描数据输出.TMS:I,JTAG鸿沟扫描模式选择5.保存引脚NC:N/A,CMPCS_B_2:I,保存,不接或者连VCCO_26.其它GND:VBATT:RAM内存备份电源.一旦VCCAUX利用了,VBATT可以不接;如果KEY RAM没有使用,推荐把VBATT接到VCCAUX或者GND,也能够不接.VCCAUX:辅助电路电源引脚VCCINT:内部核心逻辑电源引脚VCCO_#:输出驱动电源引脚VFS:I,(LX45不成用)编程时,key EFUSE电源供电引脚.当不编程时,这个引脚的电压应当限制在GND到3.45V;当不使用key EFUSE时,推荐把该引脚连接到VCCAUX或者GND,悬空也能够.RFUSE:I,(LX45不成用)编程时,key EFUSE接地引脚.当不编程时或者不使用key EFUSE时,推荐把该引脚连接到VCCAUX或者GND,然而,也能够悬空.7.GTP 引脚MGTAVCC:收发器混合旌旗灯号电路电源引脚MGTAVTTTX,MGTAVTTRX:发送,接收电路电源引脚MGTAVTTRCAL:电阻校订电路电源引脚MGTAVCCPLL0,MGTAVCCPLL1:锁相环电源引脚MGTREFCLK0/1P,MGTREFCLK0/1N:差分时钟正负引脚MGTRREF:内部校准终端的精密参考电阻引脚MGTRXP[1:0],MGTRXN[1:0]:差分接收端口MGTTXP[1:0],MGTTXN[1:0]:差分发送端口• 1. Spartan6系列封装概述Spartan6系列具有低成本、省空间的封装方式,能使用户引脚密度最大化.所有Spartan6 LX器件之间的引脚分配是兼容的,所有Spartan6 LXT器件之间的引脚分配是兼容的,但是Spartan6 LX和Spartan6 LXT器件之间的引脚分配是不兼容的.表格 1Spartan6系列FPGA封装2. Spartan6系列引脚分配及功能胪陈Spartan6系列有本人的公用引脚,这些引脚是不克不及作为Select IO使用的,这些公用引脚包含:公用配置引脚,表格2所示 GTP高速串行收发器引脚,表格3所示表格 2Spartan6 FPGA公用配置引脚留意:只要LX75, LX75T, LX100, LX100T, LX150, and LX150T器件才有VFS、VBATT、RFUSE引脚.表格 3Spartan6器件GTP通道数目留意:LX75T在FG(G)484 和 CS(G)484中封装4个GTP通道,而在FG(G)676中封装了8个GTP通道;LX100T在FG(G)484 和 CS(G)484中封装4个GTP通道,而在FG(G)676 和 FG(G)900中封装了8个GTP通道.如表4,每一种型号、每一种封装的器件的可用IO 引脚数目不尽不异,例如对于LX4 TQG144器件,它总共有引脚144个,其中可作为单端IO引脚使用的IO个数为102个,这102个单端引脚可作为51对差分IO使用,另外的32个引脚为电源或特殊功能如配置引脚.表格 4Spartan6系列各型号封装可用的IO资本汇总表格 5引脚功能胪陈3. Spartan6系列GTP Transceiver引脚如表6所示,对LX25T,LX45T而言,只要一个GTP Transceiver通道,它的地位是X0Y0,所再Bank号为101;其他旌旗灯号GTP Transceiver的解释类似.表格 6GTP Transceiver所在Bank编号关于XILINX FPGA中VRP/VRN管脚的使用XILINX公司的Virtex系列FPGA芯片上,每个BANK都有一对VRP/VRN管脚.VRP/VRN管脚是一对多功能管脚,当一个BANK使用到某些DCI(Digitally Controlled Impedance)接口电平尺度时,须要通过该BANK的VRP/VRN管脚接入参考电阻.此时,VRN通过一个参考电阻R上拉到Vcco,VRP通过一个参考电阻R下拉到地.VRP/VRN管脚提供一个参考电压供DCI内部电路使用,DCI内部电路根据此参考电压调整IO输出阻抗与内部参考电阻R匹配.当使用到DCI级联时,仅主BANK (master)须要通过VRP/VRN提供参考电压,从BANK (slave)不须要使用VRP/VRN,从BANK的VRP/VRN管脚可当成普通管脚使用.当VRP/VRN不必于DCI功能时,可用于普通管脚.不须要VRP/VRN外接参考电阻的DCI输出接口电平尺度有:HSTL_I_DCIHSTL_III_DCIHSTL_I_DCI_18HSTL_III_DCI_18SSTL2_I_DCISSTL18_I_DCISSTL15_DCI不须要VRP/VRN外接参考电阻的DCI输入接口电平尺度有:LVDCI_15LVDCI_18LVDCI_25LVDCI_DV2_15LVDCI_DV2_18 LVDCI_DV2_25。

Altera FPGA和 Xilinx-FPGA-引脚功能详解

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O 口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE 被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

FPGA各管脚简介

用户I/O:不用解释了。

配置管脚:MSEL[1:0] 用于选择配置模式,比如AS、PS等。

DATA0 FPGA串行数据输入,连接到配置器件的串行数据输出管脚。

DCLK FPGA串行时钟输出,为配置器件提供串行时钟。

nCSO(I/O)FPGA片选信号输出,连接到配置器件的nCS管脚。

ASDO(I/O)FPGA串行数据输出,连接到配置器件的ASDI管脚。

nCEO 下载链期间始能输出。

在一条下载链中,当第一个器件配置完成后,此信号将始能下一个器件开始进行配置。

下载链上最后一个器件的nCEO悬空。

nCE 下载链器件始能输入,连接到上一个器件的nCEO,下载链的最后一个器件nCE接地。

nCNFIG 用户模式配置起始信号。

nSTATUS 配置状态信号。

CONF_DONE 配置结束信号。

电源管脚:VCCINT 内核电压。

130nm为1.5V,90nm为1.2VVCCIO 端口电压。

一般为3.3V,还可以支持多种电压,5V、1.8V、1.5VVREF 参考电压GND 信号地时钟管脚:VCC_PLL PLL管脚电压,直接连VCCIOVCCA_PLL PLL模拟电压,截止通过滤波器接到VCCINT上GNDA_PLL PLL模拟地GNDD_PLL PLL数字地CLK[n] PLL时钟输入PLL[n]_OUT PLL时钟输出特殊管脚:VCCPD 用于寻则驱动VCCSEL 用于控制配置管脚和PLL相关的输入缓冲电压PROSEL 上电复位选项NIOPULLUP 用于控制配置时所使用的用户I/O的内部上拉电阻是否工作TEMPDIODEN 用于关联温度敏感二极管******************************************************************************** ****************************************************1/1.I/O, ASDO在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用。

xilinxfpga引脚功能详细介绍

Xilinx F PGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户10引脚XX代表某个Bank内唯一的一对引脚,Y=[PIN]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_#多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn: I/O (在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出曰。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISOl: I,在并口模式(SelectMAP/BPI)下,DO 是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_M1SO2, D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBsoAn: 0, A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O 口。

AWAKE: O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE 是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISOO: I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下, CSI_B 是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISOO是SPI总线的第一位数据。

FCS_B: 0, BPI flash 的片选信号。

FOE_B: O, BPI flash的输出使能信号FWE_B: O, BPI flash的写使用信号LDC: O, BPI模式配置期间为低电平HDC: O, BPI模式配置期间为高电平CSO_B: O,在并口模式下,工具链片选信号。

FPGA配特殊引脚的含义

这是一个专用的配置状态脚。双向脚,当它是输出脚时,是漏极开路的。当作为状态输出脚时,在配置之前和过程中,它都被置为低电平。一旦配置数据接收完成,并且没有任何错误,初始化周期一开始,CONF_DONE 就会被释放。当作为状态输入脚时,在所有数据都被接收后,要将它置为高电平。之后器件就开始初始化再进入用户模式。它不可以用作普通I/O来用。这个脚外成也必须接一个10K 欧的电阻。

2.I/O,nCSO

在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用.在AS 模式下,这个脚是CII 用来给外面的串行配置芯片发送的使能脚。在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效。这个脚是低电平有效的。直接接到配置芯片的/CS 脚(第1 脚)。

3.I/O,CRC_ERROR

9. nCONFIG

专用的输入管脚。这个管脚是一个配置控制输入脚。如果这个脚在用户模式下被置低,FPGA就会丢失掉它的配置数据,并进入一个复位状态,并将所有的I/O 脚置成三态的。nCONFIG从低电平跳变到高电平的过程会初始化重配置的过程。如果配置方案采用增强型的配置器件或EPC2,用户可以将nCONFIG 脚直接接到VCC 或到配置芯片的nINIT_CONF 脚上去。这个脚带了输入Buffer,支持施密特触发器的磁滞功能。实际上,在用户模式下,nCONFIG信号就是用来初始化重配置的。当nCONFIG 脚被置低后,初始化进程就开始了。当nCONFIG脚被置低后,CII 就被复位了,并进入了复位状态,nSTATUS 和CONF_DONE 脚被置低,所有的I/O 脚进入三态。nCONFIG 信号必须至少保持2us。当nCONFIG 又回到高电平状态后,nSTATUS 又被释放。重配置就开始了。在实际应用过程中可以将nCONFIG 脚接一个10K 的上拉电阻到3.3V.

fpga 的正负输入管脚

fpga 的正负输入管脚

FPGA(Field-Programmable Gate Array)的正负输入管脚是指用于接收电信号的引脚。

在FPGA 中,通常有两个管脚用于接收差分信号,即正输入和负输入。

正输入管脚(Positive Input Pin)通常用于接收信号的正极或非反相信号。

它是差分信号对中的一个端点,用于传输正相位的信号。

负输入管脚(Negative Input Pin)则用于接收信号的负极或反相信号。

它是差分信号对中的另一个端点,用于传输反相位的信号。

通过使用差分输入,FPGA 可以更好地抵抗噪音干扰,并提供更可靠的信号传输。

这种差分输入结构通常用于高速数字电路中,例如高速串行通信接口(如PCIe、USB等)。

XilinxFPGA引脚功能详细介绍

Xilinx FPGA 引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户 IO 引脚XX 代表某个 Bank 内唯一的一对引脚, Y=[P|N] 代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ 代表在用户 IO 的基本上添加一个或多个以下功能。

Dn: I/O (在 readback 期间),在 selectMAP 或者 BPI 模式下, D[15:0] 配置为数据口。

在从 SelectMAP 读反馈期间,如果 RDWR_B=1 ,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1 : I,在并口模式(SelectMAP/BPI )下,DO 是数据的最低位,在 Bit-serial 模式下, DIN 是信号数据的输入;在 SPI 模式下, MISO 是主输入或者从输出;在 SPI*2 或者 SPI*4 模式下, MISO1 是 SPI 总线的第二位。

D1_MISO2,D2_MISO3 : I,在并口模式下, D1和D2是数据总线的低位;在 SPI*4模式下, MISO2 和MISO3 是 SPI 总线的 MSBs。

An: O, A[25:O] 为 BPI 模式的地址位。

配置完成后,变为用户 I/O 口。

AWAKE : O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非 SUSPEND 模式被使能, AWAKE 被用作用户 I/O。

MOSI_CSI_B_MISO0 : I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B 是一个低电平有效的片选信号;在 SPI*2 或者 SPI*4 的模式下, MISOO 是 SPI 总线的第一位数据。

FCS_B:O, BPI flash 的片选信号。

FOE_B:O, BPI flash 的输出使能信号FWE_B : O, BPI flash 的写使用信号LDC :O, BPI 模式配置期间为低电平HDC:O, BPI 模式配置期间为高电平CSO_B: O,在并口模式下,工具链片选信号。

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍之答禄夫天创作注:技术交流用,希望对大家有所帮忙。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚酿成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bitserial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变成用户I/O口。

AWAKE:O,电源保管挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

FPGA的配置引脚说明

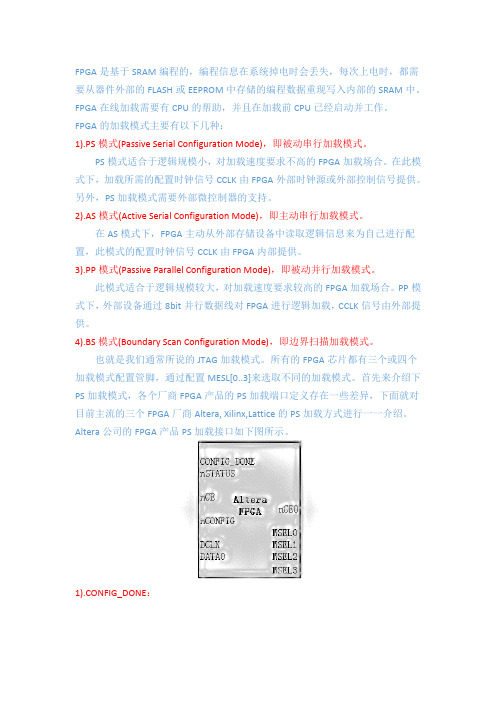

FPGA是基于SRAM编程的,编程信息在系统掉电时会丢失,每次上电时,都需要从器件外部的FLASH或EEPROM中存储的编程数据重现写入内部的SRAM中。

FPGA在线加载需要有CPU的帮助,并且在加载前CPU已经启动并工作。

FPGA的加载模式主要有以下几种:1).PS模式(Passive Serial Configuration Mode),即被动串行加载模式。

PS模式适合于逻辑规模小,对加载速度要求不高的FPGA加载场合。

在此模式下,加载所需的配置时钟信号CCLK由FPGA外部时钟源或外部控制信号提供。

另外,PS加载模式需要外部微控制器的支持。

2).AS模式(Active Serial Configuration Mode),即主动串行加载模式。

在AS模式下,FPGA主动从外部存储设备中读取逻辑信息来为自己进行配置,此模式的配置时钟信号CCLK由FPGA内部提供。

3).PP模式(Passive Parallel Configuration Mode),即被动并行加载模式。

此模式适合于逻辑规模较大,对加载速度要求较高的FPGA加载场合。

PP模式下,外部设备通过8bit并行数据线对FPGA进行逻辑加载,CCLK信号由外部提供。

4).BS模式(Boundary Scan Configuration Mode),即边界扫描加载模式。

也就是我们通常所说的JTAG加载模式。

所有的FPGA芯片都有三个或四个加载模式配置管脚,通过配置MESL[0..3]来选取不同的加载模式。

首先来介绍下PS加载模式,各个厂商FPGA产品的PS加载端口定义存在一些差异,下面就对目前主流的三个FPGA厂商Altera, Xilinx,Lattice的PS加载方式进行一一介绍。

Altera公司的FPGA产品PS加载接口如下图所示。

1).CONFIG_DONE:加载完成指示输出信号,I/O接口,高有效,实际使用中通过电阻上拉到VCC,使其默认状态为高电平,表示芯片已加载完毕,当FPGA正在加载时,会将其驱动为低电平。

xilinxfpga管脚类型

xilinxfpga管脚类型

xilinx fpga 管脚类型

xilinx fpga 管脚类型

XilinxFPGA是一种可编程逻辑设备,它的管脚类型包括以下几种:

1.输入型(Input):用于向FPGA中输入数据或控制信息。

2.输出型(Output):用于从FPGA中输出数据或控制信息。

3.双向型(Bidirectional):用于同时进行输入和输出操作。

4.三态型(TriState):具有三态输出能力,可以将输出置为高阻态(High-Z)。

5.时钟型(Clock):用于提供时钟信号,通常用于同步输入和输出数据。

6.电源与接地型(Power and Ground):用于连接到电源和地线,提供电源和接地功能。

FPGA管脚类型的选择取决于具体的应用需求。

在设计过程中,需要根据信号类型、频率和电压等因素选择合适的管脚类型。

同时,还需要考虑管脚的数量和布局,以便满足整个系统的电路连接需求。

- 1 -。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

这是一个专用的配置状态脚。双向脚,当它是输出脚时,是漏极开路的。当作为状态输出脚时,在配置之前和过程中,它都被置为低电平。一旦配置数据接收完成,并且没有任何错误,初始化周期一开始,CONF_DONE 就会被释放。当作为状态输入脚时,在所有数据都被接收后,要将它置为高电平。之后器件就开始初始化再进入用户模式。它不可以用作普通I/O来用。这个脚外成也必须接一个10K 欧的电阻。

7/13.I/O,VREF

用来给某些差分标准提供一个参考电平。没有用到的话,可以当成I/O 来用。

14/20. DATA0

专用输入脚。在AS 模式下,配置的过程是:CII 将nCSO 置低电平,配置芯片被使能。CII然后通过DCLK 和ASDO 配合操作,发送操作的命令,以及读的地址给配置芯片。配置芯片然后通过DATA 脚给CII 发送数据。DATA 脚就接到CII 的DATA0 脚上。CII 接收完所有的配置数据后,就会释放CONF_DONE 脚(即不强制使CONF_DONE 脚为低电平),CONF_DONE 脚是漏极开路(Open-Drain)的。这时候,因为CONF_DONE 在外部会接一个10K 的电阻,所以它会变成高电平。同时,CII 就停止DCLK 信号。在CONF_DONE 变成高电平以后(这时它又相当于变成一个输入脚),初始化的过程就开始了。所以,CONF_DONE 这个脚外面一定要接一个10K 的电阻,以保证初始化过程可以正确开始。 DATA0,DCLK,NCSO,ASDO 脚上都有微弱的上拉电阻,且一直有效。在配置完成后,这些脚都会变成输入三态,并被内部微弱的上拉电阻将电平置为高电平。在AS 模式下,DATA0就接到配置芯片的DATA(第2 脚)。

PLL[n]_OUT PLL时钟输出

特殊管脚:

VCCPD 用于寻则驱动

VCCSEL 用于控制配置管脚和PLL相关的输入缓冲电压

PROSEL 上电复位选项

NIOPULLUP 用于控制配置时所使用的用户I/O的内部上拉电阻是否工作

TEMPDIODEN 用于关联温度敏感二极管

nCNFIG 用户模式配置起始信号。

nSTATUS 配置状态信号。

CONF_DONE 配置结束信号。

电源管脚:

VCCINT 内核电压。130nm为1.5V,90nm为1.2V

VCCIO 端口电压。一般为3.3V,还可以支持多种电压,5V、1.8V、1.5V

VREF 参考电压

ASDO(I/O)FPGA串行数据输出,连接到配置器件的ASDI管脚。

nCEO 下载链期间始能输出。在一条下载链中,当第一个器件配置完成后,此信号将始能下一个器件开始进行配置。下载链上最后一个器件的nCEO悬空。

nCE 下载链器件始能输入,连接到上一个器件的nCEO,下载链的最后一个器件nCE接地。

当错误检测CRC 电路被选用时,这个脚就被作为CRC_ERROR 脚,如果不用默认就用来做I/O。但要注意,这个脚是不支持漏极开路和反向的。当它作为CRC_ERROR 时,高电平输出则表示出现了CRC 校验错误(在配置SRAM 各个比特时出现了错误)。CRC 电路的支持可以在setting 中加上。这个脚一般与nCONFIG 脚配合起来用。即如果配置过程出错,重新配置.

I/O 脚或漏极开路的输出脚。当这个脚被使能后,该脚上从低到高的跳变指示FPGA 已经进入了用户模式。如果INIT_DONE 输出脚被使能,在配置完成以后,这个脚就不能被用做用户I/O 了。在QuartusII 里面可以通过使能Enable INIT_DONE 输出选项使能这个脚。

76/108. nCEO

2/2.I/O,nCSO

在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用.在AS 模式下,这个脚是CII 用来给外面的串行配置芯片发送的使能脚。在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效。这个脚是低电平有效的。直接接到配置芯片的/CS 脚(第1 脚)。

3/3.I/O,CRC_ERROR

15/21. DCLK

PS 模式下是输入,AS 模式下是输出。在PS 模式下,DCLK 是一个时钟输入脚,是外部器件将配置数据传送给FPGA 的时钟。数据是在DCLK 的上升沿把数据,在AS 模式下,DCLK脚是一个时钟输出脚,就是提供一个配置时钟。直接接到配置芯片的DCLK 脚上去(第6脚)。无论是哪种配置模式,配置完成后,这个脚都会变成三态。如果外接的是配置器件,配置器件会置DCLK 脚为低电平。如果使用的是主控芯片,可以将DCLK 置高也可以将DCLK 置低。配置完成后,触发这个脚并不会影响已配置完的FPGA。这个脚带了输入Buffer,支持施密特触发器的磁滞功能。

82/121. nSTATUS

这是一个专用的配置状态脚。双向脚,当它是输出脚时,是漏极开路的。在上电之后,FPGA立刻将nSTATUS 脚置成低电平,并在上电复位(POR)完成之后,释放它,将它置为高电平。作为状态输出脚时,在配置过程中如果有任何一个错误发生了,nSTATUS 脚会被置低。作为状态输入脚时,在配置或初始化过程中,外部控制芯片可以将这个脚拉低,这时候FPGA就会进入错误状态。这个脚不能用作普通I/O 脚。nSTATUS 脚必须上拉一个10K 欧的电阻。

I/O 脚或输出脚。当配置完成后,这个脚会输出低电平。在多个器件的配置过程中,这个脚会连接到下一个器件的nCE 脚,这个时候,它还需要在外面接一个10K 的上拉电阻到Vccio。多个器件的配置过程中,最后一个器件的nCEO 可以浮空。如果想把这个脚当成可用的I/O,需要在软件里面做一下设置。另外,就算是做I/O,也要等配置完成以后。

142/206 DEV_CLRn

I/O 或全局的清零输入端。在QuartusII 里面,如果选上Enable Device-Wide Reset(DEV_CLRn)这个功能。这个脚就是全局清零端。当这个脚被置低,所有的寄存器都会被清零。这个脚不会影响到JTAG 的边界扫描或编程的操作。

用户I/O:不用解释了。

配置管脚:

MSEL[1:0] 用于选择配置模式,比如AS、PS等。

DATA0 FPGA串行数据输入,连接到配置器件的串行数据输出管脚。

DCLK FPGA串行时钟输出,为配置器件提供串行时钟。

nCSO(I/O)FPGA片选信号输出,连接到配置器件的nCS管脚。

GND 信号地

时钟管脚:

VCC_PLL PLL管脚电压,直接连VCCIO

VCCA_PLL PLL模拟电压,截止通过滤波器接到VCCINT上

GNDA_PLL PLL模拟地

GNDD_PLL PLL数字地

CLK[n] PLL时钟输入

4/4.I/O,CLKUSR

当在软件中打开Enable User-supplled start-up clock(CLKUSR)选项后,这个脚就只可以作为用户提供的初始化时钟输入脚。在所有配置数据都已经被接收后,CONF_DONE 脚会变成高电平,CII 器件还需要299 个时钟周期来初始化寄存器,I/O 等等状态,FPGA 有两种方式,一种是用内部的晶振(10MHz),另一种就是从CLKUSR 接进来的时钟(最大不能超过100MHz)。有这个功能,可以延缓FPGA 开始工作的时间,可以在需要和其它器件进行同步的特殊应用中用到。

在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用。在AS 模式下,这个脚是CII 向串行配置芯片发送控制信号的脚。也是用来从配置芯片中读配置数据的脚。在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效,配置完成后,该脚就变成三态输入脚。ASDO 脚直接接到配置芯片的ASDI 脚(第5 脚)。

16/22. nCE

专用输入脚。这个脚是一个低电平有效的片选使能信号。nCE 脚是配置使能脚。在配置,初始化以及用户模式下,nCE 脚必须置低。在多个器件的配置过程中,第一个器件的nCE 脚要置低,它的nCEO 要连接到下一个器件的nCE 脚上,形成了一个链。nCE 脚在用JTAG编程模式下也需要将nCE 脚置低。 这个脚带了输入Buffer,支持施密特触发器的磁滞功能。

84/125,85/126. MSEL[1:0]

这些脚要接到零或电源,表示高电平或低电平。00 表示用AS 模式,10 表示PS 模式, 01是FAST AS 模式.如果用JTAG 模式,就把它们接00, JTAG 模式跟MSEL 无关,即用JTAG模式,MSEL 会被忽略,但是因为它们不能浮空,所以都建议将它接到地。

20/26. nCONFIG

专用的输入管脚。这个管脚是一个配置控制输入脚。如果这个脚在用户模式下被置低,FPGA就会丢失掉它的配置数据,并进入一个复位状态,并将所有的I/O 脚置成三态的。nCONFIG从低电平跳变到高电平的过程会初始化重配置的过程。如果配置方案采用增强型的配置器件或EPC2,用户可以将nCONFIG 脚直接接到VCC 或到配置芯片的nINIT_CONF 脚上去。这个脚带了输入Buffer,支持施密特触发器的磁滞功能。实际上,在用户模式下,nCONFIG信号就是用来初始化重配置的。当nCONFIG 脚被置低后,初始化进程就开始了。当nCONFIG脚被置低后,CII 就被复位了,并进入了复位状态,nSTATUS 和CONF_DONE 脚被置低,所有的I/O 脚进入三态。nCONFIG 信号必须至少保持2us。当nCONFIG 又回到高电平状态后,nSTATUS 又被释放。重配置就开始了。在实际应用过程中可以将nCONFIG 脚接一个10K 的上拉电阻到3.3V.

************************************************************************************************************************************1/1.I/O, ASDO