Cyclone_III配置

EP3C10E144C8中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

对于Cyclone III器件最大额定值.

表1-1 列出绝对

芯片中文手册,看全文,戳

1–2

第 1章: Cyclone III器件数据表

电气特性

1

超出所列条件

表1-1 对器件造成永久性损坏.

此外,在延长时间周期绝对最大额定值设备操作具有设备不利影响.

表 1-1. Cyclone III器件绝对最大额定值

(1)

符

参数

况

过冲持续时间为%高时间

VI = 3.95 V

100

VI = 4.0 V

95.67

VI = 4.05 V

55.24

VI = 4.10 V

31.97

VI = 4.15 V

18.52

VI = 4.20 V

10.74

Vi

交流输入 电压

VI = 4.25 V VI = 4.30 V

6.23 3.62

Cyclone III器件.稳态电压和预期电流值

III器件中提供旋风

表1-3.

没有高原.

所有系统必须严格单调

表 1-3. Cyclone III器件推荐工作条件

(1), (2)

符

参数

条件

Min Typ Max Unit

VCCINT (3)

电源电压为内部逻辑

电源电压为输出缓冲器,3.3-V

手术

—

1.15 1.2 1.25

运行条件

当Cyclone III器件在一个系统中实现,它们是根据一组定义参数分级.为防护持 Cyclone III器件中最高性能和可靠性,系统设计人员必须考虑本文件中操 作要求. Cyclone III器件提供商用,工业和汽车级版本.商业设备在-6(最 快),-7和-8速度等级提供.工业和汽车设备仅在-7速度年级课程.

FPGA具体型号及参数

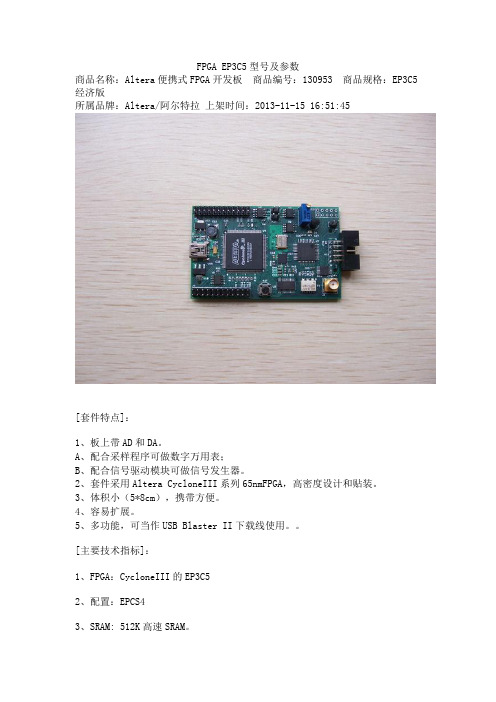

FPGA EP3C5型号及参数

商品名称:Altera便携式FPGA开发板商品编号:130953 商品规格:EP3C5经济版

所属品牌:Altera/阿尔特拉上架时间:2013-11-15 16:51:45

[套件特点]:

1、板上带AD和DA。

A、配合采样程序可做数字万用表;

B、配合信号驱动模块可做信号发生器。

2、套件采用Altera CycloneIII系列65nmFPGA,高密度设计和贴装。

3、体积小(5*8cm),携带方便。

4、容易扩展。

5、多功能,可当作USB Blaster II下载线使用。

[主要技术指标]:

1、FPGA:CycloneIII的EP3C5

2、配置:EPCS4

3、SRAM: 512K高速SRAM。

4、常用电压型DA :1 路10Bit,1.25 MHz maximum update rate

5、AD :1 路10Bit,1.25 MSPS

6、1个LED指示

7、1个复位按钮

8、24M有源晶振

9、2个24针扩展座,支持20个扩展IO,4个CLK输入。

10、四层板,通过全板EMC/EMI和SI仿真。

11、高速电流型DA:可选1 路14Bit 165MSPS(完全版才有此项)。

Altera Cyclone III系列FPGA开发板简介

ETL-002 Altera Cyclone III系列FPGA开发板简介概述ETL-002 FPGA开发板是以Altera公司的最新系列Cyclone III中的3C10为主芯片,并提供了极为丰富的芯片外围接口资源以及下载线,数据线以及资料光盘等。

除了这些硬件外,我们还提供了十多个接口实验,并公开了电路原理图和实验的Verilog源代码,以便于大家对照学习,并可以在该开发板上进行二次开发。

单板描述主芯片EP3C10提供了10320个逻辑单元(LE),46块SRAM(每块9K bits), 23个18*18的乘法器。

开发板自带USB供电电路:您只需将USB线插上您的USB端口,无需外接+5V直流电源,开发板即可工作。

开发板同时支持AS模式下载和JTAG模式下载。

程序固化既可通过JTAG口也可直接对板上的FLASH进行编程。

丰富的外围接口可满足常用的外设的人机交互,我们还将剩下未用的40个用户I/O引脚全部引出,使得您可以通过这些信号对本开发板进行电路扩展。

这些接口主要包括:PS2鼠标接口:可以将PS2鼠标的任何移动的信息反应在数码管上PS2键盘接口:可以将PS2键盘上的任意按键以16进制的信息反应在数码管上VGA显示器接口:可以将FPGA产生的信息反映在VGA显示器上。

开发板自带了动态彩条显示的功能双串口接口:可以与任何的串口设备相接。

开发板自带的演示程序是将PC上的超级终端中输入的任何信息返回PC 4位数码管:可以实时显示任何的数字信息。

开发板自带的演示程序实时地显示分钟和秒钟的信息。

4位LED灯:用于指示状态。

开发板自带了跑马灯实验。

4位按键开关:可用于复位等作用。

4位拨码开关:可用于电路的选择作用教学实验除了开发板的丰富的硬件资源外,我们还提供了数十个学习实验。

通过这些实验,您可以学习FPGA芯片,Quartus II软件和设计仿真和下载等FPGA的设计流程,然后将试验中程序执行的信息通过数码管,LED 灯,串口等板上的硬件直观的显示出来。

Cyclone III资料

Cyclone III原型开发调试转载:/ilove314/1819329/Message.aspx 最近设计的Cyclone III原型板是特权同学第一次接触Cyclone III的器件。

原理图、PCB绘制、管脚分配上都碰到了一些问题,这些问题或多或少都是由于个人对新器件不熟悉、设计的时候有一些粗心大意造成的。

主要针对板级的硬件设计,这里凌乱的罗列一下,做一点总结,今后要多吸取教训,低级的失误要尽量避免。

1. 首先要提一个没有解决的问题,EP3C5E144/EP3C10E144/ EP3C16E144/ EP3C 25E144(是管脚完全兼容的不同资源的器件,Altera在这一点上是非常值得称道的)器件的PIIN11和PIN12存在不可同时使用的问题,这个问题出现在架构了一个NIOS2系统里集成了EPCS控制器的时候,在Cyclone II中是不需要分配这个EPCS控制器的管脚的(内部自动映射),而Cyclone III则需要手动分配(事先需要到Setting里动动手脚)。

EPCS的DCLK需要分配到PIN12上,工程中分配了一个SDRAM的D0脚给PIN11,编译到Fitting阶段就Error了。

在handbook里海找没什么成效,求助于搜索引擎,最终看到有人遇到相同的问题,但是给出的却是不是办法的解决办法:不用PIN11或者不用PI N12。

这个问题上特权同学也很是无可奈何,估计是Cyclone III器件的这两个脚做了一些信号耦合之类的检查,也不知道是否在工具选项里做一些设置可以取消此类检查。

也很期待有相同遭遇的朋友现身说法,告诉特权如何解决问题。

2. 再说两个很低级的错误,错的很傻,没有什么技术含量,只能给自己敲个警钟:干活的时候脑子一定要清醒。

两个错误分别和BOM表和网络标号有关。

先说和BOM表有关的,这个错误源于原理图上两个三端稳压器-1.2和-2.5的标示刚好反过来了,因为管脚定义和封装都一样所以也没留意,好在最后只影响BOM表的标示,但这也导致了第一块样板焊接的时候出现了1.2V和2.5V互换位置的惨剧,结果可想而知,EP3C10E144C7就这样挂了,非常的心疼。

EP3C25F256C8N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

–40 — 125 °C

50 µs — 50毫秒 —

50 µs — 3毫秒 —

—

—

10

mA

须知 表 1-3:

(1) V 所有I / O块设备操作过程中都必须启动.所有V 必须启动和关断同时.

管脚必须供电到2.5 V(即使不使用PLL)和

(2) V

必须始终连接到V

通过一个去耦电容和铁素体珠.

(3)购买V 必须上升单调.

(1)

符

参数

况

过冲持续时间为%高时间

VI = 3.95 V

100

VI = 4.0 V

95.67

VI = 4.05 V

55.24

VI = 4.10 V

31.97

VI = 4.15 V

18.52

VI = 4.20 V

10.74

Vi

交流输入 电压

VI = 4.25 V VI = 4.30 V

6.23 3.62

对于Cyclone III器件最大额定值.

表1-1 列出绝对

芯片中文手册,看全文,戳

1–2

第 1章: Cyclone III器件数据表

电气特性

1

超出所列条件

表1-1 对器件造成永久性损坏.

此外,在延长时间周期绝对最大额定值设备操作具有设备不利影响.

表 1-1. Cyclone III器件绝对最大额定值

符

参数

VCCINT VCCIO

VCCA

电源电压为内部逻辑

电源电压为输出缓冲器

电源电压(模拟),用于锁相环 (PLL)调节器

VCCD_PLL VI I OUT

VESDHBM

电源电压(数字)PLL

cyclone3引脚整理

FLASH_nC E, nCSO

I/O, Output(A S, AP Note 13

DATA1, ASDO

PLL[1..4 ]_CLKOUT p Note 3

I/O, Output

Clock, Input

来自于 PLL [1..4]. 的可选 positive 正端外部 时钟输出 。该引脚 如果被用 作PLL输 出,能被 指定为单 端或差分 I/O标准 。

专用全局 时钟输入 引脚,用 于差分全 局时钟输 入或用户 输入引脚 的 negative 负端输入 。不支持 编程弱上 拉电阻。 不使用时 连接到 GND,注9.

MSEL[0.. 3]

Input

配置输入 引脚,用 来设置 Cyclone III 设备 配置方案 。一些较 小的设备 或包装选 项不支持 AP注 13flash 编程,不 使用 MSEL3引 脚。

这些引脚 内部连接 5-KΩ resistor to GND。 当未被使 用时,连 接至GND, 不悬空。 Device Family Handbook :配置, 设计安全 性, Cyclone III Devices 远程系统 升级。如 果使用 JTAG 配 置,连到 GND.

nCE 应 该接到 模式,则 GND

CONF_DON E

Bidirect ional (opendrain)

专用配置 状态引 脚,随着 状态输 出,在配 置前和配 置期间, CONF_DON E pin drives low 当状态输 入,所有 数据被接 收后, CONF_DON E变为高 。然后设 备初始 化,进入 用户使用 模式。该 引脚不可 做I/O引 脚,引脚 应被拉 高,通过 上拉电阻 被释放。 10-KΩ.

Cyclone III的LVDS接口注意事项

Cyclone III的LVDS接口注意事项对于Cyclone III器件,handbook中明确提到了以下的一些注意事项:1.对于作为LVDS传输的bank必须接2.5V的VCCIO。

2.左右bank(即1/2/5/6bank)的LVDS发送差分对信号无需外接匹配电阻,上下bank(即3/4/7/8bank)则需要。

3.分配管脚时,左右bank的LVDS差分信号在IO分配时选择IO标准为LVDS;上下bank的LVDS差分信号在IO分配时选择IO标准为LVDS_E_3R,好像没什么特殊含义,应该是帮助开发工具识别是哪个bank上的LVDS信号而已吧。

多谢网友iampeter在博文中提到这一点,帮助没太认真消化handbook的特权同学解决了这个问题。

除此以外,还有其它的一些技巧和注意事项,特权同学做了一点归纳:1.在分配管脚时,只要指定LVDS信号的p端(+),则n端(-)自动匹配;实际在verilog 中只要一个信号接口即可,无需一个差分对接口定义在源代码中。

2.可以使用MegaWizard中的IP核ALTLVDS实现并串转换的LVDS传输。

具体配置和说明建议参考相关手册。

3.接收部分没有进行测试和实验,不做归纳和整理。

4. 图1是一个7位并行输入的LVDS数据发送采集的波形,可以看到在默认输出时钟相位情况下,最高位bit6置1时为时钟上升沿后的第一个数据。

数据传送的效果大体如图2所示。

实际传输的相位是可以根据需要调整的。

图1 (上为时钟,下位数据)参考资料:1. /iampeter/240246/Message.aspx#2. Cyclone III handbook。

EP3C25Q240C8N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

手术

—

1.15 1.2 1.25

V

—

3.135 3.3 3.465 V

电源电压为输出缓冲器,3.0-V

手术

—

2.85

3

3.15

V

VCCIO (3), (4)

电源电压为输出缓冲器,2.5-V

手术

电源电压为输出缓冲器,1.8-V

手术

电源电压为输出缓冲器,1.5-V

手术

—

2.375 2.5 2.625 V

(4)所有输入缓冲器由在V驱动

供电.

(5)50-200毫秒之间POR时间标准POR范围.每个单独电源应达到在推荐工作范围 50毫秒.

3-9毫秒(6)POR时间,快速POR范围.每个单独电源应在3毫秒达到推荐工作范围内.

芯片中文手册,看全文,戳

第 1章: Cyclone III器件数据表

表1-2 列出所允许最大输入电压过冲和 过冲电压作为在装置寿命百分比持续时间. 允许最大过冲持续时间被指定为高时间比设备寿命百分比.

Max

Unit

1.8

V

3.9

V

3.75

V

1.8

V

3.95

V

40

mA

±2000

V

±500

V

150

°C

125

°C

表1-2 and

芯片中文手册,看全文,戳

芯片中文手册,看全文,戳

July 2012 CIII52001-3.5

CIII52001-3.5

1.Cyclone III器件数据表

本章介绍电气特性,开关特性,以及I / O

对Cyclone时机

CycloneIII使用注意事项V1.0

© 2008 Cytech Technology Ltd – Confidential

Notice6:在使用增量编译时的告警

在使用增量编译的时候,如果在子工程中分配了管脚,在导出.QXP网表 文件以及在定层导入网表的时候,QUARTUS会出现如下的警告,会造成 用户的误解,导出网表时的警告:

Warning: Complex I/O atoms found during Design Partition Export Warning: Node GZ_DATA[0] is a non-trivial IO atom Warning: Node GZ_DATA[1] is a non-trivial IO atom Warning: Node GZ_DATA[2] is a non-trivial IO atom Warning: Node GZ_DATA[3] is a non-trivial IO atom Warning: Node GZ_DATA[4] is a non-trivial IO atom Warning: Node GZ_DATA[5] is a non-trivial IO atom Warning: Node GZ_DATA[6] is a non-trivial IO atom Warning: Node GZ_DATA[7] is a non-trivial IO atom Warning: Node flash_d[0] is a non-trivial IO atom Warning: Node flash_d[1] is a non-trivial IO atom Warning: Node flash_d[2] is a non-trivial IO atom Warning: Node flash_d[3] is a non-trivial IO atom Warning: Node flash_d[4] is a non-trivial IO atom Warning: Node flash_d[5] is a non-trivial IO atom Warning: Node flash_d[6] is a non-trivial IO atom Warning: Node flash_d[7] is a non-trivial IO atom

CYCLONE III EPCS使用方法

一、只使用FPGA硬件资源,不使用NIOS的时候

需要将nCEO引脚设为用户引脚,注意:一般编译器是默认它为程序下载的引脚的

将nCEO设为用户IO,其它的保留原样

二、使用NIOS的时候

由于CD0板子上没有设计FLASH。

所以在使用NIOS的时候,需要把程序存在EPCS器件中。

CYCLONE III器件跟其它器件的EPCS使用方法不同。

将DEVICE AND PIN OPTIONS页全部置为USER IO

在SOPC中添加epcs_flash_controller

在FPGA工程的顶层模块中添加EPCS控值器的接口

在NIOS的FLASH PROGRAMMER中做如下设置

将FPGA的SOF文件用QUARTUS的通过JTAG下载到FPGA后,

在NIOS的FLASH PROGRAMMER中点这时,NIOS的FLASH

PROGRAMMER会把.SOF文件和NIOS生成的.ELF文件合在一起,生成另一个配置文件下载到板子上的EPCS芯片中

重新上电,FPGA就以正常运行NIOS+FPGA的程序了

注意:在使用NIOS的时候FPGA的PIN_22因为太靠近PIN_23:DCLK(FPGA提供给EPCS 芯片的时钟)而不能再使用(使用时QUARTUS编译器会报错)。

PIN_22对应了CD0板子上的GPIO1[13],

所以在有NIOS的工程中都没有使用这一个引脚,对应的有NIOS的FPGA顶层也写成了如下:

跳过了…[12]这个引脚。

Cyclone III FPGA系列

Cyclone III FPGA系列:一切皆有可能前所未有的同时实现了低功耗、高性能和低成本Cyclone® III FPGA系列前所未有的同时实现了低功耗、高性能和低成本,大大提高了您的竞争力。

其特性以及Cyclone III FPGA体系结构为您的大批量、低功耗、低成本应用提供了理想的解决方案。

为满足您独特的设计需求,这一FPGA系列包括:∙Cyclone III:功耗最低、成本最低的高性能FPGA∙Cyclone III LS:具有安全特性、功耗最低的FPGA Cyclone III LS器件具有200K逻辑单元、8 Mbits嵌入式存储器以及396个嵌入式乘法器,是高性能处理、低功耗应用的理想选择,包括:轻松达到您的功耗目标具有200K逻辑单元(LE)、8-Mbits存储器,而静态功耗不到1/4瓦,该系列设立了功耗标准。

采用台积电(TSMC)的低功耗(LP)工艺技术进行制造,无论是通信设备、手持式消费类产品,还是软件无线电设备,这些FPGA都能够轻松满足您的功耗预算。

设计安全性Cyclone III LS FPGA利用低功耗、高性能FPGA平台,在硬件、软件和知识产权(IP)层面上率先实现了一系列安全特性。

一系列安全特性保护了您的IP不被篡改、逆向剖析和克隆。

而且,这些器件还使您能够通过设计分离特性,在一个芯片中实现冗余功能,从而减小了实际应用的体积、重量和功耗。

全面的设计资源为确保流畅、成功的设计流程,帮助您更快的将构思变为收益,Altera 提供全面的Cyclone III FPGA设计环境,包括:∙Quartus® II开发软件∙成熟的IP库∙Nios® II,世界上最通用的嵌入式处理器∙低成本开发套件∙专用参考设计将您的设计从构思变为产品,更迅速推向市场。

采用Cyclone III FPGA,一切皆有可能。

相关链接∙观看划分FPGA设计,实现冗余和信息安全网播∙下载Cyclone III FPGA手册(PDF)∙观看Cyclone III FPGA视频Cyclone III 器件系列体系结构Cyclone® III FPGA前所未有地同时实现了低功耗、低成本和高性能。

DE0使用说明中文

第 3 章.

DE0 控制面板 ..............................................................................................12

3.1 初始化控制面板 ............................................................................................................................... 12 3.2 控制 LED 及七段数码管 .................................................................................................................. 14 3.3 开关和按钮 ....................................................................................................................................... 16 3.4 SDRAM 以及 Flash 控制器和编程器................................................................................................ 16 3.5 PS/2 设备........................................................................................................................................... 18 3.6 SD 卡.................................................................................................................................................. 19 3.7 VGA ................................................................................................................................................... 19

利用高级Cyclone_III_FPGA_PLL,提高灵活性,增加集成度

利用高级Cyclone III FPGA PLL,提高灵活性,增加集成度-技术白皮书来源:EDACN摘要:在使用FPGA时,经常忽略了它的一个优点——能够集成时钟解决方案。

这种集成能力不但降低了系统成本,而且最新的65-nm Altera®Cyclone®III FPGA支持高级时钟管理和锁相环(PLL)技术,因此,还极大地提高了设计灵活性。

设计人员利用Cyclone III时钟管理功能,管理整个FPGA和电路板的时钟系统。

而且,由于Cyclone III PLL集成在FPGA中,可以利用Altera 的Quartus®II设计环境,轻松进行设置和配置。

关键词:FPGA,Cyclone III FPGA PLL,集成度引言在使用FPGA时,经常忽略了它的一个优点——能够集成时钟解决方案。

这种集成能力不但降低了系统成本,而且最新的65-nm Altera®Cyclone®III FPGA支持高级时钟管理和锁相环(PLL)技术,因此,还极大地提高了设计灵活性。

设计人员利用Cyclone III时钟管理功能,管理整个FPGA 和电路板的时钟系统。

而且,由于Cyclone III PLL集成在FPGA中,可以利用Altera的Quartus®II 设计环境,轻松进行设置和配置。

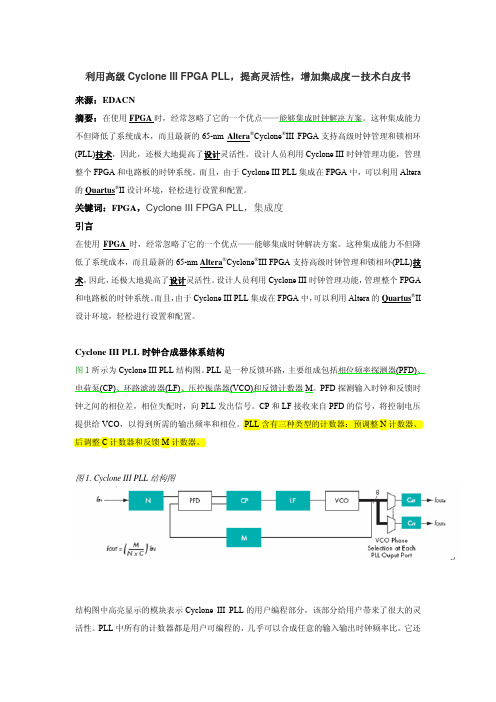

Cyclone III PLL时钟合成器体系结构图1所示为Cyclone III PLL结构图。

PLL是一种反馈环路,主要组成包括相位频率探测器(PFD)、电荷泵(CP)、环路滤波器(LF)、压控振荡器(VCO)和反馈计数器M。

PFD探测输入时钟和反馈时钟之间的相位差,相位失配时,向PLL发出信号。

CP和LF接收来自PFD的信号,将控制电压提供给VCO,以得到所需的输出频率和相位。

PLL含有三种类型的计数器:预调整N计数器、后调整C计数器和反馈M计数器。

图1. Cyclone III PLL结构图结构图中高亮显示的模块表示Cyclone III PLL的用户编程部分,该部分给用户带来了很大的灵活性。

Cyclone_III_EP3C25E144_外型尺寸-封装尺寸

June 2011

Altera Corporation

04R-00221-1.0

2

Altera Device Pacage Information

Package Outline

TOP VIEW

D D1

Pin 144

BOTTOM VIEW

D2

Pin 144

Pin 1

Pin 1 ID

Pin 1

E1

E2

Package Outline Dimension Table

Millimeters Symbol Min. A A1 A2 D D1 D2 E E1 E2 L L1 S b c e 0 0.20 0.17 0.09 6.55 0.45 6.55 1.45 0.05 1.30 Nom. 1.55 0.10 1.45 22.00 BSC 20.00 BSC 6.70 22.00 BSC 20.00 BSC 6.70 0.60 1.00 REF 0.22 0.50 BSC 3.5 7 0.27 0.20 6.85 0.75 6.85 Max. 1.65 0.15 1.60

Altera Corporation

04R-00221-1.0

E

Pin 36

Pin 36

A2 A1

A

See Detail A

Detail A

e

C Gage Plane

b

S L L1

0.25mm

04R-00221-1.0

June 2011

Altera Corporation

Altera Device Package Information

3

Document Revision History

Altera最新FPGA

Stratix III FPGA系列简介

表1. Stratix III 逻辑器件简介

Stratix III L Family Variants 器件 EP3S L50 19,000 47,500 38,000 108 6 1,836 594 216 EP3S L70 27,000 67,500 54,000 150 6 2,214 844 288 EP3SL 110 42,600 106,500 85,200 275 12 4,203 1,331 288 EP3SL 150 56,800 142,000 113,600 355 16 5,499 1,775 384 EP3SL 200 79,560 198,900 159,120 468 24 7,668 2,486 576 EP3SE 260 101,760 254,400 203,520 864 48 14,688 3,180 768 EP3SL 340 135,200 338,000 270,400 1,144 48 17,208 4,225 576

Stratix IV FPGA系列简介

表 2. Stratix IV E 增强型器件简介

Stratix IV E 型号 特性 等价逻辑单元 (LE) 自适应逻辑模块 (ALM) 寄存器 M9K 存储器模块 M144K 存储器模块 嵌入式存储器 (Kbits) MLAB (Kbits) 18 x 18 Multipliers (1) EP4SE110 105,600 42,240 84,480 660 16 8,244 1,320 512 EP4SE230 228,000 91,200 182,400 1,235 22 14,283 2,850 1,288 EP4SE290 291,200 116,480 232,960 936 36 13,608 3,640 832 EP4SE360 353,600 141,440 282,880 1,248 48 18,144 4,420 1,040 EP4SE530 531,200 212,480 424,960 1,280 64 20,736 6,640 1,024 EP4SE680 681,100 272,440 544,880 1,529 64 22,977 8,514 1,360

基于CycloneⅢ构成的RS编码系统

基于CycloneⅢ构成的RS编码系统苗鑫;邓攀;殷奎喜【摘要】本文采用Ahera公司的FPGA器件CycloneIII系列EP3CIO作为核心器件构成了R-S(255,223)编码系统;利用QuartusⅡ9.0作为硬件仿真平台,用硬件描述语言Verilog_HDL实现编程,并且通过JTAG接口与EP3C10连接。

R—S(Reed—Solomon)码是一类纠错能力很强的特殊的非二进制BCH码,能应对随机性和突发性错误,广泛应用于各种通信系统中和保密系统中。

R—S (255,223)x6能够检测32字节长度和纠错16字节长度的连续数据错误信息。

%This paper uses Altera company FPGA Cyclone III series EP3C10 devices as a core component of R-S (255223) coding system;Using Quartus II 9.0 as a hardware emulation platform, using hardware description language Verilog__HDL programming, and through the JTAG interface and EP3C10 conneetion.R-S ( Reed-Solomon ) code is a kind of special non binary BCH code which's error correction capability is very strong, can deal with random and burst error, widely used in all kinds of communication systems and security systems.R-S (255223) code is capable of detecting and correcting the length of 32 bytes 16 byte length of continuous data error information.【期刊名称】《电子设计工程》【年(卷),期】2012(020)004【总页数】4页(P189-192)【关键词】CycloneⅢ;QuartusⅡ9.0;Verilog_HDL;R—S(255;223).码【作者】苗鑫;邓攀;殷奎喜【作者单位】南京师范大学物理科学与技术学院,江苏南京210046;南京师范大学物理科学与技术学院,江苏南京210046;南京师范大学物理科学与技术学院,江苏南京210046【正文语种】中文【中图分类】TN911.22R-S码是用其发明人的名字Reed和Solomon命名的。

cyclone3的配置方式

cyclone3的配置方式cyclone3的配置方式cyclone3器件使用SRAM单元保存配置信息。

因为SRAM掉电易失的特性,fpga芯片上电的时候必须重新配置。

根据期间密度和封装选择,它有如下5中配置方案(红色部分为常用配置方案,并不是所有FPGA芯片都能使用所有配置方案,具体可查看cyclone3的器件手册):1. Active serial (AS)主动串行配置2. Active parallel (AP)主动并行配置3. Passive serial (PS)被动串行配置4. Fast passive parallel (FPP)快速被动并行配置5. Joint Test Action Group (JTAG)AS和AP配置方案需要外部FLASH存储器存储配置信息。

其它3种配置方案需要外部的控制器或者下载电缆。

主动配置方案以及JTAG方案常用于单芯片系统设计。

下面重点介绍AS,AP和JTAG。

以AS配置为例介绍。

Cyclone3器件的配置芯片通常选择EPCS64,EPCS16以及EPCS4或者flash.这些芯片能够提供廉价,方便(引脚少)的解决方案。

因为FPGA芯片容量的限制,它对配置信息的大小也有所限制。

EP3C80系列器件可提供21MBITS的配置信息流容量。

MSEL【3:0】为FPGA器件的输入,用于确定配置方式。

AS模式下,它连接1101.AP模式下,它连接1011.注意要直接接 VCCA or GND,更不能悬空,避免无效配置。

查看手册可得到其它配置值。

在JTAG模式下,忽略MSEL配置,JTAG模式有优先权。

AS模式支持配置信息压缩,AP模式不支持。

压缩信息可以节约空间以及配置时间。

在Device & Pin Options――Configuration中可以选择压缩与否。

选择好器件后,参考下图连接。

POR――上电复位.复位时间由MSEL【3:0】决定。

复位结束后开始发送配置控制信号。

altera cyclone系列器件命名规则

altera cyclone系列器件命名规则Cyclone系列是Altera(现为英特尔公司)推出的一系列现场可编程门阵列(FPGA)器件。

这个系列的名称起源于台风(Cyclone),代表了其高性价比和低功耗的特点。

Cyclone系列器件广泛应用于各种领域,包括消费电子、通信、计算机和工业自动化等。

Cyclone系列器件的命名规则是由多个部分组成的,每个部分都代表了不同的信息。

1. 器件系列:命名的开始部分即是器件系列的名字,Cyclone系列的器件以"Cyclone"为前缀。

2. 产品系列:紧随器件系列名称之后的部分即是产品系列的名字。

Cyclone系列具有许多不同的产品系列,如Cyclone II、Cyclone III、Cyclone IV和Cyclone V等。

每个产品系列都有其特定的性能和功能特点。

3. 系列特定功能:接下来的部分是系列特定功能的描述,用以区分不同的器件。

例如,Cyclone II系列的器件可以包括E、G、GX和GT等型号,代表着不同的逻辑单元数、内存容量以及电路特性。

4. 温度等级:在命名规则中,温度等级通常以后缀的形式标识。

不同的温度等级反映了器件能够工作的温度范围。

常见的温度等级包括商业级(C)和工业级(I)等。

5. 封装类型:器件的封装类型也是命名中的一部分,用以说明器件外部尺寸和引脚排布等信息。

常见的封装类型有塑封式(QFP)和裸片(BGA)等。

6. 特殊功能后缀:在一些情况下,器件的命名可能还会包含某些特殊功能的后缀,以便更好地描述器件的功能和特性。

通过遵循这样的命名规则,Altera Cyclone系列的器件名称具备了清晰明了以及区分不同特性的能力。

对于开发者和用户来说,这样的命名规则为选择合适的器件提供了便利,并且使得在文档和规格表中查找相应的信息更加容易。

总之,Altera Cyclone系列器件的命名规则是由器件系列、产品系列、系列特定功能、温度等级、封装类型以及特殊功能后缀等多个部分组成的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Cyclone III 的配置

全文翻译自Altera公司Cyclone III的器件手册。

所有表格与图标标号与手册原文一致,以便于查对。

出于个人需要,仅翻译了AS与JTAG配置两部分,且仅都配置一片FPGA芯片。

可以通过压缩数据的方法以节约存储空间,并节省程序load时间(page 220);

9通过Remote System Upgrade方式可以减少新产品面市的时间(page 221);

9AS Configuration(Serial Configuration Devices)

¾表10-6显示的是对各种配置电平来说,MSELx管脚的接法

¾单一器件配置

四个接口管脚包含了串口时钟(DCLK),串行数据输出(DATA),AS 数据输入(ASDI),以及低电平有效的片选信号(nCS)。

注:

1)上拉一个电阻,连接到该管脚所在的bank的VCCIO;

2)Cyclone III器件通过DATA[1]-to-ASDI路径控制配置芯片;

3)nCEO管脚浮空,或者当没有连接到另一个器件的nCE管脚时,可以当作通用IO使用;

4)MSEL管脚的设置,用于选择不同的电平标准和不同的POR时间;参考表10-6,选择

接法;

5)这些是复用管脚。

FLASH_nCE管脚在AS配置电路图中当作nCSO功能使用,DATA[1]

管脚当作ASDO功能使用;

6)这些串接的电阻尽可能靠近配置芯片

当连接一个配置芯片到Cyclone III器件时,DATA[0]管脚必须串一个电阻,并应接近配置芯片。

配置器件和Cyclone III芯片间连线的长度应符合表10-8所推荐的值。

当选择AS配置方式的时候,BAMK 1的IO电压必须是3.3,3.0或2.5。

上电以后,CIII器件有一个POR时间的延迟,在此期间,nSTATUS和CONF_DONE 会一直为低,所有的IO也都是三态输出。

芯片配置的三个阶段分别是复位,配置和初始化。

当nCONFIG或者nSTATUS为低,芯片处于复位状态,经过POR时间后,CIII释放nSTATUS,进入配置模式。

(为开始配置,所有配置管脚和JTAG管脚所在的BANK的VCCINT,VCCA和VCCIO必须成功上电)。

CIII器件生成的串口时钟(DCLK)控制整个配置周期并为串口提供时序。

CIII利用每步40MHz的晶振生成DCLK。

在AS配置模式下,配置芯片在DCLK的上升沿锁存输入和控制信号,并在下降沿送出数据;而CIII会在DCLK的下降沿发出控制信号并在DCLK的下降沿锁存配置数据。

CIII接收完所有的配置信息后,释放开环输出的CONF_DONE。

只有当CONF_DONE 变成高电平时,CIII才开始初始化。

如果在配置期间出现了错误,CIII会将nSTATUS信号拉低,表示有一个数据帧错误,CONF_DONE信号保持为低。

如果Auto-restart configuration after error 选项选中的话,CIII 会复位配置信号,通过向FLASH_NCE发一个脉冲,经过复位时间后释放nSTATUS的状态(最大230us)。

注:

1)所有这些管脚连接到所在BANK的VCCIO;

2)nCEO管脚可以悬空,或者当没有被连接到另外一个器件的nCE管脚时当作一个通用管

脚使用;

3)为USB下载线提供3.3V电源

4)MSEL管脚的设置,用于选择不同的电平标准和不同的POR时间;参考表10-6,选择

接法;

5)这些是复用管脚。

FLASH_nCE管脚在AS配置电路图中当作nCSO功能使用,DATA[1]

管脚当作ASDO功能使用;

6)这些二极管和电容必须靠近CIII芯片,必须保证二极管和电容可以容忍4.1V的交流电

压。

外接的二极管和电容用于保护CIII AS配置输入管脚,因为当使用下载线对器件进行编程时会可能overshoot。

Altera推荐使用Schottky二极管,而不是Zener二极管。

7)当CIII工作于multi-device AS配置模式,在CIII主机和从机只基恩连接repeater 缓存。

¾JTAG配置

CIII的JTAG配置优先级超过其它所有配置方式,因此,在进行其它方式配置时,JTAG 配置方式可以立即启动而不用等其它方式配置结束。

当CIII的MSEL管脚设置成AS模式,当JTAG配置发生时,CIII器件不会发出DCLK信号。

用于JTAG配置的4个管脚是TDI,TDO,TMS和TCK。

TCK管脚有内部弱上拉电阻,而TDI和TMS则需要外部上拉一个电阻(通常为25K)。

TDO输出管脚是由BANK1的VCCIO供电。

所有的JTAG输入管脚都是由VCCIO驱动的,且仅仅支持LVTTL I/O标准,在JTAG配置期间,所有用户I/O管脚都是三态。

VCCIO为2.5V,3.0V或3.3V的器件的JTAG配置,参考图10-24。

所有的I/O管脚都维持在最大4.1V交流电压。

由于JTAG管脚没有内部PCI过压保护二极管,因此必须用VCCA 的2.5V给下载电缆供电。

注:

1)所有这些管脚连接到所在BANK的VCCIO;

2)把nCONFIG和MSEL[3..0]管脚连接成一个非JTAG配置的模式。

如果仅仅使用JTAG

模式,则把nCONFIG拉高,并把MSEL[3..0]接到地上,除此以外,得把DCLK和DATA[0]拉高或拉低;

3)插头的6脚是下载电缆输出驱动的参考电压,VIO需要符合VCCA;

4)为成功进行JTAG配置,nCE必须连到地上或拉低;

5)nCEO管脚浮空或者当作一个通用I/O使用;

6)用来自VCCA的2.5-V给下载电缆供电,插头上的4脚给MasterBlaster电缆供电,

MasterBlaster电缆可以接收板子上的5.0V或者3.3V电压。

进行JTAG配置的时候,必须考虑CIII的一些专用配置管脚,见表10-17:

表10-7:JTAG配置时,其它专用配置管脚的连接

Signal Description

nCE nCE必须接到地上,或者通过一电阻拉低,或者由其它控制电路驱动。

如器件还由AS,PS,AP,PP配置链,则进行JTAG配置时,nCE需要连到地上nCEO 该chain上的所有CIII器件的CEO必须浮空,或者连到另一个器件的nCE MSEL[3..0] 不能浮空,应该按照其它配置模式去接这几个管脚

nCONFIG 通过一个电阻拉高,或者由其它控制电路驱动

nSTATUS 通过一个10k的电阻连接到该管脚所在bank的VCCIO,如果有多个芯片,则必须每个都上拉电阻

CONF-DONE 通过一10k的电阻上拉到VCCIO。

JTAG配置完成后,CONF-DONE为高DCLK 不能浮空,根据板子的要求,拉高或拉低。