如何设计电磁兼容的电路板

电路中的电磁兼容性设计

电路中的电磁兼容性设计电磁兼容性(Electromagnetic Compatibility,缩写为EMC)是指在一定环境中,电子设备能够在互不干扰的条件下协同工作的能力。

在现代社会中,电子设备的普及和使用广泛,因此电磁兼容性设计变得愈发重要。

1. 电磁兼容性的重要性当多个电子设备在相同的频率下共同工作时,电磁相互干扰的问题可能会出现。

例如,在医院的手术室中,存在着大量的医疗设备,如果这些设备之间没有达到良好的电磁兼容性,就可能导致干扰,从而影响医生的工作效率和患者的安全。

因此,电磁兼容性设计对于确保设备的正常运行和人身安全起到至关重要的作用。

2. 电磁兼容性设计的原则为了实现电磁兼容性设计,我们可以遵循以下原则:2.1 分隔与屏蔽为了减少电磁相互干扰,我们可以通过物理分隔和电磁屏蔽来降低信号的传播。

物理分隔可以通过合理布局电路板或设备的方式来实现,以减少同一设备内部的相互干扰。

而电磁屏蔽则使用金属外壳或金属层对电磁场进行阻挡,从而防止电磁泄露和外部干扰。

2.2 压制噪音与干扰源在电路中,存在着各种各样的噪音和干扰源,如电源噪声、开关电流等。

通过采用滤波器、隔离器和衰减器等方法,可以有效地抑制噪音和干扰源的影响,从而降低电磁干扰。

2.3 路径优化与电磁耦合在电路设计中,路径走向和电磁耦合也是需要重点考虑的因素。

通过合理的电路布局和优化路径,可以降低电磁泄露和电磁干扰的风险。

此外,对于有源元件(如晶体管、集成电路等),还可以采取电磁屏蔽和内部接地方式,以减少对周围电路的干扰。

3. 电磁兼容性测试与验证在电磁兼容性设计完成后,还需要进行相应的测试和验证,以确保设计是否符合要求。

这些测试通常包括辐射测试和传导测试。

辐射测试主要是针对设备对周围空间的电磁泄露进行测试,传导测试则是检测设备内部电路对外部电磁干扰的敏感性。

测试结果通常使用规定的电磁兼容性标准进行评估,并根据所在行业或地区的规定,对测试结果进行分析和判定。

电路板级的电磁兼容设计

电路板级的电磁兼容设计电磁兼容是现代电子设备设计中重要的一环,在电路板级的设计中尤为关键。

以下是几个重要的设计原则和方法,可用于电路板级的电磁兼容设计。

1.地线设计:地线是电路板设计中一个重要的组成部分,它扮演着连接和分配各种信号和电源的角色。

一个良好的地线设计可以有效地减小电磁辐射和电磁敏感性。

在地线设计中,应注意以下几个方面:-地位连接:确保地线连接短、粗、宽以及直接。

-地位平面:使用连续和全面的地位平面,降低环路电流的流动。

-地位隔离:将模拟和数字地位隔离开,以防止互相干扰。

-地位分割:将地位分成不同的区域,以隔离敏感的模拟信号和噪声源。

2.信号层规划:在多层电路板设计中,信号层的布局和规划对于电磁兼容性也至关重要。

以下是几个信号层规划的原则:-信号区域:将信号分组到不同的区域,确保相互之间的干扰最小。

-电源与地位:为每个器件提供干净的电源和地位,以降低电磁噪声的产生。

-信号路径:设计短而直接的信号路径,减小环路电流和辐射电磁场。

-高频信号:使用特殊板层来隔离高频信号,以阻止其在其他层之间传播。

3.输入输出接口的电磁屏蔽:输入输出接口通常是电子设备与外部环境连接的部分,容易受到外部电磁干扰的影响。

为了保护输入输出接口免受干扰,可采用以下方法:-电源滤波器:在输入电源线路上安装滤波器,以阻止电磁噪声进入设备。

-磁隔离:使用磁隔离器分离输入输出接口和电路板,阻止磁耦合干扰。

-屏蔽罩:采用金属屏蔽罩覆盖输入输出接口和相关电路,以隔离干扰源。

4.地线回流路径的设计:地线回流路径通常是电磁兼容性问题的焦点。

良好的地线回流路径设计可以最大限度地减小环路电流和电磁辐射。

以下是几个关键的设计原则:-低阻抗路径:确定良好的地线回流路径,以最小化环路电流。

-地位平面:使用连续的地位平面成为地线回流路径的一部分。

-层间连接:确保信号和地位通过好的层间连接,减小环路电流。

5.模拟与数字信号隔离:模拟信号和数字信号相互干扰是电磁兼容设计中的一个常见问题。

设计电路板时需注意的电磁兼容事项

设计电路板时需注意的电磁兼容事项设计电路板时,需要注意的电磁兼容事项1. 引言:电磁兼容(Electromagnetic Compatibility, EMC)是指电子设备和系统在电磁环境中能够正常工作,而不造成对周围环境和其他设备的干扰或受到干扰的能力。

在设计电路板时,为了确保设备的正常运行并避免可能的干扰,需要注意一些电磁兼容的事项。

2. 地线设计:a. 良好的地线设计非常重要,可以帮助减少电磁干扰并提高电路板的抗干扰能力。

b. 尽量缩短地线长度,减小回路面积,以降低对其他线路的感应作用。

c. 使用单点接地(Single Point Grounding)的方法,将所有电路的地线连接到一个共同的地点,减少接地回路带来的干扰。

3. 电源线设计:a. 电源线应尽量绕远离其他线路和敏感器件,避免磁场、电场的干扰。

b. 使用滤波器来消除电源线上的高频噪声和干扰信号。

c. 为关键电路提供稳定的电源,避免电源噪声对其他电路的影响。

4. 线路布局和走线设计:a. 尽量规划好线路和元器件的布局,避免过度拥挤和堆叠,减少交叉干扰。

b. 对于高频信号线路,应尽量保持短、直和紧凑的布线方式,减少信号衰减和串扰。

c. 采用单层布线或分层布线,将信号线和电源线、地线分开布置,提高信号完整性和阻碍干扰。

5. 屏蔽和接地:a. 使用屏蔽罩(Shielding)可以有效地阻挡外界电磁干扰,提高电路板的抗干扰能力。

b. 合理安排接地线的布线,并确保良好的接地连接,减少接地回路的电阻和电感。

c. 针对敏感元器件或高频线路,可以采用地线隔离技术,将其与其他线路的接地隔离开来,减少串扰和干扰。

6. 元器件的选择和布局:a. 选择符合电磁兼容标准的元器件,例如具有抗干扰能力的芯片和滤波器。

b. 合理布置敏感元器件和辐射源,避免它们之间的相互干扰。

c. 对于高频线路,选择适当的元器件,例如差分线路来减少串扰,以及线束布局来降低电感和互感。

电磁兼容解决方案

电磁兼容解决方案一、引言电磁兼容(Electromagnetic Compatibility,简称EMC)是指电子设备在特定电磁环境下能够正常工作,同时不对周围环境和其他设备造成干扰的能力。

随着电子设备的广泛应用,电磁兼容问题日益凸显。

本文将详细介绍电磁兼容解决方案的标准格式。

二、问题描述在电子设备的设计和生产过程中,往往会遇到电磁兼容问题。

这些问题包括电磁辐射和电磁感应两个方面。

电磁辐射是指电子设备在工作时产生的电磁波向周围空间传播,可能对其他设备或者系统造成干扰。

电磁感应是指电子设备受到外部电磁场的影响,导致设备内部电路发生故障或者性能下降。

三、解决方案为了解决电磁兼容问题,我们需要采取一系列的措施。

以下是一些常见的解决方案:1. 设计合理的电路板布局合理的电路板布局是确保电磁兼容的重要因素之一。

通过合理安排电路板上的元件、信号线和电源线的位置,可以减少电磁辐射和电磁感应的发生。

同时,应尽量避免信号线和电源线的交叉和平行布局,以减少电磁干扰。

2. 使用屏蔽材料和屏蔽技术屏蔽材料可以有效地抑制电磁辐射和电磁感应。

常见的屏蔽材料包括金属板、金属网、金属涂层等。

在设计电子设备时,可以在关键部位使用屏蔽材料来减少电磁干扰。

此外,还可以采用屏蔽技术,如屏蔽罩、屏蔽隔板等,来进一步提高电磁兼容性。

3. 优化电源系统设计电源系统是电子设备的重要组成部份,也是电磁兼容问题的关键。

通过合理设计电源系统,包括滤波器的选择和布局、地线的设计等,可以有效地降低电磁辐射和电磁感应。

4. 进行电磁兼容测试和验证在电子设备的设计和生产过程中,应进行电磁兼容测试和验证,以确保设备符合相关的电磁兼容标准。

常见的测试项目包括电磁辐射测试、电磁感应测试等。

通过测试和验证,可以及时发现和解决电磁兼容问题,提高设备的可靠性和稳定性。

四、实施步骤为了实施电磁兼容解决方案,我们可以按照以下步骤进行:1. 分析电磁兼容问题首先,需要对电子设备的电磁兼容问题进行分析。

电路电磁兼容性设计如何设计抗干扰和抗辐射电路

电路电磁兼容性设计如何设计抗干扰和抗辐射电路电磁兼容性(Electromagnetic Compatibility, EMC)是指电子设备在相互干扰和和外界电磁环境下能够正常工作的能力。

在电子产品的设计中,抗干扰和抗辐射电路的设计是确保电子设备在各种电磁环境下能够稳定运行的重要因素。

本文将讨论电路电磁兼容性设计中如何设计抗干扰和抗辐射电路。

一、抗干扰电路设计抗干扰电路设计是为了减少电子设备对外界电磁噪声的敏感度,防止其发生故障或误操作。

以下是几种常见的抗干扰电路设计方法:1. 电源线滤波器:通过在电源输入端添加滤波电路,能够滤除掉电源线上的高频噪声,减小对电子设备的影响。

2. 地线设计:良好的接地设计可以有效地抑制干扰信号的传播,例如通过增加接地电感和接地电容,形成低阻抗的接地路径。

3. 屏蔽设计:在电路板的设计中,使用屏蔽罩或金属层来遮蔽电子设备内部的干扰源,从而降低对周围环境的干扰。

4. 布线设计:合理的布线可以减少信号间的串扰,例如将高频信号线和低频信号线分开布置,避免相互干扰。

5. 过压保护设计:在电路中添加适当的过压保护电路,可以避免由于外界电磁干扰引起的过压情况,保护电子设备的正常工作。

二、抗辐射电路设计抗辐射电路设计是为了减少电子设备对外界电磁辐射的敏感度,防止其自身辐射对其他设备和系统造成干扰。

以下是几种常见的抗辐射电路设计方法:1. 圆孔规则:根据电磁波波长和孔洞尺寸之间的关系,设计合理大小的圆孔,使其具有较好的屏蔽性能。

2. 接地设计:良好的接地设计可以有效地将电磁辐射信号导入地面,减小辐射功率。

3. 电磁辐射滤波器:通过添加辐射滤波器,限制高频电流在电路中的传播,减少辐射发射。

4. 屏蔽设计:在电路板设计中增加屏蔽层或屏蔽导线,使电磁辐射局限在设备内部,减少对外界的辐射。

5. 地面平面分割:通过将地面平面划分为小的分区,降低不同分区之间电荷的流动速度,减小辐射功率。

三、电路模拟与仿真为了更好地评估电路的电磁兼容性性能,可以使用电磁仿真软件对电路进行模拟和仿真。

电路电磁兼容设计

电路电磁兼容设计是为了使电路在预期的电磁环境中能够正常工作,同时不会对其他系统或设备造成电磁干扰。

以下是一些常见的电路电磁兼容设计方法:

1. 合理分区:将电路按照功能进行分区,以减少不同电路之间的相互干扰。

2. 滤波:在电路的输入和输出端添加滤波器,以减少电磁干扰的传播。

3. 屏蔽:对电路进行屏蔽,以减少电磁辐射和外部电磁干扰的影响。

4. 接地:合理设计接地系统,以减少地线电流对电路的影响。

5. 布局:合理布局电路元器件,以减小电磁干扰的传播路径。

6. 降低工作频率:在可能的情况下,尽量降低电路的工作频率,以减小电磁辐射和干扰。

7. 使用抗干扰元件:使用抗干扰能力强的元件,如电磁继电器、光电耦合器等。

8. 软件抗干扰:在软件层面采取措施,如数字滤波、软件陷阱等,以减小电磁干扰的影响。

在进行电路电磁兼容设计时,需要考虑系统的整体电磁环境,采取多种措施进行综合防护,以达到最佳的电磁兼容效果。

同时,还需要进行实际的测试和验证,以确保设计的有效性。

电磁兼容在电路设计中的原则和方法

电磁兼容在电路设计中的原则和方法电磁兼容设计要求在元器件级、部件级、设备级、系统级都达到互不干扰,正常工作。

元器件、部件级上的电磁干扰主要来自不同的元件之间的电磁耦合,电路设计的任务之一就是要消除元件和部件级上发生的电磁干扰影响。

设备级,系统级所发生的电磁干扰与电子设备所处的电磁环境,各电子设备之间的相互影响,以及电子设备内部的元件和部件之间的电磁耦合有关。

1 电磁兼容的分层设计原则这主要是按照电磁兼容设计的先后顺序来考虑的,从先到后可分为以下几层:(1) 元器件的选择和PCB设计,这是关键的;(2) 接地设计,这是主要的手段。

以上两层如果设计的好,可完成电磁兼容的80%以上的工作。

(3) 屏蔽设计;(4) 滤波设计和瞬态骚扰抑制。

以上两层是辅助手段,多为事后补救措施,也是我们最不提倡的。

(5) 可根据实际电路需要,结合以上几层来综合设计。

2 保证电磁兼容的方法主要根据构成干扰的三要素从下几方面来保证电磁兼容。

2.1 在不同等级上保证电磁兼容1) 从元器件级上来说,当是无源元件时,考虑(1)工作频带以外的元件参数与工作频带上的有很大的区别;(2)插件元件的末端引线有电感存在,当高频时这个电感易发生电磁兼容问题;(3)元件有寄生电容,寄生电感,在电路上表现为分布参数,在分析电路时也要考虑由它带来的等效电路。

当是有源元件时,工作中产生的电磁辐射也会以传导电流的方式成为干扰源,当是非线性元件时还可能发生频谱成分的变化,这种变化也会引起干扰。

2) 从设备级上来说,主要是保证减少对敏感设备的耦合,可考虑(1)增加脉冲前沿时间以减少干扰的频宽;(2)消除电路中震荡器产生的谐波及信号的谐波;(3)限制干扰辐射或消除干扰的传播途径。

3) 从系统级上来说,主要是靠组织或系统工程的方法来保证,因为有可能在单个设备上的电磁兼容得到了改善,但同时却影响了其它设备的工作条件,使得其它设备的性能指标变坏,此时需要从系统上折中考虑,另外,重要的一点是电磁兼容设计必须得到系统总体设计的高度重视。

电磁兼容设计方案

电磁兼容设计方案电磁兼容(EMC)设计方案是为了保证电气设备能够在电磁环境中正常工作而制定的一系列措施。

下面将介绍一个基本的电磁兼容设计方案,以确保电气设备的可靠性和性能。

首先,需要进行全面的电磁环境调研。

通过测量,分析和评估电气设备所处的电磁环境,包括电磁场强度、频谱分布和其他干扰源等。

了解电磁环境对设备的影响,为后续的设计和改进提供依据。

其次,在电路设计中采用合适的电磁屏蔽措施。

包括使用抗干扰电路,提高电路的抗干扰能力。

在电路板布局时,尽量避免高频信号线和低频信号线的交叉,并采用分层布线和差分信号传输方式,减少电磁辐射和敏感性。

同时,在电路板布局和元器件选择中,要考虑到电磁兼容的要求。

合理布局电源和信号线路,减少回路面积和长度。

选择具有良好抗干扰能力的元器件,对于敏感元件,要采取良好的隔离措施。

另外,对电气设备进行合理的屏蔽设计。

可以采用金属壳体、屏蔽罩等方式对设备进行外部屏蔽,阻止外部电磁干扰的进入。

同时,在设计电路板时,合理安排信号和电源线的布局,减少电流回路面积和长度,减少电磁辐射。

此外,进行全面的电磁兼容测试和评估。

通过实验室测试,对电气设备的电磁兼容性进行评估,包括辐射干扰和传导干扰。

根据测试结果,对设备进行必要的改进和优化,确保其在各种电磁环境下能够正常工作。

最后,制定完善的电磁兼容管理策略。

包括制定电磁兼容设计标准和规范,对设备生产过程进行控制,确保每个生产的设备都符合相应的标准要求。

同时,培训和教育工作人员,提高其对电磁兼容问题的认识和处理能力。

综上所述,一个完善的电磁兼容设计方案涉及到电磁环境调研、电路设计和布局、屏蔽设计、兼容性测试和评估以及管理策略等方面。

通过采取合适的措施,可以确保电气设备在各种电磁环境下的可靠性和性能。

电路板级的电磁兼容设计

电路板级的电磁兼容设计电磁兼容性(Electromagnetic Compatibility,EMC)是指电子设备在电磁环境中无干扰地正常工作,并且不对周围的其他设备产生影响。

在电子产品设计中,电路板级的设计是重要的环节之一,其中的电磁兼容设计起着关键的作用。

首先,电磁兼容设计的目标是通过控制电磁辐射和敏感度,使得电路板在工作过程中不会发生电磁干扰。

因此,在电路板的布局设计中,需要合理安排电源线、地线和信号线的走线路径,以尽量减小信号线的回送路径长度和面积,从而减少电磁辐射。

此外,还应根据信号线的频率特性和传输速率,采取合适的终端匹配电阻、衰减器等措施,避免信号的反射和干扰。

其次,地线的设计也是电磁兼容设计中的重要环节。

在电路板的设计中,地线的作用是提供低阻抗的回路,将所有模拟和数字信号的共模噪声引导到地。

因此,在设计过程中,需要将地线设计为宽厚的导线,以降低其电阻和电感,从而减小回流干扰。

另外,电源线的设计也需要考虑电磁兼容性。

在电源线的走线设计中,需要尽量避免与信号线和地线的交叉路径,以减少信号的干扰。

同时,还需要使用低阻抗的电源滤波器和抑制器,以滤除来自电源线的高频噪声,并保证电力的稳定性。

此外,电磁屏蔽也是电磁兼容设计中的一种重要手段。

通过在关键区域周围添加遮蔽罩、金属隔离层等结构,可以有效地减少电路板对周围环境的电磁辐射,同时也可以阻塞外部电磁场的干扰。

最后,电磁兼容设计还需要进行严格的电磁兼容测试。

通过使用专业的电磁兼容测试仪器,对电路板进行辐射和传导测试,以确保其符合相关的电磁兼容性标准。

综上所述,电路板级的电磁兼容设计是保证电子设备正常工作、减少电磁干扰和提高抗干扰能力的关键环节。

通过合理的布局设计、地线的规划、电源线的工艺以及电磁屏蔽的应用,可以有效地提高电路板的电磁兼容性,确保电子设备在复杂的电磁环境中稳定、可靠地工作。

接上文,继续探讨电路板级的电磁兼容设计。

在电磁兼容设计中,还需要考虑到高频信号的传输和干扰问题。

电路板级的电磁兼容设计

器件 上 。这种 做法 使 电源布线 分布 阻抗 非 常 小 , 电路压 降小 ,器件上 能得 到稳 定 的直 流 电压 。同时平 面间 靠得 很近 ,能较 好地 抑制 电场 耦合 。且 电源 平面往 返 电流大 小相 等 , 磁场 干扰 能抵 消 。 () 地平 面法 2共

的负 载端接 上 一个 瞬态变 化 的信号 源 。特 别 是在 高频 ,有 的器 件工 作在数 字开 关状 态 , 这一 现象 更为 突 出。这样 电源 布线 既含 有直 流 电压 ,又 含 有 瞬态 变化 的 电压 ( 为 寄生 称 电压 ) ,瞬 变 电压 会 产生 高 次谐 波 ,其 都 是 产 生E I 主要来 源 。 M的 2 电源 布线 的防干 扰措 施 . () 1 电源 平 面法 利 用P B C 的一层 作 为 电源 平 面层 ,至 少 有 一层 作为地 平面 ,每 一层 只 能提 供一 种 电

、

尽 可能 缩短 高频 元件 之 间的连 线 ,设法 影 响 ,负载 电压或 电流 的瞬态 变化 会 引起 电 减 少它 们 的 分布 参 数 和 相互 间的E I 易受 源 电压或 电流 发生 瞬态 变化 ,这如 同在 电源 M。

制 造 商 提 供 具 有较 低辐 射 的 胶 合 逻 辑 产 品 ( 合 逻辑 产 品指 的是连 接 不兼 容 的复杂 电 胶 路 的简单 逻 辑 电路 ) 。 2传 输线 匹配I0 C 出 引脚 必须匹 配 . / :I输 高速 信号 的传 输 线 。例如 当驱 动一 个2 5 Q的 并联终端 负载时 ,就 可 以使用 总线驱动器 。 3低 输入 电容 :低输 入 电容有 助于 降低 . 逻 辑 器件 的状 态变 化 时的 电流 峰值 , 因此可 以减 小磁场 辐 射和 地返 回 电流 。 4 铝 电解 电容 可 能发 生几微 秒 的暂 时性 . 介质 击 穿 , 因而在 纹波 很大 或有 瞬变 电压 的 电路里 ,应 该 使用 固体 电容 器 。 5 使 用 寄 生 电感 和 电 容 量 较 小 的 电阻 . 器 。片 状 电阻器 可用 于 超高 频段 。 6 大 电感 寄生 电容 大 ,为 了提高 低频 部 . 分 的插入 损 耗 ,不要 使用 单 节滤波 器 ,而应 启动 区 域无 功投 入策 略 。

印制电路板的电磁兼容性设计

摘 要:在电子设备的设 计中,PCB设计作为电子设备设计中的关键性基础设计步骤 ,尤其在高速电子电路 设备 的设计 中,PCB的电磁兼容性 设计可谓 是关 键 巾 的关 键 ,它 的 电磁 兼 容 性 的 优 劣 直 接 影 响着 电子 设 备 的 性 能 。本 文 在 深 入 探 讨 PCB产 生 电磁 于 扰 的 原 因 和 掌 握 电磁 兼 容 原 理 的基 础 上 ,针 对产 生 电磁 干 扰 的类 型采 取 相 应 的措 施 ,给 出 了 PCB电磁 兼 容 性 没计 的 几 种典 型方 法 ,重 点 阐述 了 PCB高 速 布 局 、布线 等 的 原 则 ,完 成 了信 号 完 整 性 的设 计 。具有普遍 的实用参考价值 。 关键词 :PCB;电磁干扰 ;电磁兼 容

I 艳春 等 :印 翻 电路 板 的 电磁 兼 容性 设计

印 制 电路 板 es ̄n of P ̄nWd Circuit Board

王 艳 春 祖 静 崔 春 生

(中北 大 学 电子 测 试 技 术 国家 重 点 实 验 室 仪 器 科 学 与 动 态 测 试 教 育部 重 点 实验 室 ,山 西 太 原 030051)

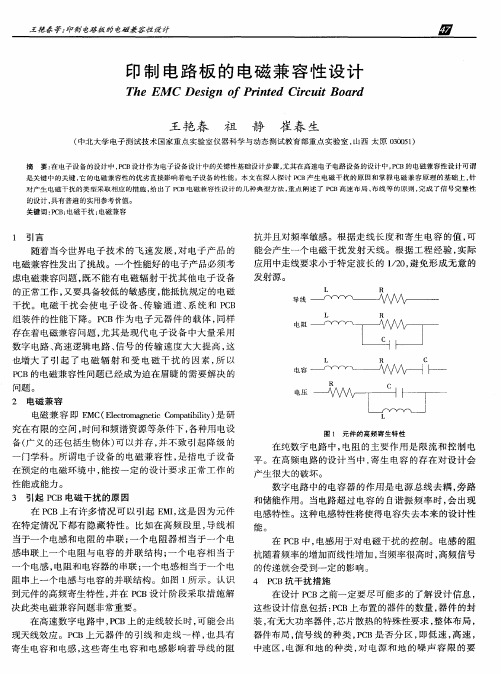

在 PCB上 有许 多 情况 可 以 引起 EMI,这 是 因 为元 件 在特定 情况 下都 有 隐 藏 特性 。 比如 在 高 频 段里 ,导线 相 当于一 个 电感 和电 阻 的 串联 ;一 个 电 阻器 相 当 于 一个 电 感 串联 上一 个 电阻 与 电容 的并 联 结 构 ;一 个 电 容相 当于 一 个 电感 ,电阻 和 电容 器 的 串联 ;一个 电感 相 当于一个 电 阻串上 一个 电感 与 电容 的并联 结构 。如 图 1所示 。认 识 到元 件 的高频 寄生 特性 ,并 在 PCB设 计 阶段 采 取措 施 解 决 此类 电磁 兼容 问题 非常 重要 。

电磁兼容设计方法

电磁兼容设计方法

电磁兼容(Electromagnetic Compatibility,EMC)设计是一种保证电子设备在同一环境中共存互不干扰的设计方法。

下面介绍一些常用的电磁兼容设计方法:

1. 总体设计:在产品设计的早期阶段,就应考虑电磁兼容性,确定设备的功能、电路板布局、信号线路走向等。

通过科学的总体设计,可以减少电磁干扰源,防止发生电磁干扰问题。

2. 接地设计:良好的接地系统可以提供低阻抗的电流回路,减少电流环路的面积和长度,减小电磁干扰。

在接地设计中要注意避免接地回路的串扰,采用单点接地,尽量避免共模干扰。

3. 滤波器设计:通过采用滤波器来减小电源线上的干扰,包括使用电源滤波器、信号线滤波器等。

滤波器可以阻止高频噪声进入到设备中,使设备正常运行。

4. 屏蔽设计:电磁屏蔽是一种减小电磁辐射和接收的有效方法,可以通过使用金属屏蔽盒、屏蔽罩、屏蔽材料等来减小电磁辐射和敏感接收器的电磁干扰。

5. 电路板布局:合理的电路板布局可以减小电磁干扰,如分隔高频和低频信号线路,减小回路的面积和长度,避免干扰源和敏感器件的靠近等。

6. 测试与验证:在设计完成后,进行电磁兼容性测试和验证,以确保产品满足

相关的电磁兼容性规范和标准。

注意:以上仅为一些常用的电磁兼容设计方法,具体的方法应根据具体产品的特点和需求来确定。

电磁兼容的电路板设计

电磁兼容的电路板设计首先,电路板设计的EMC要点包括:1.接地设计:良好的接地设计是确保电路板EMC性能的关键。

合理布局和设计接地回路,避免地线共享,减小接地回路的面积和环形电流路径,可以有效减少干扰的产生和传播。

2.信号层分离:把电路板的不同信号层进行有效的分离,主要是通过地平面和电源平面之间的划分实现。

在多层板设计中,地平面和电源平面可以是内层铜层,通过过孔和盲埋孔与外部电源连接。

3.信号线布线:合理的信号线布线设计可以减少电磁辐射和电磁干扰。

在布线过程中,应尽量使用规则的走线方式,减少信号线的长度和曲折度,减小回路面积。

同时,可以采用阻抗匹配和差分信号布线等手段来降低互连线的电磁辐射。

4.消除回路共享:不同信号线共享回路会导致互导耦合和辐射干扰,因此应该避免回路共享。

例如,将模拟信号回路和数字信号回路分开布局,减小它们之间的电磁干扰。

5.屏蔽设计:在必要的情况下,可以采用屏蔽措施来抑制电磁辐射和测量。

例如,在高频电路中,可以使用屏蔽罩或屏蔽壳体来避免电磁泄漏。

在电磁兼容的电路板设计中,还存在一些常见的EMC问题,需要特别注意:1.辐射干扰:电路板上的电流和信号会通过电磁波的辐射而对周围设备产生干扰。

主要解决方法包括良好的接地设计、合理的信号布线和降低回路共享等。

2.互导耦合:不同信号线之间的互相干扰会导致电路的性能下降。

可以采用阻抗匹配、差分布线、屏蔽等措施来减小互导耦合。

3.地计问题:地电位的差异和地电流的路径问题会导致电路板上的共模干扰和故障。

合理的接地设计和屏蔽措施可以有效解决这类问题。

4.灵敏性问题:对于一些高灵敏度设备,电路板上的微弱干扰可能会对其性能产生较大影响。

可以提高电路板的抗干扰能力,例如通过分割电源平面、使用阻燃材料和屏蔽技术等。

最后,为了确保电磁兼容的电路板设计能够达到预期的效果,需要进行必要的测试和验证。

常用的EMC测试方法包括电磁辐射测量、电磁感应测量、传导干扰测量等。

常用电路的EMC设计

常用电路的EMC设计1.引言电磁兼容(EMC)是指各种电磁设备在同一环境下能够和谐共存,不受相互干扰和损坏。

EMC设计对于常用电路至关重要,特别是对于那些需要在复杂电磁环境中工作的设备来说。

本文将介绍常用电路的EMC设计原则和方法。

2.EMC设计原则2.1电路板布局电路板布局是EMC设计的关键。

布局时需要考虑以下原则:-分离模拟和数字电路:模拟和数字电路应互相独立布局,以避免互相干扰。

-最短路径原则:尽量缩短信号路径,减小传输线路的长度,以减少EMC问题。

-地线设计:地线应具备良好的连通性和低阻抗,以减少共模噪声。

-天线效应:布局时要避免形成天线效应,尽量减小电磁辐射。

-电源电容:在电源引线和电源针脚之间放置合适的电容,以减少电源纹波。

2.2模拟和数字信号处理模拟和数字信号处理需遵循以下原则:-模拟和数字信号分离:模拟信号和数字信号应互相独立地处理,以避免干扰。

-模拟滤波器:应在输入和输出端使用适当的模拟滤波器,以减少射频干扰。

-数字滤波器:在数字信号处理中使用适当的滤波器,以减少射频干扰。

2.3屏蔽和接地屏蔽和接地是EMC设计中非常重要的一部分:-金属屏蔽:电路板或设备外部可以使用金属屏蔽来减少电磁辐射和敏感度。

-模拟和数字屏蔽:模拟和数字电路应互相独立屏蔽,以减少互相干扰。

-接地:良好的接地设计可以减少共模噪声,提高系统的抗干扰能力。

3.EMC设计方法3.1减小电磁干扰减小电磁干扰的方法主要包括:-建立EMC指导方针:在设计开始之前,制定EMC设计指导方针,以确保设计的正确性。

-使用低噪声元器件:选择低噪声、高频性能好的元器件,将有助于减小电磁干扰。

-使用抗干扰设计:在电路布局和PCB设计中使用抗干扰技术,如屏蔽和滤波器。

-合理的地线设计:合理设计和布局地线,减小共模噪声。

3.2提高抗干扰能力提高抗干扰能力的方法包括:-模拟电路与数字电路分离:模拟电路和数字电路要通过合适的屏蔽和滤波器进行分离,防止相互干扰。

PCB板中的EMC设计指南和整改方法

PCB板中的EMC设计指南和整改方法EMC(电磁兼容性)设计是在PCB(印刷电路板)设计中至关重要的一环。

它确保电子设备在电磁环境中正常运行,同时不产生对其他设备或系统的电磁干扰。

为了实现良好的EMC设计,下面将介绍一些EMC设计指南和可能的整改方法。

EMC设计指南:1.良好的地线设计:地线是EMC设计的基础。

一个良好设计的地线系统可以有效降低电磁干扰。

地线应该尽量厚实,形成一个低阻抗的路径,以便将电流引导回源。

此外,地线的布局应符合电磁场传播的方向,避免出现回路共振。

2.分隔信号和电源线:为了避免信号引起电源线的干扰,应尽量将它们分隔布线。

如果信号和电源线必须穿越,那么应尽可能以垂直或交叉的方式进行布线。

3.组件布局:EMC设计中组件的布局也是重要的。

应将发射较强电磁干扰的组件(如高频放大器、开关电源等)远离敏感组件。

此外,应避免长线或环路,以减少电磁辐射。

4.屏蔽处理:对于发射强电磁干扰的组件或系统,可以采用屏蔽措施,如使用金属外壳或屏蔽盖。

屏蔽材料应选择导电性好的材料,并确保屏蔽与地线连接良好。

5.使用滤波器:滤波器可用于限制高频信号的传输,从而减少辐射和传导干扰。

在PCB设计中,可以使用滤波器对输入和输出信号进行滤波,尤其是在高速信号传输或高频噪声环境中。

整改方法:1.优化地线布局:如果发现地线布局存在问题,应重新考虑地线的布局方式。

可以通过增加地线的宽度和长度,减少电磁干扰。

2.重新布线:如果信号和电源线布线混在一起,可以尝试重新布线,将它们分隔开来。

这有助于减少信号对电源线的干扰。

3.添加衰减材料:如果存在辐射干扰,可以在关键区域添加衰减材料,如吸波材料或铁氧体材料。

这些材料可以吸收电磁辐射,并减少传导干扰。

4.优化组件布局:如果发现组件之间存在辐射干扰,可以尝试调整它们的位置。

将辐射干扰较大的组件远离敏感组件,减少电磁干扰的影响。

5.重新选择元件:如果一些元件的辐射干扰太大,可以尝试重新选择辐射干扰较小的元件。

pcb电磁兼容要求

pcb电磁兼容要求PCB(Printed Circuit Board,印刷电路板)的电磁兼容性(EMC,Electromagnetic Compatibility)要求是确保电子设备在不同电磁环境中稳定运行并避免对其他设备产生干扰的重要方面。

以下是PCB电磁兼容性方面的一些常见要求和注意事项:1.电磁干扰抑制:-PCB应设计为在设备内部有效抑制电磁干扰,防止设备内部的信号相互干扰。

-使用屏蔽罩、滤波器和隔离元件等措施,减小电磁辐射和传导。

2.辐射和传导干扰控制:-控制PCB上导线的长度、走线方式和布局,以减小电磁辐射。

-使用地平面和电源平面来控制传导干扰。

-避免并行导线和高速数字信号线与敏感模拟信号线交叉。

3.防护与屏蔽:-对敏感信号线进行屏蔽,使用屏蔽罩和屏蔽层等。

-采用合适的地线设计,确保地的连通性和均匀性。

4.耦合和共模噪声抑制:-通过合适的电源线滤波器、差模和共模电感器等元件来抑制耦合和共模噪声。

-确保模拟和数字地域的适当隔离。

5.接地设计:-采用低阻抗的地线设计,确保设备内部地的均匀性。

-避免接地回流路径上的闭环。

6.抑制电磁脉冲:-使用合适的电源电容和电源电感器,抑制电磁脉冲。

-采用电源线滤波器,控制电源谐波。

7.标准符合:-遵循相关的EMC标准和规范,例如,EN55022、EN55024等。

-对PCB进行EMC测试,确保其符合适用的标准。

以上是一般性的PCB电磁兼容性要求,具体的要求可能会根据应用领域、产品类型和所处的电磁环境等因素而有所不同。

在设计PCB时,密切关注这些要求可以提高产品的可靠性和稳定性。

电子电路布局的EMC设计准则和示例

电子电路布局的EMC设计准则和示例EMC(Electromagnetic Compatibility,电磁兼容性)是指电子设备在电磁环境中无相互干扰且能正常工作的能力。

在电路设计过程中,EMC设计是非常重要的一环,它能够保证电子设备正常运行,并减少电磁干扰对其他设备的影响。

本文将介绍电子电路布局的EMC设计准则和示例,并详细列举步骤。

一、EMC设计准则:1. 尽量减少回路长度:回路长度越长,电磁波传播的路径就越长,干扰信号的问题会更加严重。

因此,在设计电路布局时要尽量缩短回路长度。

2. 适当使用铺铜:通过合理使用铺铜层来减少回路的阻抗,降低电磁辐射的问题。

同时,铺铜层还可用于建立大地平面,增加电磁屏蔽效果。

3. 保持信号线和电源线的分离:为了避免信号线和电源线之间互相干扰,应尽量将它们分离开来布局。

可以使用不同的铺铜层或间隔来隔离信号线和电源线。

4. 避免信号线和辐射物体的交叉:辐射物体包括传输线、散射线和天线等。

信号线和辐射物体之间的交叉会引起电磁干扰,因此应避免它们的交叉。

5. 采用合适的布局规划:合理规划电路板上各部分的位置,确保信号的传输路径尽可能短,同时也要考虑到布线、阻抗匹配等问题。

6. 控制布线走线:布线走线要遵循短、粗、宽、直的原则,尽可能减小阻抗,降低交叉干扰,提高信号质量。

7. 合理选择元器件:选择合适的元器件对EMC设计非常重要。

应选择与EMC 要求相符的低噪声、低电磁辐射的元器件,并尽量避免使用有明显辐射磁场的元器件。

8. 加强接地设计:良好的接地设计可以提高电磁屏蔽效果,减少电磁辐射。

应在电路设计中充分考虑接地的布局和连接方法,并避免接地线的断开、升高阻抗等问题。

9. 使用滤波器和抑制器:滤波器和抑制器可以有效抑制电磁辐射和吸收噪声,提高电路的抗干扰能力。

在设计电路布局时,可以考虑加入合适的滤波器和抑制器,进一步提高电磁兼容性。

10. 增加屏蔽:对于特别敏感的部件或高频信号,可采用金属屏蔽罩或截获罩等形式进行屏蔽,减少电磁辐射和接收干扰。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第一章如何設計符合電磁相容要求的印刷電板簡介EMC鴻 友 科 技安規磁檢部紹崧 Gary Lu #4223R.E C.E R.S C.S EMI EMS★Radiated :此種能的電磁場經由媒介面傳輸.RF能是一般在自由空間內傳播. ☆Conducted :此種能的電磁場經由導体媒介而傳播的.一般是經由電線或內部 接電纜. ★R.S :模擬射射頻電磁場對電子產品所造成的干擾. :模擬傳導性射頻電磁場對電子產品所造成的干擾. ☆C.S ★ESD :模擬靜電干擾對電子產品所造成的干擾. :模擬擊突波對電子產品所造成的干擾. ☆SURGE ★EFT :模擬電器快速暫態/叢訊對電子產品所造成的干擾. :模擬電源頻磁場對電子產品所造成的干擾. ☆PFMF ★DIP :模擬電源電壓瞬間下或中斷頻對電子產品所造成的干擾. ☆HARMONIC:測電子產品對電源所造成電諧波的干擾值. (conducted測電壓諧波,HARMONIC測電諧波.) 壓制 :經由設計以在源頭端低或消除RF能,以使其用依賴如屬機殼等方法. 封閉、包圍:防止RF能逸出一個封閉物體 ,一般是用屬屏蔽或是用塑膠外殼加導電漆, 將RF能封閉在機殼面.EMI組成有以下三個要素Noise sourceCoupling pathReceiver在EMI組成的要素當中.主要以Noise source為最重要.因為如果沒有noise source的 產生的話就需要有Coupling path傳播徑.相對的也就需要有Receiver接收. 但是如果沒有其中任何一個徑的話,也就構成EMI. 在修改的時候我們可以控制noise source釋放出的能,以達到EMI法規的規範.第二章使用Microstrip或stripline的方式壓制PCB層面的射頻射構成一個系統. Microstrip:指PCB的外層Trace,經一介電質鄰接一整片平片(solid plane).這種方式 主要提供PCB上的RF壓制.★缺點是PCB外部信號層會射RF能進入環境.除非在 此層上下加入屬屏障.Layer 的堆疊分配Layer# 2 Layers 1 S1 2 S2 3 4 5 6 7 8 9 10 Comments 低速設計4 Layers (2 routing) 6 Layers (4 routing) 6 Layers (4 routing)S1 S1 S1 S1 S1 S1 S1 S2 S2 S2 S2 S2 S2S2 S3 S3 S4 S4 S3 S3 S4 S3 S3 S4 S5 S6 S4 S5 S6保持高信號阻抗及低電源阻抗 低速設計。

差的電源,高信號阻抗 critical信號放在S2 低速信號放在S2-S3。

高速信號放在S2-S3。

較差之電源阻 抗 最佳之EMC 最佳之EMC。

S4對電源雜訊容忍 高Stripline:介於個solid planes(Voltage 或 Ground)之間,.平面間會有電容性耦 合,導致低高速信號的邊緣速(edge rate),主要效應再對內部trace的RF能的完 整屏障對射頻射也有較佳的抑制能.6 Layers (3 routing) 8 Layers (6 routing) 8 Layers (4 routing) 10 Layers (6 routing)S= Signal routing layer信號佈線層 P= Power G= Ground1八層板1 COMP SIDE 2 GROUND 3 Signal 1 4 GROUND 5 POWER 6 Signal 2 7 GROUND 電源及接地面間極佳的磁通抵銷 極好的佈線層(X方向) X-Y Paired Trace 極好的佈線層(X方向) X-Y Paired Trace 極好的佈線層(Y方向)20-H Rule由於磁通的接,RF電存在於Power plane的邊緣.此種層間耦合作用稱為fringing 通常僅於高速PCB.要減低此效應,所有電源平面應該比相鄰的地平面小(20-H Rule) 使用20-H會提高PCB的本質自諧振頻.電源分布界效應發生在10-H左右.20-H代表 約70%的通邊界. 當使用20-H時.在相鄰的信號層之任何在此無銅箔面區域上之佈線應從新佈線,使其 可以相鄰一完整平面層. H是代表power plane和ground plane之間的距.(有可能是Trace距平面的高) 使power平面比ground平面小20-H.8 SOLDER SIDE 極好的佈線層(Y方向)接地方式單點接地 (1)在1MHz以上的頻,一般使用單點接地. (2)低頻.中頻.或是高頻各級電,能有效的防止局部電的共阻抗干擾. (3)在較高的頻.Trace的電感會增加PCB的阻抗.接地及信號迴★☆★永遠把高速電及振盪器至於銅柱越近越好. ☆計算所有接地點之直線距與λ/20之比值.接地點間的距要小於λ/20. λ為系統所產生之最高頻之波長.絲固定至屬機殼λ/20 λ/20 λ/20 λ/20 λ/20 λ/20 λ/20 λ/20 λ/20絲固定點間之距應超過電板 上最高頻之λ/20(1) 高頻產品多採用多點機殼接地. (2) 將RF電並由Ground plane至機殼之地.可減低由PCB電源出的 多點接地 地阻抗. (3) 在高頻電上.件的接腳應盡減短. (4)如64MHz振盪器之λ/20為23cm.如果任何個接地絲銅柱間之距大於23cm,就 會有RF環存在.減低RF地迴的位置 ☆ ★ ☆ ★ ☆ ★ ☆ ★ 含有高RF能量的電路與系統的地之間. 依功能區分之子系統之間. 多點接地之處. I/O連線及相關之電路之間. 電源輸入端及系統之地之間. 界面卡連接器及主系統之地之間. 電路板之邊緣.映像平面層Image Plane★映像平面就是一個在電源或地電位之完整銅箔層. ☆使用映像平面層可以提供RF電一個低阻抗徑以迴返到其源頭,達到RF電的 迴返徑並減低EMI. ★RF電會產生電容性偶合(或電感)如果是100%偶合,則trace與最近平面就會 產生common-mode RF電.在PCB內部的映像平面就會低地雜訊電壓,而允 許RF電以較緊密的耦合方式回到源頭.緊密的耦合可提供flux cancellation,這 也是使用完整平面的另一個原因之ㄧ. ☆集膚深:電只在物質的表層集膚深動.所以differential-mode以及 commom-mode電只在平面的表層動,會在映像平面的內部或底層動.I1 E I2 Itotal=I1+I2 Common-mode Current Z EI1 I2 Itotal=I1-I2 Differential-mode Current Z2分割 Partitioning☆要防止同的頻寬區域間互相耦合,就要採用功能上的分割, ★適當的分割可以穩定電.簡化佈線.改善信號品質. ★盡少用貫穿孔,因為貫穿孔會在電上增加約1-3nH的電感. ★管PCB或週邊的電源帶出的雜訊皆應要以bypass電容ac並至機殼之地. ☆這些電容可以低power supply帶出的RF電Coupling至信號及data線上.將power 接器的RF電移除可以改善主機板與周邊信號傳輸的品質.也可以低EMI. ☆將電板依功能區分成子系統.將高頻區、中頻區、低頻區分開.,如果可以的話將之分割. ★每一個分割區都要接地至機殼之地,接地的越多越可以減低地迴.第三章旁及去耦合 Bypassing and DecouplingBypassing及decoupling是防止RF能由一電轉移至另一電的技術. 最佳的應用方式是同時運用Bulk、Bypass及Decoupling電容.Decoupling:去耦合電容將高頻元件產生在電源平面上的RF能移除.主要是為 在clock或data轉換時,提供足夠的dc電壓及電給元件的正常操作. 當在最大電容負載的況下元件的信號腳同時換時,藉由在power trace及ground trace之間卻保有一低阻抗之電源達成耦合. 如果用太多的decoupling電容,會由電源供應器吸引大的電,因 此應在power supply放一群bulk電容以提供其電. Bypassing:旁電容能移除需要的RF雜訊.避免其耦合元件或cable之commonmode EMI進入敏感區,並且提供波功能. Bulk:大型電容在最大負載下,所有通訊腳同時換,對元件保持其DC電及電壓穩 定,同時可以防止因元件之電湧造成的電源失效. 提供電之能儲存以維持所需的電及電壓. 在power輸入端及板子的對角方向加上大型(bulk)電容,在power輸入接 器最遠的地方加bulk電容,在有大的直電壓及電需求的元件邊皆應加上 bulk電容.bulk電容會減小電壓及電的波動,提高系統的穩定.I/O InterConnect I/O Logic User Interface Logic Gate Arrey/ Control Logic Support Logic Support Logic Power for Peripherals Peripheral I/O Peripheria l I/OPower for PeripheralsDMA Controller Memory buffer Memory arreyCPU,Cache, OscillatorPower for Peripherals諧振 (共振) Resonance◎在電容本身就包含一個LCR電,在此處L=接腳長的電感,R=接腳的電 阻,C=本身電容.當到達某一頻時,L及C之組合變成諧振,提供一個非 常低的阻抗而有效的轉移RF信號.當頻到達諧振以上的時候,電容性就會 變成電感性,使Bypassing及Decoupling變的沒有效果. ★共振是發生在當電感向及電容向的相位差為的時候.也就是此時電 對AC電壓是純電阻性.並諧振 當一並RLC電在諧振點時, 阻抗最大 阻抗等於電阻 相位差(phase angle difference)為 電最小 功(power)最小C L Rω=1LC諧振:XL=XC並C , RL諧振ωL =1CωC在實際上的諧振電一般會包括一個電感與一個電容 並,因為電感會具有一些電阻,所以等效的電圖就 是RL,並C. 這一種型式的諧振,在諧振點的時候電會最低.ω = 1 LC諧振電 總阻抗為R+j(XL-XC)當一RLC電在諧振點時, 阻抗最低 阻抗等於電阻 相位差(phase angle difference)為 電最大 功(power)最大RLω=1LC R L2電容器的物特性 ★電容器在諧振頻時還是電容性.但是到達諧振頻以上的時候電容就會變成電 感性,並會隨著頻的增加而增大其電感性.所以去耦合的效果就低. ☆電感並會改變特性跟電容一樣.但是其阻抗大小會隨著頻的改變而改變. ★電感周圍的寄生電容會導致並諧振而改變響應.電的頻越高其阻抗越高. RF電經一個阻抗造成RF電壓,其關係式為歐姆定 Vrf=Irf x Zrf . ☆在設計去耦合電容時最重要的關點就是接腳的引線和電感. ★在某些運用上.需要並個電容以達到較寬的RF壓制頻帶時.這個電容應該要 相差100倍(如0.1μF與0.001μF)才能達到最佳的效果. ☆在使用大型電容時,選擇電容器的額定電壓應大於該電源訊號的倍,以避免因為 電壓突波造成電容的破壞. ★並電容器 ◎並電容的低接腳電感.此時組電容器接腳並,可以提供倍的接線寬使接 線電感減低.此低的電感就是並電容器的主要由. ●在大容質電容器之諧振頻點以上其阻抗隨頻增加而增加(電感性),而小容質 電容器扔為電容性. ◎要移除所有信號腳同時換產生的RF電,通常是使用個電容並(0.1μF及 0.001μF)緊鄰在每一個電源腳旁邊,電容值必須要相差100倍.電源 C1 R1 L1 接地 C2 R2 L2 C2:100pF與1000pF 電容器並之等效電 C1:0.1uF與0.01uF 電容器並之等效電3Placement 件放置★在考慮要如何放置件的同時.必須先解PCB的實體構成. ☆將一個去耦合電容鄰近於IC的電源腳做為電儲存可以達成一小區域環.此去耦 合電的阻抗一定要小於其他電源分配電的阻抗.此一低阻抗可以確保在trace 及電中的高頻成分可以完全的在此封閉的環中. ★當使用去耦合電容時重要的是減短接腳的長並且盡靠近元件旁邊. ☆去耦合電容因放置在每一個元件旁邊.至少應該要預去耦合電容的位置以於 EMI測試時的需求.再測試過程中在視情況移除一些多餘的電容. 大型電容放置位置:(1).電源供應器進入PCB之電源輸入接器的位置. (2).附屬卡週邊次級電之I/O接器的電源端. (3).電源消耗大的電或元件旁. (4).距電源輸入結器最遠的距. (5).與DC輸入端遠高密元件區. (6).Clock電旁邊.Thanks for your attention!!4一﹑零件佈置Placement第四章 : Clock 電路將 clock 電放在機版中央或 PCB 之屬銅柱接地點,可放在邊緣或接近I/O電區 Clock trace 要成點對點的射,在接器端對 clock 作 termination 可提供合適的終 端避免Clock trace 成為一單極天線。