xilinx FPGA SelectIO模块资料

Xilinx-FPGA配置的一些细节

Xilinx-FPGA配置的一些细节Xilinx FPGA配置的一些细节2010年07月03日星期六 14:260 参考资料(1) Xilinx: Development System Reference Guide. dev.pdf, v10.1在Xilinx的doc目录下有。

(2) Xilinx: Virtex FPGA Series Configuration and Readback. XAPP138 (v2.8) March 11, 2005在Xilinx网站上有,链接/bvdocs/appnotes/xap p138.pdf(3)Xilinx: Using a Microprocessor to Configure Xilinx FPGAs via Slave Serial or SelectMAP Mode.XAPP502 (v1.5) December 3, 2007在Xilinx网站上有,链接/bvdocs/appnotes/xap p502.pdf注:此外xapp139和xapp151也是和配置相关的。

(4)Xilinx: Virtex-4 Configuration Guide. UG071 (v1.5) January 12, 2007(5) Tell me about the .BIT file format.链接:/FAQ_Pages/0026_Tell_me_about_bit_files.htm1 Xilinx配置过程主要讲一下Startup Sequence。

Startup Sequence由8个状态组成.除了7是固定的之外,其它几个的顺序是用户可设置的,而且Wait for DCM和DCI是可选的。

其中默认顺序如下:这些在ISE生成bit文件时通过属性页设定。

这几个状态的具体含义如下:Release_DONE : DONE信号变高GWE : 使能CLB和IOB,FPGA的RAMs和FFs可以改变状态GTS : 激活用户IO,之前都是高阻。

xilinxFPGASelectIO模块

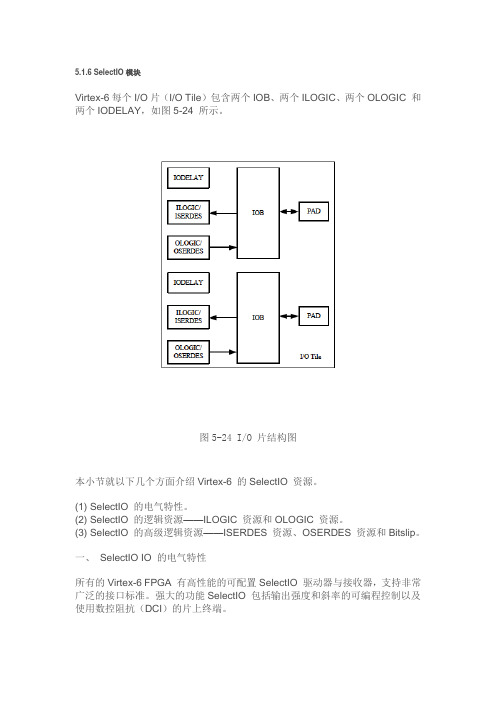

5.1.6 SelectIO模块Virtex-6每个I/O片(I/O Tile)包含两个IOB、两个ILOGIC、两个OLOGIC 和两个IODELAY,如图5-24 所示。

图5-24 I/O 片结构图本小节就以下几个方面介绍Virtex-6 的SelectIO 资源。

(1) SelectIO 的电气特性。

(2) SelectIO 的逻辑资源——ILOGIC 资源和OLOGIC 资源。

(3) SelectIO 的高级逻辑资源——ISERDES 资源、OSERDES 资源和Bitslip。

一、SelectIO IO 的电气特性所有的Virtex-6 FPGA 有高性能的可配置SelectIO 驱动器与接收器,支持非常广泛的接口标准。

强大的功能SelectIO 包括输出强度和斜率的可编程控制以及使用数控阻抗(DCI)的片上终端。

IOB 包含输入、输出和三态SelectIO 驱动器。

支持单端I/O 标准(LVCMOS、HSTL、SSTL)和差分I/O 标准(LVDS、HT、LVPECL、BLVDS、差分HSTL 和SSTL)。

注意:差分输入和VREF 相关输入由VCCAUX 供电。

IOB、引脚及部逻辑的连接如图5-25 所示。

图5-25 IOB、引脚及部逻辑连接图IOB 直接连接ILOGIC/OLOGIC 对,该逻辑对包含输入和输出逻辑资源,可实现数据和三态控制。

ILOGIC和OLOGIC可分别配置为ISERDES和OSERDES。

Xilinx软件库提供了大量与I/O相关的原语,在例化这些原语时,可以指定I/O标准。

与单端I/O相关的原语包括IBUF(输入缓冲器)、IBUFG(时钟输入缓冲器)、OBUF(输出缓冲器)、OBUFT(三态输出缓冲器)和IOBUF(输入/输出缓冲器)。

与差分I/O相关的原语包括IBUFDS(输入缓冲器)、IBUFGDS (时钟输入缓冲器)、OBUFDS(输出缓冲器)、OBUFTDS(三态输出缓冲器)、IOBUFDS(输入/输出缓冲器)、IBUFDS_DIFF_OUT(输入缓冲器)和IOBUFDS_DIFF_OUT(输入/输出缓冲器)。

xilinx的select io用法 -回复

xilinx的select io用法-回复Xilinx的SelectIO用法是FPGA设计中的一个重要部分,用于实现输入输出(IO)功能。

SelectIO引脚提供了可配置和高性能的输入输出资源,能够适应不同类型的信号和电平标准。

本文将逐步讨论Xilinx的SelectIO 用法,包括SelectIO的架构、配置和应用。

一、SelectIO架构Xilinx的SelectIO架构基于IOB(Input Output Buffer)单元,提供了许多可编程的特性,可以灵活地适应不同的应用需求。

它包括四个主要组件:1. 输入寄存器(Input Register):用于接收外部信号,并对其进行缓存和同步。

输入寄存器可以配置为寄存器模式或者旁路模式。

2. 输出寄存器(Output Register):用于发送数据到外部设备。

输出寄存器可以配置为输出驱动模式或者旁路模式。

3. 引脚锁定(Pin Locking):用于锁定引脚的配置。

一旦引脚被锁定,就无法再修改其配置。

4. 引脚复用(Pin Muxing):用于将不同的功能分配给IO引脚。

每个IO 引脚可以配置为多个不同的功能,如输入、输出、双向、全局时钟等。

二、SelectIO配置1. 使用IP核:Xilinx提供了一系列IP核,用于简化SelectIO的配置和使用。

可以使用工具进行图形化配置,设置不同的参数和功能选项,并生成对应的Verilog/VHDL代码。

2. 使用XDC文件:Xilinx设计约束(XDC)文件可以用于指定SelectIO 的配置参数。

可以通过XDC文件中的约束语法来设置输入输出模式、电平标准、时钟频率等。

然后,使用综合工具和实现工具来将XDC文件中的约束映射到具体的FPGA设计中。

3. 使用Vivado工具:Xilinx的Vivado设计套件提供了强大的SelectIO 配置和验证工具。

在Vivado中,可以通过图形界面或命令行工具来配置SelectIO引脚的功能,包括输入输出模式、电平标准、时钟约束等。

fpga芯片 指令集

FPGA芯片指令集

FPGA(Field Programmable Gate Array)是一种可编程逻辑门阵列,其指令集可以根据需要进行配置。

FPGA的指令集通常包括以下几种指令:

配置指令:用于配置FPGA的内部逻辑模块、I/O模块等。

这些指令通常在FPGA上电或重新配置时执行一次。

逻辑操作指令:用于实现逻辑运算,如与、或、非等操作。

这些指令可以用于组合逻辑电路的设计。

控制指令:用于控制FPGA内部模块的时序和状态。

例如,使能信号、时钟信号等。

内存操作指令:用于对FPGA内部的RAM、FIFO等存储器进行读写操作。

I/O操作指令:用于配置FPGA的输入输出引脚,设置其电平和方向等。

这些指令集的具体实现和语法规则取决于具体的FPGA芯片和开发工具。

不同的FPGA厂商和开发工具可能具有不同的指令集和语法规则,因此在实际应用中需要根据具体的硬件和开发环境进行选择和使用。

XilinxFPGA介绍

目前FPGA芯片仍是基于查找表技术的,但其概念和性能已经远远超出查找表技术的限制,并且整合了常用功能的硬核模块(如块RAM、时钟管理和DSP)。

图1-1所示为Xilinx公司FPGA的内部结构示意图(由于不同系列的应用场合不同,所以内部结构会有一定的调整),从中可以看出FPGA芯片主要由 6部分组成:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块。

图1-1 FPGA芯片的内部结构每个模块的功能如下:1.可编程输入输出单元(IOB)可编程输入/输出单元简称I/O单元,是芯片与外界电路的接口部分,完成不同电气特性下对输入/输出信号的驱动与匹配要求,提供输入缓冲、输出驱动、接口电平转换、阻抗匹配以及延迟控制等功能,其一般示意结构如图1-2所示。

FPGA内的I/O按组分类,每组都能够独立地支持不同的I/O标准。

通过软件的灵活配置,可适配不同的电气标准与I/O物理特性,可以调整驱动电流的大小,可以改变上、下拉电阻。

目前,I/O口的频率也越来越高,一些高端的FPGA 通过DDR寄存器技术可以支持高达2Gbps的数据速率。

外部输入信号可以通过IOB模块的存储单元输入到FPGA的内部,也可以直接输入FPGA 内部。

当外部输入信号经过IOB模块的存储单元输入到FPGA内部时,其保持时间(Hold Time)的要求可以降低,通常默认为0。

为了便于管理和适应多种电器标准,FPGA的IOB被划分为若干个组(bank),每个bank的接口标准由其接口电压VCCO决定,一个bank只能有一种VCCO,但不同bank的VCCO可以不同。

只有相同电气标准的端口才能连接在一起,VCCO 电压相同是接口标准的基本条件。

2.可配置逻辑块(CLB)CLB是FPGA内的基本逻辑单元。

CLB的实际数量和特性会依器件的不同而不同,但是每个CLB都包含一个可配置开关矩阵,此矩阵由4或6个输入、一些选型电路(多路复用器等)和触发器组成。

xilinxfpga引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_#用户IO引脚XX代表某个Bank内唯一得一对引脚,Y=[P|N]代表对上升沿还就是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_#多功能引脚ZZZ代表在用户IO得基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚.D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0就是数据得最低位,在Bit—serial模式下,DIN就是信号数据得输入;在SPI模式下,MISO就是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1就是SPI总线得第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1与D2就是数据总线得低位;在SPI*4模式下,MISO2与MISO3就是SPI总线得MSBs.An:O,A[25:0]为BPI模式得地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式得状态输出引脚。

SUSPEND就是一个专用引脚,AW A KE就是一个多功能引脚。

除非SUSPEND模式被使能,AW AKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B就是一个低电平有效得片选信号;在SPI*2或者SPI*4得模式下,MISO0就是SPI总线得第一位数据。

FCS_B:O,BPI flash 得片选信号.FOE_B:O,BPI flash得输出使能信号FWE_B:O,BPIflash 得写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AW AKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE 是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

xilinxfpga引脚功能详细介绍

Xilinx F PGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户10引脚XX代表某个Bank内唯一的一对引脚,Y=[PIN]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_#多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn: I/O (在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出曰。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISOl: I,在并口模式(SelectMAP/BPI)下,DO 是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_M1SO2, D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBsoAn: 0, A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O 口。

AWAKE: O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE 是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISOO: I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下, CSI_B 是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISOO是SPI总线的第一位数据。

FCS_B: 0, BPI flash 的片选信号。

FOE_B: O, BPI flash的输出使能信号FWE_B: O, BPI flash的写使用信号LDC: O, BPI模式配置期间为低电平HDC: O, BPI模式配置期间为高电平CSO_B: O,在并口模式下,工具链片选信号。

ilin fpga 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

xilinx原语手册手册

xilinx原语手册手册

Xilinx原语手册是一份详细介绍Xilinx FPGA(现场可编程门

阵列)器件中可用原语的手册。

Xilinx原语是一组预定义的硬件功

能模块,可以在FPGA设计中使用。

这些原语包括逻辑门、存储器单元、乘法器、加法器等,它们可以用于构建复杂的数字逻辑电路和

信号处理系统。

这份手册通常包含了各种原语的详细说明,包括其

功能、输入输出接口、时序特性以及在设计中的最佳实践等内容。

在Xilinx原语手册中,你可以找到关于各种原语的详细描述,

包括其功能、使用方法、时序要求、资源占用情况等。

这些信息对

于FPGA设计工程师来说非常重要,因为它们可以帮助工程师更好地

理解和利用FPGA中的硬件资源,从而设计出高性能、低功耗的电路。

除了具体的原语介绍外,Xilinx原语手册还可能包括一些设计

实例和最佳实践,帮助工程师更好地应用这些原语来解决实际的设

计问题。

此外,手册中也可能包含一些与原语相关的设计注意事项、时序约束建议等内容,这些对于确保设计的正确性和稳定性非常重要。

总之,Xilinx原语手册是Xilinx FPGA设计工程师日常工作中

的重要参考资料,它提供了关于FPGA原语的全面而详细的信息,帮助工程师更好地应用这些原语来设计出高性能、可靠的数字电路系统。

xilinx的select io用法

Xilinx的Select IO是一种灵活的I/O接口解决方案,用于连接FPGA引脚和其他接口。

它提供了一种方式来选择不同的I/O标准或配置,以满足不同的应用需求。

Select IO的主要用法包括:

1.选择I/O标准:Select IO可以配置为不同的I/O标准,如LVDS、LVCMOS、

LVTTL等,以满足不同的接口需求。

2.配置引脚:通过Select IO,可以配置FPGA引脚为输入、输出、双向或独立

的I/O总线。

这使得开发者可以根据需要灵活地配置引脚的方向和功能。

3.高速接口设计:Select IO支持高速接口设计,如HDMI、DisplayPort等,

可以满足高带宽数据传输的需求。

4.自定义接口:除了标准的I/O接口外,开发者还可以使用Select IO来实现自

定义的接口协议,以满足特定的应用需求。

需要注意的是,使用Select IO需要一定的硬件和软件知识,以及对FPGA设计和编程的理解。

在使用Select IO时,建议参考Xilinx的官方文档和相关教程,以确保正确地配置和使用Select IO。

xilinx的select io用法 -回复

xilinx的select io用法-回复Xilinx's Select IO Usage: An In-depth GuideIntroduction:Xilinx is a renowned semiconductor company that specializes in programmable logic devices and associated software tools. One of the notable features in Xilinx's product line is the Select IO interface, which offers versatile capabilities to interface programmable devices with external systems. In this article, we will dive into the usage of Select IO and explore its step-by-step implementation.Part 1: Understanding Select IOBefore we delve into the practical aspects of using Select IO, it is important to understand its significance. Select IO is ahigh-performance interface that enables seamless communication between programmable devices, such as FPGAs, and external systems, such as memory or peripheral devices. It provides flexible I/O configurations with various voltage standards, support for different protocols, and advanced features like real-time data capture and transmission.Part 2: Select IO ArchitectureTo effectively utilize Select IO, it's crucial to have a grasp of its underlying architecture. Select IO consists of several key components, including differential input/output buffers, clock management circuitry, programmable impedance control, and digital signal processing blocks. These features collectively enable the interface to handle a wide range of I/O requirements and optimize the signal quality.Part 3: Select IO ConfigurationNow that we understand the fundamentals, let's move on to the configuration aspect of Select IO. The process involves a series of steps outlined below:Step 1: Identifying I/O Pin LocationsStart by identifying the specific I/O pins on the programmable device that will be used for interfacing with external systems. This involves referring to the device's datasheet or pin configuration documentation provided by Xilinx.Step 2: Assigning I/O StandardsSelect IO supports multiple I/O standards, such as LVCMOS, LVDS, HSTL, etc. Choose the appropriate I/O standard based on thevoltage levels and signaling requirements of the external system. The Xilinx Vivado Design Suite provides a user-friendly interface to assign I/O standards to the relevant I/O pins.Step 3: Configuring Voltage LevelsNext, configure the voltage levels for each I/O pin. Select IO allows for flexible voltage assignments, catering to both single-ended and differential signaling requirements. Ensure the voltage levels specified are compatible with the connected external systems.Step 4: Enabling Output/Input Buffer FeaturesSelect IO offers various advanced features, such as on-chip termination, data capture, and programmable output drive strength. Enable and configure these features as per the specific project requirements, ensuring optimal signal integrity and noise immunity.Step 5: Assigning Output/Input Delay ConstraintsTo meet timing requirements, assign appropriate output and input delay constraints. This step ensures that data is correctly captured or transmitted within the desired timing margins and complies with the design specifications.Part 4: Advanced Features of Select IOIn addition to its core functionality, Select IO provides several advanced features that enhance its versatility and performance. These features include:1. Programmable I/O impedance control: Select IO allows for impedance matching and termination adjustments, thereby optimizing signal integrity for specific applications.2. Real-time data capture: This feature enables the capturing of incoming data signals accurately and precisely, facilitating applications that require high-speed data acquisition.3. In-system programmability: Select IO can be reconfiguredon-the-fly, allowing for dynamic changes in I/O standards, voltage levels, and other parameters during runtime, enhancing system flexibility.Part 5: Verification and TestingOnce the Select IO configuration is complete, it is crucial to thoroughly test and verify the interface's functionality. Use Xilinx'sverification tools, such as simulation and hardware debugging, to ensure proper signal transmission, noise immunity, and compliance with the design specifications.Conclusion:Select IO is a powerful interface provided by Xilinx, enabling easy and efficient communication between programmable devices and external systems. Understanding its architecture and following the step-by-step configuration process outlined in this article will empower engineers to effectively utilize Select IO's capabilities. With its advanced features and support for diverse I/O requirements, Select IO is a valuable tool in the arsenal of FPGA designers and embedded systems developers.。

Xilinx7系列FPGA架构之器件配置(一)

Xilinx7系列FPGA架构之器件配置(一)引言:本系列博文描述7系列FPGA配置的技术参考。

作为开篇,简要概述了7系列FPGA的配置方法和功能。

随后的博文将对每种配置方法和功能进行更详细的描述。

本文描述的配置方法和功能适用于所有7系列家族器件,只有少数例外。

1.概述Xilinx®7系列FPGA通过将特定于应用程序的配置数据(位流)加载到内存中进行配置。

7系列FPGA可以主动从外部非易失性存储设备加载,也可以通过外部智能源(如微处理器、DSP处理器、微控制器、PC或板测试仪)被动进行配置。

在任何情况下,都有两个通用配置数据路径。

第一个是串行数据路径,这种情况需要最少的硬件管脚连接。

第二个数据路径是8位、16位或32位数据路径,用于更高性能或访问(或链接)行业标准接口,非常适合外部数据源,如处理器或x8或x16并行闪存。

与处理器和处理器外围设备一样,Xilinx FPGA可以在线重新编程,编程次数无限制。

由于Xilinx FPGA配置数据存储在CMOS配置锁存器(CCL)中,因此必须在断电后对其进行重新配置。

每次通过专用配置引脚将比特流加载到FPGA器件中。

这些配置引脚可以用作多种不同配置模式的接口:•主动-串行配置模式•从(或被动)-串行配置模式•主动-并行(SelectMAP)配置模式(x8和x16)•主动-并行(SelectMAP)配置模式(x8,x16和x32)•JTAG边界扫描模式•主动-串行SPI Flas配置模式(x1,x2,x4)•主动-字节BPI Flash配置模式(x8,x16),使用并行NOR Flash这些配置模式通过输入管脚M[2:0]设置不同的电平进行模式选择。

M2,M1和M0应该连接至DC电压常量,可以直接接GND或者VCCO_0或者通过上拉或下拉电阻(≤1kΩ)连接至GND或者VCCO_0。

上述几种配置模式中主或者从是以配置时钟管脚CCLK的方向为参考的。

fpga的基本构造单元

FPGA的基本构造单元主要包括可编程输入/输出单元(IOB)、基本可编程逻辑单元、完整的时钟管理模块、丰富的布线资源以及内嵌的底层功能单元和嵌入式专用硬核。

1. 可编程输入/输出单元(IOB):目前大多数FPGA的I/O单元被设计为可编程模式,即通过软件的灵活配置,可适应不同的电器标准与I/O物理特性。

可以调整匹配阻抗特性,上下拉电阻;可以调整输出驱动电流的大小等。

2. 基本可编程逻辑单元:FPGA的基本可编程逻辑单元是由查找表(LUT)和寄存器(Register)组成的,查找表完成纯组合逻辑功能。

FPGA内部寄存器可配置为带同步/异步复位和置位、时钟使能的触发器,也可以配置成为锁存器。

一般依赖寄存器完成同步时序逻辑设计。

3. 时钟管理模块:用于生成精确稳定的时钟信号,以驱动FPGA内部的逻辑和I/O单元。

4. 丰富的布线资源:连接各个逻辑单元,使它们能够以正确的方式通信。

5. 内嵌的底层功能单元和嵌入式专用硬核:这些单元可以完成更复杂的任务,如乘法器、DSP、ARM等。

以上信息仅供参考,如需了解更多信息,建议查阅FPGA相关书籍或咨询专业人士。

xilinx FPGA SelectIO模块资料

5.1.6 SelectIO模块Virtex-6每个I/O片(I/O Tile)包含两个IOB、两个ILOGIC、两个OLOGIC 和两个IODELAY,如图5-24 所示。

图5-24 I/O 片结构图本小节就以下几个方面介绍Virtex-6 的SelectIO 资源。

(1) SelectIO 的电气特性。

(2) SelectIO 的逻辑资源——ILOGIC 资源和OLOGIC 资源。

(3) SelectIO 的高级逻辑资源——ISERDES 资源、OSERDES 资源和Bitslip。

一、SelectIO IO 的电气特性所有的Virtex-6 FPGA 有高性能的可配置SelectIO 驱动器与接收器,支持非常广泛的接口标准。

强大的功能SelectIO 包括输出强度和斜率的可编程控制以及使用数控阻抗(DCI)的片上终端。

IOB 包含输入、输出和三态SelectIO 驱动器。

支持单端I/O 标准(LVCMOS、HSTL、SSTL)和差分I/O 标准(LVDS、HT、LVPECL、BLVDS、差分HSTL 和SSTL)。

注意:差分输入和VREF 相关输入由VCCAUX 供电。

IOB、引脚及内部逻辑的连接如图5-25 所示。

图5-25 IOB、引脚及内部逻辑连接图IOB 直接连接ILOGIC/OLOGIC 对,该逻辑对包含输入和输出逻辑资源,可实现数据和三态控制。

ILOGIC和OLOGIC可分别配置为ISERDES和OSERDES。

Xilinx软件库提供了大量与I/O相关的原语,在例化这些原语时,可以指定I/O标准。

与单端I/O相关的原语包括IBUF(输入缓冲器)、IBUFG(时钟输入缓冲器)、OBUF(输出缓冲器)、OBUFT(三态输出缓冲器)和IOBUF(输入/输出缓冲器)。

与差分I/O相关的原语包括IBUFDS(输入缓冲器)、IBUFGDS (时钟输入缓冲器)、OBUFDS(输出缓冲器)、OBUFTDS(三态输出缓冲器)、IOBUFDS(输入/输出缓冲器)、IBUFDS_DIFF_OUT(输入缓冲器)和IOBUFDS_DIFF_OUT(输入/输出缓冲器)。

Xilinx7系列FPGASelectIO篇(2)

Xilinx7系列FPGASelectIO篇(2)上篇咱们简单的说了I/O的电气特性,本篇咱们接着介绍I/O逻辑资源,先贴上两张图。

图1为HPBANK的I/O模块,图2为HRBANK的I/O模块,两者区别在于后者无ODELAYE模块。

图1:HP BANK I/O模块图2:HR BANK I/O模块I/O逻辑资源主要包含5部分:1, ILOGICILOGIC即输入信号处理逻辑,紧挨着IOB,外界的输入信号最先经过的就是ILOGIC。

ILOGIC是由许多的数据选择器和一个IDDR(inputDouble data rate)触发器构成。

该触发器既可以双沿捕获输入数据也可以拆分成普通单沿触发器。

在HP BANK中,ILOGIC被称为ILOGICE2,在HR BANK中,ILOGIC被称为ILOGICE3。

图3给出了ILOGICE3的示意图:图3:ILOGICE3示意图2, IDELAYIDELAY被称为信号延迟模块,它的作用就是把信号延迟一段时间。

对于一些需要对齐的输入信号来说,这至关重要。

在7系列FPGA中,它被称为IDELAYE2。

IDELAYE2可以将信号延迟0~31节,在这区间任意可调,并且每节的延迟精度约为78ps(1/(32×2×FREF),FREF 为IDELAYCTRL的参考时钟)。

图4为IDELAYE2例化框图。

图4:IDELAYE2例化框图3, IDELAYCTRLIDELAYCTRL其实是个辅助模块,这么说吧,只要咱们使用了IDELAY或者ODELAY,IDELAYCTRL必须被使用,要不然就无法正常工作。

因为IDELAY或者ODELAY的延迟精度是由IDELAYCTRL的输入时钟决定的,一般为200MHz。

下图5为IDELAYCTRL例化框图。

图5:IDELAYCTRL例化框图4, ODELAYODELAY和IDEALY的使用方式差不多,只不过ODELAY是用作输出信号的延迟。

简谈XilinxFPGA原理及结构

简谈XilinxFPGA原理及结构FPGA是在PAL、PLA和CPLD等可编程器件的基础上进一步发展起来的一种更复杂的可编程逻辑器件。

它是ASIC领域中的一种半定制电路,既解决了定制电路的不足,又克服了原有可编程器件门电路有限的缺点。

由于FPGA需要被反复烧写,它实现组合逻辑的基本结构不可能像ASIC那样通过固定的与非门来完成,而只能釆用一种易于反复配置的结构,查找表-Look Up Table,LUT,可以很好地满足这一要求。

目前,主流FPGA都采用了基于SRAM工艺的查找表结构,也有一些军品和宇航级FPGA采用Flash/熔丝/反熔丝工艺的查找表结构。

1查找表结构及功能由布尔代数理论可知,对于一个n输入的逻辑运算,最多产生2^n个不同的组合。

所以,如果预先将相应的结果保存在一个存储单元中,就相当于实现了与非门电路的功能。

FPGA的原理的实质,就是通过配置文件对查找表进行配置,从而在相同的电路情况下实现了不同的逻辑功能。

1.1输入查找表结构LUT本质就是一个RAM。

自FPGA诞生以来,多使用4输入的LUT,可以看成一个包含四位地址线的RAM。

当设计者通过原理图或HDL描述了一个逻辑电路后,FPGA厂商提供的集成开发工具就会自动计算逻辑电路的所有可能结果,并把真值表事先写人到RAM中。

这样,每输入一个信号进行逻辑运算就等于输人一个地址进行查表,找出地址对应的内容,然后输出内容即可。

下面用一个4输人逻辑与门电路的例子来说明LUT实现组合逻辑的原理。

LUT描述四输入逻辑与关系如表2.1所示。

表2.1 输入与门的真值表从表2.1可以看到,LUT具有和逻辑电路相同的功能,但是LUT 具有更快的执行速度和更大的规模。

与传统化简真值表构造组合逻辑的方法相比,LUT具有明显的优势,主要表现在:(1)LUT实现组合逻辑的功能由输入决定,而不是由复杂度决定。

(2)LUT实现组合逻辑有固定的传输延迟。

1.2输入查找表新结构在65nm工艺条件下,与其他电路(特别是互连电路)相比,LUT的常规结构大大缩小。

FPGA模块说明书

FPGA模块1 概述1.1模块结构框图和功能描述该模块具有在线下载和在系统可编程功能,模块可采用总线供电和外部供电两种供电方式;模块中采用的FPGA为altera公司的CycloneⅡEP2C5Q208C8N 的FPGA,具有4608个逻辑单元,119808个比特的嵌入RAM,两个锁相环(PLL),142个用户I/O管脚,可使用Altera的Nios软核和丰富的IP库,快速实现完整的可编程单芯片系统(SOPC),完全满足复杂的设计要求。

1.2模块系统资源分配:计算机可以通过JATG向FPGA下载程序;FPGA通过本模块提供的丰富I/O口与片外资源发生进行数据交换,从而达到与片外资源进行有效的通信;本模块向用户提供了十分丰富的I/O口,用户可以通过编程对这些I/O口进行各种操作。

提供了4*4的键盘,8个发光二极管,4个单独的按键。

AS方式与JATG方式AS为FPGA主动下载方式,在FPGA主动下载方式中,由目标FPGA来输出控制和同步信号(包括配置时钟)给Altera专用的一种串行配置芯片(EPCS1),在配置芯片收到命令后,就把配置数据发到FPGA,完成配置过程。

在系统上电后,FPAG和配置器件都进入到上电复位关态(POR)。

这时,FPGA驱动nSTATUS为低,指示其处于“忙”态;同时驱动CONF_DONE为低,表示器件未被配置。

当POR过程完成以后,FPGA随即释放nSTA TUS信号,这个开漏信号被外部的上拉电阻拉为高电平后,FPGA就进入了配置模式。

在AS配置中所有操作均由FPGA发起,它在配置过程中完全处于主动状态。

在该配置模式下,FPGA输出有效配置时钟信号DCLK,它是由FPGA将驱动nCSO信号为低,这就使能了串行配置器件。

FPGA使用ASDO到ASDI的信号控制配置芯片,配置数据由DA TA管脚读出,配置到FPGA中。

从而完成整个配置过程。

AS下载方式如图:图中串行时钟输入(DCLK);AS控制信号输入(ASDI);片选信号(nCS);串行数据输出(DA TA);JA TG是IEEE 1149.1边界扫描测试的标准接口。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

5.1.6 SelectIO模块Virtex-6每个I/O片(I/O Tile)包含两个IOB、两个ILOGIC、两个OLOGIC 和两个IODELAY,如图5-24 所示。

图5-24 I/O 片结构图本小节就以下几个方面介绍Virtex-6 的SelectIO 资源。

(1) SelectIO 的电气特性。

(2) SelectIO 的逻辑资源——ILOGIC 资源和OLOGIC 资源。

(3) SelectIO 的高级逻辑资源——ISERDES 资源、OSERDES 资源和Bitslip。

一、SelectIO IO 的电气特性所有的Virtex-6 FPGA 有高性能的可配置SelectIO 驱动器与接收器,支持非常广泛的接口标准。

强大的功能SelectIO 包括输出强度和斜率的可编程控制以及使用数控阻抗(DCI)的片上终端。

IOB 包含输入、输出和三态SelectIO 驱动器。

支持单端I/O 标准(LVCMOS、HSTL、SSTL)和差分I/O 标准(LVDS、HT、LVPECL、BLVDS、差分HSTL 和SSTL)。

注意:差分输入和VREF 相关输入由VCCAUX 供电。

IOB、引脚及内部逻辑的连接如图5-25 所示。

图5-25 IOB、引脚及内部逻辑连接图IOB 直接连接ILOGIC/OLOGIC 对,该逻辑对包含输入和输出逻辑资源,可实现数据和三态控制。

ILOGIC和OLOGIC可分别配置为ISERDES和OSERDES。

Xilinx软件库提供了大量与I/O相关的原语,在例化这些原语时,可以指定I/O标准。

与单端I/O相关的原语包括IBUF(输入缓冲器)、IBUFG(时钟输入缓冲器)、OBUF(输出缓冲器)、OBUFT(三态输出缓冲器)和IOBUF(输入/输出缓冲器)。

与差分I/O相关的原语包括IBUFDS(输入缓冲器)、IBUFGDS (时钟输入缓冲器)、OBUFDS(输出缓冲器)、OBUFTDS(三态输出缓冲器)、IOBUFDS(输入/输出缓冲器)、IBUFDS_DIFF_OUT(输入缓冲器)和IOBUFDS_DIFF_OUT(输入/输出缓冲器)。

二、SelectIO的逻辑资源SelectIO的逻辑资源主要是指ILOGIC和OLOGIC资源,它们完成了FPGA引脚到内部逻辑的连接功能,包括组合输入/输出、三态输出控制、寄存器输入/输出、寄存器三态输出控制、DDR输入/输出、DDR输出三态控制、IODELAYE1高分辨率可调整延迟单元及其控制模块。

下面简要介绍ILOGIC和OLOGIC功能。

(1) ILOGIC。

图5-26 ILOGIC内部逻辑ILOGIC的内部逻辑如图5-26所示,可以实现的操作包括:异步/组合逻辑、DDR 模式(OPPOSITE_EDGE、SAME_EDGE或SAME_EDGE_PIPELINED)、电平敏感型锁存器和边沿触发D型触发器。

∙异步/组合逻辑。

用来创建输入驱动器与FPGA内部资源之间的直接连接。

当输入数据与FPGA 内部逻辑之间存在直接(非寄存)连接,或者当“将I/O寄存器/锁存器合并到IOB 中”的设置为OFF时,此通路被自动使用。

∙输入DDR(IDDR)。

Virtex-6器件的ILOGIC中有专用寄存器来实现输入双倍数据速率(DDR)。

可以通过例化IDDR的原语来使用此功能。

IDDR只有一个时钟输入,下降沿数据由输入时钟的反相版本(在ILOGIC内完成反相)进行时钟控制。

所有输入I/O 模块的时钟均为完全多路复用,即ILOGIC或OLOGIC模块之间不共用时钟。

IDDR支持以下三种操作模式:OPPOSITE_EDGE模式、SAME_EDGE模式和SAME_EDGE_PIPELINED模式。

SAME_EDGE和SAME_EDGE_PIPELINED与Virtex-5一样。

这些模式允许设计人员在ILOGIC模块内部将下降沿数据转移到上升沿时钟域,以节省CLB和时钟资源并提高性能。

这些模式是用DDR_CLK_EDGE属性实现的。

各模式下时序图请参考图5-27、图5-28和图5-29。

图5-27 OPPOSITE_EDGE模式下的输入双倍数据速率图5-28 SAME_EDGE模式下的输入双倍数据速率图5-29 SAME_EDGE_PIPELINED模式下的输入双倍数据速率可编程绝对延迟单元IODELAYE1。

每个I/O模块包含一个可编程绝对延迟单元,称为IODELAYE1。

IODELAYE1可以连接到ILOGIC/ISERDES或OLOGIC/OSERDES模块,也可同时连接到这两个模块。

IODELAYE1是具有32个tap的环绕延迟单元,具有标定的tap分辨率。

请参考附带光盘中的《Virtex-6 IO用户手册》。

IODELAYE1可用于组合输入通路、寄存输入通路、组合输出通路或寄存输出通路,还可以在内部资源中直接使用。

IODELAYE1允许各输入信号有独立的延迟。

通过在《Virtex-6用户手册》中规定的范围内选择IDELAYCTRL参考时钟,可以改变tap延迟分辨率。

IODELAYE1资源可用作IDELAY、ODELAY或组合延迟。

.IDELAYE1允许各输入信号有独立的延迟。

延迟单元可以被校验到一个绝对延时固定值(TIDELAYRESOLUTION),这个值不随工艺,电压和温度的变化而改变。

IODELAYE1有四种操作模式:分别是零保持时间延迟模式(IDELAY_TYPE=DEFAULT)、固定延迟模式(IDELAY_TYPE=FIXED)、可变延迟模式(IDELAY_TYPE=VARIABLE)和可装载的可变延时模式(IDELAY_TYPE=VAR_LOADABLE)。

零保持时间延迟模式允许向后兼容,以使用Virtex-5器件中的零保持时间延迟功能的设计,在这种模式下使用时,不需要例化IDELAYCTRL的原语。

在固定延迟模式,延迟值由属性IDELAY_VALUE确定的tap数决定,此值配置后不可更改,此模式必须例化IDELAYCTRL的原语。

在可变延迟模式,配置后通过控制信号CE和INC来改变延迟值,此模式必须例化IDELAYCTRL的原语。

在可装载的可变延时模式下,IDELAY TAP可以通过FPGA逻辑相连的5位CNTVALUEIN<4:0>装载。

当配置为此模式时,也必须例化IDELAYCTRL原语。

∙IDELAYCTRL延时控制模块。

当IDELAYE1或ISERDES的原语中的IOBDELAY_TYPE属性设置为FIXED、VARIABLE或者VAR_LOADABLE时,都必须例化IDELAYCTRL。

IDELAYCTRL模块连续校验IODELAYE1的延时环节,以减少工艺、电压和温度的影响。

(2) OLOGIC资源。

OLOGIC由两个主要模块组成,分别是输出数据通路和三态控制通路。

这两个模块具有共同的时钟(CLK),但具有不同的使能信号OCE和TCE。

输出通路和三态通路可独立配置为边沿触发的D型触发器、电平敏感锁存器、异步/组合逻辑或者DDR模式。

∙组合数据输出和三态控制路径。

组合输出通路用来实现从FPGA内部逻辑到输出驱动器或输出驱动器控制端的直接连接。

当FPGA的内部逻辑与输出数据或三态控制之间存在直接(不寄存)连接,或者当“将I/O寄存器/锁存器合并到IOB中”的设置为OFF时,此路径被使用。

∙输出DDR(ODDR)。

Virtex-6器件的OLOGIC中具有专用寄存器,用来实现DDR功能。

要使用此功能,只需要例化ODDR。

ODDR只有一个时钟输入,下降沿数据由输入时钟的反相时钟控制。

ODDR支持两种操作模式:OPPOSITE_EDGE模式和SAME_EDGE模式。

SAME_EDGE模式允许在ODDR时钟的上升沿将两个数据送至ODDR,以节省CLB和时钟资源并提高性能。

OPPOSITE_EDGE模式使用时钟的两个沿以两倍吞吐量从FPGA内部采集数据,两个输出都送至IOB 的数据输入或三态控制输入。

图5-30所示为使用OPPPOSITE_EDGE模式时输出DDR的时序图。

图5-31所示为使用SAME_EDGE模式时输出DDR的时序图。

图5-30 OPPPOSITE_EDGE模式时输出DDR图5-31 SAME_EDGE模式时输出DDR输出ODDR可以将时钟的一个副本传送到输出。

将ODDR原语的D1固定为High,D2固定为Low,时钟与数据ODDR的时钟一样。

这个方案可以确保输出数据与输出时钟延时的一致性。

三、SelectIO的高级特性除了SelectIO的电器特性和专用于收发SDR或DDR数据的寄存器结构之外,Virtex-6还提供了更高级的逻辑特性。

其中包含串并转换器ISERDES、并串转换器OSERDES和Bitslip。

(1) ISERDES。

Virtex-6 ISERDES是专用的串并转换器,具有专门实现高速源同步应用的时钟控制与逻辑功能。

图5-32为ISERDES的结构图,其中包括串并转换器(ISERDES)、Bitslip子模块,以及对选通存储器接口的支持,如网络接口、DDR3接口和QDR接口。

图5-32 ISERDES结构图输入串并转换器。

ISERDES解串器可以实现高速数据传输,不要求FPGA内部资源与输入数据频率匹配。

此转换器支持SDR和DDR。

在SDR模式下,串并转换器可以实现2、3、4、5、6、7或8bit宽的并行字。

在DDR模式下,串并转换器可以实现4、6、8或10位宽的并行字。

ISERDES的原语ISERDES1如图5-33所示。

图5-33 ISERDES的原语ISERDES1Bitslip模块。

Virtex-6器件中的所有ISERDES模块都包含一个Bitslip子模块。

这个子模块可在源同步网络型应用中实现字对齐。

Bitslip对ISERDES模块中的并行数据重新排序,以便将解串器所接收重复串行模式的每种组合都送至FPGA内部逻辑。

这种重复串行模式通常称为培训模式(许多网络和电信标准都支持培训模式)。

Bitslip操作通过将ISERDES模块的Bitslip引脚置为有效,可以在并行侧对输入串行数据流重新排序。

此操作重复进行,直到找到训练模型。

图5-34 中所示为SDR 和DDR 模式下Bitslip 操作的效果。

为了便于说明,采用了八位数据宽度。

Bitslip 操作与CLKDIV 同步。

在SDR 模式下,每次Bitslip 操作使输出模式左移一位。

在DDR 模式下,每次Bitslip操作使输出模式在右移一位和左移三位之间交替变化。

在此示例中,输出模式在第八次Bitslip 操作时还原到初始模式。

这里假定串行数据是八位重复模式。

图5-34 Bitslip 操作使用Bitslip 子模块的指导原则如下。