EN29SL800B-70KI中文资料(Eon Silicon)中文数据手册「EasyDatasheet - 矽搜」

Eon Silicon Solution IC产品顶部标记说明书

PurposeEon Silicon Solution Inc. (hereinafter called “Eon”) is going to provide its products’ top marking on ICs with < cFeon > from January 1st, 2009, and without any change of the part number and the compositions of the ICs. Eon is still keeping the promise of quality for all the products with the same as that of Eon delivered before. Please be advised with the change and appreciate your kindly cooperation and fully support Eon’s product family.Eon products’ New Top MarkingcFeon Top Marking Example:Continuity of SpecificationsThere is no change to this data sheet as a result of offering the device as an Eon product. Any changes that have been made are the result of normal data sheet improvement and are noted in the document revision summary, where supported. Future routine revisions will occur when appropriate, and changes will be noted in a revision summary.Continuity of Ordering Part NumbersEon continues to support existing part numbers beginning with “Eon” and “cFeon” topmarking. To order these products, during the transition please specify “Eon top marking” or “cFeon top marking” on your purchasing orders.For More InformationPlease contact your local sales office for additional information about Eon memory solutions.Distinctive Characteristics MCP Features■Power supply voltage of 2.7 V to 3.3V ■High performance- 70 ns■Package- 7 x 9 x 1.2mm 56 ball FBGA ■Operating Temperature - 25°C to +85°CGeneral DescriptionThe EN71GL series is a product line of stacked Multi-Chip Product (MCP) packages and consists of:■ EN29GL128 (Page mode) Flash memory with lowest address sector protected.■Pseudo SRAM.For detailed specifications, please refer to the individual datasheets listed in the following table.Device DocumentNOR Flash EN29GL128Pseudo SRAM ENPSL32Product Selector Guide128Mb Flash MemoryDevice-Model#EN71GL128B0pSRAM density32M pSRAMFlash Access time 70ns pSRAM Access time 70nsPage read Access time25ns pSRAM Page read Accesstime25nsPackage56 FBGAMCP Block DiagramConnection DiagramMCP Flash-only Addresses Shared Addresses EN71GL128B0 A22, A21 A20 – A0Pin DescriptionSignal Description A22–A0 23 Address Inputs (Common)DQ15–DQ0 16 Data Inputs/Outputs (Common)CE1#f Chip Enable 1 (Flash)CE1#ps Chip Enable 1 (pSRAM)CE2ps Chip Enable 2 (pSRAM)OE# Output Enable (Common)WE# Write Enable (Common)RY/BY# Ready/Busy Output (Flash)UB# Upper Byte Control (pSRAM)LB# Lower Byte Control (pSRAM)RESET# Hardware Reset Pin, Active Low (Flash)WP#/ACC Hardware Write Protect/Acceleration Pin (Flash)V CC f Flash 3.0 volt-only single power supplyV CC ps pSRAM Power SupplyV SS Device Ground (Common)NC Pin Not Connected InternallyLogic SymbolORDERING INFORMATIONEN71GL128 B0 ―70 C W PPACKAGING CONTENT(Blank) = ConventionalP = Pb FreeTEMPERATURE RANGEW = Wireless (-25°C to +85°C)PACKAGEC =56-Ball Fine Pitch Ball Grid Array (FBGA)0.80mm pitch, 7mm x 9mm packageSPEED70 = 70nspSRAM densityB0 = 32M pSRAMBASE PART NUMBEREN = Eon Silicon Solution Inc.71GL = Multi-chip Product (MCP)3.0V Page Mode Flash Memory and RAM128 = 128 Megabit (8M x 16)PACKAGE MECHANICAL56-ball Fine-Pitch Ball Grid Array (FBGA) 7 x 9 mm Package, pitch: 0.8mm, ball: 0.4mmNote : Controlling dimensions are in millimeters (mm).Revisions ListRevision No Description DateA Initial Release 2009/05/27B Update EN29GL128 (Page mode) Flash memory with lowest address sector2009/11/23 protected on page 2.。

EN29LV640L-90TIP资料

FEATURES• Single power supply operation- Full voltage range: 2.7 to 3.6 volts for read, erase and program operations• Low power cons umption (typical values at 5 MHz)- 9 mA typical active read current- 20 mA typical program/erase current- Less than 1 μA current in standby or automatic sleep mode.• JEDEC standards compatible- Pinout and software compatible with single-power supply Flash standard• Manufactured on 0.18μm process technology• Flexible Sector Architecture:- One hundred and twenty-eight 32K-Word /64K-byte sectors.• Minimum 100K program/erase endurance cycles.• High performance for program and erase - Word program time: 8µs typical - Sector Erase time: 500ms typical - Chip Erase time: 64s typical • Package Options - 48-pin TSOP - 48-ball FBGASoftware features: • Sector Group Protection- Provide locking of sectors to prevent program or erase operations within individual sectors - Additionally, temporary Sector GroupUnprotect allows code changes in previously protected sectors. • Standard DATA# polling and toggle bits feature• Unlock Bypass Program command supported • Sector Erase Suspend / Resume modes: Read and program another Sector during Sector Erase Suspend Mode• Support JEDEC Common Flash Interface (CFI).Hardware features:• Pin compatible to lower density, easy replacement for code expansion. • RESET# hardware reset pin- Hardware method to reset the device to read mode. • WP#/ACC input pin- Write Protect (WP#) function allowsprotection of first or last 32K-word sector, regardless of previous sector protect status - Acceleration (ACC) function provides accelerated program timesGENERAL DESCRIPTIONThe EN29LV640H/L / EN29LV640U is a 64-Megabit ( 4Mx16 ), electrically erasable, read/write non-volatile flash memory. Any word can be programmed typically in 8µs. This device is entirely command set compatible with the JEDEC single-power-supply Flash standard.The EN29LV640H/L / EN29LV640U is designed to allow either single Sector or full Chip erase operation, where each Sector Group can be protected against program/erase operations or temporarily unprotected to erase or program. The device can sustain a minimum of 100K program/erase cycles on each Sector.EN29LV640 64 Megabit (4M x 16-bit ) CMOS 3.0 Volt-only, Uniform Sector Flash MemoryPRODUCT SELECTOR GUIDEProduct Number EN29LV640H/LEN29LV640USpeed OptionFull Voltage Range: V CC =2.7 – 3.6 V90 90 Max Access Time (ns) 90 90 Max CE# Access Time (ns) 90 90 Max OE# Access Time (ns) 3535BLOCK DIAGRAMWE# CE# OE#State ControlCommand RegisterErase Voltage GeneratorInput/Output BuffersProgram Voltage GeneratorChip Enable Output EnableLogicData LatchY-Decoder X-Decoder Y-GatingCell MatrixTimerV CC DetectorA21-A0V CC V SS DQ15-DQ0Address LatchSector Protect SwitchesSTBSTBWP#/ ACC RY/BY#RESET#CONNECTION DIAGRAMSTABLE 1. PIN DESCRIPTIONLOGIC DIAGRAMDQ15 – DQ0A21 – A0WE#CE#RY/BY#OE#RESET#WP# / ACCPin Name Function A21-A0 22 Address inputs DQ15-DQ0 16 Data Inputs/Outputs CE# Chip Enable Input OE# Output Enable Input WE#Write Enable InputWP#/ACC Write Protect / Acceleration Pin RY/BY# Ready/Busy status output RESET# Hardware Reset Input Pin V cc Supply Voltage (2.7-3.6V) V ss GroundNCNot Connected to anythingORDERING INFORMATIONEN29LV640 H ─90 T C PPACKAGING CONTENT(Blank) = ConventionalP = Pb FreeTEMPERATURE RANGEI = Industrial (-40°C to +85°C)C = Commercial (0°C to +70°C)PACKAGET = 48-pin TSOPB = 48-Ball Fine Pitch Ball Grid Array (FBGA)0.80mm pitchSPEED OPTIONSee Product Selector Guide and Valid CombinationsSECTOR for WRITE PROTECT (WP#/ACC=0)H=highestaddresssectorprotectedL=lowestaddresssectorprotectedBASE PART NUMBEREN29LV640 / EN29LV640U64 Megabit(4M x 16-Bit) Uniform Sector Flash3V Read, Erase and ProgramPRODUCT SELECTOR GUIDEValid Combinations VccEN29LV640H–90 EN29LV640L–90 TI, TCBI,BCV cc = 2.7V-3.6VTable 2. Sector (Group) Address Tables Sector GroupProtect/UnprotectSector Address Range for Sector EraseSector Group A21-A17 Sector A21A20A19A18A17A16A15Address Range(hexadecimal) SA0 0 0 0 0 0 0 0 000000–007FFFSA1 0 0 0 0 0 0 1 008000–00FFFFSA2 0 0 0 0 0 1 0 010000–017FFFSG0 00000SA3 0 0 0 0 0 1 1 018000–01FFFFSA4 0 0 0 0 1 0 0 020000–027FFFSA5 0 0 0 0 1 0 1 028000–02FFFFSA6 0 0 0 0 1 1 0 030000–037FFF SG100001SA7 0 0 0 0 1 1 1 038000–03FFFFSA8 0 0 0 1 0 0 0 040000–047FFFSA9 0 0 0 1 0 0 1 048000–04FFFFSA10 0 0 0 1 0 1 0 050000–057FFF SG200010SA11 0 0 0 1 0 1 1 058000–05FFFFSA12 0 0 0 1 1 0 0 060000–067FFFSA13 0 0 0 1 1 0 1 068000–06FFFFSA14 0 0 0 1 1 1 0 070000–077FFF SG300011SA15 0 0 0 1 1 1 1 078000–07FFFFSA16 0 0 1 0 0 0 0 080000–087FFFSA17 0 0 1 0 0 0 1 088000–08FFFFSA18 0 0 1 0 0 1 0 090000–097FFF SG4 00100SA19 0 0 1 0 0 1 1 098000–09FFFFSA20 0 0 1 0 1 0 0 0A0000–0A7FFFSA21 0 0 1 0 1 0 1 0A8000–0AFFFFSA22 0 0 1 0 1 1 0 0B0000–0B7FFF SG5 00101SA23 0 0 1 0 1 1 1 0B8000–0BFFFFSA24 0 0 1 1 0 0 0 0C0000–0C7FFFSA25 0 0 1 1 0 0 1 0C8000–0CFFFFSA26 0 0 1 1 0 1 0 0D0000–0D7FFF SG6 00110SA27 0 0 1 1 0 1 1 0D8000–0DFFFFSA28 0 0 1 1 1 0 0 0E0000–0E7FFFSA29 0 0 1 1 1 0 1 0E8000–0EFFFFSA30 0 0 1 1 1 1 0 0F0000–0F7FFF SG700111SA31 0 0 1 1 1 1 1 0F8000–0FFFFFSector Group A21-A17 Sector A21 A20A19A18A17A16A15Address Range(hexadecimal) SA32 0 1 0 0 0 0 0 100000–107FFFSA33 0 1 0 0 0 0 1 108000–10FFFFSA34 0 1 0 0 0 1 0 110000–117FFFSG8 01000SA35 0 1 0 0 0 1 1 118000–11FFFFSA36 0 1 0 0 1 0 0 120000–127FFFSA37 0 1 0 0 1 0 1 128000–12FFFFSA38 0 1 0 0 1 1 0 130000–137FFF SG9 01001SA39 0 1 0 0 1 1 1 138000–13FFFFSA40 0 1 0 1 0 0 0 140000–147FFFSA41 0 1 0 1 0 0 1 148000–14FFFFSA42 0 1 0 1 0 1 0 150000–157FFF SG10 01010SA43 0 1 0 1 0 1 1 158000–15FFFFSA44 0 1 0 1 1 0 0 160000–167FFFSA45 0 1 0 1 1 0 1 168000–16FFFFSA46 0 1 0 1 1 1 0 170000–177FFF SG11 01011SA47 0 1 0 1 1 1 1 178000–17FFFFSA48 0 1 1 0 0 0 0 180000–187FFFSA49 0 1 1 0 0 0 1 188000–18FFFFSA50 0 1 1 0 0 1 0 190000–197FFF SG12 01100SA51 0 1 1 0 0 1 1 198000–19FFFFSA52 0 1 1 0 1 0 0 1A0000–1A7FFFSA53 0 1 1 0 1 0 1 1A8000–1AFFFFSA54 0 1 1 0 1 1 0 1B0000–1B7FFF SG13 01101SA55 0 1 1 0 1 1 1 1B8000–1BFFFFSA56 0 1 1 1 0 0 0 1C0000–1C7FFFSA57 0 1 1 1 0 0 1 1C8000–1CFFFFSA58 0 1 1 1 0 1 0 1D0000–1D7FFF SG14 01110SA59 0 1 1 1 0 1 1 1D8000–1DFFFFSA60 0 1 1 1 1 0 0 1E0000–1E7FFFSA61 0 1 1 1 1 0 1 1E8000–1EFFFFSA62 0 1 1 1 1 1 0 1F0000–1F7FFF SG15 01111SA63 0 1 1 1 1 1 1 1F8000–1FFFFFSector Group A21-A17 Sector A21A20A19A18A17A16A15Address Range(hexadecimal) SA64 1 0 0 0 0 0 0 200000–207FFFSA65 1 0 0 0 0 0 1 208000–20FFFFSA66 1 0 0 0 0 1 0 210000–217FFFSG16 10000SA67 1 0 0 0 0 1 1 218000–21FFFFSA68 1 0 0 0 1 0 0 220000–227FFFSA69 1 0 0 0 1 0 1 228000–22FFFFSA70 1 0 0 0 1 1 0 230000–237FFF SG1710001SA71 1 0 0 0 1 1 1 238000–23FFFFSA72 1 0 0 1 0 0 0 240000–247FFFSA73 1 0 0 1 0 0 1 248000–24FFFFSA74 1 0 0 1 0 1 0 250000–257FFF SG1810010SA75 1 0 0 1 0 1 1 258000–25FFFFSA76 1 0 0 1 1 0 0 260000–267FFFSA77 1 0 0 1 1 0 1 268000–26FFFFSA78 1 0 0 1 1 1 0 270000–277FFF SG1910011SA79 1 0 0 1 1 1 1 278000–27FFFFSA80 1 0 1 0 0 0 0 280000–287FFFSA81 1 0 1 0 0 0 1 288000–28FFFFSA82 1 0 1 0 0 1 0 290000–297FFF SG2010100SA83 1 0 1 0 0 1 1 298000–29FFFFSA84 1 0 1 0 1 0 0 2A0000–2A7FFFSA85 1 0 1 0 1 0 1 2A8000–2AFFFFSA86 1 0 1 0 1 1 0 2B0000–2B7FFF SG2110101SA87 1 0 1 0 1 1 1 2B8000–2BFFFFSA88 1 0 1 1 0 0 0 2C0000–2C7FFFSA89 1 0 1 1 0 0 1 2C8000–2CFFFFSA90 1 0 1 1 0 1 0 2D0000–2D7FFF SG2210110SA91 1 0 1 1 0 1 1 2D8000–2DFFFFSA92 1 0 1 1 1 0 0 2E0000–2E7FFFSA93 1 0 1 1 1 0 1 2E8000–2EFFFFSA94 1 0 1 1 1 1 0 2F0000–2F7FFF SG2310111SA95 1 0 1 1 1 1 1 2F8000–2FFFFFSector Group A21-A17 Sector A21A20A19A18A17A16A15Address Range(hexadecimal) SA96 1 1 0 0 0 0 0 300000–307FFFSA97 1 1 0 0 0 0 1 308000–30FFFFSA98 1 1 0 0 0 1 0 310000–317FFFSG24 11000SA99 1 1 0 0 0 1 1 318000–31FFFFSA100 1 1 0 0 1 0 0 320000–327FFFSA101 1 1 0 0 1 0 1 328000–32FFFFSA102 1 1 0 0 1 1 0 330000–337FFF SG25 11001SA103 1 1 0 0 1 1 1 338000–33FFFFSA104 1 1 0 1 0 0 0 340000–347FFFSA105 1 1 0 1 0 0 1 348000–34FFFFSA106 1 1 0 1 0 1 0 350000–357FFF SG26 11010SA107 1 1 0 1 0 1 1 358000–35FFFFSA108 1 1 0 1 1 0 0 360000–367FFFSA109 1 1 0 1 1 0 1 368000–36FFFFSA110 1 1 0 1 1 1 0 370000–377FFF SG27 11011SA111 1 1 0 1 1 1 1 378000–37FFFFSA112 1 1 1 0 0 0 0 380000–387FFFSA113 1 1 1 0 0 0 1 388000–38FFFFSA114 1 1 1 0 0 1 0 390000–397FFF SG28 11100SA115 1 1 1 0 0 1 1 398000–39FFFFSA116 1 1 1 0 1 0 0 3A0000–3A7FFFSA117 1 1 1 0 1 0 1 3A8000–3AFFFFSA118 1 1 1 0 1 1 0 3B0000–3B7FFF SG29 11101SA119 1 1 1 0 1 1 1 3B8000–3BFFFFSA120 1 1 1 1 0 0 0 3C0000–3C7FFFSA121 1 1 1 1 0 0 1 3C8000–3CFFFFSA122 1 1 1 1 0 1 0 3D0000–3D7FFF SG30 11110SA123 1 1 1 1 0 1 1 3D8000–3DFFFFSA124 1 1 1 1 1 0 0 3E0000–3E7FFFSA125 1 1 1 1 1 0 1 3E8000–3EFFFFSA126 1 1 1 1 1 1 0 3F0000–3F7FFF SG31 11111SA127 1 1 1 1 1 1 1 3F8000–3FFFFF Note: The sizes of all sectors are 32K-word.USER MODE DEFINITIONSTABLE 3. BUS OPERATIONSOperation CE#OE#WE#RESET#WP#/ACC A21-A0DQ15-DQ0 Read LLHHL/HA IN D OUTWrite LHLH(Note1)A IN(Note 3)AcceleratedProgramL H L H V HH A IN(Note 3)CMOS Standby V cc±0.3V X X V cc±0.3VH XHigh-ZTTL Standby H X X H L / H X High-Z Output Disable L H H H L / H X High-Z Hardware Reset X X X L L / H X High-ZSector Group Protect (Note 2) L H L V ID HSA,A6=L,A1=H,A0=L(Note 3)Sector GroupUnprotect (Note 2) L H L V ID HSA,A6=H,A1=H,A0=L(Note 3)TemporarySector GroupUnprotectX X X V ID H A IN(Note 3)L=logic low= V IL, H=Logic High= V IH, V ID= V HH = 11 ± 0.5V = 10.5 ─ 11.5V, X=Don’t Care (eitherL or H, but not floating!), SA=Sector Addresses (A21-A15), D IN=Data In, D OUT=Data Out,A IN=Address InNotes:1. If the system asserts V IL on the WP# / ACC pin, the device disables program and erasefunctions in the first or last sector independent of whether those sectors were protected orunprotected; if the system asserts V IH on the WP# /ACC pin, the device reverts to whether thefirst or last sector was previously protected or unprotected. If WP# / ACC = V HH, all sectors willbe unprotected.2. Please refer to “Sector Group Protection & Unprotection”, Flowchart 6a and Flowchart 6b.3. D IN or D OUT as required by command sequence, data polling, or sector protect algorithm.Read ModeThe device is automatically set to reading array data after device power-up or hardware reset. No commands are required to retrieve data. The device is also ready to read array data after completing an Embedded Program or Embedded Erase algorithmAfter the device accepts an Sector Erase Suspend command, the device enters the Sector Erase Suspend mode. The system can read array data using the standard read timings, except that if it reads at an address within erase-suspended sectors, the device outputs status data. After completing aprogramming operation in the Sector Erase Suspend mode, the system may once again read array data with the same exception. See “Sector Erase Suspend/Resume Commands” for more additional information.The system must issue the reset command to re-enable the device for reading array data if DQ5 goes high or while in the autoselect mode. See the “Reset Command” for additional details.Output Disable ModeWhen the OE# pin is at a logic high level (V IH), the output from the device is disabled. The output pins are placed in a high impedance state.Standby ModeThe device has a CMOS-compatible standby mode, which reduces the c urrent to < 1µA (typical). It is placed in CMOS-compatible standby when the CE# pin is at V CC± 0.5. RESET# and BYTE# pin must also be at CMOS input levels. The device also has a TTL-compatible standby mode, which reduces the maximum V CC c urrent to < 1mA. It is placed in TTL-compatible standby when the CE# pin is at V IH. When in standby modes, the outputs are in a high-impedance state independent of the OE# input.Automatic Sleep ModeThe device has an automatic sleep mode, which minimizes power consumption. The devices will enter this mode automatically when the states of address bus remain stable for t acc + 30ns. ICC4 in the DC Characteristics table shows the current specification. With standard access times, the device will output new data when addresses change.Writing Command SequencesTo write a command or command sequence to program data to the device or erase data, the system has to drive WE# and CE# to V IL, and OE# to V IH.The device has an Unlock Bypass mode to facilitate faster programming. Once the device enters the Unlock Bypass mode, only two write cycles are required to program a word, instead of four.The system can also read the autoselect codes by entering the autoselect mode, which need the autoselect command sequence to be written. Please refer to the “Command Definitions” for all the available commands.Autoselect Identification ModeThe autoselect mode provides manufacturer and device identification, and sector protection verification, through identifier codes output on DQ15–DQ0. This mode is primarily intended for programming equipment to automatically match a device to be programmed with its corresponding programming algorithm. However, the autoselect codes can also be accessed in-system through the command register.When using programming equipment, the autoselect mode requires V ID(10.5 V to 11.5 V) on address pin A9. Address pins A6, A1, and A0 must be as shown in Autoselect Codes table. In addition, when verifying sector group protection, the sector group address must appear on the appropriate highest order address bits. Refer to the corresponding Sector Address Tables. The “Command Definitions” table shows the remaining address bits that are don’t-care. When all necessary bits have been set as required, the programming equipment may then read the corresponding identifier code on DQ15–DQ0. To access the autoselect codes in-system; the host system can issue the autoselect command via the command register, as shown in the Command Definitions table. This method does not require V ID. See“Command Definitions” for details on using the autoselect mode. Note that a Reset command is required to return to read mode when the device is in the autoselect mode.TABLE 4. Autoselect Codes (Using High Voltage, V ID )L=logic low= V IL , H=Logic High= V IH , V ID =11 ± 0.5V, X=Don’t Care (either L or H, but not floating!), SA=Sector AddressesNote:1. A8=H is recommended for Manufacturing ID check. If a manufacturing ID is read with A8=L, the chip will output a configuration code 7Fh.2. A9 = V ID is for HV A9 Autoselect mode only. A9 must be ≤ Vcc (CMOS logic level) for Command AutoselectMode.RESET#: Hardware ResetWhen RESET# is driven low for t RP , all output pins are tristates. All commands written in the internal state machine are reset to reading array data.Please refer to timing diagram for RESET# pin in “AC Characteristics”.Sector Group Protection & UnprotectionThe hardware sector group protection feature disables both program and erase operations in any sector group. The hardware chip unprotection feature re-enables both program and erase operations in previously protected sector group. A sector group consists of four adjacent sectors that would be protected at the same time. Please see Table 2 which show the organization of sector groups.There are two methods to enable this hardware protection circuitry. The first one requires only that the RESET# pin be at V ID and then standard microprocessor timings can be used to enable or disable this feature. See Flowchart 6a and 6b for the algorithm and Figure 11 for the timings.When doing Sector Group Unprotect, all the unprotected sector groups must be protected prior to any unprotect write cycle.The second method is for programming equipment. This method requires V ID to be applied to both OE# and A9 pins and non-standard microprocessor timings are used. This method is described in a separate document, the Datasheet Supplement of EN29LV640H/L ; EN29LV640U, which can be obtained by contacting a representative of Eon Silicon Solution, Inc.Description CE# OE# WE# A21toA15 A14 to A10A92A8A7A6A5 to A2A1 A0 DQ15 to DQ0H1XX1Ch Manufacturer ID: Eon L L H X X V IDLX L XL LXX7FhAutoselect Device ID L L H X X V IDX X L X L H 227Eh Sector Protection VerificationL L H SA X V IDX X L X H LXX01h(Protected)XX00h(Unprotected)Write Protect / Accelerated Program (WP# / ACC)The Write Protect function provides a hardware method to protect the first or last sector against erase and program without using V ID.When WP# is Low, the device protects the first or last sector regardless of whether these sectors were previously protected or unprotected using the method described in “Sector Group Protection & Unprotection”, Program and Erase operations in these sectors are ignored.When WP# is High, the device reverts to the previous protection status of the first or last sector. Program and Erase operations can now modify the data in those sectors unless the sector is protected using Sector Group Protection.Note that the WP# pin must not be left floating or unconnected.When WP#/ACC is raised to V HH the memory automatically enters the Unlock Bypass mode(please refer to “Command Definitions”), temporarily unprotects every protected sectors, and reduces the time required for program operation. The system would use a two-cycle program command sequence as required by the Unlock Bypass mode. When WP#/ACC returns to V IH or V IL, normal operation resumes. The transitions from V IH or V IL to V HH and from V HH to V IH or V IL must be slower than t V HH, see Figure 5. Note that the WP#/ACC pin must not be left floating or unconnected. In addition, WP#/ACC pin mustnot be at V HH for operations other than accelerated programming. It could cause the device to be damaged.Never raise this pin to V HH from any mode except Read mode, otherwise the memory may be left in an indeterminate state.A 0.1µF capacitor should be connected between the WP#/ACC pin and the VSS Ground pin to decouple the current surges from the power supply. The PCB track widths must be sufficient to carry the currents required during Unlock Bypass Program.Temporary Sector Group UnprotectThis feature allows temporary unprotection of previously protected sector groups to change data while in-system. The Temporary Sector Group Unprotect mode is activated by setting the RESET# pin to V I D. During this mode, formerly protected sector groups can be programmed or erased by simply selecting the sector group addresses. Once V I D is removed from the RESET# pin, all the previously protected sector groups are protected again. See accompanying flowchart and timing diagrams in Figure 10 for more details.StartReset#=V ID(note 1) Perform Erase or ProgramOperationsRESET#=V IH Temporary Sector Group Unprotect Completed (note 2)Notes:1. All protected sector groups are unprotected. (If WP#/ACC=V IL, the first or last sector will remain protected.)2. Previously protected sector groups are protected again.COMMON FLASH INTERFACE (CFI)The common flash interface (CFI) specification outlines device and host systems software interrogation handshake, which allows specific vendor-specified software algorithms to be used for entire families of devices. Software support can then be device-independent, JEDEC ID-independent, and forward- and backward-compatible for the specified flash device families. Flash vendors can standardize their existing interfaces for long-term compatibility.This device enters the CFI Query mode when the system writes the CFI Query command, 98h, to address 55h, any time the device is ready to read array data.The system can read CFI information at the addresses given in Tables 5-8.The upper address bits (A7–MSB) must be all zeros. To terminate reading CFI data, the system must write the reset command.The system can also write the CFI query command when the device is in the autoselect mode. The device enters the CFI query mode and the system can read CFI data at the addresses given in Tables 5–8. The system must write the reset command to return the device to the autoselect mode.Table 5. CFI Query Identification StringAddresses Data Description10h 11h 12h 0051h0052h0059hQuery Unique ASCII string “QRY”13h 14h 0002h0000hPrimary OEM Command Set15h 16h 0040h0000hAddress for Primary Extended Table17h 18h 0000h0000hAlternate OEM Command set (00h = none exists)19h 1Ah 0000h0000hAddress for Alternate OEM Extended Table (00h = none exists)Table 6. System Interface StringAddresses Data Description1Bh 0027h Vcc Min (write/erase)DQ7-DQ4: volt, DQ3 –DQ0: 100 millivolt1Ch 0036h Vcc Max (write/erase)DQ7-DQ4: volt, DQ3 –DQ0: 100 millivolt1Dh 0000h Vpp Min. voltage (00h = no Vpp pin present)1Eh 0000h Vpp Max. voltage (00h = no Vpp pin present)1Fh 0003h Typical timeout per single byte/word write 2NμS20h 0000h Typical timeout for Min, size buffer write 2NμS (00h = not supported) 21h 000Ah Typical timeout per individual block erase 2N ms22h 0000h Typical timeout for full chip erase 2N ms (00h = not supported)23h 0005h Max. timeout for byte/word write 2N times typical24h 0000h Max. timeout for buffer write 2N times typical25h 0002h Max. timeout per individual block erase 2N times typical26h 0000h Max timeout for full chip erase 2N times typical (00h = not supported)Table 7. Device Geometry DefinitionAddresses Data Description27h 0017h Device Size = 2Nbytes 28h 29h 0001h0000h Flash Device Interface description (refer to CFI publication 100)2Ah 2Bh 0000h 0000h Max. number of byte in multi-byte write = 2N (00h = not supported) 2Ch 0001h Number of Erase Block Regions within device 2Dh 2Eh 2Fh 30h 007Fh 0000h 0000h 0001h Erase Block Region 1 Information (refer to the CFI specification of CFI publication 100) 31h 32h 33h 34h 0000h 0000h0000h 0000h Erase Block Region 2 Information35h 36h 37h 38h 0000h 0000h0000h 0000h Erase Block Region 3 Information39h 3Ah 3Bh 3Ch 0000h 0000h0000h 0000hErase Block Region 4 InformationTable 8. Primary Vendor-specific Extended QueryAddresses Data Description40h 41h 42h 0050h 0052h 0049h Query-unique ASCII string “PRI” 43h 0031h Major version number, ASCII 44h 0033h Minor version number, ASCII45h 0004hAddress Sensitive Unlock0 = Required, 1 = Not Required 46h 0002hErase Suspend0 = Not Supported, 1 = To Read Only, 2 = To Read & Write 47h 0004hSector Protect0 = Not Supported, X = Number of sectors in per group 48h 0001hSector Temporary Unprotect00 = Not Supported, 01 = Supported 49h 0004h Sector Protect/Unprotect scheme01 = 29F040 mode, 02 = 29F016 mode,03 = 29F400 mode, 04 = 29LV800A mode 4Ah 0000hSimultaneous Operation00 = Not Supported, 01 = Supported 4Bh 0000hBurst Mode Type00 = Not Supported, 01 = Supported 4Ch 0000hPage Mode Type00 = Not Supported, 01 = 4 Word Page, 02 = 8 Word Page 4Dh 00A5hMinimum WP#/ACC (Acceleration) Supply Voltage00 = Not Supported, DQ7-DQ4 : Volts, DQ3-DQ0 : 100mV 4Eh 00B5hMaximum WP#/ACC (Acceleration) Supply Voltage00 = Not Supported, DQ7-DQ4 : Volts, DQ3-DQ0 : 100mV4Fh 00XXh 00h = Uniform Sector DevicesHardware Data protectionThe command sequence requirement of unlock cycles for programming or erasing provides data protection against inadvertent writes as seen in the Command Definitions table. Additionally, the following hardware data protection measures prevent accidental erasure or programming, which might otherwise be caused by false system level signals during Vcc power up and power down transitions, or from system noise.Low V CC Write InhibitWhen V CC is less than V LKO, the device does not accept any write cycles. This protects data during V CC power up and power down. The command register and all internal program/erase circuits are disabled, and the device resets. Subsequent writes are ignored until V CC is greater than V LKO. The system must provide the proper signals to the control pins to prevent unintentional writes when V CC is greater than V LKO.Write Pulse “Glitch” protectionNoise pulses of less than 5 ns (typical) on OE#, CE# or WE# do not initiate a write cycle.Logical InhibitWrite cycles are inhibited by holding any one of OE# = V IL, CE# = V IH, or WE# = V IH. To initiate a write cycle, CE# and WE# must be a logical zero while OE# is a logical one. If CE#, WE#, and OE# are all logical zero (not recommended usage), it will be considered a read.Power-up Write InhibitDuring power-up, the device automatically resets to READ mode and locks out write cycles. Even with CE# = V IL, WE#= V IL and OE# = V IH, the device will not accept commands on the rising edge of WE#.COMMAND DEFINITIONSThe operations of the device are selected by one or more commands written into the commandregister. Commands are made up of data sequences written at specific addresses via the command register. The sequences for the specified operation are defined in the Command Definitions table (Table 9). Incorrect addresses, incorrect data values or improper sequences will reset the device to Read Mode.Table 9. EN29LV640H/L / EN29LV640U Command DefinitionsBus Cycles (Note 1-2)1stCycle 2ndCycle3rdCycle4thCycle5thCycle6thCycleCommand Sequence C y c l e sAddr DataAddr DataAddr DataAddr DataAddr DataAddr DataRead (Note 3)1RA RD Reset 1xxx F0 Manufacturer ID 4555 AA 2AA 55 55590000 1007F 1CDevice ID 4555 AA 2AA 55 55590 X01 227E A u t o s e l e c tSector Protect Verify (Note 4)4555 AA 2AA 55 55590(SA)X02XX00 XX01Program 4555 AA 2AA 55 555A0 PA PD Unlock Bypass 3555 AA 2AA 55 55520 Unlock Bypass Program2XXX A0 PA PD Unlock Bypass Reset 2XXX90XXX00Chip Erase 6555 AA 2AA 55 55580 555 AA 2AA 55 55510Sector Erase 6555 AA 2AA 55 55580 555 AA 2AA 55 SA 30 Sector Erase Suspend 1BA B0 Sector Erase Resume 1BA 30 CFI Query 15598Address and Data values indicated are in hex. Unless specified, all bus cycles are write cycles RA = Read Address: address of the memory location to be read. This is a read cycle. RD = Read Data: data read from location RA during Read operation. This is a read cycle. PA = Program Address: address of the memory location to be programmed. X = Don’t-Care PD = Program Data: data to be programmed at location PASA = Sector Address: address of the Sector to be erased or verified (in Autoselect mode).Address bits A21-A15 uniquely select any Sector.Notes:1. Data bits DQ15-DQ8 are don’t care in command sequences, except for RD and PD.2. Unless otherwise noted, address bits A21-A15 are don’t cares.3. No unlock or command cycles required when device is in read mode.4. The data is 00h for an unprotected sector group and 01h for a protected sector group.。

Oeko-tex标准中文版

新版Oeko-Tex 100标准14.0 - 7.5 4.0 - 7.5 4.0 - 9.0 4.0 - 9.0 Law 112 n.d.不得检出75 300 300Sb (antimony 锑) 30.0 30.0 30.0As (arsenic 砷)0.2 1.0 1.0 1.0Pb (lead 铅 注:严禁使用铅及其合金 ) 0.2 1.0 1.0 1.0 Cd (cadmium 镉) 0.1 0.1 0.1 0.1Cr (chromium 铬) 1.0 2.0 2.0 2.0Cr(VI) 铬 (六价)定量限值:六价铬 Cr(VI)0.5ppm, 禁用的芳香胺20ppm,禁用的燃料50ppm. Co (cobalt 钴) 1.0 4.0 4.0 4.0 Cu (copper 铜) 25.0 50.050.0 50.0Ni (nickel 镍) 1.0 4.0 4.0 4.0 Hg (mercury 汞)0.02 0.02 0.02 0.02sum 总计0.5 1.0 1.0 1.0Pentachlorphenol (PCP) 0.05 0.5 0.5 0.5 2,3,5,6-Tetrachlorphenol (TeCP) 0.05 0.5 0.5 0.5DINP, DNOP, DEHP, DIDP, BBP, DBPsum 总计0.1DEHP, BBP, DBPsum 总计0.1TBT 0.5 1.0 1.0 1.0 DBT 1.0Orthophenylphenol (OPP) 邻苯基苯酚 50.0 100.0 100.0 100.0cleavable arylamines 可分解之芳胺类not used 不可使用carcinogens 致癌物not used 不可使用allergens 致敏物not used 不可使用others 其他 not used 不可使用sum 总计 1.0 1.0 1.0 1.0none 没有general 总体none 没有PBB, TRIS, TEPA, pentaBDE, octaBDE not used 不可使用to water 耐水 3 3 3 3 to acidic perspiration 耐酸性汗液 3 - 4 3 - 4 3 - 4 3 - 4 to alkaline perspiration 耐碱性汗液 3 - 4 3 - 4 3 - 4 3 - 4 to rubbing, dry 耐干摩擦 4 4 4 4 to saliva and perspiration 耐唾液和汗液fast 坚牢Formaldehyd 甲醛[50-00-0]0.1 0.1 0.1 0.1 Toluol 甲苯[108-88-3]0.1 0.1 0.1 0.1 Styrol 苯乙烯[100-42-5]0.005 0.005 0.005 0.005Vinylcyclohexen 乙烯基环乙烷[100-40-3]0.002 0.002 0.002 0.0024-Phenylcyclohexen 苯基环乙烷 [4994-16-5]0.03 0.03 0.03 0.03Butadien 丁二烯[106-99-0]0.002 0.002 0.002 0.002 Vinylchlorid[75-01-4]0.002 0.002 0.002 0.002 aromatic hydrocarbons 芳香烃0.3 0.3 0.3 0.3organic volatiles 有机挥发物0.5 0.5 0.5 0.5general 总体no abnormal odour 无异味SNV 195 651 (modified 经修改) 3 3 3 3引自Oeko-Tex。

LED灯泡能源之星标准(译文)

LED灯泡(一体成型式)能源之星标准标准适用方:各生产商及分销商最新版本修订日期:2010年3月22日标准生效日期:2010年8月31日注:以下内容中“LED灯泡(一体成型式)”简称为:LED灯泡承担的义务以下内容为能源之星合作协议的条款,涉及具有资质的LED灯泡的生产商和分销商能源之星成员必须坚持以下程序要求:●遵守现行能源之星资格标准、性能标准的定义,必须配合能源之星相关部门关于有权按照能源之星标准对产品进行第三方检测,检验合格后方可获准进行公开销售。

●遵守现行能源之星标识指南。

该指南描述了能源之星标志被如何使用。

成员必须遵循哪些准则以及确保所有相关的法定代表人,例如广告代理商、经销商、分销商都必须遵守这些准则。

●成员在申请LED灯泡认证的一年内必须至少有一款产品经检测合格或已经获得能源之星标志使用授权。

一旦上述通过,该成员即被认可。

当成员在做产品认证时,必须符合当时最新的认证标准。

●使用清晰且一一对应的带能源之星LED灯泡的标贴。

主要外包装物正面必须有能源之星证书标志,企业网站、产品目录、用户手册及技术规格参数表必须包含能源之星信息。

●成员必须每半年一次向能源之星组委会提供最新产品样本,并更新产品内容,包含任何产品的修改、检测数据的修改、产品型号或销售代码的变更、以及该产品将在一定时间内逐步终止生产或淘汰。

在此基础上,成员资格才可以被保持。

●如有任何供应商变化,包括新设备、新型号、新包装的信息变更,必须在30天以内以书面或在线等方式,告知具体的变化内容。

●对于每一类产品,必须提供官方认可的检测机构出具的符合能源之星产品性能标准的检测报告。

●每一个分类产品必须提供电子版或者复印件形式的包装样式报告,只有产品性能和包装检测结果均合格,才能进入合格产品目录。

●组委会将任意抽选某一成员的产品进行第三方检测,检测相关费用由成员承担,如成员拒绝接受检测,则其成员资格将被免除。

●每半年提交一次产品出货信息,特别是符合能源之星标准产品出货的总量,信息提交时应写明以下信息:灯头类型ANSI标准外形型号全向灯:A、BT、P、PS、S、T装饰灯:B、BA、C、CA、DC、F、G定向灯:BR、ER、K、MR、PAR、R非标准的:功率数产品编号(如果有)能源之星希望成员能主动提供出货总量信息及其中能源之星产品在总数中所占品种及百分比。

2N70中文资料(Unisonic Technologies)中文数据手册「EasyDatasheet - 矽搜」

VDS=560V, V GS=10V, I D=2.0A (注1,2)

VGS = 0 V, I SD = 2.0 A

VGS = 0 V, I SD = 2.0A di / dt = 100 A /μs(注1)

功 率 M OSFET

最小典型最大单位

700

V

10 μA

100 nA

-100 nA

0.4

V/°С

2.0

4.0 V

5.0 6.3 Ω

270 350 pF 38 50 pF 5 7 pF

芯片中文手册,看全文,戳

2N70

电气特性(续)

参数

开关特性 导通延迟时间 导通上升时间 关断延迟时间 关断下降时间 总栅极电荷 栅源充 栅漏极电荷

最小典型最大单位

30 ns

80 ns

50 ns

70 ns

8.1 11 nC

1.7

nC

4.4

nC

1.4 V

2.0 A

8.0 A

260

ns

1.09

μC

芯片中文手册,看全文,戳

2N70

测试电路和波形

D.U.T.

+

V

+

-

L

R

同类型

V

作为D.U.T.

司机

* dv / dt由R控制 * I 由脉冲周期控制 * D.U.T.-测试设备

功 率 M OSFET

V

V

(驱动器)

I (D.U.T.)

V (D.U.T.)

图 . 1A峰值二极管恢复 dv / dt测试电路

期

EN29LV800BB-70BC中文资料(Eon Silicon)中文数据手册「EasyDatasheet - 矽搜」

扇区防护护: 部门,以防止编程或擦除个别行业内运

营硬件锁定 - 另外,临时机构撤消允许先

前锁定行

业代码更改.

高性能

- 存取时间快55纳秒

低功耗(在5个典型值 MHz) - 6 mA典型有效读电流 - 24 mA典型编程/擦除电流

- 1 µA 典型待机电流(标准访问

时间到主动模式)

灵活部门架构:

- 一个16字节,两个8字节,一个32字节, 十五64K字节扇区(字节模式)

RY/BY#

DQ0 – DQ15 (A-1)

芯片中文手册,看全文,戳

EN29LV800B

扇形

18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

表 2A.顶 部 引 导 块 扇 区 架 构

地址范围

(X16)

(X8)

行业

SIZE (千字节/ A18 A17 A16 A15 A14 A13 A12

K字)

7E000h-7FFFFh FC000h-FFFFFh

16/8

111111X

7D000h-7DFFFh FA000h-FBFFFh

8/4

1111101

7C000h-7CFFFh F8000h-F9FFFh

8/4

1111100

78000h-7BFFFh F0000h – F7FFFh

32/16

11 1 1 0XX

44

DQ7

43

DQ14

42

DQ6

41

DQ13

40

DQ5

39

DQ12

38

DQ4

37

Vcc

36

DQ11

35

EN29LV040A-70RSIP中文资料(Eon Silicon)中文数据手册「EasyDatasheet - 矽搜」

EN29LV040A

cFeon顶部标记示例:

cFeon

型 号 : XXXX-XXX 批 号 : XXXXX 日 期 代 码 : XXXXX

规格连续性

有没有改变此数据表作为提供设备作为Eon公司产品结果.已作出任何变化是正常数据表改善 结果,并指出在文档修订摘要,其中支持.今后日常产品更新会在适当时候改变会注意到 在修订概要发生,.

表 2.均 匀 BLOCK部 门 架 构

扇形

地址范围

扇区大小

A18

A17

A16

(千字节)

7

70000h –7FFFFh

64

1

1

1

6

60000h – 6FFFFh

64

1

1

0

5

50000h – 5FFFFh

64

1

0

1

4

40000h – 4FFFFh

64

1

0

0

3

30000h – 3FFFFh

64

0

1

1

2

20000h – 2FFFFh

OE ),芯片使能( CE ),和写使能(WE)

控制,这消除总线争用问题.该设备被设计为允许是单扇区或整片擦除操作,每个部门可以单独防

护护,防止编程/擦除操作或暂时未受防护护擦除或程序.该设备可以维持最低限度每个扇区10

0K编程/擦除周期.

芯片中文手册,看全文,戳 接线图

EN29LV040A

特征

与EN29LV040完全兼容

单电源工作

- 全电压范围:2.7-3.6伏读写 操作电池供电应用.

- 稳定电压范围:3.0-3.6伏读 操作和写操作高性能3.3伏微处理器.

EN29GL064B-70BIP中文资料(Eon Silicon)中文数据手册「EasyDatasheet - 矽搜」

图 4.逻 辑 图

A0 – A21

复位#

CE# OE# WE# Byte#

EN29GL064 RY/BY#

DQ0 – DQ15 (A-1)

芯片中文手册,看全文,戳

表 2.产 品 选 择 指 南

产品编号

速度选项

全电压范围:VCC = 2.7 - 3.6 V V =1.65 – 3.6 V

功能

A21–A0 数据输入/输出. DQ15(数据输入/输出,文字模式), A-1(LSB地址输入,字节模式)

芯片使能

输出使能

硬件复位引脚

就绪/忙输出

写使能

电源电压(2.7〜3.6V)

地面

V I / O输入. 字节/字模式选择 写防护护/加速引脚 留作将来使用.

没有连接到任何东西

初稿

EN29GL064

芯片中文手册,看全文,戳

初稿

EN29GL064

64兆位(8192K×8位/ 4096K×16位)闪存 页模式闪存,CMOS 3.0电压只有

EN29GL064

特征

单电源工作

- 全电压范围:2.7至3.6伏读

写操作

高性能

- 存取时间快70纳秒

VIO 输入/输出1.65〜3.6伏特 - 所有输入电平(地址,控制和DQ输入

A10

A11

DQ7 DQ14 DQ13

DQ6

A5

B5

C5

D5

E5

F5

G5

H5

WE# RESET# A21

A19

DQ5 DQ12

VCC

DQ4

A4

B4

C4

D4

E4

F4

G4

H4

807阻燃型单组份室温硫化硅橡胶说明书

807阻燃型单组份室温硫化硅橡胶简介:●本产品为脱醇系阻燃型单组份室温硫化硅橡胶。

特点●电子专用:本产品专为电源等电器开发的室温硫化硅橡胶粘接剂。

●抑制触点失效:公司运用独特专利技术,解决挥发性材料导致封闭式电源触点失效的问题,大大延长使用寿命。

●环保无卤阻燃:产品阻燃等级为UL 94 V-0级,完全不含有溴系等有害阻燃剂,也不含有其它氯、氟化物、重金属等有害物质,符合ROHS指令以及最新环保要求。

固化时气味小,挥发物低,固化后的产品对铜等金属没有腐蚀性,是安全环保的电子粘接材料。

●快速固化:产品表干时间短(≤30min),深层固化快,有利于快速粘接。

●本品固化后拉伸强度和拉伸剪切强度较高,对橡胶、塑料、金属等材质具有非常优异的粘接性能。

且具有优良的挠曲性以及绝缘、防潮、防震功能。

●固化物耐臭氧和紫外线、具有良好的耐候性和耐老化性能,可在-45℃-180℃条件下使用。

用途●主要适用于各类电源电子元器件产品的粘接、密封。

性能参数使用说明●通常在室温及相对湿度为30%-80%的条件下固化,在24-72小时内固化物理性能可达完全性能的90%以上。

产品不适用于高度密闭或深层固化。

●请在通风良好的工作环境下使用产品。

不慎接触眼睛和皮肤应立即冲洗、擦洗干净或由医生治疗。

●可在-45℃至180℃的温度范围内长期使用。

然而在温度范围的上下限,在材料的特殊性和表现可能变得复杂化,需要经过对您的部件或者组件进行检验才能核实。

●所粘接的表面需保持清洁,如果表面有油污残留则会影响粘接。

适宜表面清洁可获得更好的效果,用户应确定最适合工艺方法。

●对多数活性金属、陶瓷、玻璃、树脂和塑料粘接牢固,但对非活性金属或非活性塑料表面如Teflon、聚乙烯或聚丙烯等材质不具良好的粘合性。

通常,增加固化温度和固化时间会提高粘合性。

●不推荐有油污、增塑剂、溶剂等会影响固化和粘接的表面直接使用,在涂层表面使用需考虑对涂层的影响。

●本产品在使用后,应将胶管密封,可保存再次使用。

EN29LV800CB-70TI中文资料

• High performance program/erase speed - Byte/Word program time: 8µs typical - Sector erase time: 500ms typical

B3

C3

RY/BY#

NC

A18

A2

B2

C2

A7

A17

A6

A1

B1

C1

A3

A4

A2

A11 D4 NC D3 NC D2 A5 D1 A1

DQ7 E4

DQ14 F4

DQ13

DQ6

G4

H4

DQ5

DQ12

Vcc

DQ4

E3 DQ2 E2

F3 DQ10 F2

G3

H3

DQ11

DQ3

G2

H2

DQ0 E1

DQ8 F1

1 1 1 1 0XX

14

70000h-77FFFh E0000h - EFFFFh 64/32

1 11 0XXX

13

68000h-6FFFFh D0000h - DFFFFh 64/32

1 10 1XXX

12

60000h-6FFFFh C0000h - CFFFFh 64/32

1 10 0XXX

11

Kwords)

18

7E000h-7FFFFh FC000h-FFFFFh

16/8

111111X

17

7D000h-7DFFFh FA000h-FBFFFh

8/4

1111101

16

EN25B32-100QC中文资料(Eon Silicon)中文数据手册「EasyDatasheet - 矽搜」

EN25B32

32兆位串行闪存与引导和参数部门

EN25B32

特征

单电源工作

- 全电压范围:2.7-3.6伏

32 M位串行闪存 - 32 M位/ 4096 K-字节/ 16384页 - 每可编程页256字节

高性能

- 100MHz时钟频率

低功耗

- 5毫安典型工作电流

底部或顶部引导配置

16384 页(每256字节)

每一页都可以单独编程(位从1编程为0).该设备部门或 大容量可擦除而不是页面可擦除.

表2a.

底 部 引 导 块 ,部 门 架 构

扇形

扇区大小( K字节)

67

64

66

64

65

64

64

64

63

64

62

64

61

64

60

64

59

64

58

64

57

64

56

64

55

该EN25B32有68部门,包括63部门为64KB,32KB一个部门,一是 部门有16KB,8KB一个部门和4KB两个部门.此装置被设计成允许或者单 部门在同一时间或整片擦除操作.该EN25B32可以防护护存储在任一顶部或底部启动配置中小部门引 导代码.该设备可以维持最低限度每个扇区100K编程/擦除周期.

串 行 数 据 输 出 ( DO)

SPI串行数据输出(DO)引脚提供数据和状态一种手段进行串行读取(移出)器件.数据移出对串行时钟 (CLK)输入引脚下降沿.

串 行 时 钟 ( CLK)

SPI串行时钟输入(CLK)引脚提供串行输入和输出操作时机. ("见SPI 模式")

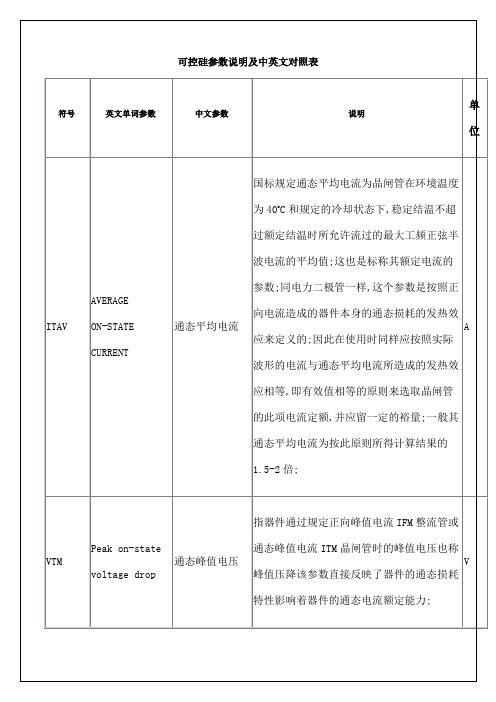

可控硅参数说明及中英文对照表

ID

Off-state leakage current

断态漏电流

-

mA

VGT

Triggering gate voltage

门极触发电压

—可以选择Vgt 25度时max值的β倍;β为门极触发电压—结温特性系数,查数据手册可得,取特性曲线中最低工作温度时的系数;若对器件工作环境温度无特殊需要,通常选择时β取1~1.2倍即可;

A

VTM

Peak on-state voltage drop

通态峰值电压

指器件通过规定正向峰值电流IFM整流管或通态峰值电流ITM晶闸管时的峰值电压也称峰值压降该参数直接反映了器件的通态损耗特性影响着器件的通态电流额定能力;

V

IDRM

Maximum forward or reverse leakage current

通态流上升率

当双向可控硅或闸流管在门极电流触发下导通,门极临近处立即导通,然后迅速扩展至整个有效面积;这迟后的时间有一个极限,即负载电流上升率的许可值;过高的dIT/dt可能导致局部烧毁,并使T1-T2 短路;假如过程中限制dIT/dt到一较低的值,双向可控硅可能可以幸存;因此,假如双向可控硅的VDRM在严重的、异常的电源瞬间过程中有可能被超出或导通时的dIT/dt有可能被超出,可在负载上串联一个几μH的不饱和空心电感;

℃

Tstg

Storage Temperature Range

贮存温度

-

℃

TL

Max.Lead Temperature for Soldering Purposes

引脚承受焊锡极限温度

-

℃

Rthj-mb

Thermal Resistance Junction tomounting base

EN29F010-70TIP中文资料

This Data Sheet may be revised by subsequent versions ©2003 Eon Silicon Solution, Inc., or modifications due to changes in technical specifications.1FEATURES• 5.0V operation for read/write/erase operations• Fast Read Access Time - 45ns, 55ns, 70ns, and 90ns• Sector Architecture:- 8 uniform sectors of 16Kbytes each - Supports full chip erase- Individual sector erase supported - Sector protection:Hardware locking of sectors to prevent program or erase operations within individual sectors• High performance program/erase speed - Byte program time: 7µs typical - Sector erase time: 300ms typical - Chip erase time: 3s typical • Low Standby Current- 1µA CMOS standby current-typical - 1mA TTL standby current • Low Power Active Current- 12mA typical active read current - 30mA program/erase current• JEDEC Standard program and erase commands• JEDEC standard DATA polling and toggle bits feature• Single Sector and Chip Erase • Sector Unprotect Mode• Embedded Erase and Program Algorithms • Erase Suspend / Resume modes:Read and program another Sector during Erase Suspend Mode• 0.23 µm triple-metal double-poly triple-well CMOS Flash Technology • Low Vcc write inhibit < 3.2V • 100K endurance cycle • Package Options - 32-pin PDIP - 32-pin PLCC- 32-pin 8mm x 20mm TSOP (Type 1) - 32-pin 8mm x 14mm TSOP (Type 1) • Commercial and Industrial Temperature RangesGENERAL DESCRIPTIONThe EN29F010 is a 1-Megabit, electrically erasable, read/write non-volatile flash memory. Organized into 128K bytes with 8 bits per byte, the 1M of memory is arranged in eight uniform sectors of 16Kbytes each. Any byte can be programmed typically in 7µs. The EN29F010 features 5.0V voltage read and write operation, with access times as fast as 45ns to eliminate the need for WAIT states in high-performance microprocessor systems.The EN29F010 has separate Output Enable (OE ), Chip Enable (CE ), and Write Enable (W E ) controls, which eliminate bus contention issues. This device is designed to allow either single Sector or full chip erase operation, where each Sector can be individually protected againstprogram/erase operations or temporarily unprotected to erase or program. The device can sustain a minimum of 100K program/erase cycles on each Sector.EN29F010 1 Megabit (128K x 8-bit) 5V Flash MemoryTABLE 1. PIN DESCRIPTIONFIGURE 1. LOGIC DIAGRAMTABLE 2. SECTOR ARCHITECTURESectorADDRESSESSIZE (Kbytes)A16 A15 A14 7 1C000h - 1FFFFh 16 1 11 618000h – 1BFFFh16115 14000h – 17FFFh 16 1 0 1 4 10000h – 13FFFh 16 1 0 0 3 0C000h – 0FFFFh 16 0 1 1 208000h – 0BFFFh1611 04000h - 07FFFh16 0 0 1 0 00000h - 03FFFh160 0 0DQ0 - DQ7VssBLOCK DIAGRAMFIGURE 2. PDIPFIGURE 3. PLCCFIGURE 4. TSOPTABLE 3. OPERATING MODES1M FLASH USER MODE TABLENOTES:1) L = V IL, H = V IH, V ID = 11.0V ± 0.5V2) X = Don’t care, either V IH or V IL3) Ax/y: Ax = Addr(x), Ay = Addr(y)TABLE 4. DEVICE IDENTIFICTION1M FLASH MANUFACTURER/DEVICE ID TABLEA8 A6 A1 A0 DQ(7-0) HEXREAD MANUFACTURER ID H(1) L L LMANUFACTURER ID1CREAD DEVICE ID X(2) L L HDEVICE ID20NOTES:1) If a Manufacturing ID is read with A8 = L, the chip will output a configuration code 7Fh. A furtherManufacturing ID must be read with A8 = H.2) X = Don’t careUSER MODE DEFINITIONSStandby ModeThe EN29F010 has a CMOS-compatible standby mode, which reduces the current to < 1µA (typical). It is placed in CMOS-compatible standby when the CE pin is at V CC± 0.5. The device also has a TTL-compatible standby mode, which reduces the maximum V CC current to < 1mA. It is placed in TTL-compatible standby when the pin is at V IH. When in standby modes, the outputs are in a high-impedance state independent of the OE input.Read ModeThe device is automatically set to reading array data after device power-up. No commands are required to retrieve data. The device is also ready to read array data after completing an Embedded Program or Embedded Erase algorithm.After the device accepts an Erase Suspend command, the device enters the Erase Suspend mode. The system can read array data using the standard read timings, except that if it reads at an address within erase-suspended sectors, the device outputs status data. After completing a programming operation in the Erase Suspend mode, the system may once again read array data with the same exception. See “Erase Suspend/Erase Resume Commands” for more information on this mode.The system must issue the reset command to re-enable the device for reading array data if DQ5 goes high, or while in the autoselect mode. See “Reset Command” section.See also “Requirements for Reading Array Data” in the “Device Bus Operations” section for more information. The Read Operations table provides the read parameters, and Read Operation Timings diagram shows the timing diagram.Output Disable ModeWhen the OE pin is at a logic high level (V IH), the output from the EN29F010 is disabled. The output pins are placed in a high impedance state.Auto Select Identification ModeThe autoselect mode provides manufacturer and device identification, and sector protection verification, through identifier codes output on DQ7–DQ0. This mode is primarily intended for programming equipment to automatically match a device to be programmed with its corresponding programming algorithm. However, the autoselect codes can also be accessed in-system through the command register.When using programming equipment, the autoselect mode requires V ID (10.5 V to 11.5 V) on address pin A9. Address pins A6, A1, and A0 must be as shown in Autoselect Codes (High Voltage Method) table. In addition, when verifying sector protection, the sector address must appear on the appropriate highest order address bits. Refer to the corresponding Sector Address Tables. The Command Definitions table shows the remaining address bits that are don’t care. When all necessary bits have been set as required, the programming equipment may then read the corresponding identifier code on DQ7–DQ0.To access the autoselect codes in-system; the host system can issue the autoselect command via the command register, as shown in the Command Definitions table. This method does not require V ID. See “Command Definitions” for details on using the autoselect mode.Reset CommandWriting the reset command to the device resets the device to reading array data. Address bits are don’t care for this command.The reset command may be written between the sequence cycles in an erase command sequence before erasing begins. This resets the device to reading array data. Once erasure begins, however, the device ignores reset commands until the operation is complete. The reset command may be written between the sequence cycles in a program command sequence before programming begins. This resets the device to reading array data (also applies to programming in Erase Suspend mode). Once programming begins, however, the device ignores reset commands until the operation is complete.The reset command may be written between the sequence cycles in an autoselect command sequence. Once in the autoselect mode, the reset command must be written to return to reading array data (also applies to autoselect during Erase Suspend).If DQ5 goes high during a program or erase operation, writing the reset command returns the device to reading array data (also applies during Erase Suspend).Write ModeProgramming is a four-bus-cycle operation. The program command sequence is initiated by writing two unlock write cycles, followed by the program set-up command. The program address and data are written next, which in turn initiate the Embedded Program algorithm. The system is not required to provide further controls or timings. The device automatically provides internally generated program pulses and verifies the programmed cell margin. Table 5 (Command Definitions) shows the address and data requirements for the byte program command sequence.When the Embedded Program algorithm is complete, the device then returns to reading array data and addresses are no longer latched. The system can determine the status of the program operation by using DQ7 or DQ6. See “Write Operation Status” for information on these status bits.Any commands written to the device during the Embedded Program Algorithm are ignored.Programming is allowed in any sequence and across sector boundaries. A bit cannot be programmed from a “0” back to a “1”. Attempting to do so may halt the operation and set DQ5 to “1”, or cause the Data# Polling algorithm to indicate the operation was successful. However, a succeeding read will show that the data is still “0”. Only erase operations can convert a “0” to a “1”.COMMAND DEFINITIONSThe operations of the EN29F010 are selected by one or more commands written into the command register to perform Read/Reset Memory, Read ID, Read Sector Protection, Program, Sector Erase, Chip Erase, Erase Suspend and Erase Resume. Commands are made up of data sequences written at specific addresses via the command register. The sequences for the specified operation are defined in the Command Table (Table 5). Incorrect addresses, incorrect data values or improper sequences will reset the device to the read mode.Table 5. EN29F010 Command Definitions1stWrite Cycle2ndWrite Cycle3rdWrite Cycle 4thWrite Cycle5thWrite Cycle6thWrite CycleCommand Sequence Read/Reset Write Cycles Req’dAddr Data Addr DataAddr DataAddr Data Addr Data AddrDataRead 1 RA RDReset 1 XXXh F0hRead/Reset 4 555h AAh 2AAh 55h 555h F0h RA RD AutoSelect Manufacturer ID 4 555h AAh 2AAh 55h 555h 90h 000h/100h 7Fh/1ChAutoSelect Device ID 4 555h AAh 2AAh 55h 555h 90h 01h 20hAutoSelect Sector Protect Verify 4 555h AAh 2AAh 55h 555h 90h BA &02h 00h/01hByte Program 4 555h AAh 2AAh 55h 555h A0h PA PD Chip Erase 6 555h AAh 2AAh 55h 555h 80h 555h AAh 2AAh 55h 555h 10hSector Erase6 555h AAh 2AAh55h555h80h 555h AAh 2AAh 55h BA30hSector Erase Suspend 1 xxxh B0h Sector Erase Resume1 xxxh 30hNotes:RA = Read Address: address of the memory location to be read. This one is a read cycle. RD = Read Data: data read from location RA during Read operation. This one is a read cycle. PA = Program Address: address of the memory location to be programmed PD = Program Data: data to be programmed at location PABA = Sector Address: address of the Sector to be erased. Address bits A16-A14 uniquely select any Sector.The data is 00h for an unprotected sector and 01h for a protected sector.Byte Programming CommandProgramming the EN29F010 is performed on a byte-by-byte basis using a four bus-cycle operation (two unlock write cycles followed by the Program Setup command and Program Data Write cycle). When the program command is executed, no additional CPU controls or timings are necessary. An internal timer terminates the program operation automatically. Address is latched on the falling edge of CE or W E , whichever is last; data is latched on the rising edge of CE or W E , whichever is first. The program operation is completed when EN29F010 returns the equivalent data to the programmed location.Programming status may be checked by sampling data on DQ7 (DATA polling) or on DQ6 (toggle bit). Changing data from 0 to 1 requires an erase operation. When programming time limit is exceeded, DQ5 will produce a logical “1” and a Reset command can return the device to Read mode.Chip Erase CommandChip erase is a six-bus-cycle operation. The chip erase command sequence is initiated by writing two unlock cycles, followed by a set-up command. Two additional unlock write cycles are then followed by the chip erase command, which in turn invokes the Embedded Erase algorithm. The device does not require the system to preprogram prior to erase. The Embedded Erase algorithm automatically preprograms and verifies the entire memory for an all zero data pattern prior to electrical erase. The system is not required to provide any controls or timings during these operations. The Command Definitions table shows the address and data requirements for the chip erase command sequence.Any commands written to the chip during the Embedded Erase algorithm are ignored.The system can determine the status of the erase operation by using DQ7, DQ6, or DQ2. See “Write Operation Status” for information on these status bits. When the Embedded Erase algorithm is complete, the device returns to reading array data and addresses are no longer latched.Flowchart 4 illustrates the algorithm for the erase operation. See the Erase/Program Operations tables in “AC Characteristics” for parameters, and Chip/Sector Erase Operation Timings for timing waveforms. Sector Erase CommandSector erase is a six bus cycle operation. The sector erase command sequence is initiated by writing two un-lock cycles, followed by a set-up command. Two additional unlock write cycles are then followed by the address of the sector to be erased, and the sector erase command. The Command Definitions table shows the address and data requirements for the sector erase command sequence.The device does not require the system to preprogram the memory prior to erase. The Embedded Erase algorithm automatically programs and verifies the sector for an all zero data pattern prior to electrical erase. The system is not required to provide any controls or timings during these operations.This device does not support multiple sector erase commands. Sector Erase operation will commence immediately after the first 30h command is written. The first sector erase operation must finish before another sector erase command can be given.Once the sector erase operation has begun, only the Erase Suspend command is valid. All other commands are ignored.When the Embedded Erase algorithm is complete, the device returns to reading array data and addresses are no longer latched. The system can determine the status of the erase operation by using DQ7, DQ6, or DQ2. Refer to “Write Operation Status” for information on these status bits. Flowchart 4 illustrates the algorithm for the erase operation. Refer to the Erase/Program Operations tables in the “AC Characteristics” section for parameters, and to the Sector Erase Operations Timing diagram for timing waveforms.Erase Suspend / Resume CommandThe Erase Suspend command allows the system to interrupt a sector erase operation and then read data from, or program data to, any sector not selected for erasure. This command is valid only during the sector erase operation. The Erase Suspend command is ignored if written during the chip erase operation or Embedded Program algorithm. Addresses are “don’t-cares” when writing the Erase Suspend command.When the Erase Suspend command is written during a sector erase operation, the device requires a maximum of 20 µs to suspend the erase operation.After the erase operation has been suspended, the system can read array data from or program data to any sector not selected for erasure. (The device “erase suspends” all sectors selected for erasure.) Normal read and write timings and command definitions apply. Reading at any address within erase-suspended sectors produces status data on DQ7–DQ0. The system can use DQ7, or DQ6 and DQ2 together, to determine if a sector is actively erasing or is erase-suspended. See “Write Operation Status” for information on these status bits.After an erase-suspended program operation is complete, the system can once again read array data within non-suspended sectors. The system can determine the status of the program operation using the DQ7 or DQ6 status bits, just as in the standard program operation. See “Write Operation Status” for more information.The system must write the Erase Resume command (address bits are “don’t care”) to exit the erase suspend mode and continue the sector erase operation. Further writes of the Resume commandare ignored. Another Erase Suspend command can be written after the device has resumed erasing. Sector Protection/UnprotectionThe hardware sector protection feature disables both program and erase operations in any sector. The hardware sector unprotection feature re-enables both program and erase operations in previously protected sectors.Sector protection/unprotection must be implemented using programming equipment. The procedure re-quires a high voltage (V ID) on address pin A9 and the control pins. Contact Eon Silicon Solution, Inc. for an additional supplement on this feature.WRITE OPERATION STATUSDQ7DATA PollingThe EN29F010 provides DATA Polling on DQ7 to indicate to the host system the status of the embedded operations. The DATA Polling feature is active during the Byte Programming, Sector Erase, Chip Erase, and Erase Suspend. (See Table 6)When the Byte Programming is in progress, an attempt to read the device will produce the complement of the data last written to DQ7. Upon the completion of the Byte Programming, an attempt to read the device will produce the true data last written to DQ7. For the Byte Programming, DATA polling is valid after the rising edge of the fourth WE or CE pulse in the four-cycle sequence. When the embedded Erase is in progress, an attempt to read the device will produce a “0” at the DQ7 output. Upon the completion of the embedded Erase, the device will produce the “1” at the DQ7 output during the read. For Chip Erase, the DATA polling is valid after the rising edge of the sixth W E or CE pulse in the six-cycle sequence. For Sector Erase, DATA polling is valid after the last rising edge of the sector erase W E or C E pulse.DATA Polling must be performed at any address within a sector that is being programmed or erased and not a protected sector. Otherwise, DATA polling may give an inaccurate result if the address used is in a protected sector.Just prior to the completion of the embedded operations, DQ7 may change asynchronously when the output enable (OE) is low. This means that the device is driving status information on DQ7 at one instant of time and valid data at the next instant of time. Depending on when the system samples the DQ7 output, it may read the status of valid data. Even if the device has completed the embedded operations and DQ7 has a valid data, the data output on DQ0-DQ6 may be still invalid. The valid data on DQ0-DQ7 will be read on the subsequent read attempts.The flowchart for DATA Polling (DQ7) is shown on Flowchart 5. The DATA Polling (DQ7) timing diagram is shown in Figure 8.DQ6Toggle Bit IThe EN29F010 provides a “Toggle Bit” on DQ6 to indicate to the host system the status of the embedded programming and erase operations. (See Table 6)During an embedded Program or Erase operation, successive attempts to read data from the device at any address (by toggling OE or CE) will result in DQ6 toggling between “zero” and “one”. Once the embedded Program or Erase operation is complete, DQ6 will stop toggling and valid data will be read on the next successive attempts. During Byte Programming, the Toggle Bit is valid after the rising edge of the fourth WE pulse in the four-cycle sequence. For Chip Erase, the Toggle Bit is valid after the rising edge of the sixth-cycle sequence. For Sector Erase, the Toggle Bit is valid after the last rising edge of the Sector Erase W E pulse. The Toggle Bit is also active during the sector erase time-out window.In Byte Programming, if the sector being written to is protected, DQ6 will toggles for about 2 µs, then stop toggling without the data in the sector having changed. In Sector Erase or Chip Erase, if all selected sectors are protected, DQ6 will toggle for about 100 µs. The chip will then return to the read mode without changing data in all protected sectors.Toggling either CE or OE will cause DQ6 to toggle.The flowchart for the Toggle Bit (DQ6) is shown in Flowchart 6. The Toggle Bit timing diagram is shown in Figure 9.DQ5 Exceeded Timing LimitsDQ5 indicates whether the program or erase time has exceeded a specified internal pulse count limit. Under these conditions DQ5 produces a “1.” (The Toggle Bit (DQ6) should also be checked at this time to make sure that the DQ5 is not a “1” due to the device having returned to read mode.) This is a failure condition that indicates the program or erase cycle was not successfully completed. . DATA Polling (DQ7), Toggle Bit (DQ6) and Erase Toggle Bit (DQ2) still function under this condition.Setting the CE to V IH will partially power down the device under those conditions.The DQ5 failure condition may appear if the system tries to program a “1” to a location that is previously programmed to “0.” Only an erase operation can change a “0” back to a “1.” Under this condition, the device halts the operation, and when the operation has exceeded the timing limits, DQ5 produces a “1.” Under both these conditions, the system must issue the reset command to return the device to reading array data.DQ2 Erase Toggle Bit IIThe “Toggle Bit” on DQ2, when used with DQ6, indicates whether a particular sector is actively erasing (that is, the Embedded Erase algorithm is in progress), or whether that sector is erase-suspended. Toggle Bit II is valid after the rising edge of the final WE# pulse in the command sequence. DQ2 toggles when the system reads at addresses within those sectors that have been selected for erasure. (The system may use either OE# or CE# to control the read cycles.) But DQ2 cannot distinguish whether the sector is actively erasing or is erase-suspended. DQ6, by comparison, indicates whether the device is actively erasing, or is in Erase Suspend, but cannot distinguish which sectors are selected for erasure. Thus, both status bits are required for sector and mode information. Refer to Table 6 to compare outputs for DQ2 and DQ6.Flowchart 6 shows the toggle bit algorithm, and the section “DQ2: Toggle Bit” explains the algorithm. See also the “DQ6: Toggle Bit I” subsection. Refer to the Toggle Bit Timings figure for the toggle bit timing diagram. The DQ2 vs. DQ6 figure shows the differences between DQ2 and DQ6 in graphical form.Reading Toggle Bits DQ6/DQ2Refer to Flowchart 6 for the following discussion. Whenever the system initially begins reading toggle bit status, it must read DQ7–DQ0 at least twice in a row to determine whether a toggle bit is toggling. Typically, a system would note and store the value of the toggle bit after the first read. After the second read, the system would compare the new value of the toggle bit with the first. If the toggle bit is not toggling, the device has completed the program or erase operation. The system can read array data on DQ7–DQ0 on the following read cycle.However, if after the initial two read cycles, the system determines that the toggle bit is still toggling, the system also should note whether the value of DQ5 is high (see the section on DQ5). If it is, the system should then determine again whether the toggle bit is toggling, since the toggle bit may have stopped toggling just as DQ5 went high. If the toggle bit is no longer toggling, the device has successfullycompleted the program or erase operation. If it is still toggling, the device did not complete the operation successfully, and the system must write the reset command to return to reading array data.The remaining scenario is that the system initially determines that the toggle bit is toggling and DQ5 has not gone high. The system may continue to monitor the toggle bit and DQ5 through successive read cycles, determining the status as described in the previous paragraph. Alternatively, it may choose to perform other system tasks. In this case, the system must start at the beginning of the algorithm when it returns to determine the status of the operation (top of Flowchart 6).Table 6. Status Register BitsNotes:DQ7 DATA Polling: indicates the P/E status check during Program or Erase, and on completion before checking bits DQ5 for Program or Erase Success.DQ6 Toggle Bit: remains at constant level when P/E operations are complete or erase suspend is acknowledged. Successive reads output complementary data on DQ6 while programming or Erase operation are on-going.DQ5 Error Bit: set to “1” if failure in programming or eraseDQ2 Toggle Bit: indicates the Erase status and allows identification of the erased Sector.DATA PROTECTIONPower-up Write InhibitDuring power-up, the device automatically resets to READ mode and locks out write cycles. Even with CE = V IL, W E = V IL and OE = V IH, the device will not accept commands on the rising edge of W E.Low V CC Write InhibitDuring V CC power-up or power-down, the EN29F010 locks out write cycles to protect against any unintentional writes. If V CC < V LOK, the command register is disabled and all internal program or erase circuits are disabled. Under this condition, the device will reset to the READ mode. Subsequent writes will be ignored until V CC > V LKO.Write “Noise” Pulse ProtectionNoise pulses less than 5ns on OE, CE or WE will neither initiate a write cycle nor change the command register.Logical InhibitIf CE=V IH or WE=V IH, writing is inhibited. To initiate a write cycle, CE and W E must be a logical “zero”. If CE, W E, and OE are all logical zero (not recommended usage), it will be considered a write.Sector Protect and UnprotectThe hardware sector protection feature disables both program and erase operations in any sector. The hardware sector unprotection feature re-enables both program and erase operation in previously protected sectors.Sector protection/unprotection must be implemented using programming equipment. The procedure requires a high voltage (V ID) on address pin A9 and the control pins. Contact Eon Silicon Solution, Inc. for an additional supplement on this feature.EMBEDDED ALGORITHMSFlowchart 1. Embedded ProgramFlowchart 2. Embedded Program Command SequenceSee the Command Definitions section for more information.Flowchart 3. Embedded EraseFlowchart 4. Embedded Erase Command Sequence See the Command Definitions section for more information.Chip Erase Sector EraseFlowchart 5. DATA Polling AlgorithmFlowchart 6. Toggle Bit AlgorithmABSOLUTE MAXIMUM RATINGSStorage TemperaturePlastic Packages . . . . . . . . . . . . . . . –65°C to +125°CAmbient Temperaturewith Power Applied. . . . . . . . . . . . . . –55°C to +125°CVoltage with Respect to GroundV CC (Note 1) . . . . . . . . . . . . . . . . . . . . –0.5 V to 7.0 VA9, OE# (Note 2) . . . . . . . . . . . . . . . –0.5 V to 11.5 VAll other pins (Note 1) . . . . . . . . . . . . –0.5 V to Vcc+0.5VOutput Short Circuit Current (Note 3) . . . . . . . . . 200 mANotes:1. Minimum DC voltage on input or I/O pins is –0.5 V. During voltage transitions, inputs may undershootV SS to –1.0V for periods of up to 50 ns and to –2.0 V for periods of up to 20 ns. See Left Figure below.Maximum DC voltage on input and I/O pins is V CC + 0.5 V. During voltage transitions, input and I/Opins may overshoot to V CC + 2.0 V for periods up to 20 ns. See Right Figure below.2. Minimum DC input voltage on A9 pin is –0.5 V. During voltage transitions, A9 and OE# mayundershoot V SS to –1.0V for periods of up to 20 ns and to –2.0 V for periods of up to 20 ns. See LeftFigure. Maximum DC input voltage on A9 and OE# is 11.5 V which may overshoot to 12.5 V forperiods up to 20 ns.3. No more than one output shorted to ground at a time. Duration of the short circuit should not be greaterthan one second. Stresses above those listed under “Absolute Maximum Ratings” may causepermanent damage to the device. This is a stress rating only; functional operation of the device atthese or any other conditions above those indicated in the operational sections of this specification isnot implied. Exposure of the device to absolute maximum rating conditions for extended periods mayaffect device reliability.OPERATING RANGESCommercial (C) DevicesAmbient Temperature (T A ) . . . . . . . . . . . 0°C to +70°CIndustrial (I) DevicesAmbient Temperature (T A ). . . . . . . . . . -40°C to +85°CV CC Supply VoltagesV CC for ± 5% devices . . . . . . . . . . . . +4.75 V to +5.25 VV CC for ± 10% devices . . . . . . . . . . . +4.50 V to +5.50 VOperating ranges define those limits between which thefunctionality of the device is guaranteed.Maximum Negative Overshoot Maximum Positive OvershootWaveform Waveform。

维沙伊·西利康晶体管数据手册说明书