实验四 电路版图环境实验

电子线路CAD实验指导书(第4版)

实验一单管放大电路原理图设计一、实验目的1. 学习工程文件的建立,掌握用工程文件管理原理图文件。

2. 熟悉绘制电路原理图的基本步骤。

3. 掌握绘制电路图工具(Wiring Tools)的基本操作。

4. 学会原理图元件库的添加及元件的查找方法。

5. 学会对电路原理图文件进行管理,掌握原理图文件的打开、存盘、退出等基本操作。

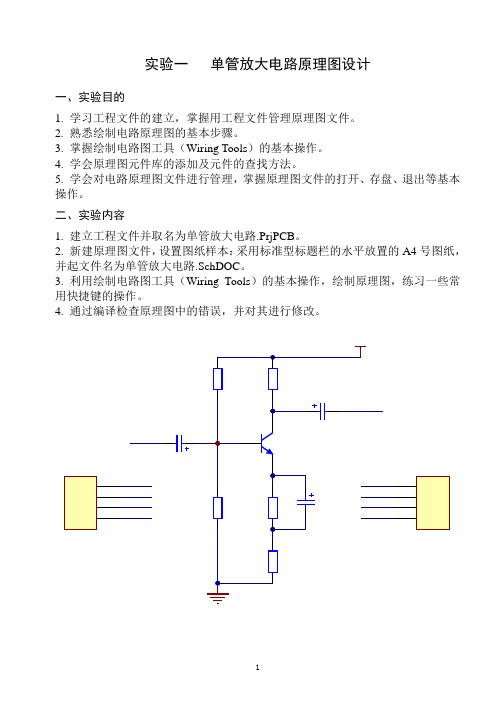

二、实验内容1. 建立工程文件并取名为单管放大电路.PrjPCB。

2. 新建原理图文件,设置图纸样本:采用标准型标题栏的水平放置的A4号图纸,并起文件名为单管放大电路.SchDOC。

3. 利用绘制电路图工具(Wiring Tools)的基本操作,绘制原理图,练习一些常用快捷键的操作。

4. 通过编译检查原理图中的错误,并对其进行修改。

实验二皮尔斯电路原理图设计一、实验目的1. 学习工程文件的建立,掌握用工程文件管理原理图文件。

2. 熟悉绘制电路原理图的基本步骤。

3. 掌握绘制电路图工具(Wiring Tools)的基本操作。

4. 学会原理图元件库的添加及元件的查找方法。

5. 学会对电路原理图文件进行管理,掌握原理图文件的打开、存盘、退出等基本操作。

二、实验内容1. 建立工程文件并取名为皮尔斯电路.PrjPCB。

2. 新建原理图文件,设置图纸样本:采用标准型标题栏的水平放置的A4号图纸,并起文件名为皮尔斯电路.SchDOC。

3. 利用绘制电路图工具(Wiring Tools)的基本操作,绘制原理图。

4. 通过编译检查原理图中的错误,并对其进行修改。

实验三电脑时控开关控制板原理图设计一、实验目的1. 学习工程文件的建立,掌握用工程文件管理原理图文件。

2. 熟悉绘制电路原理图的基本步骤。

3. 掌握绘制电路图工具(Wiring Tools)的基本操作。

4. 学会原理图元件库的添加及元件的查找方法。

5. 学会对电路原理图文件进行管理,掌握原理图文件的打开、存盘、退出等基本操作。

二、实验内容1. 建立工程文件并取名为电脑时控开关控制板.PrjPCB。

本科生课-集成电路版图设计-实验报告

西安邮电大学集成电路版图设计实验报告学号:XXX姓名:XX班级:微电子XX日期:20XX目录实验一、反相器电路的版图验证1)反相器电路2)反相器电路前仿真3)反相器电路版图说明4)反相器电路版图DRC验证5)反相器电路版图LVS验证6)反相器电路版图提取寄生参数7)反相器电路版图后仿真8)小结实验二、电阻负载共源放大器版图验证9)电阻负载共源放大器电路10)电阻负载共源放大器电路前仿真11)电阻负载共源放大器电路版图说明12)电阻负载共源放大器电路版图DRC验证13)电阻负载共源放大器电路版图LVS验证14)电阻负载共源放大器电路版图提取寄生参数15)电阻负载共源放大器电路版图后仿真16)小结实验一、反相器电路的版图验证1、反相器电路反相器电路由一个PMOS、NPOS管,输入输出端、地、电源端和SUB 端构成,其中VDD接PMOS管源端和衬底,地接NMOS管的漏端,输入端接两MOS管栅极,输出端接两MOS管漏端,SUB端单独引出,搭建好的反相器电路如图1所示。

图1 反相器原理图2、反相器电路前仿真通过工具栏的Design-Create Cellview-From Cellview将反相器电路转化为symbol,和schemetic保存在相同的cell中。

然后重新创建一个cell,插入之前创建好的反相器symbol,插入电感、电容、信号源、地等搭建一个前仿真电路,此处最好在输入输出网络上打上text,以便显示波形时方便观察,如图2所示。

图2 前仿真电路图反相器的输入端设置为方波信号,设置合适的高低电平、脉冲周期、上升时间、下降时间,将频率设置为参数变量F,选择瞬态分析,设置变量值为100KHZ,仿真时间为20u,然后进行仿真,如果仿真结果很密集而不清晰可以右键框选图形放大,如图3所示。

图3 前仿真结果3、反相器电路版图说明打开之前搭建好的反相器电路,通过Tools-Design Synthesis-Laout XL新建一个同cell目录下的Laout文件,在原理图上选中两个MOS管后在Laout中选择Create-Pick From Schematic从原理图中调入两个器件的版图模型。

电子电路CAD实验指导书正文

表 2-1 CPU Clock 电路原理图元件明细表

Footprint AXIAL0.4 AXIAL0.4

RAD0.2 XTAL1 DIP14

-4-

(2) 绘制电路原理图如图 2-2 所示。

R1 1K

Q5 A

PNP

电子电路 CAD 实验指导书

Q2 NPN

R6 47 R8 4 70 Q4 PNP

Q6

二、实验内容

(1) 绘制电路原路图 CPU Clock 如图 2-1 所示。

XTAL1

R1 470R

4.00 MHz R2 470R

U9A

U9B

C10

1

2

3

4

74LS04

0.1uF

74LS04

U9C

5

6

74LS04

图 2-1 CPU Clock

VCC

R5 330R

C P UCLK

Lif Ref

Designator

PNP

+1. 5 V B

R3

R4

R2

R5

2 K2

47

1K

47

Q1 NPN

Q3 NPN

R7 1 00 K C1

CAP

D1 DIODE

图 2-2

-4 .5 V

注:国标的二极管一条直线贯穿,在三角形处不中断;三极管外面不再加圆。符号如下:

-5-

电子电路 CAD 实验指导书

(3) 绘制电路原理图如课本 63 页图 4.53,习题 9 所示。

管脚的长度可根据需要进行 Length 设置。

e) 设置元件属性,单击元件管理器中的 Description 按纽或选择 Tools|Description 命令,

电路原理图与电路板设计实验报告

电路原理图与电路板设计实验报告学院:班级:专业:姓名:学号:指导老师:河南工业大学实验报告专业班级姓名学号同组者姓名完成日期成绩评定实验题目:(一)原理图设计环境画原理图实验实验目的:1.熟练PROTEL99se的原理图编辑环境。

2.掌握常用管理器,菜单的使用,电气规则检查。

3.掌握元器件的调用,属性含义。

实验内容:教材:1.1,1.2,1.3,1.4环境熟悉2.1,2.2工具条对象,器件调用2.3,2.4菜单使用,元件属性修改4.2练习1---练习8实验仪器:PROTEL99se软件实验步骤:(1)放置元件:就是在元件库中找元件,然后用元件管理器的Place按钮将元件放在原理图中。

放置元件时需要使用如下所示快捷键:空格键:每单击一次空格键使元件逆时针旋转90度。

TAB键:当元件浮动时,单击TAB键就可以显示属性编辑窗口。

X键:元件水平镜像。

Y键:元件垂直镜像。

(2)连接导线。

使用划线工具连接导线。

(3)放置电源,地线和网络标记。

放置电源和地线标记前要显示电源地线工具箱。

(4)自动元件编号:使用菜单Tool/Annotate对元件自动编号。

(5)编辑元件属性。

单击元件,在弹出的属性窗口中输入元件的属性,注意一定要输入元件封装。

(6)电气规则检查。

使用Tool/ERC菜单,对画好的原理图进行电气规则检查,检查完毕后,出现报表信息,就可以进行下一步。

(7)原件图元件列表。

使用Edit/Export to Spread菜单,按照向导提示进行操作。

(8)建立网络表。

使用菜单Design/Netlist。

实验截图:注意事项:连线:从器件的端点开始到端点结束,不要多余的线,按空格旋转原件;PAGEDOWN PAGEUO缩放。

河南工业大学实验报告专业自动化班级1302 姓名张鹏涛学号同组者姓名完成日期成绩评定实验题目:(二)原理图练习实验实验目的:1.掌握层次电路图设计方法。

2.了解层次电路原理图各图之间的关系。

电路板设计实验报告

电路板设计实验报告电路板设计实验报告引言:电路板设计是电子工程师在实际应用中非常重要的一项技能。

通过设计电路板,我们可以将电子元件连接起来,实现各种功能。

本实验旨在通过实际操作,掌握电路板设计的基本原理和技巧。

一、实验目的本实验的主要目的是让学生了解电路板设计的基本流程和注意事项,培养学生的电路板设计能力和实践操作能力。

二、实验材料和设备1. 电路设计软件:本实验采用Altium Designer软件进行电路板设计。

2. 电路元件:包括电阻、电容、晶体管、集成电路等。

3. 电路板:选择合适的电路板材料和尺寸,如FR-4材料。

4. 设计工具:包括焊接工具、测试仪器等。

三、实验步骤1. 确定电路功能:首先,我们需要明确电路板的功能需求,根据需求选择合适的电路元件。

2. 绘制电路原理图:使用Altium Designer软件,根据电路功能需求,绘制电路原理图。

在绘制原理图时,需要注意元件的连接方式和引脚定义。

3. 设计电路板布局:在Altium Designer软件中,根据原理图进行电路板布局设计。

合理布局电路元件,考虑信号线的走线路径和电源线的供电路径,避免干扰和交叉干扰。

4. 进行电路布线:根据电路布局进行电路布线设计。

合理布置信号线和电源线,避免信号干扰和电源噪声。

5. 进行电路板设计规则检查:在Altium Designer软件中,进行电路板设计规则检查,确保电路板符合设计要求。

6. 生成Gerber文件:在Altium Designer软件中,生成Gerber文件,用于电路板的生产制造。

7. 制作电路板:将Gerber文件发送给电路板制造厂家,制作出实际的电路板。

8. 进行焊接和组装:将电子元件焊接到电路板上,并进行测试和调试。

四、实验结果与分析经过以上步骤,我们成功设计并制作了一块电路板。

通过测试和调试,我们验证了电路板的功能和性能。

在设计过程中,我们注意到电路布局和布线对电路性能的影响非常重要。

版图实验报告(完美版)

图 1-9 带隙基准源的电路原理图 10、完成电路图后按 X 键检查和保存,无错误后退出;

第4页

11、回到 ic6151 界面,依次选择 File->Export->CDL,弹出 CDL Out 界面,个参数如图 1-10 所பைடு நூலகம்;

第8页

实验二: 带隙基准源电路的版图设计

一、实验目的: 1、熟悉 Linux 系统基本命令并学会使用同时熟练画 layout 的一些快捷方式; 2、掌握半导体集成电路的设计规则; 3、掌握半导体集成电路的布局布线; 4、掌握使用 Cadence Virtuoso 版图编辑软件进行模拟 IC 版图布局设计; 5、掌握如何根据电路图提取网表,从而进行 LVS 检查验证; 6、学会使用 cadence 工具对所画版图进行 DRC 验证,确保版图符合工艺设计规则; 7、学会如何看 DRC 和 LVS,以便对错误进行修改。 二、实验原理和内容: 1、设计规则: (1)同层金属之间的距离是 0.6us (2)不同电位的阱间距是 4us (3)在对差分对和电流镜的匹配时,用的共质心的原则 (4)对于电流镜和差分对这类敏感模块要用 guardring (5)对于电阻要加 dummy 2、原理:Virtuoso Layout Editor 是一种基于 LINUX 系统的 EDA 工具,用于集成电路版图 设计。该工具可以进行 DRC 和 LVS 检查验证,DRC(设计规则检查)即查看所画版图是否符 合工艺设计规则,只有通过 DRC 检查,版图才能在现有工艺条件下实现;LVS(版图和电路 图一致性比较)即查看版图是否和电路图一致,只有通过 LVS 检查,版图才能在电学特性和 电路所要实现的功能上和原电路保持完全一致。本实验利用 Cadence 画出电路原理图,然 后进行检查与验证; 3、内容:首先根据已经知道的电路原理图分析其那些器件需要匹配,将匹配的器件画在一 起,分成若干个版图模块。带隙基准源大致分为:电流镜模块,分压电阻模块,差分对模块 以及剩下的单个电阻; 4、需要用到的快捷键: F2 保存 C 键 复制 F 键 满屏 M 键 移动工具 Shift+M 合并工具 K 键 标尺工具 L 键 标签工具

电路版图设计实训报告总结

电路版图设计实训报告总结实训背景电路版图设计是电子工程技术的重要环节,对于电子产品的研发和制造起着举足轻重的作用。

为了提高学生的实际操作能力,培养学生综合设计能力,我们开展了一次电路版图设计实训。

实训目的通过本次实训,旨在使学生掌握电路版图设计的基本原理、方法和技巧,培养学生的创新意识和实际动手能力,培养学生解决实际问题的能力。

实训内容本次实训主要包括以下内容:1. 电路原理图设计:通过学习电路的基本原理,学生了解了电路的图形表示方法和符号,熟悉了电路图纸上各个元件的标注和连接方式。

2. 器件选型和元件布局:根据电路设计需求,学生学会了选择相应的器件,并进行器件的布局及连线,保证电路的稳定性和可靠性。

3. PCB设计:在PCB设计软件的指导下,学生学会了将电路原理图转化为PCB布局图,布局各个元件、联线、设置电路元件的封装和尺寸等,保证了电路的良好性能。

4. PCB调试:学生通过连接电路、接通电源进行调试,检查电路的连接和工作情况,对可能存在的问题及时进行修复,确保电路的正常工作。

实训步骤本次实训分为以下几个步骤:1. 学生通过课堂学习和实际操作,了解电路版图设计的基本原理和流程。

2. 学生根据所学知识,选择一个简单的电路进行设计,包括电源、元器件、连接线等。

3. 学生使用电路设计软件,将电路原理图转化为PCB布局图,设置相关参数、布局元件、连线等。

4. 学生进行PCB布线、调试和测试,检查电路的连接和工作情况,对可能存在的问题及时进行修复。

5. 学生在指导老师的帮助下完成实训报告,总结本次实训的经验和收获。

实训收获本次实训对于学生来说是一次宝贵的机会,他们通过实际操作掌握了电路版图设计的基本原理和方法。

在实训中,学生不仅提高了自己的动手操作能力和创新意识,而且通过与同学的合作,锻炼了团队合作和沟通协调的能力。

通过本次实训,学生不仅学到了专业知识,还培养了实际操作能力,提高了自己解决实际问题的能力。

电路原理图的绘制实验报告

(2)执行菜单命令Tools | New Component(新器件),将元件名改为7426后,进入一个新Biblioteka 的编辑画面。图2-3新建元件

执行右键菜单命令【Options选项】→【Document Options文档选项】,系统弹出Library Editor Workspace对话框,设置元件库编辑器界面的样式、大小、方向、颜色等参数。这里我们可以只设置捕捉栅格尺寸,其他设置可采用默认设置。

图2-23

在接下来的对话框中封装尺寸,底部散热焊盘尺寸,倾斜间距,焊盘片设置,焊盘间距,元件公差,焊盘位置和类型设置,丝印层中封装轮廓,封装命名界面等。

图1-2新建项目文件

在弹出的“New Project”对话框中,“Name”下输入新建项目的名称,“Browse Location”按钮选择项目文件的存放路径,复选框“Create Project Folder”如果选中会自动在计算机的硬盘中新建一个文件夹,存放项目相关的所有文件。

在上图所示的“Name”编辑栏里设置名为自己班级学号姓名的文件夹和项目文件

《工程应用软件》

实验报告

学院:

专业:

班级:

姓名:

学号:

实验报告

实验一实验名称:电路原理图的绘制

姓名:实验组别:

实验日期:年月日 成绩:

一、实验目的

1. 掌握Altium Designer软件的安装、运行及卸载,掌握Altium Designer的基本操作;

2. 掌握项目文件、工程文件的创建和编辑器环境的设置,熟悉常用元件库和各主要菜单及命令的使用;

ADG609绘制完成, 定义元件属性后,放置到原理图中。

图2-13

3.完成DIP14元件封装图。(要求:用手动和向导两种方式完成。)

实验电路结构图介绍(doc 7页)

实验电路结构图介绍(doc 7页)第三节:实验电路结构图CLOCK0CLOCK2CLOCK5CLOCK9目标芯片F PG A /C P L D HEXPIO2PIO3PIO4PIO5PIO7PIO6D1D2D3D4D5D6D7D8D16D15D14D13D12D11数码1数码2数码3数码4数码5数码6数码7数码8NO.0S P E A K E R扬声器实验电路结构图译码器译码器译码器译码器译码器译码器译码器译码器PIO15-PIO12PIO11-PIO8PIO7--PIO2HEX 键1键2键3键4键5键6键7键8PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16CLOCK9CLOCK5CLOCK2CLOCK0SPEAKER扬声器NO.1PIO11-PIO8PIO15-PIO12PIO48PIO49D15D16HEX HEXPIO32PIO33PIO34PIO35PIO36PIO37PIO38PIO39D1D2D3D4D5D6D7D8实验电路结构图译码器译码器译码器译码器FPGA/CPLD 目标芯片12345678PIO3-PIO0PIO7-PIO4HEX HEX 键1键2键3键4键5键6键7键8PIO39-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16附图2 实验电路结构图NO.0 附图3 实验电路结构图NO.1附图13 GW48-CK系统的VGA和RS232引脚连接图(此两个接口与PK系列引脚不同)附图14 新GW48-PK3/CP+系统的VGA和RS232引脚连接图(此VGA接口与老式PK系列引脚不同)附图7 实验电路结构图NO.5(VGA引脚为老式PK系列和新式PK2S/4引脚)CLOCK9CLOCK5CLOCK2CLOCK0PIO8D11D12PIO9D13PIO10D14PIO11D15PIO12PIO13D16D6D5D4D3D2D1D7D8)(12345678实验电路结构图NO.6目标芯片FPGA/CPLD 扬声器S P E A K E RPIO3-PIO0PIO7-PIO4HEX HEXPIO16PIO13-PIO8PIO23PIO22PIO21PIO20PIO19PIO18PIO17直接与7段显示器相接PIO46-PIO40PIO38-PIO32PIO30-PIO24PIO22-PIO16PIO46-PIO40 接 g, f, e, d, c, b, aPIO38-PIO32 接 g, f, e, d, c, b, aPIO30-PIO24 接 g, f, e, d, c, b, a 七段PIO22-PIO16 接 g,f,e,d,c,b,a键1键2键3键4键5键6键7键8附图8 实验电路结构图NO.6 附图12 GW48-PK2上扫描显示模式时的连接方式: 8数码管扫描式显示,输入信号高电平有效D+(PIO65)D-(PIO64)GNDVCCSLAVEUSB PIO65PIO64OO O O选择开关T O F P G A T O M C U键复位接PC 机串行通讯接口接口电路235RS-232B4P27P26P25P24P23P22P21P20PSEN ALE EA P07P06P05P04P03P02P01P00VCC A T 89C 5140393837363534333231302928272625242223212019181716151413121110987654321GND X1X2PIO66PIO67PIO77PIO76PIO79PIO78P31P30RESET PIO75PIO74PIO73PIO72PIO71PIO70PIO69PIO68LCD 液晶显示屏VCC GND P22P21P20P00P01P02P03P04P05P06P07P23P241234567891011121314151617181920附图11 实验电路结构图COM (GW48-PK3上液晶与单片机以及FPGA 的I/O 口的连接方式)P82P62EP1C3目标板插座EP1C6/12目标板插座P94P91P79PIO26PIO28PIO30PIO32PIO34目标板插座22423PIO27PIO29PIO31PIO33PIO35+12V -12V 2423GND VCC VCCIO o o o o o oo o o o o o o o o o o o o o PIO26PIO28PIO30PIO32PIO342423PIO27PIO29PIO31PIO33PIO35+12V -12V P177P144P1432423GND VCC VCCIO P5P23o o o o o oo o o o o o o o o o o o o o第七节 GW48CK/PK2/PK3/PK4 系统万能接插口与结构图信号/与芯片引脚对照表结构图上的信号名GWAC6 EP1C6/12Q240Cyclone GWAC3 EP1C3TC144Cyclone GWA2C5 EP2C5TC144 CycloneIIGWA2C8 EP2C8QC208 CycloneIIGW2C35 EP2C35FBGA484C8 CycloneII WAK30/50 EP1K30/50TQ C144 ACEXGWXS200 XC3S200 SPARTANGWXS200 XC3S200 SPARTAN引脚号引脚号引脚号引脚号引脚号引脚号 引脚号引脚号PIO 0 233 1 1438 AB15 8 5 21PIO 1 234 2 144 10 AB14 9 6 22 PIO 2 235 3 3 11 AB13 10 7 24 PIO 3 236 4 4 12 AB12 12 8 26 PIO 237 5 7 13 AA20 13 10 27PIO239 7 9 15 AA18 18 12 29 6240 10 24 30 L19 19 13 31 PIO71 11 25 31 J14 20 14 33 PIO8PIO2 32 26 33 H15 21 15 34 93 33 27 34 H14 22 17 15 PIO104 34 28 35 G16 23 18 16 PIO116 35 30 37 F15 26 20 35 PIO127 36 31 39 F14 27 21 36 PIO138 37 32 40 F13 28 23 37 PIO1412 38 40 41 L18 29 24 39 PIO15PIO13 39 41 43 L17 30 25 40PIO1714 40 42 44 K22 31 26 42PIO1815 41 43 45 K21 32 27 43PIO1916 42 44 46 K18 33 28 44PIO2017 47 45 47 K17 36 30 45结构图上的信号名GWAC6EP1C6/12Q240CycloneGWAC3EP1C3TC144CycloneGWA2C5EP2C5TC144CycloneIIGWA2C8EP2C8QC208CycloneIIGW2C35EP2C35FBGA484C8CycloneIIWAK30/50EP1K30/50TQC144 ACEXGWXS200XC3S200SPARTANGWXS200XC3S200SPARTAN 引脚号引脚号引脚号引脚号引脚号引脚号引脚号引脚号PIO2118 48 47 48 J22 37 31 46PIO2219 49 48 56 J21 38 32 48PIO2320 50 51 57 J20 39 33 50PIO2421 51 52 58 J19 41 35 51PIO2541 52 53 59 J18 42 36 52PIO128 67 67 92 E11 65 76 113 26132 68 69 94 E9 67 77 114 PIO27133 69 70 95 E8 68 78 115 PIO28134 70 71 96 E7 69 79 116 PIO29PIO135 71 72 97 D11 70 80 117 30136 72 73 99 D9 72 82 119 PIO31PIO137 73 74 101 D8 73 83 120 32138 74 75 102 D7 78 84 122 PIO33139 75 76 103 C9 79 85 123 PIO34PIO140 76 79 104 H7 80 86 123 35141 77 80 105 Y7 81 87 125 PIO36PIO158 78 81 106 Y13 82 89 126 37159 83 86 107 U20 83 90 128 PIO38160 84 87 108 K20 86 92 130 PIO39161 85 92 110 C13 87 93 131 PIO40PIO162 96 93 112 C7 88 95 132 41163 97 94 113 H3 89 96 133 PIO42PIO164 98 96 114 U3 90 97 135 43165 99 97 115 P3 91 98 137 PIO44166 103 99 116 F4 92 99 138 PIO45PIO167 105 100 117 C10 95 100 139 46168 106 101 118 C16 96 102 140 PIO47PIO169 107 103 127 G20 97 103 141 48173 108 104 128 R20 98 104 143 PIO49226 131 129 201 AB16 137 130 2 PIO60225 132 132 203 AB17 138 131 3 PIO61PIO224 133 133 205 AB18 140 132 4 62223 134 134 206 AB19 141 135 5 PIO63PIO222 139 135 207 AB20 142 137 7 64219 140 136 208 AB7 143 140 9 PIO65218 141 137 3 AB8 144 141 10 PIO66PIO217 142 139 4 AB11 7 1 11 67180 122 126 145 A10 119 129 161 PIO68PIO69181 121 125 144 A9 118 123 156结构图上的信号名GWAC6EP1C6/12Q240CycloneGWAC3EP1C3TC144CycloneGWA2C5EP2C5TC144CycloneIIGWA2C8EP2C8QC208CycloneIIGW2C35EP2C35FBGA484C8CycloneIIWAK30/50EP1K30/50TQC144 ACEXGWXS200XC3S200SPARTANGWXS200XC3S200SPARTAN 引脚号引脚号引脚号引脚号引脚号引脚号引脚号引脚号PIO70182 120 122 143 A8 117 122 155PIO71183 119 121 142 A7 116 119 154PIO72184 114 120 141 A6 114 118 152PIO73185 113 119 139 A5 113 116 150PIO74186 112 118 138 A4 112 113 149PIO75187 111 115 137 A3 111 112 148PIO76216 143 141 5 AB9 11 2 12PIO77215 144 142 6 AB10 14 4 13PIO78188 110 114 135 B5 110 108 147PIO79195 109 113 134 Y10 109 107 146SPEAKER174 129 112 133 Y16 99 105 144CLO CK0 28 93 91(CLK4)23 L1 126 124 184CLO CK2 153 17 89(CLK6)132 M1 54 125 203CLO CK5 152 16 17(CLK0)131 M22 56 127 204CLO CK9 29 92 90(CLK5)130 B12 124 128 205。

电路板图环境实验

文档来源为:从网络收集整理.word版本可编辑.欢迎下载支持.

实验4电路板图环境实验

一、实验目的

1、理解电路板图与原理图之间的关系

2、理解网络表生成及其作用,网络表所包含的内容

3、掌握由原理图(网络表)生成电路板的步骤方法,错误原因及其修改

二、实验内容

1、熟悉电路板设计环境;6.1

三、实验环境

Protel99se画图环境

四、实验过程

五、实验注意事项

1、网络表的生成;原理图界面;Design----Create Netlist

2、PCB的生成:先建立PCB文件,然后在PCB界面:Design---Netlist (网络表)

封装库的添加:Add/Remove 添加Miscellaneous.ddb,

封装库的路径如下:安装目录/LIBRARY/PCB/GENERIC/FOOTPRINTS/*.DDB

六、实验心得

能自己从电路原理图到PCB图的转化,能从PCB库中添加封装,能生成网络表,熟悉了封装库的建立,添加和封装的调用。

1文档收集于互联网,如有不妥请联系删除.。

电路路板设计实验报告

电路路板设计实验报告一、实验目的本实验旨在通过对电路路板的设计和制作过程的实践,加深对电路原理和布线技巧的理解和掌握,提高实际操作能力和创新意识。

二、实验器材和软件2.1 实验器材- 电路模拟软件:Proteus- 个人电脑及相应接口- PCB制作设备:电镀设备、刻蚀设备、铜箔基板等2.2 实验软件- 电路设计软件:CADENCE- PCB设计软件:EAGLE三、实验内容本次实验设计的是一个数字时钟电路,主要包括时钟显示电路、控制电路和电源电路。

3.1 时钟显示电路设计时钟显示电路采用数码管显示,使用四个共阳极的七段数码管,共用两个74LS47译码器进行驱动。

其中,四个七段数码管分别显示时、分、秒的十位和个位。

3.2 控制电路设计控制电路采用了一个16位的可编程计数器进行时序控制,并通过按钮进行手动设置时间。

3.3 电源电路设计电源电路采用变压器降压、整流、滤波和稳压四个阶段进行,保证时钟电路的工作稳定可靠。

四、实验步骤4.1 电路原理图设计根据实验需要,采用CADENCE电路设计软件,按照电路功能和互联关系设计电路原理图。

将时钟显示电路、控制电路和电源电路等模块按需要布局,并使用正确的电路符号代表电子元器件,连接合理的信号线。

4.2 PCB布局设计根据电路原理图进行PCB布局设计,在EAGLE PCB设计软件中创建相应的PCB文件。

将电路板上各个元器件的位置、走线、电源和地线连接等进行规划布局,保证信号线的最短路径,避免干扰和交叉干扰。

4.3 地线和电源线布线在PCB布局的基础上,进行地线和电源线的布线。

将地线和电源线与实验器材的接地和电源端子相连接,形成完整电路。

4.4 信号线布线在地线和电源线布线完成后,进行信号线的布线。

根据电路原理图上的信号线连接关系,采用最短路径原则进行布线,减小信号线的长度和阻抗。

4.5 校核和优化在布线完成后,进行校核和优化。

通过对布线结果进行分析和仿真,发现并解决可能出现的问题,优化电路设计。

电路图版图实训

实训报告学院:信息工程学院班级:微电A0901姓名:袁恬学号:0405090109指导教师:刘新王智鹏日期:2011年6月23日五.实训结果分析1.版图的布局要尽量紧密,缩小版图的面积2.画图时要注意尺寸的大小3.LVS检验未通过时,须仔细查找错误,并改正,在进行LVS校正六.实训心得通过这为期两周的实训课程,让我不再是课堂上所了解的一些皮毛,让我对版图有了一次重新的定位,原来版图设计不仅仅只是将电路图转换到版图上,关注版图是否能通过DRC、LVS的检验,还得考虑到版图的总体面积,器件的导通性及延迟等影响,这些综合因素将决定以后产品的质量及功能等在这对几个电路图的版图设计时,我并没有完全注意到布局等因素的影响,只是完全的追求是否能通过DRC、LVS的检验,这是非常不可取的。

我深深的意识到了这点的不足,如将来有机会在接触版图,我一定会从多方位的考虑,而不是一味的去为了完成目标而完成目标。

在画图过程中,尤其实在比较器comp1106的版图设计时,LVS不能通过,经过多次的修改,但最终还是没能通过,我就快放弃了,最终我有重新连线,才通过了LVS,在接下来的D触发器dff1106的版图设计时,LVS还是报错,我仔细的将电路图连线与版图进行了一一对照,也没有发现错误,正当我真的不想再看了,我同桌才发现了我的版图中缺少了两个阱,才使我的问题迎刃而解!接下来的带复位端的D触发器endff1106、一位全加器fadd1106也都出现了类似的问题,不过在遇到这些问题时,一定要冷静、沉着,慢慢的去检查错误,不然要是越慌乱可能导致版图被改得一塌糊涂,不得不重新在画。

总之,这次的实训不仅让我真正的认识了版图设计,也对它有了一些初步的认识,因为这不仅是对思维的训练,也是对我们遇事处理问题的一次考验,让我受益匪浅。

目录实训目的 (1)实训时间 (1)实训内容 (1)实训过程 (1)1.比较器comp1106 (1)2.D触发器dff1106 (4)3.带复位端的D触发器endff1106 (6)4.一位全加器fadd1106 (8)实训结果分析 (10)实训心得 (10)。

实验四电位、电压的测定及电路电位图的绘制

实验四电位、电压的测定及电路电位图的绘制一、实验目的1.验证电路中电位的相对性、电压的绝对性2. 掌握电路电位图的绘制方法二、原理说明在一个闭合电路中,各点电位的高低视所选的电位参考点的不同而变,但任意两点间的电位差(即电压)则是绝对的,它不因参考点的变动而改变。

电位图是一种平面坐标一、四两象限内的折线图。

其纵坐标为电位值,横坐标为各被测点。

要制作某一电路的电位图,先以一定的顺序对电路中各被测点编号。

以图4-1的电路为例,如图中的A~F, 并在坐标横轴上按顺序、均匀间隔标上A、B、C、D、E、F、A。

再根据测得的各点电位值,在各点所在的垂直线上描点。

用直线依次连接相邻两个电位点,即得该电路的电位图。

在电位图中,任意两个被测点的纵坐标值之差即为该两点之间的电压值。

在电路中电位参考点可任意选定。

对于不同的参考点,所绘出的电位图形是不同的,但其各点电位变化的规律却是一样的。

四、实验内容利用DGJ-03实验挂箱上的“基尔霍夫定律/叠加原理”线路,按图4-1接线。

1. 分别将两路直流稳压电源接入电路,令U1=6V,U2=12V。

(先调准输出电压值,图4-1电流插座再接入实验线路中。

)2. 以图4-1中的A点作为电位的参考点,分别测量B、C、D、E、F各点的电位值φ及相邻两点之间的电压值U AB、U BC、U CD、U DE、U EF及U FA,数据列于表中。

五、实验注意事项1.本实验线路板系多个实验通用,本次实验中不使用电流插头。

DG05上的K3应拨向330Ω侧,三个故障按键均不得按下。

2. 测量电位时,用指针式万用表的直流电压档或用数字直流电压表测量时,用负表棒(黑色)接参考电位点,用正表棒(红色)接被测各点。

若指针正向偏转或数显表显示正值,则表明该点电位为正(即高于参考点电位);若指针反向偏转或数显表显示负值,此时应调换万用表的表棒,然后读出数值,此时在电位值之前应加一负号(表明该点电位低于参考点电位)。

模拟集成电路实验实验四报告

单级电流源负载共源放大器设计集成电路设计与分析实验B(四)一、实验目的1.熟练掌握使用Cadence Virtuoso ADE5.1.41软件进行原理图的编辑2.使用器件设计参数表格的数据进行电路设计3.掌握电流源负载的共源放大器的设计方法二、实验软件:Cadence IC Virtuoso ADE 5.1.41三、实验要求:实验前请做好预习工作,实验后请做好练习,较熟练地使用Virtuoso软件对原理图进行编辑并熟练掌握常用的几种低频模拟电路的分析方法。

华侨大学电子工程系(The Department of Electronic Engineering Huaqiao University)1单级电流源负载共源放大器设计华侨大学电子工程系(The Department of Electronic Engineering Huaqiao University )2 第一部分 单级共源放大器设计已知:VDD=3.3V , I=100uA 要求:Av>30dB , 输出摆幅>2V1.1 单级共源放大器设计一、参数估算1.根据输出摆幅的要求,分配NMOS 和PMOS 的过驱动电压,电路如图1所示,1.30.35,0.5onN onP onP V V V V V V +<⇒==onN 可以取V2.估算共源放大器增益111211(||)()()v mN oN oP G thN n p onN n p I A g r r V V I V λλλλ===-++由此可知,电流源负载的共源放大器小信号增益只和过驱动电压和放大级的沟道长度调制系数有关,选择合理的过驱动电压和沟道长度调制系数使其满足设计要求。

选择的输入管的过驱动电压为0.35V ,L 取1um 时即可满足设计要求。

2.估算静态工作电压:共源放大器的输入电压0.350.350.550.9G thN V V =+=+=3.30.50.75 2.05Vbp =--=单级电流源负载共源放大器设计华侨大学电子工程系(The Department of Electronic Engineering Huaqiao University )3 输出节点的静态工作点(0.35 2.8)/2 1.575+= 3.验证增益是否满足设计要求:查表1.2可知,此时NMOS 的0.03n λ=,PMOS 0.11p λ=2200/0.35571/mN onNIg uA V uA V V === 11171.4()(0.030.11)100out n p D R k I V uAλλ-===Ω++⨯ 571/71.440.7v m out A g R uA V k ==⨯Ω=4.估算器件宽长比,查表1可知:92,43n p K K ==221(/)/()100/(920.35)8.8799/1MN n onN W L I K V u u =⨯=⨯=≈=221(/)/()100/(430.5)9.39.59.5/1MP p onP W L I K V u u =⨯=⨯=≈=二、仿真验证:1.静态工作点仿真结果如图所示,仿真结果显示单级电流源负载共源放大器设计华侨大学电子工程系(The Department of Electronic Engineering Huaqiao University )4 2.输出电压摆幅仿真结果如图所示:设置仿真时不需要从0扫到VDD ,只需要在静态工作点附近3.跨导m GSdIg dV,所以可以先扫描出I-VG 曲线然后在Tools 中选择Calculator …工具(计算器)点击wave 然后在显示的波形中选择你需要进行数学处理的曲线,如 选择后计算器中会有显示如本例中(IS(“M0/D ””/home/hww/…”))接着对该曲线进行处理,需要对其微分,在计算器中Special Functions 下拉菜单中选择Deriv单级电流源负载共源放大器设计华侨大学电子工程系(The Department of Electronic Engineering Huaqiao University )5 选择完成后,最终需要将其显示出来: 在ADE 中OUTPUTs 选择Setup …选择Get Expression选择OK 后,该波形将进行数学处理显示出来: 点击Plot Outputs 将显示处理完的波形,如下所示:输入为900mV 时跨导约为320uA/V 。

集成电路版图或非门的版图实验

或非门版图实验

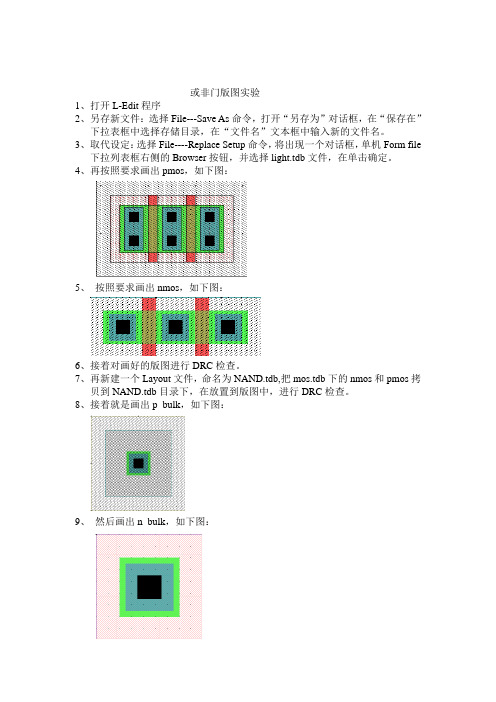

1、打开L-Edit程序

2、另存新文件:选择File---Save As命令,打开“另存为”对话框,在“保存在”

下拉表框中选择存储目录,在“文件名”文本框中输入新的文件名。

3、取代设定:选择File----Replace Setup命令,将出现一个对话框,单机Form file

下拉列表框右侧的Browser按钮,并选择light.tdb文件,在单击确定。

4、再按照要求画出pmos,如下图:

5、按照要求画出nmos,如下图:

6、接着对画好的版图进行DRC检查。

7、再新建一个Layout文件,命名为NAND.tdb,把mos.tdb下的nmos和pmos拷

贝到NAND.tdb目录下,在放置到版图中,进行DRC检查。

8、接着就是画出p_bulk,如下图:

9、然后画出n_bulk,如下图:

10、然后把各部分放到一张版图上,进行连接,然后进行DRC检查,如下图:

11、然后将图导出,生成网表文件,接着用T-spice打开,进行模拟。

对模拟

的量添加命令,如下:

.include "E:\Program Files\Tanner\tanner\TSpice70\models\ml2_125.md"

.tran/op 2n 80n method=bdf

.print tran v(A) v(B) v(Y)

vdc1 Vdd GND 5

vpulse1 A GND PULSE (0 5 0 2n 2n 8n 20n)

vpulse2 B GND PULSE (0 5 0 4n 4n 16n 40n)

仿真波形图如下:。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验四电路板图环境实验

姓名:张延庆学号:201223030222班级:测控1202班专业:测控技术与仪器

一实验目的

(1)理解电路版图与原理图之间的关系

(2)理解网络表生成与其作用,网络表所包含的内容

(3)掌握由原理图(网络表)生成电路板图的步骤方法,错误原因以及修改

二实验内容

(1)熟悉电路板设计环境

(2)300页12.2练习1

三实验步骤

原理图的生成

(1)首先建立ddb数据库文件。

在数据库文件里面新建原理图文件,之后开始按照书本要求在编辑界面摆放相关元器件

(2)若555定时器在默认的元件库里面无法找到,可利用元件管理器中的find功能进行查询

(3)摆放好所有元件之后开始进行连线,之后进行元件的名称,相关参数以及封装类型的修改。

最终结果如下图所示

(4)电气规则检查无误之后利用design菜单下面的create netlist选项来生成网络表格,里面显示了有关这张原理图中的元件的封装,名称,参数,连接方式等。

如下图所示。

印制电路板的生成

(1)在相同文件夹下生成一个pcb 文件,双击打开,在里面的design 菜单下的load netlist 选项来加载已生成的网络表格。

(2)弹出一个对话框,若显示所有元件均正确合理,则可以进行下一步。

若显示有错误出现则根据所弹出的错误信息进行修改。

(3)修改完成之后点击execute按钮来放置远见的封装图,利用shove功能来尽心推开元件(4)在keepout layer层面来绘制电路板的边界,长为2180mil,宽为1380mil。

(5)把元件拉进所画好的矩形区域,在区域内进行人工布局。

(6)人工布局完成之后进行人工布线,最终结果如下图所示。

四实验结果

原理图

电路板图

五注意事项

网络表的生成:原理图界面:design---create netlist

Pcb的生成:先建立pcb文件,然后在pcb界面:design--netlist

封装库的添加:add/remove添加miscellaneous.ddb general ic.ddb等。