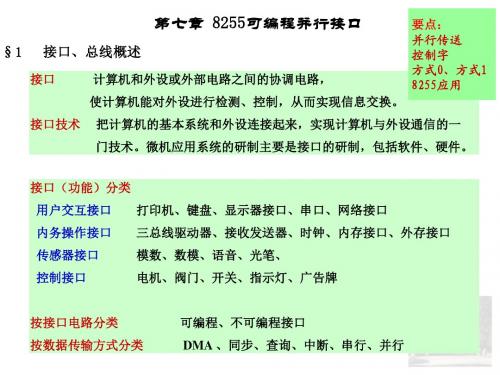

第7章 并行接口和8255芯片20101112版

第7章并行接口8255

并行接口

中断方式 :中断方式是外设主动向处理器申 请服务 。处理器工作效率高,并且能使外设 及时得到服务。(第六章的中断系统)。

DMA方式 :在存储器与外设之间开辟一条高 速数据通道,在传送过程中不需要处理器参与。 大量数据传输时效率高。(第8章)。

信息转换。I/O接口还要实现信息格式变换、 电平转换、码制转换、传送管理以及联络控制 等功能。

接口的基本功能

输入/输出(Input/Output)接口的作用: 接口是完成计算机与外界的数据交换,主

机和外部设备两者之间的同步与协调,速度的 匹配和数据格式转换的逻辑部件。它是计算机 系统的重要组成部分。

注意:再简单的接口也有地址 问题,CS为片选信号,确定地 址。

图中,一为输出、一为输入, 因此CS可以不同,也可以相同 (用同一地址)。

每一个373可接8个发光二极管,

每一个245(244)可接8个

开关。

输入输出接口扩展

CPU引脚数有限,(直接带负载能力有限)。 扩大系统的适应能力

只要适合应用目的的芯片都可以用。(注意逻辑 与电平的匹配问题。)

简单I/O输出接口--8282

简单I/O输入接口

缓冲器作为输入接口:必须具有三态输出功能。 74LS244,74 LS245 等 。 与 8286 芯 片 逻 辑 类似。

锁存器作为输入接口:带寄存器。 (74LS373,74LS374)

信号经“缓冲”后,增强驱动能力(可驱动8 个TTL芯片)。74LS244,74LS245。

ALE、IO/M、RD、WR、DT/R、DEN、(CS) (INTR、INTA)

第七章 8255接口电路

&

WR

PC3 PC4,5

&

2

PC0

③INTR 为中断请求信号,高电平有效。它是当外设将 数据取走并给出应答ACK 信号之后,8255向CPU提出中 断请求,让CPU输出一个新的数据。

&

WR

PC3 PC4,5

&

2

PC0

方式1的输出: 当A口工作于方式1且用作输出口时,C口的PC7线 用作输出缓冲器满OBF信号,PC6用作外设收到数据后 的响应信号ACK,PC3用作中断请求输出信号线INTR。 当B口工作于方式l且用作输出口时,C口的PC1线 用作输出缓冲器满OBF信号,PC2用作外设收到数据后 的响应信号ACK,PC0用作中断请求输出信号线INTR。

PA3 PA2 PA1 PA0 RD CS GND A1 A0 PC7 PC6 PC5 PC4 PC0 PC1 PC2 PC3 PB0 PB1 PB2

1

40

5 35

10 30

15 25

20

21

PA4 PA5 PA6 PA7 WR RESET D0 D1 D2 D3 D4 D5 D6 D7 VCC PB7 PB6 PB5 PB4 PB3

7.3 8255的工作方式 3种工作方式可用软件编程对控制口设置来指定。 三种基本的工作方式为: 方式0-基本的输入输出方式 方式1-选通输入输出方式 方式2-双向传送方式。 1) 工作方式0(基本输入输出方式) 功能:方式0不使用联络信号,也不使用中断,A口和B 口可定义为输入或输出口,C口分成两个部分(高四位 和低四位),C口的两个部分也可分别定义为输入或输 出。在方式0,所有口输出均有锁存,输入只有缓冲, 无锁存,C口还具有按位将其各位清0或置1的功能。常 用于与外设无条件的数据传送或接收外设的数据。

第7章可编程接口芯片3-8255

2013年8月7日

通信教研室

29

3、方式2--双向选通输入/输出方式

8位数据线与外设进行双向通信,既能发 送,也能接收(双向总线I/O)。工作时可用 程序查询方式,也可工作在中断方式。 方式2只限于A组使用,用端口C的5个信 号线进行联络,工作时,输入/输出都锁存; 当A组工作在方式2时,B组可以在方式0/1 工作

2013年8月7日

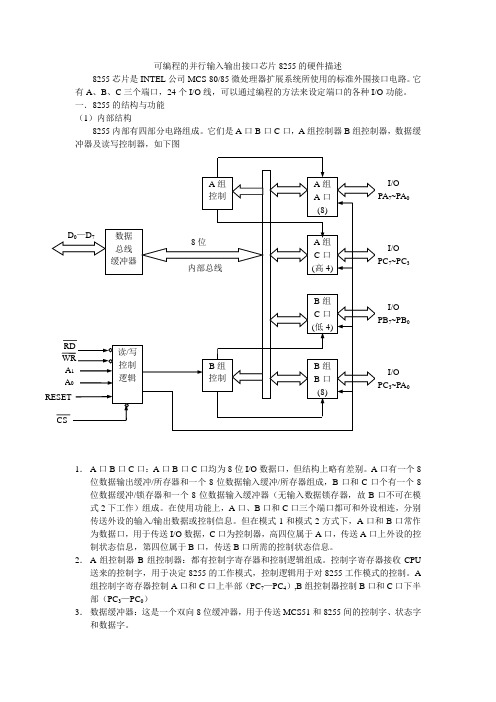

图 8255A的内部结构及外部引脚图

通信教研室

8

1)数据总线缓冲器 数据总线缓冲器为双向三态8位缓冲器,它是 8255A与微机数据总线的接口。 传输的信息有输入数据、输出数据、控制字及状态 信息 2)、读/写控制电路 读/写控制逻辑负责管理8255A的数据传输过程。 它接收片选信号CS以及来自地址总线的地址信息 A1、A0和来自控制总线的信号RESET,RD,WR, 将这些信号组合后实现对A组部件和B组部件的控 制。

INTR高电平有效 RD#下降沿清INTR,上升沿清IBF

2013年8月7日 通信教研室 23

方式1输入的中断控制

8255A输入时的中断由中断允许触发器INTE控制 置位1允许中断,复位0禁止中断 对INTE的置位/复位操作由端口C的对应位实现 端口A的INTEA对应PC4 端口B的INTEB对应PC2

2013年8月7日 通信教研室 7

8255A内部结构

A组 控制 A组 A口 (8位) PA7~PA0

D7~D0

数据 总线 缓冲器

RD WR A0 A1 CS RESET 读/写

A组 C口 (高4位)

控制

逻辑

B组 C口 (低4位)

B组 控制

B组 B口 (8位)

PA3 PA2 PA1 PA0 RD CS PC7~PC4 GND A1 A0 PC7 PC6 PC5 PC3~PC0 PC4 PC3 PC2 PC1 PC0 PB0 PB1 PB7~PB0 PB2

最新七章并行通信接口技术ppt课件

并行通信与串行通信

数据通信的基本方式可分为并行通信与串行 通信两种: 并行通信:是指利用多条数据传输线将一个 数据的各位同时传送。传输速度快,适用于 短距离通信。 串行通信:是指利用一条传输线将数据一位 位地顺序传送。通信线路简单,利用电话或 电报线路就可实现通信,降低成本,适用于 远距离通信,但传输速度慢。

INTE ——中断允许信号,高电平有效

用于控制中断允许或中断屏蔽,PC4(PC2)置1,允 许中断,PC4(PC2)置0,禁止中断

8255A方式1作输入时的各联络信号对应关系

联络信号 STB* IBF INTR INTE

端口A

对应PC4 对应PC5 对应PC3 PC4置位

端口C

对应PC2 对应PC1 对应PC0 PC2置位

适用于无条件传送和查询方式的接口电路

方式1:选通输入输出方式

适用于查询和中断方式的接口电路

方式2:双向选通传送方式

适用于与双向传送数据的外设 适用于查询和中断方式的接口电路

1.方式0

方式0的特点 (1)A口、C口的高4位、B口以及C口的低4

位可分别定义为输入或输出,各端口互相独 立,故共有16种不同的组合。 (2)定义为输出的口均有锁存数据的能力, 而定义为输入的口则无锁存能力。

状态信号可以通过读取端口C得到(P287)

8255A工作在方式1下的输入时序

端口A方式1作输出:

PA7~PA0 INTEA PC6

PC7

PC3

外设响应信号 表示外设已经接收到数据

ACKA OBFA

INTRA

输出缓冲器满信号 表示CPU已经输出了数据

中断允许触发器

中断请求信号 请求CPU再次输出数据

并行接口技术及接口芯片8255A的应用

方式1输入(端口B) INTE B

& PC0 INTRB PB7~0 PC2 PC1 D7~0 STBB IBFB

2

RD

I/O

2

STB:外设给8255A的“输入选通”信号,低电平有效。 IBF:8255A给外设的回答信号“输入缓冲器满”,高电平有效。 INTR:8255A给CPU的“中断请求”信号,高电平有效。

0

D6

D5

D4

D3

D2

D1

D0

特征 位

不 用 (写0)

位 选 择 000=C口0位 001=C口1位 … 111=C口7位

1=置位 (高电平) 0=复位 (低电平)

例2:若要把C口的PC2引脚置成高电平输出,

则命令字应该为00000101B或05H。

置位/复位命令字必须写入8255A的命令寄存器

其程序段为:MOV

code segment begin proc far assume cs:code push ds sub ax,ax push ax MOV DX,383H MOV AL,10000000B OUT DX,AL MOV AL,1 AGAIN:OUT DX,AL LOOP $ LOOP $

AND AL,0FEH OUT DX,AL ADD AL,3 AND AL,0FH PUSH AX MOV AH,11 INT 21H INC AL POP AX JNZ AGAIN ret begin endp code ends end begin

并行接口技术 及接口芯片8255A的应用

可编程并行接口

并行接口的特点:

1、在多根据数据线上以数据字节(字)为单位与I/O设备或 被控对象传送信息。 如: 打印机接口,A/D、D/A转换器接口,IEEE-488接口,

可编程的并行输入输出接口芯片8255的硬件描述

CS

A1A0

RD

WR

端口

功能

0

0 0

0

1

A口

读A口

0

0 0

1

0

A口

写A口

0

0 1

0

1

B口

读B口

0

0 1

1

0

B口

写B口

0

1 0

0

1

C口

读C口

0

1 0

1

0

C口

写C口

0

1 1

1

0

控制口

写状态字

1

ΧΧ

Χ

Χ

Χ

总线高阻

3.并行I/O总线分三组,PA7—PA0:双向I/O总线,通过状态字设定输入或输出状态,用来传输数据,也可以设定为双向口传输数据方式;PB7—PB0:双向I/O总线,通过状态字设定输入或输出状态,用来传输数据; PC7—PC0:双向数据/控制总线,用来传送I/O数据或控制/状态信息,可以设定为输入或输出方式,也可设定为控制/状态方式,有控制字决定。若8255处于模式0,则PC7—PC0位数据总线;若8255处于模式1或模式2,则PC7—PC0作为控制/状态线用。

MOVX A,@DPTR;读入PA口数据

MOV DPTR,#0001H;PB口地址为0001H

MOVX @DPTR,A;写入PB口

SJMP MAIN1

;PC口的位控方式

SETB P2.1

SETB P2.0

CLR P2.1

CLRP2.0

MAIN:MOV DPTR,#0003h

MOV A,#01h

MOVx @DPTR,A

;PA,PB模式0

并行接口芯片8255A

控制字介绍

01

02

03

控制字是用来设置8255a芯片工 作模式的16位二进制数。

控制字的格式为:XXXX XXXX XXXX XXXXXXXX。其中,最高 位是读/写控制位,中间4位是端 口C的置位/复位控制位,接下来 的4位是端口B的控制位,最后4 位是端口A的控制位。

控制字的写入顺序是先写高位, 再写低位。

03

目前,8255a芯片已经被广泛 应用于各种领域,成为计算机 和电子工程中重要的接口芯片 之一。

02 8255a芯片工作原理

芯片内部结构

ห้องสมุดไป่ตู้

01

三个并行I/O端口:端口A、端口B和端口C,每个端口都有 8个位。

02

一个控制寄存器:用于设置芯片的工作模式和控制信号的 输入。

03

一个数据总线:用于数据传输。

工作模式介绍

模式0

基本输入输出模式。在这种模式 下,端口A、B和C都可以被配置 为输入或输出模式,通过控制字 来选择。

模式1

选通I/O模式。在这种模式下,端 口A和B被配置为输出模式,端口 C被配置为输入模式。

模式2

双向I/O模式。在这种模式下,所 有三个端口都可以被配置为双向 模式,即既可以输入也可以输出。

并行接口芯片8255a

目录

CONTENTS

• 8255a芯片概述 • 8255a芯片工作原理 • 8255a芯片编程 • 8255a芯片应用实例 • 8255a芯片与其他芯片比较 • 8255a芯片未来发展展望

01 8255a芯片概述

芯片功能介绍

01

8255a是一款并行接口芯片,主要用于实现并行数据 传输和控制。

优点

支持多种游戏控制器,传输速度快, 响应速度快,提高游戏体验。

8255芯片

8255芯片8255是Intel公司生产的可编程并行I/O接口芯片,有3个8位并行I/O口。

具有3个通道3种工作方式的可编程并行接口芯片(40引脚)。

其各口功能可由软件选择,使用灵活,通用性强。

8255可作为单片机与多种外设连接时的中间接口电路。

8255作为主机与外设的连接芯片,必须提供与主机相连的3个总线接口,即数据线、地址线、控制线接口。

同时必须具有与外设连接的接口A、B、C口。

由于8255可编程,所以必须具有逻辑控制部分,因而8255内部结构分为3个部分:与CPU连接部分、与外设连接部分、控制部分。

1)与CPU连接部分根据定义,8255能并行传送8位数据,所以其数据线为8根D0~D7。

由于8255具有3个通道A、B、C,所以只要两根地址线就能寻址A、B、C口及控制寄存器,故地址线为两根A0~A1。

此外CPU要对8255进行读、写与片选操作,所以控制线为片选、复位、读、写信号。

各信号的引脚编号如下:(1)数据总线DB:编号为D0~D7,用于8255与CPU传送8位数据。

(2)地址总线AB:编号为A0~A1,用于选择A、B、C口与控制寄存器。

(3)控制总线CB:片选信号、复位信号RST、写信号、读信号。

当CPU要对8255进行读、写操作时,必须先向8255发片选信号选中8255芯片,然后发读信号或写信号对8255进行读或写数据的操作。

2)与外设接口部分根据定义,8255有3个通道A、B、C与外设连接,每个通道又有8根线与外设连接,所以8255可以用24根线与外设连接,若进行开关量控制,则8255可同时控制24路开关。

各通道的引脚编号如下:(1)A口:编号为PA0~PA7,用于8255向外设输入输出8位并行数据。

(2)B口:编号为PB0~PB7,用于8255向外设输入输出8位并行数据。

(3)C口:编号为PC0~PC7,用于8255向外设输入输出8位并行数据,当8255工作于应答I/O方式时,C口用于应答信号的通信。

8255可编程并行接口知识点总结(word文档物超所值)

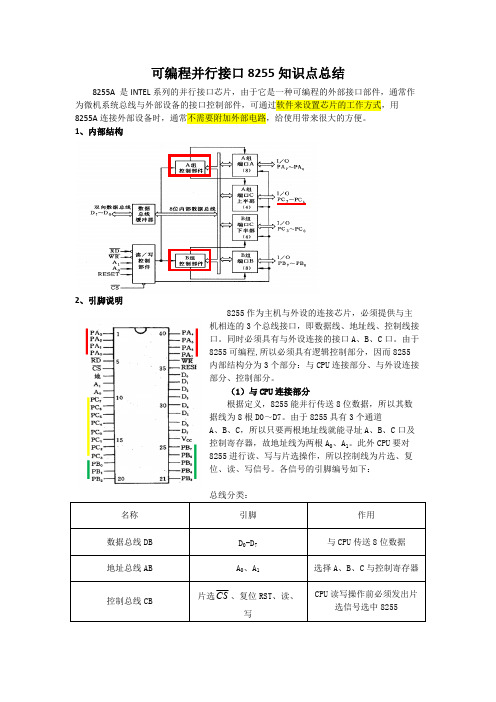

可编程并行接口8255知识点总结8255A 是INTEL 系列的并行接口芯片,由于它是一种可编程的外部接口部件,通常作为微机系统总线与外部设备的接口控制部件,可通过软件来设置芯片的工作方式,用8255A 连接外部设备时,通常不需要附加外部电路,给使用带来很大的方便。

1、内部结构2、引脚说明8255作为主机与外设的连接芯片,必须提供与主机相连的3个总线接口,即数据线、地址线、控制线接口。

同时必须具有与外设连接的接口A 、B 、C 口。

由于8255可编程,所以必须具有逻辑控制部分,因而8255内部结构分为3个部分:与CPU 连接部分、与外设连接部分、控制部分。

(1)与CPU 连接部分根据定义,8255能并行传送8位数据,所以其数据线为8根D0~D7。

由于8255具有3个通道A 、B 、C ,所以只要两根地址线就能寻址A 、B 、C 口及控制寄存器,故地址线为两根A 0、A 1。

此外CPU 要对8255进行读、写与片选操作,所以控制线为片选、复位、读、写信号。

各信号的引脚编号如下:总线分类:名称引脚作用数据总线DB D 0-D 7与CPU 传送8位数据地址总线ABA 0、A 1选择A 、B 、C 与控制寄存器控制总线CB片选、复位RST 、读、CS 写CPU 读写操作前必须发出片选信号选中8255(2)与外设接口部分8255有3个通道A、B、C与外设连接,每个通道又有8根线与外设连接,所以8255可以用24根线与外设连接,若进行开关量控制,则8255可同时控制24路开关。

①数据端口A、B、C端口A(PA0-PA7):对应了1个8位的数据输入锁存器和1个数据输出锁存/缓冲器。

所以A 作为输入或输出时,数据均受到锁存。

端口B(PB0-PB7):对应了1个8位的数据输入缓冲器和1个数据输出锁存器/缓冲器。

所以B输入锁存,输出不受到锁存。

端口C(PC0-PB7):对应1个8位数据缓冲器和1个数据输出锁存/缓冲器,所以C输入不锁村,输出锁存。

微机课件_10第七章:8255并行接口PPT资料22页

方式2——双向选通输入/输出

只有A口可以工作在此方式下,并且A口既做输 入口又做输出口(双向输入/输出)

有专门的联络信号,由C口的5个引脚担任,C 口剩下的3个引脚可以作输入/输出,也可用作B 口方式1的联络线

可采用查询或中断传送 各联络信号间的时序和状态字基本是方式1下的

控制字= 00000111 B = 07H

MOV MOV OUT

AL, 07H DX, 303H DX, AL

8

4. 8255A的工作方式

方式0——基本输入/输出方式

A、B、C三口都可以工作在此方式下 无专门的联络信号,不能采用中断传送,可用于无

条件传送和查询传送 端口信号线间无固定时序,由引脚控制信号定时,

无固定的状态字 单向输入/输出,端口只能工作在输入或输出方式 输出时可锁存,输入时只能缓冲不锁存

9

方式1——选通输入/输出方式

只有A、B口可以工作在此方式下 有专门的联络信号,由C口的6个引脚担任, C

口剩下的2个引脚还可以作输入/输出 可以进行查询或中断传送 联络信号间有固定时序,有确定的状态字 单向输入/输出,输入、输出时都可以锁存

19

三种工作方式的对比

20

例:8255A用B组进行数据传输,B口工作在方式1 输入,C口下半部输出(A口不设)。端口地址 300H~303H。

① 写出初始化程序;

②打开B组的中断允许信号INTEB,即使PC2=1。

分析:工作方式字= 10000110 B = 86H

C口的按位置位/复位控制字= 00000101 B = 05H

第七章 并行接口和 8255

1

7.1 概述

并行通信

并行I-O接口芯片8255A

·INTR:中断请求信号输出,高电平有效。当它有效时,请求CPU 向8255A端口写入数据。

·INTE:中断允许控制位,它既不是输入也不是输出信号,而是 一个内部控制位。通过对PC6(端口A)或者PC2(端口B)置位/复位来开 放/禁止端口输入中断请求。

②方式1的输出 当A口与B口设定为方式1输出时,也各指定了C口的3根线为信号线,其引脚 定义和端口结构如图8-4所示。

图8-4 方式1输出时引脚定义和端口结构图.

(一)各控制信号的定义如下:

·(Output Buffer Full):输出缓冲器满信号,低电平有效。 它有效时,表示CPU已将数据写到8255A的输出端口,通知外设来取数。

这两个控制字共用一个端口地址,用特征位D7来区分。若控制字的D7 =1, 则为方式选择控制字;若控制字D7 =0,则是C口按位置位/复位控制字。控 制字必须写入控制寄存器。

1.控制字 (1) 方式选择控制字(D7 =1) 方式选择控制字的格式如图8-6所示。

图8-6 8255A的方式选择控制字

(2)C口按位置位/复位控制字(D7 =0) C口按位置位/复位控制字的格式如图8-7所示。

·IBF(Input Buffer Full):输入缓冲器满信号,高电平 有效。当它有效时,说明输入缓冲器中锁存有信息,且尚未 被CPU取走,通知外设不能再传送新数据;只有当它为低电平 时,即表示CPU已读取了数据,输入缓冲器变空,此时才允许 外设传送新的数据。

·INTR:中断请求信号,高电平有效。它有效时,请求 CPU从8255A读取外设已送入的数据。

在方式1下,A口和B口仍作为数据的输入和输出口而同时要利用C口的某些位作为 控制和状态信号。

8255可编程通用并行接口芯片

INTR:中断请求信号,高电平有效。当外设将数据锁存于 接口之中,且又允许中断请求发生时,就会产生中断请求。 2. 工作方式2,又称双向输入输出方式I/O操作

只有A口才能工作在方式2。A口工作方式2时要利用C口的5 条线才能实现。此时,B口只能工作在方式0或者方式1下,而C 口剩余的3条线可作为输入线、输出线或B口方式1之下的控制线。 C口提供的控制线如图7.12所示。

8255

D7

PA 0~PA 7

PB 0~ PB 7

ALE

RST

RESET

PC0~PC7

图7.9 8255的扩展逻辑电路

1.3 8255的工作方式

8255共有三种工作方式,这些工作方式可用软件编程来指定。

1. 工作方式0,又称基本输入输出方式

2. 工作方式1,又称选通输入输出方式 在这种方式下,A口和B口仍作为数据的输出或输入口而 同时要利用C口的某些位作为控制和状态信号,从而实现这种 工作方式。

走数据,口的缓冲器变空,且接口允许中断时,INTR有效。

即,

且允许中断,则INTR=1。

(2)方式1下,A口和B口均为输入

这种情况和两口均为输出类似,各条控制引线的定义如 图7.11所示。

A口

PC7

PC6

PC3

8255

PC0 PPCC21 B口

OBFA ACKA INTRA

INTRB OBFB ACKB

C口和一个控制寄存器供用户编程。的不同编码可分别选择上述

三个口和一个控制寄存器。地址编码如表7-2所示。

表7-2 地址编码

微机原理和接口知识点第7章并行接口8255

RD

CS A1 A0

D7~D0 CPU数据总线

数据有效

地址有效 数据有效

2) 在CPU发出读信号之前,外设已将欲输入的数据送入 8255的数据总线缓冲器。

3) 8255数据总线缓冲器中的数据必须保持到读信号消失 后才结束。

4) 读脉冲宽度至少大于300ns。

5) 在整个输入数据期间,地址信号保持有效。

I/O PB7~PB0

A1 , A0:8255内部寄存器地址寻址信号,8255内部有4个

端口,A,B,C与控制口。

A1

A0

端口

0

0

A口

0

1

B口

1

0

C口

1

1

控制口

说明: 1) A口有3种工作方式 方式0:基本I/O方式; 方式1:单向选通I/O方式,输入或输出只能选一种; 方式2:双向选通I/O方式,一次设置后通道既可以做输入

RD

CPU CB

WR

RESET

A0

CPU AB

A1

CS

8255A

I/O PA7~PA0

I/O PC7~PC4 外 I/O PC3~PC0 设

I/O PB7~PB0

PA1

3

PA0

4

RD

5

CS

6

GND 7

PA7~PA0, PB7~PB0, PC7~PC0

A1

8

A0

9

与外设相连的独立地址的

A

PC7 10 PC6 11

1. 8255的内部结构

8255是Intel系列的并行接口芯片,它是可编程的,可以用 来设置其工作方式,不需要再附加外部电路。

A组 控制

DB 数据总线 8位内部数据总线 缓冲器

清华计算机硬件技术基础--沈永林老师 并行接口电路

RD Trr 输入数据 CSA0A1 DB Trd

DB PA RD WR 8255 RESET A1 A0 CS

T1

T2

T3

T4

CLK

IO/M A19~16/S6~3 A15~A8 AD7~0 ALE RD DT/R DEN AB AB S6~S3

△T

DB

RD Trr

输入数据

CSA0A1 DB Trd

SBHE LA23 LA22 LA21 LA20 LA19 LA18 LA17 MEMW MEMR SD8 SD9 SD10 SD11 SD12 SD13 SD14 SD15

ISA总线(工业标准结构): IRQ9——原来是IRQ2,中断请求线 REFRESH——原为DACK0,刷新信号。 36线的定义如下: SD15~SD8——高8位数据线,双向 SBHE——数据高位允许信号,双向 MEMCS16—— 存储器 16 位选择信号, 输入,进行 16位数据传送,接口卡须回 送这一信号EISA IOCS16——I/O设备16位选择信号,输入, 进行16位数据传送的I/O设备发之 LA23~LA17——M/IO设备高7位地址 IRQ15~IRQ10——中断请求信号,输入。 其中 IRQ13 保留作为 80287 的中断请求 线,没有对外引出 DRQ7~DRQ0—— DMA请求信号,输入 DACK7~DACK0—— DMA响应信号,输出 MASTER——I/O 处理器发出的总线控 制信号,表示它已经控制了总线, 输入 MEMR——16M存储器读信号,双向 SMEMR——只读1M以内的存储空间 MEMW——16M存储器写信号,双向 SMEMW——只写1M以内的存储空间

GND B1 I/O CH CK A1 RESET DRV SD7 +5V SD6 IRQ9 SD5 -5V SD4 DRQ2 SD3 -12V SD2 0WS SD1 +12V SD0 GND B10 A10 I/O CH RDY SMEMW AEN SMEMR SA19 IOW SA18 MEMCS16 D1 C1 IOR SA17 IOCS16 DACK3 SA16 IRQ10 DRQ3 SA15 IRQ11 DACK1 SA14 IRQ12 DRQ1 SA13 IRQ15 REFRESH SA12 IRQ14 BCLOCKB20 A20 SA11 DACK0 IRQ7 SA10 DRQ0 IRQ6 SA9 DACK5 D10C10 IRQ5 SA8 DRQ5 IRQ4 SA7 DACK6 IRQ3 SA6 DRQ6 DACK2 SA5 DACK7 T/C SA4 DRQ7 BALE SA3 +5V +5V SA2 MASTER OSC SA1 GND D18C18 GND B31 A31 SA0 图 7-3 ISA总线信号

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第1节并行接口的概念

第1节并行接口的概念(续)

第1节并行接口的概念(续)

第2节8255A结构

第2节8255A结构

第2节8255A结构

第2节8255A结构

第2节8255A结构

第2节8255A结构

第2节8255A结构

第2节8255A结构

第3节8255工作方式与控制字

第4节8255工作方式与控制字(续)

第4节8255工作方式与控制字(续)

第4节8255工作方式与控制字(续)例:PC置位:00000111B

第4节8255工作方式与控制字(续)

第4节8255工作方式与控制字(续)

第4节8255工作方式与控制字(续)例:PC置位:00000111B

第4节8255工作方式与控制字(续)

第4节8255工作方式与控制字(续)

l 按位置位/复位控制字(续)

n 例:驱动喇叭产生不同声音【方波,频率,PC 6】

outspk proc

mov dx, 303H ;8255A 命令口地址mov al, 00001101B ;使PC 6=1out dx, al ;送到命令口call delay_200; 软件延时:200ms mov al, 00001100B ;是PC 6=0out dx, al ;送到命令口call delay_200; 软件延时:200ms outspk endp

注意:改变延时时间(delay_200)即可改变方波频率。

第4节8255工作方式与控制字(续)

) LED

LED

2

LED

4

LED

6

) LED

LED

2

LED

4

LED

6

) LED 0LED 2LED 4LED 6

0 0 010 0 000 0 110 0 1

第4节8255工作方式与控制字(续)

第4节8255工作方式与控制字(续)

第5节8255工作方式

第5节8255工作方式(续)

) LED

LED

2

LED

4

LED

6

第5节8255工作方式(续)

第5节8255工作方式(续)

第5节8255工作方式(续)

第5节8255工作方式(续)

第5节8255工作方式(续)

AND AL,04H ;测试PC2位是否为0

Y JNZ BUSY;忙,则等待;不忙,则向A口送数

结束

第5节8255工作方式(续)

DEC CX;字符数减1

JNZ BUSY;未完,继续

Y BUF DB “256个ASCII字符代码……”结束

第5节8255工作方式(续)

第5节8255工作方式(续)

第5节8255工作方式(续)

第5节8255工作方式(续)

第5节8255工作方式(续)

第5节8255工作方式(续)

第5节8255工作方式(续)

第5节8255工作方式(续)

第5节8255工作方式(续)。