Allegro等长线Xnet约束设置

allegro差分对和XNET设置

差分线的设置,相对等长线以及xnet的设置不同的信号对走线的要求不同,差分线为了抗干扰能力强,要求两根信号线在一定范围内等长等间距。

而现对等长线要求信号的相对延时在一定的范围内必须比较接近。

这个设置在原理图阶段可以设置,不过现在要讲的主要是在allegro环境下的设置。

一差分线的设置点击logic——》assign differential pair出现以上对话框的时候选择要创立的差分对的两根线。

方法很简单只要点击要选择的线就可以了在net1 和net2 上就可以显示这两个线的名字。

Diff pair name 自己起个记住名字。

一会设置规则的时候还要用到。

点击add 差分对就设定好了。

下面是通过约束管理器来定义差分对的走线规则。

点击set up——》constraints——》electrical选择net ——》differential pair 找到我们刚才设定的差分对名字lwq4 规则设定为5/7 Ok二等长线以及xnet 的设置许多等长线要求的场合往往等长线里还包含电阻,如果不用xnet 就需要画两组等长线,给布线带来很大的工作量。

特别是布线空间有限的时候。

1.设置xnet2.点击analyze——》SI/EMI sim ——》signal model assignment如上图,点击要创建xnet的器件比如说排阻rp4 点击creat model 出现如下对话框点击ok 出现如下对话框这里value 是仿真的时候用的阻值我们可以随便填个值比如说10 不过记住要这组等长线所有value 都要相等。

Single pins 这个非常重要,现在我们用的是排阻他有八个引脚。

就是说有四根线输入输出排阻,那么1 脚和8脚对应第一根线的输入输出,那么 2 脚和7脚对应第二根线的输入输出,那么3 脚和6脚对应第三根线的输入输出,那么4脚和5脚对应第四根线的输入输出,所以single pins 就对应 1 8 2 7 3 6 4 5 。

Allegro设置差分线和等长的方法

Allegro设置差分线和等长的方法

方法一:

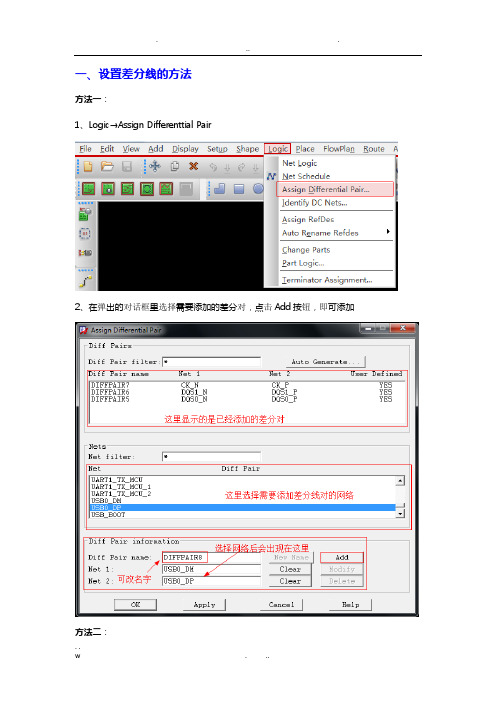

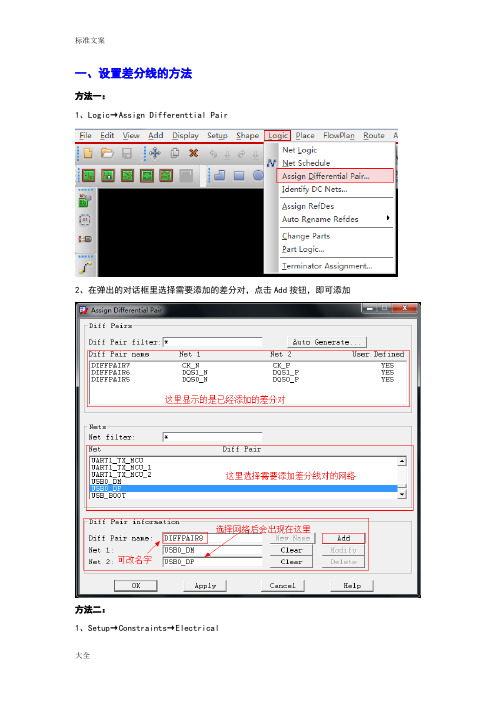

1、Logic -->Assign Differential Pair

2、在弹出的对话框里选择需要添加的差分对,点击Add按钮,即可添加。

方法二:

1、Setup -->Constraints -->Electrical

2、选择Net,然后在Objects-->Create-->Differential Pair

3、在弹出的对话框里选择需要添加的差分对,点击Create按钮

设置完差分对后,需要设置其约束规则,方法如下:

1、Setup -->Constraints -->Electrical-->Physical-->Physical Constraint Set-->All Layers

2、初始默认的有一个DEFAULT规则,右击DEFAULT,选择Create -->Physical CSet

4、弹出对话框,在Physical CSet 栏写上规则名称(建议根据差分线的阻抗描写,例:DIFF100),点击OK,可以看到多了一行PCS。

5、设置好规则项后,就可以在这项规则里设置线宽、线间距、过孔等参数

6、在Net 一栏看到有已经设好的差分线,在Referenced physical CSet 选项下选择刚设好的规则。

ALLEGRO约束设置

A L L E G R O约束规则设置介绍目录:第一部分:差分对的约束设置............... 错误!未指定书签。

第二部分:非差分信号约束设置............. 错误!未指定书签。

第三部分:区域约束设置................... 错误!未指定书签。

第四部分:XNet等长设置................... 错误!未指定书签。

本文所有操作与设置均在AllegroPCBeditor15.5环境中进行。

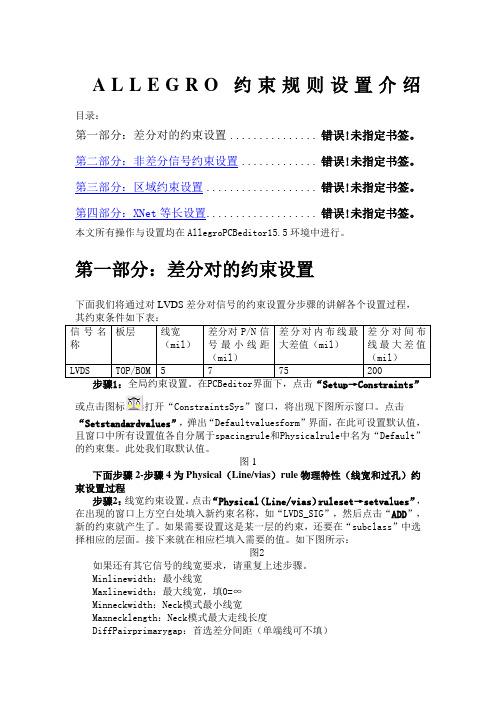

第一部分:差分对的约束设置下面我们将通过对LVDS差分对信号的约束设置分步骤的讲解各个设置过程,或点击图标打开“ConstraintsSys”窗口,将出现下图所示窗口。

点击“Setstandardvalues”,弹出“Defaultvaluesform”界面,在此可设置默认值,且窗口中所有设置值各自分属于spacingrule和Physicalrule中名为“Default”的约束集。

此处我们取默认值。

图1下面步骤2-步骤4为Physical(Line/vias)rule物理特性(线宽和过孔)约束设置过程步骤2:线宽约束设置。

点击“Physical(Line/vias)ruleset→setvalues”,在出现的窗口上方空白处填入新约束名称,如“LVDS_SIG”,然后点击“ADD”,新的约束就产生了。

如果需要设置这是某一层的约束,还要在“subclass”中选择相应的层面。

接下来就在相应栏填入需要的值。

如下图所示:图2如果还有其它信号的线宽要求,请重复上述步骤。

Minlinewidth:最小线宽Maxlinewidth:最大线宽,填0=∞Minneckwidth:Neck模式最小线宽Maxnecklength:Neck模式最大走线长度DiffPairprimarygap:首选差分间距(单端线可不填)DiffPairneckgap:Neck模式差分间距(单端线可不填)过孔规格在“Vialistproperty”中设定,一般设定在默认约束规则下。

Allegro16.6约束规则设置详解_SCC

Allegro16.6约束规则设置详解_SCCAllegro16.6约束规则设置详解前言:本文主要讲解Allegro16.6约束管理器的使用,从基本约束规则到高级约束规则的设置。

目录:一、基本约束规则设置1、线间距设置2、线宽设置3、设置过孔4、区域约束规则设置5、设置阻抗6、设置走线的长度范围7、设置等长7.1、不过电阻的NET等长7.2、过电阻的XNET等长7.3、T型等长8、设置通用属性9、差分规则设置9.1、创建差分对9.2、设置差分约束10、Pin Delay二、高级约束规则设置11、单个网络长度约束12、a+b类长度约束13、a+b-c类长度约束14、a+b-c在最大和最小传播延迟中的应用1、线间距设置(1)、设置默认间距规则点击CM图标,如下图所示,打开约束管理器。

单击Spacing,再点击All Layers,如下图所示。

右边有一个DEFAULT就是默认规则,我们可以修改其值。

按住Shift键,点击第一个和最后一个即可选中所示,然后输入一个值,这样就都修改了,如下图所示(2)、定义特殊的间距约束点选Default按鼠标右键,执行Create-Spacing CSet加入新规则。

取一个有意义点的名字,如下图所示,单击OK。

按住Shift键选中所有,输入12,回车。

然后为所需要设置的网络分配规则单击左边的Net-All Layers,在右边工作簿中,为GND网络设置12MIL_SPACE规则,在Referenced Spacing CSet下选中12MIL_SPACE,如下图所示(3)、设置Class-Class规则若针对不同的信号群组有不同的间距规则,则需要设置Class-Class选到Net Class-Class后,在右边CLOCK(2)上右键选择Ctreat- Class-Class...,如下图所示选择2个不同的Net Classes,如下图所示,单击OK如下图所示。

在右边的Referenced Spacing CSet栏可以修改其值。

Allegro16.6设置等长规则

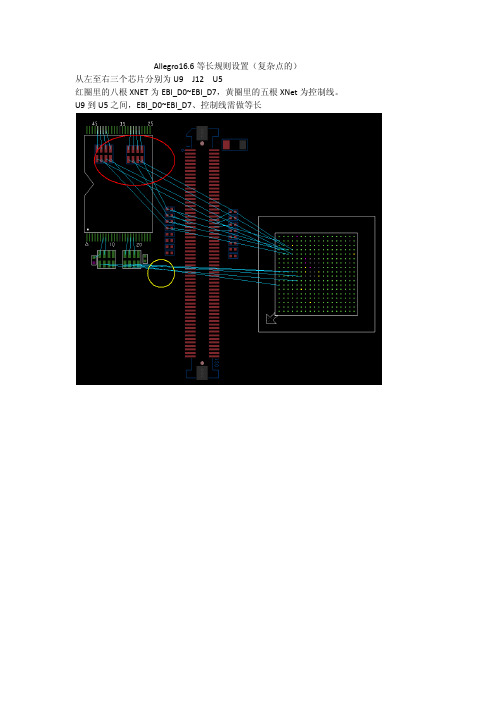

Allegro16.6等长规则设置(复杂点的)从左至右三个芯片分别为U9 J12 U5红圈里的八根XNET为EBI_D0~EBI_D7,黄圈里的五根XNet为控制线。

U9到U5之间,EBI_D0~EBI_D7、控制线需做等长多出来的八根XNET为EBI_D8~EBI_D15J12到U5之间EBI_D0‐ EBI_D15做等长接下来开始步骤:(设模型、X‐NET就不说啦,坛子里有很多说的挺清楚的)将EBI_D0~EBI_D15设为一个Class,EBI_D将EBI_D0~EBI_D15设PINPAIREBI_D0~EBI_D7设置两组PINPAIREBI_D8~EBI_D15设置一组PINPAIR设EBI_D0 拓扑Set‐Constraint红框中填好点ADD再新增另一个规则点ADD点OK后回到以下界面,FILE‐Update Constraint Manager点是出现两组MGrp,每组下面只出现一对,因为仅对EBI_D0设了规则。

EBI_D0和EBI_D1~D7的拓扑一样的,将刚才生成的ElecCset赋予它们赋予它们的同时,两组MGrp里的PPr也在增多但EBI_D8~D15的拓扑和它们不一样,所以得重新建拓扑设规则省略几步,和之前设的时候一样的点是,可以看到EBI_D8被赋予规则EBI_D8,EBI_D9~D15拓扑与EBI_D8一样的,所以把EBI_D8这一规则分别赋予它们。

目前为止,EBI_D0~D15从U5到J12就做了等长,走线时就有控制进度条显示但是从U5到U9这一段还有几根控制线未加进来找到这几根控制线,add to MatchGroupEBINAND这一MatchGroup里就有这些XNET了。

红色框中选择ALL DRIVERS..红色框中改为0mil:100milU9到U5之间,EBI_D0~EBI_D7、控制线就做好等长啦、这种设等长的方式思路挺清晰的,所以就推荐给大家,或者是给还不会设等长的一点参考。

allegro 中关于xnet 的等长设置

Allegro 中关于 XNET 的等长设置近年来,随着科技的不断进步和信息技术的快速发展,人们对于数据传输和网络通讯的需求越来越高。

在这样的背景下,Allegro 这款优秀的软件在 XNET 方面的等长设置备受关注。

下文将针对这一主题展开论述,以便读者更深入地了解这个问题。

一、XNET 简介XNET 是一种用于数据传输和网络通讯的现代化技术,它采用了一系列的协议和标准,可以实现设备之间的信息交换和通讯。

在工业自动化和车辆电子等领域,XNET 扮演着非常重要的角色。

二、Allegro 中的 XNET在 Allegro 中,XNET 技术得到了广泛的应用。

作为高性能的电子设计自动化工具,Allegro 对于 XNET 的支持非常完善,用户可以通过Allegro 对 XNET 进行灵活、高效的配置和管理。

三、等长设置的重要性等长设置在 XNET 技术中起着非常重要的作用。

通过等长设置,可以保证数据在传输过程中不发生失真和变形,确保通讯的质量和可靠性。

合理的等长设置是 XNET 技术中的关键环节,影响着整个系统的性能和稳定性。

四、Allegro 中关于 XNET 的等长设置在 Allegro 中,用户可以通过一系列的操作和设置来对 XNET 进行等长设置。

具体来说,可以从以下几个方面进行配置:1. 等长线路的设计在进行 XNET 的等长设置时,首先需要考虑的是等长线路的设计。

通过合理的布线和线路设计,可以尽量减少信号传输中的时延和失真,保证数据的准确性。

2. 信号调整和校准在 Allegro 中,用户可以对 XNET 的信号进行调整和校准,以确保各个信号的等长性。

通过精确的校准,可以让信号在传输过程中保持稳定和一致,提高通讯的可靠性。

3. 参数优化和实时监控除了静态的等长设置外,Allegro 还提供了参数优化和实时监控的功能。

用户可以根据实际情况对 XNET 进行动态调整,及时发现和处理通讯中的问题,保证系统的稳定运行。

Allegro16.6约束规则设置详解

Allegro16.6约束规则设置详解前言:本文主要讲解Allegro16.6约束管理器的使用,从基本约束规则到高级约束规则的设置。

目录:一、基本约束规则设置1、线间距设置2、线宽设置3、设置过孔4、区域约束规则设置5、设置阻抗6、设置走线的长度范围7、设置等长7.1、不过电阻的NET等长7.2、过电阻的XNET等长7.3、T型等长8、设置通用属性9、差分规则设置9.1、创建差分对9.2、设置差分约束10、Pin Delay二、高级约束规则设置11、单个网络长度约束12、a+b类长度约束13、a+b-c类长度约束14、a+b-c在最大和最小传播延迟中的应用1、线间距设置(1)、设置默认间距规则点击CM图标,如下图所示,打开约束管理器。

单击Spacing,再点击All Layers,如下图所示。

右边有一个DEFAULT就是默认规则,我们可以修改其值。

按住Shift键,点击第一个和最后一个即可选中所示,然后输入一个值,这样就都修改了,如下图所示(2)、定义特殊的间距约束点选Default按鼠标右键,执行Create-Spacing CSet加入新规则。

取一个有意义点的名字,如下图所示,单击OK。

其值是从默认规则拷贝的,先修改其值。

按住Shift键选中所有,输入12,回车。

然后为所需要设置的网络分配规则单击左边的Net-All Layers,在右边工作簿中,为GND网络设置12MIL_SPACE规则,在Referenced Spacing CSet下选中12MIL_SPACE,如下图所示(3)、设置Class-Class规则若针对不同的信号群组有不同的间距规则,则需要设置Class-Class选到Net Class-Class后,在右边CLOCK(2)上右键选择Ctreat-Class-Class...,如下图所示选择2个不同的Net Classes,如下图所示,单击OK如下图所示。

在右边的Referenced Spacing CSet栏可以修改其值。

Allegro中等长设置方法

创建模型:

如果排阻PinNumber顺序是这样的,则:

注:Pin Number与Pin Number之间有空格

创建模型:

d)完成模型设置后,查看这个排阻的Net属性,在Net name下面会多 一个Net名字,这表示Xnet已经创建好了。

导入PACAGE长度:

1、File->Import->Pin Delay:

2、Pin Delay File是芯片厂提供的 文件,因没有这一文件,暂时没法演示。

等长规则应用:

i)完成的效果,如下图:

总结

这是通过模型来设置等长规则的一种 方法,如果Xnet已经创建好了,则在 Constraint Manager一样可以设置,会 更方便,之所以提出这种方法,只是多 一种选择,当匹配比较复杂的时候,模 型创建就相对复杂

设置等长规则:

设置等长规则:

设置等长规则:

c)选择菜单Set->Constraints,出现如下窗体:

设置等长规则:

Rule Name:等长规则名字,这里可以随便输入,不过最好方便辨认 From:开始Pin To:结束Pin Scope:规则适应范围

Local:适用本网络 Global:适用所有网络 Bus:适用所在Bus Class: 适用所在Class Delta Type:Delta匹配类型,Delta为与基准线对比值,如果一组线要 求等长,我们可以把Delta设为None,或把Delta值设为0 Delay: 延迟 Length:长度,一般都设长度 Delta: 设定值 Tol Type: 误差类型 Tolerance: 误差范围。

f)在Constraint Manager中就有更新提示:

allegro设置差分线和等长的方法

一、设置差分线的方法方法一:1、Logic→Assign Differenttial Pair2、在弹出的对话框里选择需要添加的差分对,点击Add按钮,即可添加方法二:1、Setup→Constraints→Electrical2、选择Net,然后在Objects→Create→Differenttial Pair3、在弹出的对话框里选择需要添加的差分对,点击Create按钮,即可添加设置完差分线对后,需要设置其约束规则,方法如下:1、初始默认的有一个DEFAULT规则,右击DEFAUlT,选择Create→Physical CSet2、弹出一下对话框,在Physical CSet栏写上规则名称,建议根据差分线的阻抗描写,点击OK,这里已经写好,规则名称为:DIFF100,就可以看到多了一行PCS3、设立好规则后就可以在这项规则里设置线宽间距等参数了4、在Net一栏看到有已经设好的差分线,在Referenced physical C Set选项下选择刚刚设好的规则DIFF100*规则设置中各个项目的含义*Line Width(设置基本走线宽度)Min:最小线宽Max:最大线宽,写0相当于无限大Neck(neck模式,一般在间距很小的时候用到)Min Width:最小线宽Max Length:最大线长Differential Pair(差分线设置,单端线可不写)Min Line Spacing:差分对的最小线间距Primary Gap:差分对理想线间距Neck Gap:差分对最小允许线间距(+)T olerance:差分线允许的误差+(-)Tolerance:差分线允许的误差-Vias(过孔选择)BB Via Stagger(设置埋/盲孔的过孔间距)Min:最小间距Max:最大间距AllowPad-Pad Connect:/ Etch:/Ts:/示意图:二、设置等长1、进入规则设置页面Electrical→Net→Routing→Relative Propagation Delay2、选中需要设置等长的网络,右击,选择Create→Match Group3、更改组名称4、设置好后,会显示MGrp,如下图。

Allegro设置差分线和等长地方法

一、设置差分线的方法方法一:1、Logic→Assign Differenttial Pair2、在弹出的对话框里选择需要添加的差分对,点击Add按钮,即可添加方法二:1、Setup→Constraints→Electrical2、选择Net,然后在Objects→Create→Differenttial Pair3、在弹出的对话框里选择需要添加的差分对,点击Create按钮,即可添加设置完差分线对后,需要设置其约束规则,方法如下:1、初始默认的有一个DEFAULT规则,右击DEFAUlT,选择Create→Physical CSet2、弹出一下对话框,在Physical CSet栏写上规则名称,建议根据差分线的阻抗描写,点击OK,这里已经写好,规则名称为:DIFF100,就可以看到多了一行PCS3、设立好规则后就可以在这项规则里设置线宽间距等参数了4、在Net一栏看到有已经设好的差分线,在Referenced physical C Set选项下选择刚刚设好的规则DIFF100*规则设置中各个项目的含义*Line Width(设置基本走线宽度)Min:最小线宽Max:最大线宽,写0相当于无限大Neck(neck模式,一般在间距很小的时候用到)Min Width:最小线宽Max Length:最大线长Differential Pair(差分线设置,单端线可不写)Min Line Spacing:差分对的最小线间距Primary Gap:差分对理想线间距Neck Gap:差分对最小允许线间距(+)Tolerance:差分线允许的误差+(-)Tolerance:差分线允许的误差-Vias(过孔选择)BB Via Stagger(设置埋/盲孔的过孔间距)Min:最小间距Max:最大间距AllowPad-Pad Connect:/Etch:/Ts:/示意图:二、设置等长1、进入规则设置页面Electrical→Net→Routing→Relative Propagation Delay2、选中需要设置等长的网络,右击,选择Create→Match Group3、更改组名称4、设置好后,会显示MGrp,如下图。

Allegro16.6约束规则设置详解2

7.2、过电阻的XNET 等长这里关键是设置XNET。

假设有一排过电阻的线需要等长。

首先创建电阻模型。

单击Signal Model 图标,如下图所示点击电阻,如下图所示,单击RN0603 10所有这种模型的电阻都高亮了,如下图所示单击Create Model。

按钮。

默认,单击OK默认单击OK。

如下图所示。

再单击OK 结束命令。

假设我们要将DR_MD49 到DR_MD53网络等长。

打开约束管理器,选择相对延迟,这里可以看到我们刚才设置的XNET。

我们在DR_MD49 网络上右键创建PIN PAIR选择2 个端点,如上图所示,单击OK。

同理,其他需要设置等长的网络,也创建PIN PAIR。

然后按住Ctrl 键选择这些PIN PAIR,右键创建MATCH GROUP 如下图所示设定约束值,及目标网络,方法同不过电阻网络等长设置。

7.3、T 型等长T 型等长设置,比如两个D DR 之间的等长就属于T 型等长,设置方法如下(以text_drr 举例)。

首先添加T 型连接点。

点击Logic-Net Schedule,单击你要设置网络的一个pin。

如下图。

在中间右键Insert T,加入T 型连接点,如下图所示然后去点击第二个pin,再回到T 型连接点,然后去点击第三个pin,右键done 即可。

创建的T 型连接点如下图所示这只是创建了一个网络的T 型连接点,如果需要创建多个,可点击进入约束管理器设置。

在N et-Routing——Wiring 下面,刚才设置的网络拓扑便会显示成UserDefined。

如下图所示选中那个网络,右键创建Creat-Electrical CSet,如下图然后将你需要设置T 型结构的网络选择刚才设置的ECSet 作为参考,Verify Schedule 选择yes 即打开验证,如下图所示。

然后打开检查模式,在约束管理器Analyze-Analysis Modes弹出的对话框中,将Stub length/Net 的检查模式选择为on 如下如所示。

Allegro中走线等长设置进阶

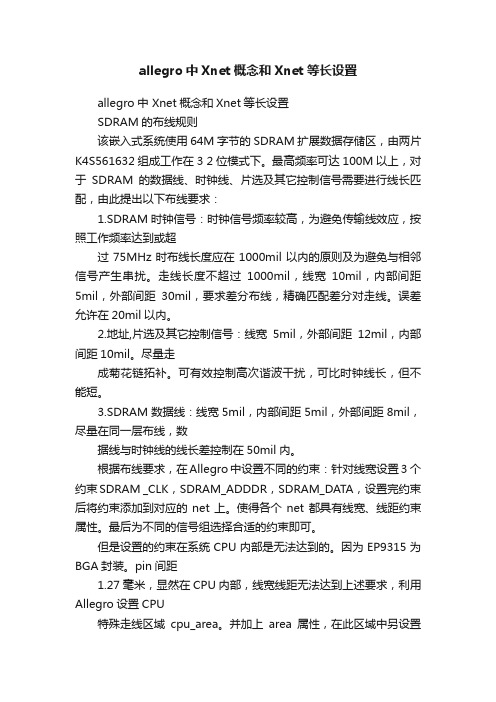

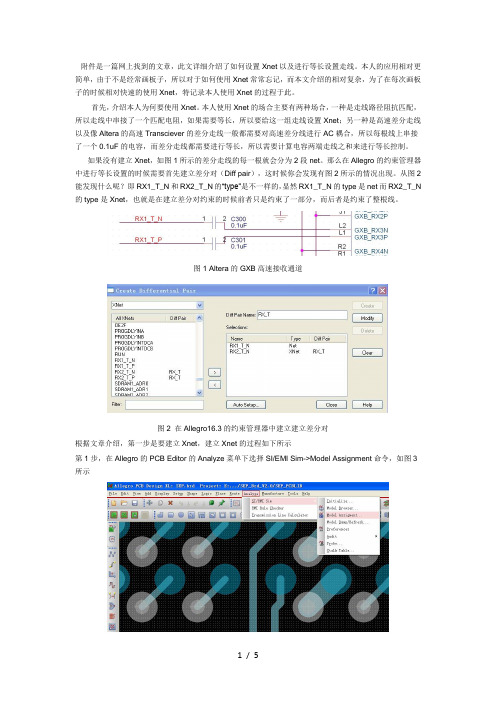

Allegro中走线等长设置进阶————————————————————————————————作者:————————————————————————————————日期:在高速电路设计中,走线的等长显得越来越重要,因此设置等长这问题也就产生了,对于简单走线等长在以前文档中都有涉及这里不再复述了,下面内容将给大家介绍一下有关Xnet等长的设置问题, 如现在主板DDR, IDE 等部分设等长问题.注意: 以下设置方法不是公板方式,是我自己摸索的设置方法,所以大家不必效仿,仅供参考! 如果大家有任何其它或简单方法也请分享一下经验!在这之前首先介绍一下一个新个概念Xnet,见下图:我们把连续的几段由无源元件(如电阻,电容或电感)连接的net合称为一段Xnet.大家知道Allegro中有两个常用的走线长度设置,PROPAGATION_DELAY, RELATIVE_ PROPAGATION_DELAY 都只能针对同一Net设置,下面是一个具体案例:现在要求U1 到U2 的走线Net*A + Net*B等长, 误差为+/-20Mil,最简单的方式就是分别设置Net*A等长和Net*B等长,误差各为+/-10Mil, 这样是可以达到要求,不过会加大Layout工程师绕线的难度,因为可能Net*A部分空间比较大有足够的绕线空间,而Net*B部分没有空间绕线,所以就比较难达到要求.如果一种设置能把Net*A与Net*B相加,然后再做等长比对,这样就可以解决问题了, 好的就是Allegro都早为这些问题考虑过了,只要把Net*A 与Net*B设置为一个Xnet问题就解决一半了.下面内容将详细介绍怎样设置Xnet与Xnet等长.第一部分: Xnet设置(下面步骤可能有些简单,不过能达到效果)0, 需要Allegro Export版本或SPECCTRAQuest中设置, 还好大家有Cracked License天下无敌,什么版本都有J1, 开启Allegro Export或SPECCTRAQuest(以下省略,用Allegro简称这两个), Open需要设置Xnet的板子.2, 点击菜单Analyze>SI/EMI Sim>Model…(比正常方式设置Model简单了些)出来的建议定义DC net直接Yes 即可,然后出现下面的Model设置窗体:3, 直接在DevType Value/Refdes 中选择要设定Model 的器件或直接在板子上点选要设置Model的器件;4, 点选Create Model,建立该零件的Model,(如果已经有该零件的Model,并在前面定义,然后Find Model即可,这里主要介绍没有的情况)在出现对话框中选择Create ESpiceDevice model,点击OK5, 出现下面窗体:ModelName: 输入产生Model的名字Circuit type: 选择Type, 电阻,电感或电容Value: 值Single Pin: 各Pin的连接顺序, 中间为空格,这里要注意要看零件的pin的排列,1 2 3 4 5 6 7 8,就是: 1 和2 是一个电阻,其它同理所以如果就是普通电阻电容那就更简单了.Common Pin: 这里不用管它,空着就可以.上面都输入好了就点击OK,完成Model的建立.点击OK退出就可以发现连接该排阻的两边的Net 都有了个Xnet属性,如下图:这样就可以搞定Xnet,很简单吧!下面就开始等长设置吧!第二部分针对Xnet部分的等长设置设置好了Xnet后就可以在Allegro中设置该Xnet的等长了,有两种方法可以设置Xnet的等长.第一种, 使用Edit>Properties定义注意必须使用Pin Pair 才能定义Xnet等长RELATIVE_ PROPAGATION_DELAY= GroupX : G : U1.5 : U2.4 : 0 : 20在没有定义Xnet之前这样定义时会提示错误的其它的和前面的等长设置方法都一样.如果大家觉得这样设置有些麻烦的话,还有一招可以使用,见下面:第二种, Constraint Manager 设置1, 开启Constraint Manager, 点选菜单Setup>Electrical Constraint Spreadsheet或直接点击工具栏出现Constraint Manager 窗体:对于Constraint Manager 的一般使用方法这里不再做详细介绍, 如果用户对这部分不熟悉可以参考其它有关Constraint Manager 使用进行学习.2, 因为我们目的是要设置等长, 所以我们用Relative Propagation Delay这属性, 从左边控制栏中选择Net>Routing>Relative Propagation Delay,3, 在右边就会显示整块板子所有的Net或Xnet,4, 建立需要等长的Pin Pair, 右键点击需要建立Pin Pair 的Xnet选择起始Pin和结束Pin,注意:1, 这里没有先后顺序.2, 如果Pin Pair 的两个Pin Type全是Passive的话不能Creat, 所以这里还需要定义一下Pin的形态, 如:Out put, In put, Bidirectional等下面是介绍如何在Allegro中定义Pin type。

如何再 Candence 设置XNET

如何在Allegro16.3里设置Xnet并进行等长设置发布时间:2012-07-05 11:45:12技术类别:PCB个人分类:Cadence附件是一篇网上找到的文章,此文详细介绍了如何设置Xnet以及进行等长设置走线。

本人的应用相对更简单,由于不是经常画板子,所以对于如何使用Xnet常常忘记,而本文介绍的相对复杂,为了在每次画板子的时候相对快速的使用Xnet,特记录本人使用Xnet的过程于此。

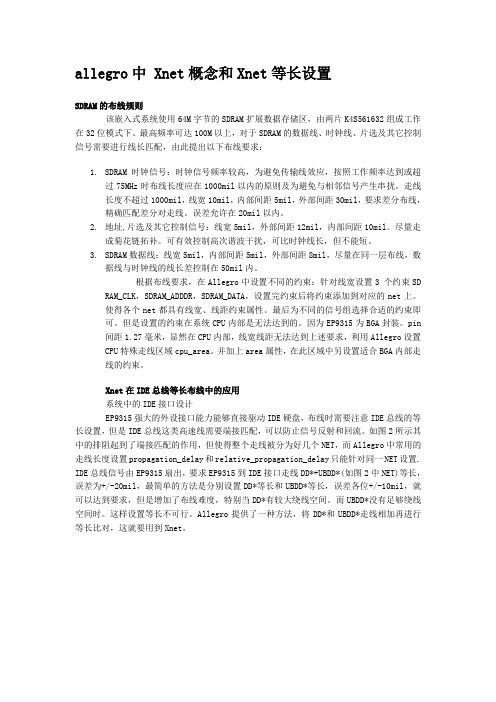

首先,介绍本人为何要使用Xnet。

本人使用Xnet的场合主要有两种场合,一种是走线路径阻抗匹配,所以走线中串接了一个匹配电阻,如果需要等长,所以要给这一组走线设置Xnet;另一种是高速差分走线以及像Altera的高速Transciever的差分走线一般都需要对高速差分线进行AC耦合,所以每根线上串接了一个0.1uF的电容,而差分走线都需要进行等长,所以需要计算电容两端走线之和来进行等长控制。

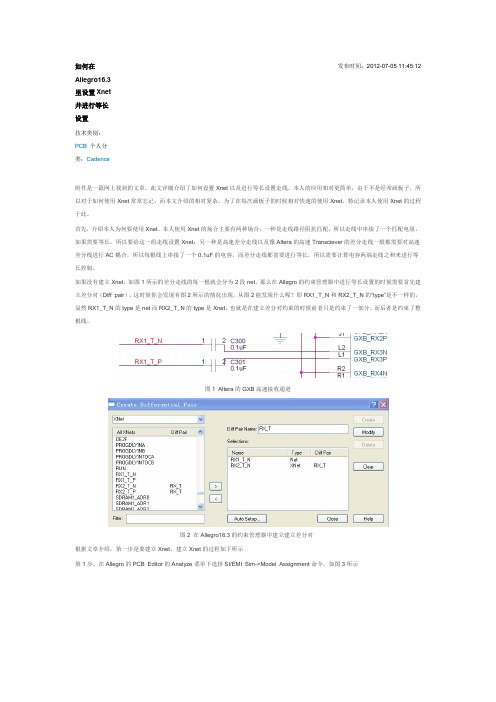

如果没有建立Xnet,如图1所示的差分走线的每一根就会分为2段net。

那么在Allegro的约束管理器中进行等长设置的时候需要首先建立差分对(Diff pair),这时候你会发现有图2所示的情况出现。

从图2能发现什么呢?即RX1_T_N和RX2_T_N的“type”是不一样的,显然RX1_T_N的type是net而RX2_T_N的type是Xnet,也就是在建立差分对约束的时候前者只是约束了一部分,而后者是约束了整根线。

图1 Altera的GXB高速接收通道图2 在Allegro16.3的约束管理器中建立建立差分对根据文章介绍,第一步是要建立Xnet,建立Xnet的过程如下所示第1步,在Allegro的PCB Editor的Analyze菜单下选择SI/EMI Sim->Model Assignment命令,如图3所示图3 启动开始建立Xnet第2步,进去以后会看到如图4所示的界面,由于差分线中串接的是0402封装的0.1uF的电容,所以选择此项。

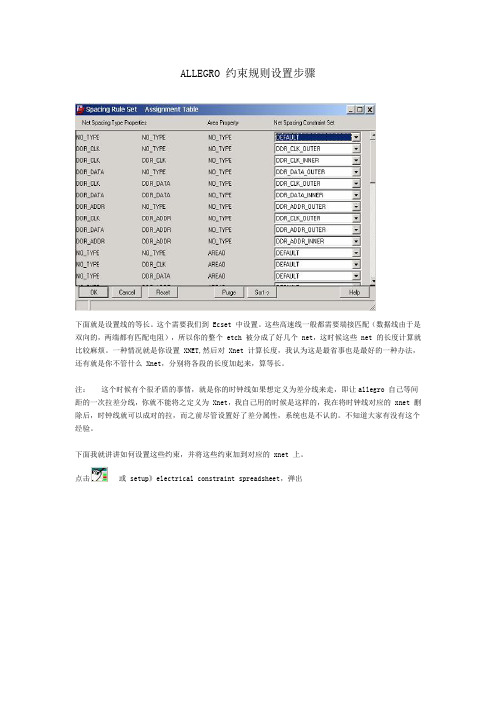

ALLEGRO 约束规则设置步骤-1

ALLEGRO 约束规则设置步骤下面就是设置线的等长。

这个需要我们到 Ecset 中设置。

这些高速线一般都需要端接匹配(数据线由于是双向的,两端都有匹配电阻),所以你的整个 etch 被分成了好几个 net,这时候这些 net 的长度计算就比较麻烦。

一种情况就是你设置 XNET,然后对 Xnet 计算长度,我认为这是最省事也是最好的一种办法,还有就是你不管什么 Xnet,分别将各段的长度加起来,算等长。

注:这个时候有个很矛盾的事情,就是你的时钟线如果想定义为差分线来走,即让allegro 自己等间距的一次拉差分线,你就不能将之定义为 Xnet,我自己用的时候是这样的,我在将时钟线对应的 xnet 删除后,时钟线就可以成对的拉,而之前尽管设置好了差分属性,系统也是不认的。

不知道大家有没有这个经验。

下面我就讲讲如何设置这些约束,并将这些约束加到对应的 xnet 上。

点击或 setup》electrical constraint spreadsheet,弹出点击 electrical constraint set》routing》total etch length,右边如上图所示出现 brd 名字,右键点击 brd名字,弹出如下右键菜单如上图点击 create ECset,则弹出输入 DDR_ADDR, 点击 ok,则 brd 名字前出现+号,打开之,可以见到设置好的DDR_ADDR.现在针对 DDR_ADDR,就可以设定具体的参数了。

比如,你可以将最小长度设定为1600mils,最大长度设为 2500mils。

这个参数的取得其实取决于你的时钟走线拓扑,因为按照走线要求,数据线,地址线等等都是以时钟线为基准的,所以,你必须先把时钟线布好,至少以后不能做大的改动,除非你能保证时钟线走线长度不变。

这里我们假设你的时钟线长为 1550mil+10mils,则显然你的地址线不能短于 1560mils,我们取为1600mils。

allegro中 Xnet概念和Xnet等长设置

allegro中 Xnet概念和Xnet等长设置SDRAM的布线规则该嵌入式系统使用64M字节的SDRAM扩展数据存储区,由两片K4S561632组成工作在3 2位模式下。

最高频率可达100M以上,对于SDRAM的数据线、时钟线、片选及其它控制信号需要进行线长匹配,由此提出以下布线要求:1.SDRAM时钟信号:时钟信号频率较高,为避免传输线效应,按照工作频率达到或超过75MHz时布线长度应在1000mil以内的原则及为避免与相邻信号产生串扰。

走线长度不超过1000mil,线宽10mil,内部间距5mil,外部间距30mil,要求差分布线,精确匹配差分对走线。

误差允许在20mil以内。

2.地址,片选及其它控制信号:线宽5mil,外部间距12mil,内部间距10mil。

尽量走成菊花链拓补。

可有效控制高次谐波干扰,可比时钟线长,但不能短。

3.SDRAM数据线:线宽5mil,内部间距5mil,外部间距8mil,尽量在同一层布线,数据线与时钟线的线长差控制在50mil内。

根据布线要求,在Allegro中设置不同的约束:针对线宽设置3 个约束SDRAM _CLK,SDRAM_ADDDR,SDRAM_DATA,设置完约束后将约束添加到对应的net上。

使得各个net都具有线宽、线距约束属性。

最后为不同的信号组选择合适的约束即可。

但是设置的约束在系统CPU内部是无法达到的。

因为EP9315为BGA封装。

pin间距1.27毫米,显然在CPU内部,线宽线距无法达到上述要求,利用Allegro设置CPU特殊走线区域cpu_area。

并加上area属性,在此区域中另设置适合BGA内部走线的约束。

Xnet在IDE总线等长布线中的应用系统中的IDE接口设计EP9315强大的外设接口能力能够直接驱动IDE硬盘,布线时需要注意IDE总线的等长设置,但是IDE总线这类高速线需要端接匹配,可以防止信号反射和回流。

如图2所示其中的排阻起到了端接匹配的作用,但使得整个走线被分为好几个NET,而Allegro中常用的走线长度设置propagation_delay和relative_propagation_delay只能针对同一NET设置.I DE总线信号由EP9315扇出,要求EP9315到IDE接口走线DD*+UBDD*(如图2中NET)等长,误差为+/-20mil,最简单的方法是分别设置DD*等长和UBDD*等长,误差各位+/-10mil,就可以达到要求,但是增加了布线难度,特别当DD*有较大绕线空间。

allegro中Xnet概念和Xnet等长设置

allegro中Xnet概念和Xnet等长设置allegro中 Xnet概念和Xnet等长设置SDRAM的布线规则该嵌入式系统使用64M字节的SDRAM扩展数据存储区,由两片K4S561632组成工作在3 2位模式下。

最高频率可达100M以上,对于SDRAM的数据线、时钟线、片选及其它控制信号需要进行线长匹配,由此提出以下布线要求:1.SDRAM时钟信号:时钟信号频率较高,为避免传输线效应,按照工作频率达到或超过75MHz时布线长度应在1000mil以内的原则及为避免与相邻信号产生串扰。

走线长度不超过1000mil,线宽10mil,内部间距5mil,外部间距30mil,要求差分布线,精确匹配差分对走线。

误差允许在20mil以内。

2.地址,片选及其它控制信号:线宽5mil,外部间距12mil,内部间距10mil。

尽量走成菊花链拓补。

可有效控制高次谐波干扰,可比时钟线长,但不能短。

3.SDRAM数据线:线宽5mil,内部间距5mil,外部间距8mil,尽量在同一层布线,数据线与时钟线的线长差控制在50mil内。

根据布线要求,在Allegro中设置不同的约束:针对线宽设置3 个约束SDRAM _CLK,SDRAM_ADDDR,SDRAM_DATA,设置完约束后将约束添加到对应的net上。

使得各个net都具有线宽、线距约束属性。

最后为不同的信号组选择合适的约束即可。

但是设置的约束在系统CPU内部是无法达到的。

因为EP9315为BGA封装。

pin间距1.27毫米,显然在CPU内部,线宽线距无法达到上述要求,利用Allegro设置CPU特殊走线区域cpu_area。

并加上area属性,在此区域中另设置适合BGA内部走线的约束。

Xnet在IDE总线等长布线中的应用系统中的IDE接口设计EP9315强大的外设接口能力能够直接驱动IDE硬盘,布线时需要注意IDE总线的等长设置,但是IDE总线这类高速线需要端接匹配,可以防止信号反射和回流。

如何在Allegro16.3里设置Xnet并进行等长设置

附件是一篇网上找到的文章,此文详细介绍了如何设置Xnet以及进行等长设置走线。

本人的应用相对更简单,由于不是经常画板子,所以对于如何使用Xnet常常忘记,而本文介绍的相对复杂,为了在每次画板子的时候相对快速的使用Xnet,特记录本人使用Xnet的过程于此。

首先,介绍本人为何要使用Xnet。

本人使用Xnet的场合主要有两种场合,一种是走线路径阻抗匹配,所以走线中串接了一个匹配电阻,如果需要等长,所以要给这一组走线设置Xnet;另一种是高速差分走线以及像Altera的高速Transciever的差分走线一般都需要对高速差分线进行AC耦合,所以每根线上串接了一个0.1uF的电容,而差分走线都需要进行等长,所以需要计算电容两端走线之和来进行等长控制。

如果没有建立Xnet,如图1所示的差分走线的每一根就会分为2段net。

那么在Allegro的约束管理器中进行等长设置的时候需要首先建立差分对(Diff pair),这时候你会发现有图2所示的情况出现。

从图2能发现什么呢?即RX1_T_N和RX2_T_N的“type”是不一样的,显然RX1_T_N的type是net而RX2_T_N 的type是Xnet,也就是在建立差分对约束的时候前者只是约束了一部分,而后者是约束了整根线。

图1 Altera的GXB高速接收通道图2 在Allegro16.3的约束管理器中建立建立差分对根据文章介绍,第一步是要建立Xnet,建立Xnet的过程如下所示第1步,在Allegro的PCB Editor的Analyze菜单下选择SI/EMI Sim->Model Assignment命令,如图3所示图3 启动开始建立Xnet第2步,进去以后会看到如图4所示的界面,由于差分线中串接的是0402封装的0.1uF的电容,所以选择此项。

可以看到此项下包含了所有工程里使用的所有的该类电容,选择你需要建立Xnet的电容,如图5所示。

图4图5第3步,在上述图4,和图5中选择相应的电容,这里是C300,(注意,这里我们事先已经将C301建好了Xnet),然后点击“Create Model”命令进入创建模型界面,如图6所示。

allegro设置差分线和等长的方法

一、设置差分线的方法方法一:1、Logic→Assign Differenttial Pair2、在弹出的对话框里选择需要添加的差分对,点击Add按钮,即可添加方法二:1、Setup→Constraints→Electrical2、选择Net,然后在Objects→Create→Differenttial Pair3、在弹出的对话框里选择需要添加的差分对,点击Create按钮,即可添加设置完差分线对后,需要设置其约束规那么,方法如下:1、初始默认的有一个DEFAULT规那么,右击DEFAUlT,选择Create→Physical CSet2、弹出一下对话框,在Physical CSet栏写上规那么名称,建议根据差分线的阻抗描写,点击OK,这里已经写好,规那么名称为:DIFF100,就可以看到多了一行PCS3、设立好规那么后就可以在这项规那么里设置线宽间距等参数了4、在Net一栏看到有已经设好的差分线,在Referenced physical C Set选项下选择刚刚设好的规那么DIFF100*规那么设置中各个工程的含义*Line Width〔设置根本走线宽度〕Min:最小线宽Max:最大线宽,写0相当于无限大Neck〔neck模式,一般在间距很小的时候用到〕Min Width:最小线宽Max Length:最大线长Differential Pair〔差分线设置,单端线可不写〕Min Line Spacing:差分对的最小线间距Primary Gap:差分对理想线间距Neck Gap:差分对最小允许线间距(+)Tolerance:差分线允许的误差+(-)Tolerance:差分线允许的误差-Vias〔过孔选择〕BB Via Stagger〔设置埋/盲孔的过孔间距〕Min:最小间距Max:最大间距AllowPad-Pad Connect:/Etch:/Ts:/示意图:二、设置等长1、进入规那么设置页面Electrical→Net→Routing→Relative Propagation Delay2、选中需要设置等长的网络,右击,选择Create→Match Group3、更改组名称4、设置好后,会显示MGrp,如下列图。

Allegro16.6约束管理器及使用示例

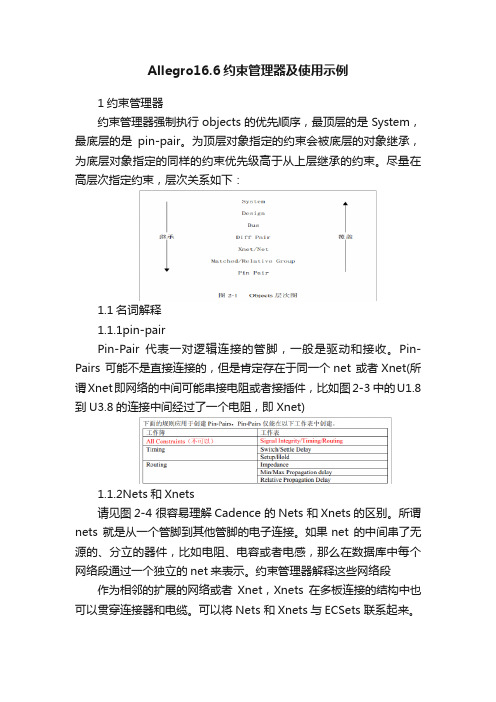

Allegro16.6约束管理器及使用示例1约束管理器约束管理器强制执行objects的优先顺序,最顶层的是System,最底层的是pin-pair。

为顶层对象指定的约束会被底层的对象继承,为底层对象指定的同样的约束优先级高于从上层继承的约束。

尽量在高层次指定约束,层次关系如下:1.1名词解释1.1.1pin-pairPin-Pair代表一对逻辑连接的管脚,一般是驱动和接收。

Pin-Pairs 可能不是直接连接的,但是肯定存在于同一个net 或者Xnet(所谓Xnet即网络的中间可能串接电阻或者接插件,比如图2-3 中的U1.8到U3.8的连接中间经过了一个电阻,即Xnet)1.1.2Nets和Xnets请见图2-4 很容易理解Cadence 的Nets 和Xnets的区别。

所谓nets 就是从一个管脚到其他管脚的电子连接。

如果net 的中间串了无源的、分立的器件,比如电阻、电容或者电感,那么在数据库中每个网络段通过一个独立的net来表示。

约束管理器解释这些网络段作为相邻的扩展的网络或者Xnet,Xnets在多板连接的结构中也可以贯穿连接器和电缆。

可以将Nets 和Xnets与ECSets 联系起来。

1.1.3Match GroupsMatch Group 是nets,Xnets或者pin-pairs 的集合,此集合一定要都匹配(delay 或者length)或者相对于组内的一个明确的目标。

如果delta 值没有定义,组内的所有成员都将是绝对匹配的,并允许有一定的偏差。

如果定义了delta 值,那么组内所有成员将相对匹配于明确的目标网络。

1.2在线检查设置首先在约束管理器中需要进行以下设置Analyze -> Analysis Modes这样在布线后,在相应的地方都会显示线长或约束相差值;如下图1.3示例通过一个实例来理解约束管理器U1看作是MCU,U2为DDR,ADDR0-3为地址线,需要作等长处理;CLK为时钟线,差分处理;U3,U4为连接同一个MCU的DDR;地址线是复用的,设置通过T型网络连接;需要作等长处理U5为DDR,DDR_DQ0-3为数据线,需要作等长处理1.3.1差分对约束即上图中的DDR_CLKP,DDR_CLKN设置Electrical ->Electrical Constraint Set -> Differential Pair 在Object的Name下方Project右键Create -> Electrical CSet;并输入参数差分对约束参数主要有以下几个:Min line spacing:内间距最小线距,若实际走线内间距小于这个值,DRC就会出错。

Allegro如何设定线长限制

Allegro如何设定线长限制Allegro如何设定线长限制Allegro如何设定线长限制1,打开allegro setup---electrical constraintspreadsheet-->net-->routing-->relative propagation delay2,鼠标右键system下面的文件名(brd 文件名)-->creat-->match group-->输入一个自定义的name(比如PCI1) 3,鼠标右键PCI1--membership-->match group-->选中所有需要长度设定的net到members4,pin pairs 选longest pin pair, scope选global relativedelay-->delta:tolerance(mil),在下面填入公差(比如0mil:100mil)5,route 完成以后actual里面就会有net 长度显示,如果全部绿色则满足规则,所有的net相互之间的长度差别在100mil以内如果是红色的,则说明不满足规则,看正负分别表示长或者短,调整至绿色ok VIA的=S=规则我们一般用0.35mm或者0.5mm的孔,基本原则是纵横比PCB THICKNESS/VIA<8,在此前提下孔径越大,板厂越容易做,但是鉴于板子的密度和通过电流的大小,需要选取一个合适的孔径要不要塞孔一般是根据工艺来的,塞孔的目的主要是防止焊接过程中会有锡珠掉落在孔内,引起短路;大于0.35MM的孔一般用树脂塞孔,不用绿油塞,为了测试的时候避免效果不好,因为绿油会流动到另外一面还有一个目的就是做COA TING的时候,如果COATING区域有大于0.45MM的孔,就要塞上,防止清漆从孔漏到另一面去,引起焊接不良BGA底部的过孔:如果不是测试点,都需要塞孔处理,防止短路及藏锡珠。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Allegro等长线Xnet约束设置

2010-11-11 11:31:00| 分类:cadence,orcad,al | 标签:|字号大中小订阅

Allegro中等长约束:

1排阻等设置为Xnet:Analyze->SI/EMI Sim->Model YES

2, 直接在DevType Value/Refdes中选择要设定Model 的器件或直接在板子上点选要设置Model的器件;

3, 点选Create Model,建立该零件的Model,(如果已经有该零件的Model,并在前面定义,然后

Find Model即可,这里主要介绍没有的情况)

在出现对话框中选择Create ESpiceDevice model,点击OK

ModelName: 输入产生Model的名字

Circuit type: 选择Type, 电阻,电感或电容

Value: 值

Single Pin: 各Pin的连接顺序, 中间为空格,

这里要注意要看零件的pin的排列,

1 2 3 4 5 6 7 8,就是: 1和2是一个电阻,其它同理

所以如果就是普通电阻电容那就更简单了.

Common Pin: 这里不用管它,空着就可以.

上面都输入好了就点击OK,完成Model的建立.

点击OK退出就可以发现连接该排阻的两边的Net都有了个Xnet属性:

这样就可以搞定Xnet,很简单吧!

下面就开始等长设置吧!

第二部分针对Xnet部分的等长设置

设置好了Xnet后就可以在Allegro中设置该Xnet的等长了,有两种方法可以设置Xnet的等

长.

第一种, 使用Edit>Properties定义

注意必须使用Pin Pair 才能定义Xnet等长

RELATIVE_ PROPAGATION_DELAY= GroupX : G : U1.5 : U2.4 : 0 : 20

在没有定义Xnet之前这样定义时会提示错误的

其它的和前面的等长设置方法都一样.

第二种, Constraint Manager 设置

1, 开启Constraint Manager, 点选菜单Setup>Electrical Constraint Spreadsheet或直接点击工具栏

出现Constraint Manager 窗体:

对于Constraint Manager 的一般使用方法这里不再做详细介绍, 如果用户对这部分不熟悉

可以参考其它有关Constraint Manager 使用进行学习.

2, 因为我们目的是要设置等长, 所以我们用Relative Propagation Delay这属性, 从左边控制栏中选择Net>Routing>Relative Propagation Delay,

3, 在右边就会显示整块板子所有的Net或Xnet,

4, 建立需要等长的Pin Pair, 右键点击需要建立Pin Pair 的Xnet

选择起始Pin和结束Pin,

注意: 1, 这里没有先后顺序.

2, 如果Pin Pair 的两个Pin Type全是Passive的话不能Creat, 所以这里还需要定义一

下Pin的形态, 如:Out put, In put, Bidirectional等

下面是介绍如何在Allegro中定义Pin type。

如何在Allegro中定义Pin Type?

1,点击菜单Edit>Properties…

2,在Find栏位中仅勾选Pin

3,直接在PCB中选中需要修改Pin Type的Pin

1、crmg里面,Analysis->Analysis Mode,把Relative Propagation勾上

2 需要等长的线做成一组Match Group

3、Realtive Dealy,Delta Tolerence栏,需要做Target的线那一栏点击右键,Set as target。