北大数字集成电路--3_cadence仿真简介

cadence简介和使用基础

CMOS电路原理图设计

或者CIW窗口→File→Open(打开已有的 Cellview)。

CMOS电路原理图设计

也可以在Library Manager中直接打开。

Cadence的使用基础

双击Schematics,出现原理图编辑器

Cadence的使用基础

之后出现Symbol Generation Options窗口。

Cadence的使用基础

出现界面:

Cadence的使用基础

可将上图修改为惯用图形,以CMOS反相器为例。

CMOS电路原理图设计

电路仿真 仿真环境简介

Schematic图形窗口→Tools→Analog Environment。

Cadence的使用基础

Cadence的使用基础

基本工作环境

局域网资源

Cadence的使用基础

用户登陆 微机登陆后,点击桌面X-manager 图标,

Cadence的使用基础

打开X-manager图标后,点击xstart 图标,出现对话 框,进行如下设置:

Cadence的使用基础

登录时出现Linux-CDE (Common Desktop Environment) 界面

一、 cadence简介和使用

集成电路设计软件技术介绍

EDA技术的概念

EDA技术是在电子CAD技术基础上发展起来 的计算机软件系统,是指以计算机为工作平台, 融合了应用电子技术、计算机技术、信息处理 及智能化技术的最新成果,进行电子产品的自 动设计

EDA工具的功能

利用EDA工具,电子设计师可以从概念、算法、 协议等开始设计电子系统,大量工作可以通过 计算机完成,并可以将电子产品从电路设计、

微电子集成电路设计仿真软件使用介绍

流扫描分析中在每一步允许迭代的次数,通过增加迭代次数,可以在电压或电流变 化很快的点收敛 。 由于MOS管线性区和饱和区之间的不连续,Newton-Raphson算法在不连续点处进 行迭点计算产生震荡,可以通过增减仿真步长值或改变仿真初始值(范围)来保证收 敛。 瞬态分析不收敛主要是由于快速的电压变化和模型的不连续,对于快速的电压变化 可以通过改变分析的步长值来保证收敛。 瞬态分析,默认采用Trapezoidal算法,精度比较高,但容易产生寄生振荡,采用 GEAR算法作为滤波器可以滤去由于算法产生的振荡,具有更高的稳定性。 瞬态分析先进行直流工作点的计算,将计算结果作为瞬态分析在T0时刻的初始值, 再通过Newton-Raphson算法进行迭代计算,在迭代计算过程中时间步长值是动态变 化的,.tran tstep中的步长值并不是仿真的步长值,只是打印输出仿真结果的时间间 隔的值,可以通过调整.options lvltim imax imin来调整步长值 。

将原来的扩展名改 为.sp

黑龙江大学集成电路与集成系统

Capture ——标注

如果生成网 表不成功, 一般表示有 重复定义的 器件

集成电路CAD设计

点击Annotate按钮,弹 出annotate对话框

选择第二项 unconditinal reference update

黑龙江大学集成电路与集成系统

O

黑龙江大学集成电路与集成系统

Capture ——打开项目

集成电路CAD设计

.DSN 具体的电路设计文件 .opj 工程文件

北大数字集成电路课件--3_cadence仿真简介

Versus 交互式编译仿真

• Verilog-XL仿真器是与 仿真器是与Verilog HDL同时开发的,因 同时开发的, 仿真器是与 同时开发的 此它成为Verilog HDL仿真器的事实上的标准。 仿真器的事实上的标准。 此它成为 仿真器的事实上的标准

•

Verilog-XL采用了多种加速算法,对每种抽象级描述 采用了多种加速算法, 采用了多种加速算法 都能很好的仿真。这些加速算法包括Turbo算法, 算法, 都能很好的仿真。这些加速算法包括 算法 XL算法及 算法及Switch-XL算法。在后面的教程中将对这 算法。 算法及 算法 些算法进行更为详尽的介绍。 些算法进行更为详尽的介绍。

Cadence Verilog仿真器 仿真器

• Verilog-XL和NC Verilog仿真器都是基于事件算法的 和 仿真器都是基于事件算法的 仿真器。仿真器读入Verilog HDL描述并进行仿真以 仿真器。仿真器读入 描述并进行仿真以 反映实际硬件的行为。 反映实际硬件的行为。 • Verilog-XL和NC Verilog仿真器遵循 和 仿真器遵循IEEE 1364 仿真器遵循 Verilog规范制定的基于事件的调度语义 规范制定的基于事件的调度语义 • 仿真器可用于

NC Verilog有什么不同? 有什么不同? 有什么不同

NC Verilog为编译的元件及其它文件建立一个库结构。增 量编译依赖于源文件、SDF文件和命令行参数。

• • 这些只影响运行时间的参数外, 除+gui、-q和-s这些只影响运行时间的参数外,其它任何命令行 、 和 这些只影响运行时间的参数外 参数的改变将使设计重新编译、 及仿真。 参数的改变将使设计重新编译、elaborate及仿真。 及仿真 如果更新了源文件及仿真时用到的SDF文件,则与它们相关的文 文件, 如果更新了源文件及仿真时用到的 文件 件将重新编译,设计也将重新elaborate和仿真。 和仿真。 件将重新编译,设计也将重新 和仿真 在调试时有完全的读、写及连接操作, 在调试时有完全的读、写及连接操作,用 +access + argument ncverilog –f run.f + access+RWC 要得到源文件行操作能力, 要得到源文件行操作能力,用+linedebug ncverilog -f run.f +linedebug 强制重编译所有设计单元,使用+noupdate 强制重编译所有设计单元,使用

cadence仿真工具介绍1

( TB ( TO ( GT ( W1 ( A1 ( W2 ( A2 ( W3 ( A3

"nwell" ) "diff" ) "poly" ) "cut" ) "metal" ) "cut" ) "metal" ) "cut" ) "metal" )

COPYRIGHT FOR ZHOUQN

COPYRIGHT FOR ZHOUQN

原理图编辑窗口结构分类编辑命令菜单常用快捷命令菜单1instance调用库单元cellview浏览器librarycellviewnameoption阵列行数列数旋转x镜像y镜像variable如果有2addpin调用端口pinpinnames总线命名方式总线名放置方式pin的旋转和镜像3addwire连线narroworwide4wirename连线命名连线规则连线粗细连线名称连线名称的相关属性10属性参数修改9undo11chechandsave12save5放大缩小8删除6stretch拉动保持连接7copy从分类菜单中可以看到命令的快捷键和许多其它命令仿真环境设置版图设计基本过程和要求在一定工艺下根据电路的要求依据版图设计规则设计每个器件的图形并完成排版布线形成一套完整的电路光刻掩膜版图形

COPYRIGHT FOR ZHOUQN

版图主要编辑命令 (2)修改类命令 ) Undo, Redo , Move, Copy, 拉动,改变形状, 拉动,改变形状, 删除,查找, 删除,查找, 合并图形, 合并图形, 制作单元, 制作单元, 打散单元, 打散单元, 劈切图形, 劈切图形, 胀缩图形, 胀缩图形, 旋转图形等等。 旋转图形等等。

CADENCE仿真流程

CADENCE仿真流程1.设计准备在进行仿真之前,需要准备好设计的原理图和布局图。

原理图是电路的逻辑结构图,布局图是电路的物理结构图。

此外,还需要准备好电路的模型、方程和参数等。

2.确定仿真类型根据设计需求,确定仿真类型,包括DC仿真、AC仿真、时域仿真和优化仿真等。

DC仿真用于分析直流电路参数,AC仿真用于分析交流电路参数,而时域仿真则用于分析电路的时间响应。

3.设置仿真参数根据仿真类型,设置仿真参数。

例如,在DC仿真中,需要设置电压和电流源的数值;在AC仿真中,需要设置信号源的频率和幅度;在时域仿真中,需要设置仿真的时间步长和仿真时间等。

4.模型库选择根据设计需求,选择合适的元件模型进行仿真。

CADENCE提供了大量的元件模型,如晶体管、二极管、电感、电容等。

5.确定分析类型根据仿真目标,确定分析类型,例如传输功能分析、噪声分析、频率响应分析等。

6.仿真运行在仿真运行之前,需要对电路进行布局和连线。

使用CADENCE提供的工具对电路进行布局和连线,并生成物理设计。

7.仿真结果分析仿真运行后,CADENCE会生成仿真结果。

利用CADENCE提供的分析工具对仿真结果进行分析,观察电路的性能指标。

8.优化和修改根据仿真结果,对电路进行优化和修改。

根据需要,可以调整电路的拓扑结构、参数和模型等,以改进电路的性能。

9.再次仿真和验证根据修改后的电路,再次进行仿真和验证,以确认电路的性能指标是否得到改善。

最后需要注意的是,CADENCE仿真流程并不是一成不变的,根据具体的设计需求和仿真目标,流程可能会有所调整和修改。

此外,CADENCE还提供了许多其他的工具和功能,如电路板设计、封装设计、时序分析等,可以根据需要进行使用。

cadence简介

实际上,机房中我们已将各配置文件写好,只要在终端中执行

cds.setup

Cadence的相关配置文件就已经自动设置完毕。如果用户在启动Cadence后,发现无法使用快捷键,则需要把.cdsinit从Cadence的安装目录中拷贝到自己的工作目录下,在终端中输入:

此外还有一个What’new窗口,介绍Cadence新版本特性,不必理会,双击左上角将其关闭。

2.5

Cadence是以库来组织文件的。为了使我们的工作和系统自带库区别,我们需要建立自己的工作库。有两种方法来建立新库,一是通过菜单栏Tools->Library Maneger打开库管理器,另一种是通过File->New->Library来建立新库。这里我们用第一种方法建立新库。单击菜单栏Tools->Library Maneger,会打开LM(Library Maneger)窗口,如图2.3所示。

②点击工具栏的zoomin和zoomout按钮可以放大缩小电路图。键入快捷键f可以使电路图自动缩放到合适大小。

③编辑电路图过程中注意要及时保存,保存方法是菜单栏->Design->Save,也可以键入快捷键大写的S(Shift+s)来保存。

3

现在,我们要开始画一个标准的CMOS反相器。一个反相器包括PMOS,NMOS,VDD,GND。

同样的方法继续设置NMOS参数,只是模型名为n18,栅长为固定值0.18u,栅宽设为pPar(“wn”)。设置好参数后的电路图如图3.9所示。

注意:①设置参数时不要自己输入单位,系统会自动加上。比如0.18uM是错误的写法。如果非要自己写单位,也要和数值之间留一个空格,否则系统会把M识别为变量。

1 cadence简介

培训资料(1)

Cadence入门教程

2006-7-19

一、

作为流行的EDA工具之一,Cadence一直以来以其强大的功能受到广大EDA工程师的青睐。Cadence可以完成整个IC设计流程的各个方面,如电路图输入(Schematic Input)、电路仿真(Analog Simulation)、版图设计(Layout Design)、版图验证(Layout Verification)、寄生参数提取(Layout Parasitic Extraction)以及后仿真(Post Simulation)。如图1.1所示,我们给出了一个简单的模拟集成电路设计流程,以及对应的Cadence工具。

Composer主界面包括:标题栏,菜单栏,工具栏,状态栏(第二行),提示区(就是最底下那行)以及最大的那个工作区。标题栏和菜单栏没什么好说的,状态栏会提示当前的命令以及所选择的物体个数,提示区会告诉你当前应该做什么事。作为初学者,在设计电路过程中应该要仔细阅读提示区中的信息。此外,

注意:①Composer中的多数命令会一直保持,直到你调用其它命令替代它或者按Esc取消,尤其是在执行delete命令时,忽视这一点很可能会误删除,一定要多加小心!Composer的Undo操作默认只能进行一次(可以在CIW窗口的Option->User Preferences中修改,最多可以是10)。所以每完成一个命令,记着按ESC取消当前命令。

.cdsinit文件:包含Cadence的一些初始化设置以及快捷键设置。

实际上,机房中我们已将各配置文件写好,只要在终端中执行

cds.setup

Cadence的相关配置文件就已经自动设置完毕。如果用户在启动Cadence后,发现无法使用快捷键,则需要把.cdsinit从Cadence的安装目录中拷贝到自己的工作目录下,在终端中输入:

cadence简介

EDA概述

• EDA技术特征:

(1)硬件采用工作站和PC机。 (2)具有IP模块化芯核的设计和可重复利用功能。 (3)EDA技术采用高级硬件描述语言描述硬件结构、参 数和功能,具有系统级仿真和综合能力。

EDA概述

• EDA工具一般由两部分组成:

逻辑工具 物理工具

物理工具主要实现物理布局布线。 逻辑工具基于网表、布尔逻辑、传输时序等概念。 该两部分由不同工具承担,利用标准化的网表文件进行 数据交换。

• Synopsys公司简介:

是为全球集成电路设计提供电子设计自动化(EDA) 软件工具的主导企业。为全球电子市场提供技术先进的 IC设计与验证平台,致力于复杂的芯片上系统(SoCs)的 开发。总部设在美国加利福尼亚州Mountain View,有 超过60家分公司分布在北美、欧洲、日本与亚洲。 提供前后端完整IC设计方案的领先EDA工具供应商。 是EDA历史上第一次由一家EDA公司集成了业界最好的 前端和后端设计工具。

第二章 EDA概述

• 电子设计自动化(EDA:Electronic Design Automation)就是利用计算机作为工作平台进 行电子自动化设计的一项技术。 • 涵盖内容:系统设计与仿真,电路设计与

仿真,印制电路板设计与校正,集成电 路版图设计数模混合设计,嵌入式系统 设计,软硬件系统协同设计,系统芯片 设计,可编程逻辑器件和可编程系统芯 片设计,专用集成电路设计等

EDA概述

• 软核IP(soft IP)是用可综合的硬件描述语言描述的 RTL级电路功能块,不涉及用与什么工艺相关的电路 和电路元件实现这些描述。 • 优点:设计周期短,设计投入少,不涉及物理实现, 为后续设计留有很大发挥空间,增大了IP的灵活性和 适应性。 • 缺点:会有一定比例的后续工序无法适应软核IP设计, 从而造成一定程度的软核IP修正,在性能上有较大的 不可预知性。

集成电路版图基础-Cadence工具简介

(2) ERC(Electrical Rule Check) 电学规则检 查。

(3) LVS(Layout Versus Schemati) 版图和电 路图一致性比较

(4) LPE(Layout Parameter Extruction) 版 图寄生参数提取

或快捷键k或点击图标

2)点击任意所需一点为起点 3)移动鼠标到空白处再次点击完成标尺 4) 按<Esc>键停止标尺命令 5)按shift+k 清除所有标尺

反相器版图实例

在P型衬底上制作CMOS反相器,需要一个 PMOS管和一个NMOS管。其中PMOS管制 作在N阱中,包含有源扩散区、多晶硅栅; NMOS管包含有源扩散区、多晶硅栅。

选择Verify-probe菜单,在弹出窗口中可以 选择查看连接关系。

3、 LVS

Layout vs. schematic comparison(版 图与电路对比),检查设计完成的版图是 否与原电路相符。

在版图编辑窗口菜单中选择verify-LVS 即 可打开对话框。

注意:如果之前运行过LVS,此时会出现一 个提示窗口。选中form contents(重新创 建LVS文件内容) ,继续LVS。

如果验证成功,返回LVS窗口,单击 “output”按钮,查看验证报告。

LVS验证报告:

错误类型

错误位置

错误原因

错误数量

错误原因

快捷键 p c q

Shift+k Shift+z

3、LSW:

layer select window(图层选 择窗口)。该窗口显示设计版 图所用的工艺库文件的位置、 可供选择和当前选中的版图图 层,以及各图层的图样属性。

精选cadence运放仿真资料

分析类型介绍

Tran分析:时间与电路参数的关系

(瞬时分析)

DC分析: 电压与电路参数的关系

(直流分析)

AC分析: 频率与电路参数的关系

(交流分析)

6/27/2019

三、模拟仿真的设置(重点)

Composerschamatic界面中的 Tools → Analog Environment项可以 打开Analog Design Environment 窗口, 如右图所示。

6/27/2019

Analog Design Simulation菜单介绍

Session菜单

Schematic Window Save State Load State Options Reset Quit

回到电路图

6/27/2019

保存当前 所设定的 模拟所用 到的各种

参数

加载已 经保存 的状态

cdsSpice hspiceS spectre等

设置模拟 时的温度

设置库文件 的路径和仿

真方式

设置仿真的 环境

(后仿真时 需设置)

6/27/2019

Analyses菜单

选择模拟类型。Spectre 的分析有很多种,如右图, 最基本的有

tran(瞬态分析) dc(直流分析) ac(交流分析)。

6/27/2019

相位裕度与负载电容的关系曲线仿真

1、设置相位裕度输出,点击Outputs ->Setup

其中运用了Candence函数PhaseMargin

6/27/2019

相位裕度与负载电容的关系曲线仿真

2、点击Tools-> Parametric Analysis设置负载电容的扫描范 围和扫描步长,其中Range Type选择From/To,Step Control选择Linear Steps

集成电路版图基础-Cadence工具简介篇00

(b)

3. 复制(Copy) 1)复制命令Edit→copy,或快捷键c 或点击图标

2)点击目标图形 3)移动鼠标到空白处再次点击完成复制 4) 按<Esc>键停止复制命令

4. 移动(move) 1)复制命令Edit→move,或快捷键m 或点击图标

2)点击目标图形 3)移动鼠标到空白处再次点击完成移动 4) 按<Esc>键停止移动命令

k

Shift+k

Shift+z

Zoom in(放大) Ctrl+z

3、LSW:

layer select window(图层选 择窗口)。该窗口显示设计版 图所用的工艺库文件的位置、 可供选择和当前选中的版图图 层,以及各图层的图样属性。 如右图显示当前所用工艺库文 件位于“MYLIB”目录下,当前 选择的图层为“active”。

注意:如果之前运行过LVS,此时会出现 一个提示窗口。选中form contents(重新 创建LVS文件内容) ,继续LVS。

如果验证成功,返回LVS窗口,单击 “output”按钮,查看验证报告。

LVS验证报告:

错误类型

错误位置

错误原因

错误数量

错误原因

Cadence工具简介

光电工程学院

王智鹏

一、浏览电路

Cadence virtuoso 基于linux操作系统, 主要包括电路系统设计工具、版图设计工 具和版图验证工具。软件启动后,会看到 全局管理窗口——CIW

在CIW窗口中点击“Tools”,选择 “library manager”打开库文件管理器。 并从中单击选择所需的library—cell—view, 双击“schematic”打开目标电路图。

cadence使用教程

cadence使用教程Cadence是一种电路设计和仿真软件,非常适合电子工程师用于电路设计和分析。

在本教程中,我们将介绍如何使用Cadence进行基本的电路设计和仿真。

首先,打开Cadence软件,并新建一个新项目。

请确保你已经安装了Cadence软件,并且拥有一个有效的许可证。

在新项目中,你需要定义电路的基本参数,如电源电压、电阻值等。

可以通过绘制原理图的方式来完成这些参数的定义。

在绘图界面中,你可以选择不同的元件,包括电源、电阻、电容、电感等。

你可以使用菜单栏中的工具来放置和连接这些元件。

一旦电路图绘制完成,你可以对电路进行仿真。

首先,需要选择合适的仿真器。

Cadence提供了多种仿真器,如Spectre和HSPICE。

选择一个适合你电路的仿真器,并设置仿真参数,如仿真时间、仿真步长等。

在仿真之前,你首先需要对电路进行布局。

布局涉及将电路中的元件放置在芯片上,并根据布线规则进行连接。

Cadence提供了强大的布局工具,可以帮助你完成这个过程。

完成布局后,你可以进行后仿真。

后仿真涉及将布局好的电路导入到仿真器中,并进行仿真分析。

你可以查看电路的性能指标,如电压、电流和功耗等。

除了基本的电路设计和仿真,Cadence还提供了其他功能,如噪声分析、温度分析和优化设计等。

你可以根据需要选择适合的功能。

总的来说,Cadence是一个功能强大的电路设计和仿真软件。

通过本教程,你可以学会如何使用Cadence进行基本的电路设计和仿真。

希望这对你的电子工程项目有所帮助。

Cadence软件介绍【范本模板】

Cadence软件介绍Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。

Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面有着绝对的优势。

Cadence 包含的工具较多几乎包括了EDA 设计的方方面面.下面主要介绍其产品线的范围.1、板级电路设计系统包括原理图输入、生成、模拟数字/混合电路仿真,fpga设计,pcb编辑和自动布局布线mcm电路设计、高速pcb版图的设计仿真等等。

包括:A、Concept HDL原理图设计输入工具, 有for NT和for Unix的产品。

B、Check Plus HDL原理图设计规则检查工具.(NT & Unix)D、Allegro Expert专家级PCB版图编辑工具(NT & Unix)E、SPECTRA Expert AutoRouter 专家级pcb自动布线工具F、SigNoise信噪分析工具G、EMControl 电磁兼容性检查工具H、Synplify FPGA / CPLD综合工具I、HDL Analyst HDL分析器J、Advanced Package Designer先进的MCM封装设计工具2、Alta系统级无线设计这部分包括:A、SPW (Cierto Signal Processing Work System)信号处理系统.可以说,spw包括了matlab的很多功能,连demo都有点象.它是面向电子系统的模块化设计、仿真和实现的环境.它的通常的应用领域包括无线和有线载波通信、多媒体和网络设备.在进行算法设计、滤波器设计、c Code生成、软/硬件结构联合设计和硬件综合的理想环境.它里面非常有意思的就是信号计算器。

B、HDS (Hardware Design System)硬件系统设计系统它现在是SPW的集成组件之一.包括仿真、库和分析扩展部分。

可以进行spw的定点分析行为级和rtl级的代码生成.C、Mutimedia多媒体(Multimedia Design Kit)它可以进行多媒体应用的设计,包括电视会议系统、数字电视等等以及任何种类的图象处理系统的设计。

Cadence软件在《模拟电子》仿真教学的应用

Cadence软件在《模拟电子》仿真教学的应用随着科技的发展,电子技术在我们生活中扮演着越来越重要的角色。

而在电子技术的学习和研究过程中,仿真技术则起到了至关重要的作用。

Cadence是一款著名的EDA (Electronic Design Automation)软件,它在电子设计和仿真领域具有广泛的应用。

在《模拟电子》的教学中,Cadence软件的应用能够帮助学生更好地理解和掌握电子电路的设计和仿真技术,从而提高他们的学习效率和实际应用能力。

一、Cadence软件简介Cadence公司成立于1988年,总部位于美国加利福尼亚州圣荷西市。

作为全球领先的EDA软件和工程服务供应商,Cadence公司主要致力于开发应用于集成电路和电子系统设计的EDA软件和工具。

Cadence软件包括了多种产品系列,如Allegro系列、OrCAD系列、Virtuoso系列等,涵盖了电路设计、电路仿真、布局设计等方面的功能,为电子工程师在设计和验证电路时提供了强大的支持。

1. 电路设计与验证Cadence软件提供了丰富的电路设计工具和功能模块,学生可以使用Cadence软件进行各种类型的电路设计,如模拟电路、数字电路、混合信号电路等。

通过Cadence软件,学生能够快速、准确地完成电路设计,并进行相应的验证与分析。

学生可以在Cadence软件中建立各种电路图,选择合适的元器件和信号源,并进行仿真和分析,从而加深对电路原理和设计方法的理解。

2. 仿真实验与参数优化3. 电路分析与报告生成在电子电路的教学过程中,学生需要进行电路分析和实验报告的生成。

Cadence软件提供了丰富的电路分析工具和报告生成功能,能够帮助学生对电路的工作原理和性能进行深入的分析,并生成相应的实验报告。

学生可以通过Cadence软件进行电路的频域分析、时域分析、交流分析、直流工作点分析等,从而全面了解电路的工作特性和性能参数,并撰写详细的实验报告。

Cadence仿真工具的介绍

深圳市共进电子有限公司

设置约束及赋予PCB

1,执行Set -> Constraints…启动Set Topology Constrains界面 :

深圳市共进电子有限公司

设置约束及赋予PCB

•

Switch-Settle项 :

Cadence仿真工具的介绍

更新日期:2010.05

深圳市共进电子有限公司

培训目的

介绍Cadence仿真工具的使用, 以便帮助大家更好的利用设计工 具来提升设计效率

学习重点

1、调用并运行设置向导 2、仿真参数设置 3、提取和建立拓朴进行仿真

培训对象

Layout工程师,

深圳市共进电子有限公司

提取和建立拓朴进行仿真

Sigxlorer的界面:

深圳市共进电子有限公司

提取和建立拓朴进行仿真

• • SigXplorer中的仿真参数设置 Pulse Stimulus标签栏:

深圳市共进电子有限公司

Xnet包含所有的通过电阻、电容或连接器连接的Driver和Receiver。Xnet是 一种抽取的网络。

深圳市共进电子有限公司

提取和建立拓朴进行仿真

• 在PCB SI的Constraint Manager中抽取拓扑

•

• • • •

1、选择菜单Constraints\Electrical Constraint Spreadsheet; 2、左边的树状窗口选择Net\Routing\Wiring; 3、选择菜单Tools\Options,设置参数; 4、在约束管理器右边的网络列表中找到并选择网络,点 击右键在弹出的菜单中选择SigXplorer菜单选项 5、在SigXplorer界面中,选择菜单File=》Save As,输 入文件名,保存一下提取的拓朴模型。

Cadence仿真简介

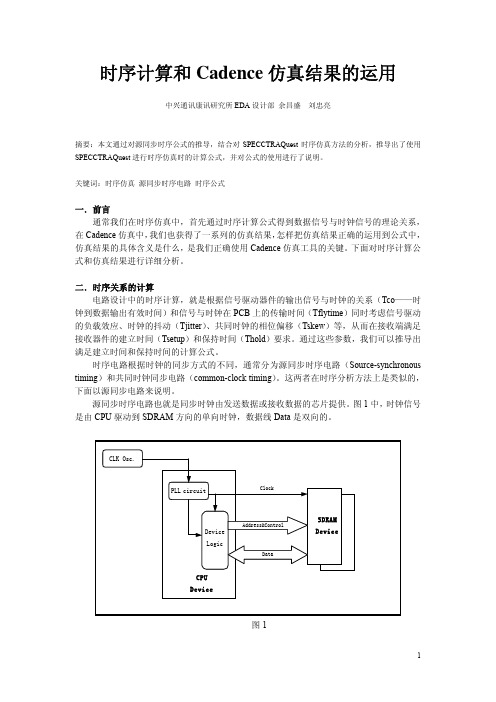

时序计算和Cadence仿真结果的运用中兴通讯康讯研究所EDA设计部余昌盛刘忠亮摘要:本文通过对源同步时序公式的推导,结合对SPECCTRAQuest时序仿真方法的分析,推导出了使用SPECCTRAQuest进行时序仿真时的计算公式,并对公式的使用进行了说明。

关键词:时序仿真源同步时序电路时序公式一.前言通常我们在时序仿真中,首先通过时序计算公式得到数据信号与时钟信号的理论关系,在Cadence仿真中,我们也获得了一系列的仿真结果,怎样把仿真结果正确的运用到公式中,仿真结果的具体含义是什么,是我们正确使用Cadence仿真工具的关键。

下面对时序计算公式和仿真结果进行详细分析。

二.时序关系的计算电路设计中的时序计算,就是根据信号驱动器件的输出信号与时钟的关系(Tco——时钟到数据输出有效时间)和信号与时钟在PCB上的传输时间(Tflytime)同时考虑信号驱动的负载效应、时钟的抖动(Tjitter)、共同时钟的相位偏移(Tskew)等,从而在接收端满足接收器件的建立时间(Tsetup)和保持时间(Thold)要求。

通过这些参数,我们可以推导出满足建立时间和保持时间的计算公式。

时序电路根据时钟的同步方式的不同,通常分为源同步时序电路(Source-synchronous timing)和共同时钟同步电路(common-clock timing)。

这两者在时序分析方法上是类似的,下面以源同步电路来说明。

源同步时序电路也就是同步时钟由发送数据或接收数据的芯片提供。

图1中,时钟信号是由CPU驱动到SDRAM方向的单向时钟,数据线Data是双向的。

图1图2是信号由CPU 向SDRAM 驱动时的时序图,也就是数据与时钟的传输方向相同时的情况。

Tsetup ’Thold ’ CPU CLK OUTSDRAM CLK INCPU Signals OUT SDRAM Signals INTco_minTco_max T ft_clkT ft_dataT cycleSDRAM ’S inputs Setup time SDRAM ’S inputs Hold time图2图中参数解释如下:■ Tft_clk :时钟信号在PCB 板上的传输时间;■ Tft_data :数据信号在PCB 板上的传输时间;■ Tcycle :时钟周期■ Tsetup’:数据到达接收缓冲器端口时实际的建立时间;■ Thold’:数据到达接收缓冲器端口时实际的保持时间;■ Tco_max/Tco_min :时钟到数据的输出有效时间。

(参考资料)Cadence的使用与基本仿真教程

Cadence的使用与基本仿真教程2014/11/9模拟集成电路设计课程实验1Outline启动Cadence新建Library 与Cell View常用快捷键常用库常用库、、器件基本仿真基本仿真指导指导仿真练习a)CS,CG,SF 电路仿真b)差分差分对电路仿真对电路仿真c)CS-CG 电路仿真2014/11/9模拟集成电路设计课程实验2启动Cadence在桌面上鼠标右击在桌面上鼠标右击,,open terminal >cd ~(回到home 目录下)>icfb &启动Cadence 。

上课时部分同学遇到问题是由于没有在home 目录下打开Cadence 2014/11/9模拟集成电路设计课程实验3新建LibraryFile>new>library2014/11/9模拟集成电路设计课程实验4新建Library起个名字>Don’t need a techfile>OK2014/11/9模拟集成电路设计课程实验5打开Library ManagerTools>Library Manager2014/11/9模拟集成电路设计课程实验6显示器件分类Show Category可以显示器件的分类2014/11/9模拟集成电路设计课程实验7显示器件分类例如例如::在tsmc018rf 库中的分类有库中的分类有::电容电容、、电阻电阻、、MOS 管等等管等等。

2014/11/9模拟集成电路设计课程实验8新建Cell ViewFile>New>Cell View2014/11/9模拟集成电路设计课程实验9新建Cell View将新建的Cell View 设定在之前新建的Library 下>起个名字>OK 2014/11/9模拟集成电路设计课程实验10快捷键快捷键::i2014/11/9模拟集成电路设计课程实验11快捷键快捷键::w2014/11/9模拟集成电路设计课程实验12快捷键快捷键::c2014/11/9模拟集成电路设计课程实验13快捷键快捷键::q2014/11/9模拟集成电路设计课程实验14快捷键快捷键::r2014/11/9模拟集成电路设计课程实验15常用库常用库、、器件2014/11/9模拟集成电路设计课程实验16搭建反相器仿真电路照图搭建反相器仿真电路2014/11/9模拟集成电路设计课程实验17设置PMOS参数:参数:设置PMOS参数将w设置为6μm2014/11/9模拟集成电路设计课程实验18设置电压源vpulse 参数设置vpulse 参数参数::AC magnitude :1DC voltage:Vdc (设为变量Vdc )Voltage 1:0Voltage 2:1.8Pulse width :1nPeriod:2n注意注意::AC 参数的设置不会影响直流工作点DC voltage 决定直流工作点决定直流工作点;;下面四个参数设置时域波形,不影响直流不影响直流。

3、cadence仿真

如图我们可以看出:运放的输出摆幅大约为-2.55V~2.55V

2011-7-14

6、瞬态仿真示例

目标:通过仿真得到运放的摆率 方法:运用瞬态仿真,输入信号设置为电压脉冲,观察输 出电压的变化情况 参数设置: 输入信号源采用analoglib中的脉冲发生器vpwl,输入电压 初始值为0 V,在10n s~10.1n s跳变到4V Tran仿真时间为100n s 在电路图中选择输出变量,Outputs-> To Be Plotted-> Select On Schematic,在这里我们选择输入脉冲以及输 出电压

(交流分析)

2011-7-14

三、模拟仿真的设置(重点) 模拟仿真的设置(重点)

Composerschamatic界面中的 Tools → Analog Environment项可以 打开Analog Design Environment 窗口, 如右图所示。

2011-7-14

Analog Design Simulation菜单介绍 菜单介绍

设置库文件 的路径和仿 真方式

设置仿真的 环境 (后仿真时 需设置)

2011-7-14

Analyses菜单

选择模拟类型。Spectre 的分析有很多种,如右图, 最基本的有 tran(瞬态分析) dc(直流分析) ac(交流分析)。

2011-7-14

tran(瞬态分析) (瞬态分析)

2011-7-14

ac(交流分析) 是分析电路性能随 着运行频率变化而 变化的仿真。 既可以对频率进 行扫描也可以在某个 频率下进行对其它变 量的扫描。

2011-7-14

Variables菜单

包括Edit等子菜单项。 可以对变量进行添加、 删除、查找、复制等操 作。变量variables既可 以是电路中元器件的某 一个参量,也可以是一 个表达式。变量将在参 量扫描parametric analysis时用到。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

时间片 timeslice • 仿真器在编译数据结构时建立一个事件队列。 • 只有当前时间片中所有事件都处理完成后,时间才能向前。 • 仿真从时间0开始,而且时轮只能向前推进。只有时间0的事件处 理完后才能进入下一时片。 • 在同一个时间片内发生的事件在硬件上是并行的 • 理论上时间片可以无限。但实际上受硬件及软件的限制。

–

编译后的所有代码的执行使用同一个核。 当重新启动仿真时,要对修改过的模块重新编译。省略这个手工过程的方 法是直接对设计进行仿真,这将自动地对修改过的模块进行重新编译。

当采用交互模式时,可以使用Tcl命令和针对NC Verilog的Tcl扩展命令。

NC Verilog全编译仿真

• • NC Verilog是最近才开发的,但其对描述的仿真与Verilog-XL完全 相同 NC Verilog仿真器用同一个核(kernel)对所有抽象级进行混合仿真, 也就是说用户可以采用各种不同抽象级混合设计。但在门级仿真的 效率差一些。 NC Verilog仿真器对源代码采用增量编译方式,减少了编译时间。 在交互模式下,可以使用Tcl命令及其针对NC Verilog的扩展命令 来修改设计和控制仿真。这将在后面进行详细描述。

仿真算法

• 基于时间的算法用于处理连续的时间及变量

– 在每一个时间点对所有电路元件进行计算 – 效率低。在一个时间点只有约2~10%的电路活动

• 基于事件的算法处理离散的时间、状态和变量

– 只有电路状态发生变化时才进行处理,只模拟哪些可能引起 电路状态改变的元件。仿真器响应输入引脚上的事件,并将 值在电路中向前传播。 – 是应用最为广泛的仿真算法 – 效率高。“evaluate when necessary”

• •

对Verilog语言的支持

• Verilog-XL和NC Verilog计划支持Verilog语言全集。 用户可依据下列标准进行设计: IEEE1364-1995 Verilog语言参考手册 OVI 2.0 Verilog语言参考手册,但不支持:

Attributes: Verilog描述中对象的属性。 函数中output或inout变元(argument):OVI2.0允许函数中output 和inout变元值能够返回。

• 基于周期的仿真以时钟周期为处理单位(与时间无关)

– – – – 只在时钟边沿进行计算,不管时钟周期内的时序 使用两值逻辑 (1, 0) 只关心电路功能而不关心时序,对于大型设计,效率高 仅适用于同步电路。

基于事件仿真的时轮(time wheel)

一个时间片的事件 可引起新的事件, 在当前时片或以后

Cadence Verilog仿真器

• Verilog-XL和NC Verilog仿真器都是基于事件算法的 仿真器。仿真器读入Verilog HDL描述并进行仿真以 反映实际硬件的行为。 • Verilog-XL和NC Verilog仿真器遵循IEEE 1364 Verilog规范制定的基于事件的调度语义 • 仿真器可用于

第三章 Cadence仿真器

• 学习内容

– 逻辑仿真算法 – 如何启动Verilog-XL和NC Verilog仿真器 – 如何显示波形

仿真算法

• 主要有三种仿真算法

– 基于时间的(SPICE仿真器) – 基于事件的(Verilog-XL和NC Verilog仿真器) – 基于周期的(cycle)

NC Verilog-全编译仿真

• NC Verilog是全编译仿真器,它直接将Verilog代码编 译为机器码执行。其过程为:

– – ncvlog编译Verilog源文件,按照编译指导(compile directive) 检查语义及语法,产生中间数据。 ncelab按照设计指示构造设的数据结构,产生可执行代码。 除非对优化进行限制,否则源代码中的元件(element)可能被优 化丢失。产生中间数据。 ncsim启动仿真核。核调入设计的数据结构,构造事件序列 (时轮),调度并执行事件的机器码。有些事件可能消失(从不 执行)除非限制优化过程。

Versus 交互式编译仿真器

• Verilog-XL是一个交互式仿真器,过程如下:

1. 读入Verilog描述,进行语义语法检查,处理编译指导 (compiler directive) 2. 在内存中将设计编译为中间格式,将所有模块和实例组装成 层次结构(设计数据结构)。源代码中的每个元件都被重新表 示并能在产生的数据结构 找到。 3. 决定仿真的时间精度,在内存中构造一个事件队列的时间数 据结构(时轮) 。 4. 读入、调度并根据事件执行每一个语句 Verilog-XL采用多种加速算法提高各种抽象级的仿真速度。 每次重新启动Verilog-XL,将重复上述步骤。 当进入交互模式时,可以输入Verilog HDL语句并加到设计的数据结构中。

– 初始化

参数初始化;没有驱动的Net缺省值为Z;其它节点初始值 为X。这些值延着设计层次传播。

– 仿真

刚开始时间为0时,仿真器将initial和always中的语句执 行一次,遇到有时序控制时停止。这些赋值可产生在时间 0或其后时间的事件。 随着时间推进,被调度事件的执行引起更多的调度事件, 直至仿真结束。

– – – – 确定想法的可行性 用不同的方法解决设计问题 功能验证 确定设计错误

仿真过程

• Verilog仿真分下列步骤:

– 编译

读入设计描述,处理编译指导(compiler directive),建立 一个数据结构定义设计的层次结构 这一步有时分为两步:compilation,elaboration

Versus 交互式编译仿真

• Verilog-XL仿真器是与Verilog HDL同时开发的,因 此它成为Verilog HDL仿真器的事实上的标准。

•

Verilog-XL采用了多种加速算法,对每种抽象级描述 都能很好的仿真。这些加速算法包括Turbo算法, XL算法及Switch-XL算法。在后面的教程中将对这 些算法进行更为详尽的介绍。