北大集成电路版图设计课件_第8章 MOS场效应晶体管

合集下载

集成电路版图设计 ppt课件

(b)

图8.3 交叠的定义

表8.5 TSMC_0.35μm CMOS工艺版图各层图形之间最小交叠

表 16.5 T SM C _0.35μ m C M O S 工 艺 版 图 各 层 图 形 之 间 最 小 交 迭

N _ w e ll A c tiv e P o ly P _ l\p lu s_ se le c t/N _ p lu s_ se l ect C o n ta c t M e ta l1 V ia 1 M e ta l2 E le c tro d e V ia 2 M e ta l3

MOS管的可变参数为:栅长(gate_length)、栅宽(gate_width) 和栅指数(gates)。

栅长(gate_length)指栅极下源区和漏区之间的沟道长度,最 小值为2lambda=0.4μm。

栅宽(gate_width)指栅极下有源区(沟道)的宽度,最小栅宽为 3 lambda=0.6μm。

201010233636cmos差动放大器单元电路设计版图的过程vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outout图716画l型金属线作地线图717画出两只mcs3并将它们的栅漏和源极互连201010233737vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outout图718画出两只mn1并将它们的栅漏和源极互连cmos差动放大器单元电路设计版图的过程201010233838图719依次画出r1并联的两只msf1和并联的两只mcf1以及偏压等半边电路版图vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outoutcmos差动放大器单元电路设计版图的过程201010233939cmos差动放大器单元电路设计版图的过程vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outout图720通过对图819中半边版图对x轴作镜像复制形成的完整版图201010234040在正式用cadence画版图之前一定要先构思也就是要仔细想一想每个管子打算怎样安排管子之间怎样连接最后的电源线地线怎样走

23-场效应晶体管PPT模板

6.场效应管和三极管都可组成各种放大电路和开关电 路,但由于前者制造工艺简单,且具有耗电少、热稳定性好、 工作电源电压范围宽等优点,因而被广泛应用于大规模和超 大规模集成电路中。

1.5 场效应管的使用注意事项

1.使用场效应管时要注意电压极性,电压和电流的数 值不能超过最大允许值。

2.为了防止栅极击穿,要求一切测试仪器、电烙铁等 都必须有外接地线。焊接时用小功率烙铁,动作要迅速,或 切断电源后利用余热焊接。焊接时,应先焊源极,后焊栅极。

转移特性曲线的斜率gm的大小反映了栅源电压UGS对漏 极电流ID的控制作用。gm的量纲为mA/V,所以,gm又称为 跨导,其定义为:

gm UIDGS(UDS为常数)

(2)输出特性曲线

输出特性曲线是指栅源电压UGS一定时,漏极电流ID与漏 极电压UDS之间的关系曲线ID=f(UDS)。它可分为三个区: 可变电阻区、恒流区和截止区。

电工电子技术

场效应晶体管*

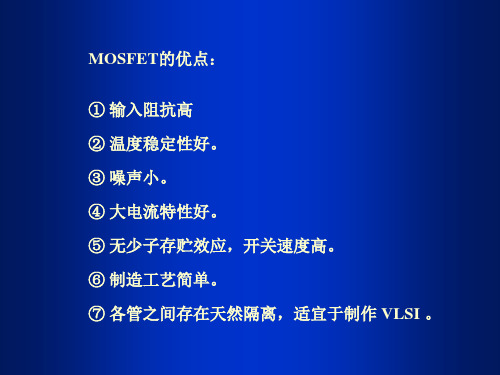

场效应晶体管(FET)是一种利用输入回路的电场效应 来控制输出回路电流的半导体器件,属于电压控制器件。它 只依靠一种载流子参与导电,故又称为单极型三极管。它具 有输入阻抗高、噪声低、热稳定性好、抗辐射能力强、功耗 小、制造工艺简单和便于集成化等优点。

根据结构不同,场效应管可分为结型场效应管(JFET) 和绝缘栅场效应管(MOS管)。由于MOS管的性能更优越, 发展更迅速,应用更广泛,因此,本节将仅介绍MOS管。

由于耗尽型MOS管自身能形成导电沟道,所以只要有 UDS存在,就会有ID产生。如果加上正的UGS,则吸引到反型 层中的电子增加,沟道加宽,ID增大。如果加上负的UGS,则 此电场将会削弱原来绝缘层中正离子的电场,使吸引到反型 层中的电子减少,沟道变窄,ID减小。若负UGS达到某一值, 则沟道中的电荷将耗尽,反型层消失,管子截止,此时的值 称为夹断电压UGS(off)或UP。

1.5 场效应管的使用注意事项

1.使用场效应管时要注意电压极性,电压和电流的数 值不能超过最大允许值。

2.为了防止栅极击穿,要求一切测试仪器、电烙铁等 都必须有外接地线。焊接时用小功率烙铁,动作要迅速,或 切断电源后利用余热焊接。焊接时,应先焊源极,后焊栅极。

转移特性曲线的斜率gm的大小反映了栅源电压UGS对漏 极电流ID的控制作用。gm的量纲为mA/V,所以,gm又称为 跨导,其定义为:

gm UIDGS(UDS为常数)

(2)输出特性曲线

输出特性曲线是指栅源电压UGS一定时,漏极电流ID与漏 极电压UDS之间的关系曲线ID=f(UDS)。它可分为三个区: 可变电阻区、恒流区和截止区。

电工电子技术

场效应晶体管*

场效应晶体管(FET)是一种利用输入回路的电场效应 来控制输出回路电流的半导体器件,属于电压控制器件。它 只依靠一种载流子参与导电,故又称为单极型三极管。它具 有输入阻抗高、噪声低、热稳定性好、抗辐射能力强、功耗 小、制造工艺简单和便于集成化等优点。

根据结构不同,场效应管可分为结型场效应管(JFET) 和绝缘栅场效应管(MOS管)。由于MOS管的性能更优越, 发展更迅速,应用更广泛,因此,本节将仅介绍MOS管。

由于耗尽型MOS管自身能形成导电沟道,所以只要有 UDS存在,就会有ID产生。如果加上正的UGS,则吸引到反型 层中的电子增加,沟道加宽,ID增大。如果加上负的UGS,则 此电场将会削弱原来绝缘层中正离子的电场,使吸引到反型 层中的电子减少,沟道变窄,ID减小。若负UGS达到某一值, 则沟道中的电荷将耗尽,反型层消失,管子截止,此时的值 称为夹断电压UGS(off)或UP。

第八章 数字集成电路基本单元及版图(续)

漏极开路输出单元

如果希望系统支持多个集成电路的正常逻辑 输出同时到总线以实现某种操作,就必须对集成 电路的输出单元进行特殊的设计以支持“线逻 辑”。同时,总线也将做适当的改变。 漏极开路输出单元结构就是其中的一种。下 图给出了两种漏极开路结构的输出单元,其中 (a)图的内部控制信号是通过反相器反相控制 NMOS管工作的方式,(b)图是同相控制的方 式。

动态存储器DRAM (Dynamic RAM)

主要指标:存储容量、存取速度。

存储容量: 用字数×位数表示,也可只用位数表 示。如,某动态存储器的容量为109位/片。 存取速度:用完成一次存取所需的时间表示。 高速存储器的存取时间仅有10ns左右。

存储单元的等效电路(1)

字线 字线

VP 位线 (a) DRAM 位线 (b) SRAM 位线

漏极开路输出单元

(a)反相器反相控制方式

(b)同相控制的方式

漏极开路结构实现的线逻辑

Vcc bi

A1

A2

目的:减少电 AN

表达式为

路结构和成本

bi A1 A 2 A N A1 A 2 A Nห้องสมุดไป่ตู้

输入、输出双向三态单元(I/O PAD)

在许多应用场合,需要某些数据端同时具有输入、输 出的功能,或者还要求单元具有高阻状态。在总线结构的 电子系统中使用的集成电路常常要求这种I/O PAD。下 图是一个输入、输出双向三态的I/O PAD单元电路。

存储单元的等效电路(2)

字线 Cut 位线 (c) 熔丝型ROM 位线 (d) EROM(EEPROM) 位线 (e) FRAM 字线 浮栅 字线

DRAM

随着高密度存储器的不断发展,存 储单元尺寸逐渐减小,这种趋势使得结 构简单的动态RAM成为首选。 DRAM单元发展过程中出现几个阶 段,这些阶段的发展使得DRAM的单元 面积越来越小。

《MOS场效应晶体管》课件

MOS场效应晶体管的制造工艺

1

制造工艺流程

MOS场效应晶体管的制造过程包括晶圆加工、掺杂、薄膜沉积、光刻和封装等 关键步骤。

2

生产中的注意事项

在MOS场效应晶体管的生产过程中,需要注意材料的纯净度、工艺参数的控制 和设备的精确性,以确保器件的质量和性能。

结束

感谢您的聆听,希望这份课件能够帮助您更好地理解MOS场效应晶体管的重 要性和应用,欢迎进一步探索和学习更多相关知识。

原则和优缺点

两种类型的MOS场效应晶体管在特性、工作模式和应用上存在一些原则和优缺点,需要根 据具体需求选择合适的类型。

MOS场效应晶体管的应用

应用领域

MOS场效应晶体管广泛应用于集成电路、通信、计 算机、消费电子等领域,是现代电子技术的重要组 成部分。

电路中的应用

MOS场效应晶体管在逻辑门、放大器、模拟电路和 功率电子等电路中发挥关键作用,满足不同应用的 要求。

MOS场效应晶体管的特性和工作原理

1 主要特性

2 工作原理

MOS场效应晶体管场效应晶体管通过控制栅极电压来调节 电流,实现信号的放大、开关和调制等功能。

MOS场效应晶体管的分类

分类介绍

MOS场效应晶体管根据栅极与通道之间的结构和电荷输运机制进行分类,主要包括增强型 和耗尽型。

《MOS场效应晶体管》课 件

通过这份课件,您将了解到有关MOS场效应晶体管的重要概念、特性、应用 及制造工艺,欢迎加入我们的学习之旅!

MOS场效应晶体管简介

MOS场效应晶体管(Metal-Oxide-Semiconductor Field Effect Transistor)是一种关键的电子器件,广泛应用于现 代半导体技术中。它由金属、氧化物和半导体材料构成,具有卓越的电子控制能力。

MOS场效应晶体管74026-PPT精选文档

正常 放大 时外 加偏 置电 压的 要求

VGS<0 ,使栅极 PN 结反偏,iG=0。

VDS>0 , 使 形 成 漏 电流iD。

问题:如果是P沟道,直流偏置应如何加?

栅源电压对沟道的控制作用

(动画2-9)

VGS 继续减小,沟道继续变窄, ID继续减小直至为0。当 当 VV =0时,在漏、源之间加有一定电压时,在漏源 GS 当 GS<0时,PN结反偏,形成耗尽层,漏源间的 漏极电流为零时所对应的栅源电压 VGS称为夹断电压 VP。 间将形成多子的漂移运动,产生漏极电流。 沟道将变窄,ID将减小。

断”。

特性曲线

vGS 2 iD IDSS (1 ) VP

v v v V G D G SD S P

(a) N沟道结型FET (b) 输出特性曲线

(b) N沟道结型FET 转移特性曲线

各类场效应三极管的特性曲线

N 沟 道 增 强 型 P 沟 道 增 强 型

绝 缘 栅 场 效 应 管

各类场效应三极管的特性曲线

N 沟 道 耗 尽 型 P 沟 道 耗 尽 型

绝 缘 栅 场 效 应 管

各类场效应三极管的特性曲线

结 型 场 效 应 管

N 沟 道

P 沟 道

场效应管参数 开启电压VGS(th) (或VT)

开启电压是 MOS增强型管的参数,栅源电压 小于开启电压的绝对值, 场效应管不能导通。

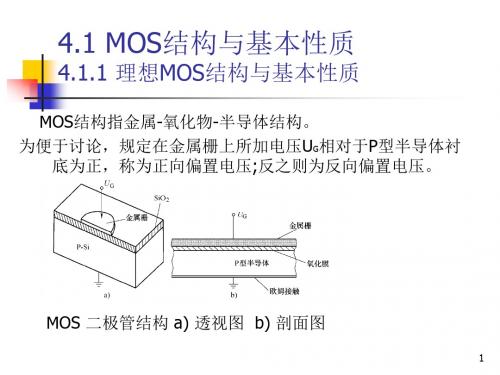

§2.3 MOS场效应晶体管

分类

Junction type Field Effect Transistor

ቤተ መጻሕፍቲ ባይዱ

场 效 应 管

结型场效应三极管JFET

N沟道

P沟道

绝缘栅型场效应三极管IGFET Insulated Gate Field Effect Transistor

集成电路版图设计基础场效应晶体管讲解

1. 电学SOA

功率晶体管的电学SOA 源于碰撞电离。背栅去偏置 效应。背栅去偏置超过了源区衬偏电压,源向衬底 注入少子。

2. 热电SOA

MOS 结构中固有寄生双极型晶体管具有和任何其他 双极型晶体管一样的缺点,尤其是会出现热击穿。 在约1ms 的延迟后,聚集的电流就会将雪崩MOS 管 烧毁,这种机制叫做热电SOA。漏区-背栅结温度较 高的部分传导较大的电流,使电流积聚到一个热点。

!!Guard Ring 必须封闭

应该采用后者

噪声抑制——屏蔽

M3

M2

Signal

M1

Coaxial Shielding

via2 M2 via1

GND

!如果需要shielding结构,请电路设计者事先告知 !!绕线时,先走Shielding结构,再绕其他线

噪声抑制——差分结构

Differential Signal

噪声抑制——去耦

Stacked Power Rails

M3

GND

小电容

M2

VDD

M1

GND

层叠电源线和地线,会形成许多小电容 对于高频噪声的泄放很有用

在做cell ring时,除非工艺方有特定要 求,往往都做成电源线与地线层叠的形式:

方便ESD走线 增大寄生电容。

噪声抑制——电源

PAD

Individual Power Rail

器件的个数是否和原理图一至(有并联的管子时注意);各器件的尺寸是否和原 理图一致。一般在拿到原理图之后,会对布局有大概的规划,先画器件,(器 件之间不必用最小间距,根据经验考虑连线空间留出空隙)再连线。对每个器件 的各端从什么方向,什么位置与其他物体连线必须先有考虑

场效应晶体管基础PPT课件

Q'SD (max) eNa xdT

金属 氧化物 p型半导体 金属 氧化物 p型半导体

VG VOX s ms

s 2 f p

VOX Q'SD (max) Q'ss COX

VTP

Q'SD (max) Q'ss COX

ms 2 f p

VTP

Q'SD (max) COX

OX

tOX

8、理想 C-V特性

C'

C 'OX

堆积

C 'OX

C 'FB

低频

C 'SD

强反型 中反型

耗尽

C 'min 高频 VFB 0

VT

VG

C 'OX

OX

tOX

C 'FB tOX

LD

OX OX LD s

sVth

eN a

C 'min tOX

xdT

OX OX xdT s

Q'ss

Ec EFi EF Ev

金属 氧化物 半导体

VG VOX s ms

s 0

VOX

Q'm Q'ss COX COX

VFB

Q'ss ms COX

Q'm Q'ss 0

5、 阈值电压

eVOX

es

e f p

Ec EFi EF Ev

Q'mT

Q'ss

xdT

tox

1 2

ms

Eg m 2e f p

MOS场效应晶体管课件

形,如图6.2 。

必须指出,上述讨论未考虑到反型层中的电子是哪 里来的。若该MOS电容是一个孤立的电容,这些电子只 能依靠共价键的分解来提供,它是一个慢过程,ms级。

2023/12/22

15

MOS电容—测量

若测量电容的方法是逐点测量法—一种慢进 程,那么将测量到这种凹谷曲线。

① ⑤

②

③

④

图 5.2

区,栅极与源极扩散区都存

在着某些交迭,故客观上存

在着Cgs和Cgd。当然,引出 线之间还有杂散电容,可

以计入Cgs和Cgd。

图 5.3

2023/12/22

18

MOS电容的计算

Cg、Cd的值还与所加的电压有关:

1)若Vgs<VT,沟道未建立,MOS管漏源沟道不通。 MOS电容 C = Cox,但C 对Cd无贡献。

2023/12/22

16

MOS电容凹谷特性测量

若测量电容采用高频方法,譬如,扫频方法, 电压变化很快。共价键就来不及瓦解,反型层就 无法及时形成,于是,电容曲线就回到Cox值。 然而,在大部分场合,MOS电容与n+区接在一 起,有大量的电子来源,反型层可以很快形成, 故不论测量频率多高,电压变化多快,电容曲线 都呈凹谷形。

2023/12/22

6

MOSFET特性曲线

在非饱和区 Ids Vds C a1Vgs b1 线性工作区

在饱和区 Ids a2 Vgs VT 2

(Ids 与 Vds无关) . MOSFET是平方律器件!

Ids

饱和区

线性区

击穿区

0

2023/2 MOSFET电容的组成

的二倍。它不仅抵消了空穴,成为本征半导体,而

且在形成的反型层中,电子浓度已达到原先的空穴 浓度这样的反型层就是强反型层。显然,耗尽层厚 度不再增加,CSi也不再减小。这样,

必须指出,上述讨论未考虑到反型层中的电子是哪 里来的。若该MOS电容是一个孤立的电容,这些电子只 能依靠共价键的分解来提供,它是一个慢过程,ms级。

2023/12/22

15

MOS电容—测量

若测量电容的方法是逐点测量法—一种慢进 程,那么将测量到这种凹谷曲线。

① ⑤

②

③

④

图 5.2

区,栅极与源极扩散区都存

在着某些交迭,故客观上存

在着Cgs和Cgd。当然,引出 线之间还有杂散电容,可

以计入Cgs和Cgd。

图 5.3

2023/12/22

18

MOS电容的计算

Cg、Cd的值还与所加的电压有关:

1)若Vgs<VT,沟道未建立,MOS管漏源沟道不通。 MOS电容 C = Cox,但C 对Cd无贡献。

2023/12/22

16

MOS电容凹谷特性测量

若测量电容采用高频方法,譬如,扫频方法, 电压变化很快。共价键就来不及瓦解,反型层就 无法及时形成,于是,电容曲线就回到Cox值。 然而,在大部分场合,MOS电容与n+区接在一 起,有大量的电子来源,反型层可以很快形成, 故不论测量频率多高,电压变化多快,电容曲线 都呈凹谷形。

2023/12/22

6

MOSFET特性曲线

在非饱和区 Ids Vds C a1Vgs b1 线性工作区

在饱和区 Ids a2 Vgs VT 2

(Ids 与 Vds无关) . MOSFET是平方律器件!

Ids

饱和区

线性区

击穿区

0

2023/2 MOSFET电容的组成

的二倍。它不仅抵消了空穴,成为本征半导体,而

且在形成的反型层中,电子浓度已达到原先的空穴 浓度这样的反型层就是强反型层。显然,耗尽层厚 度不再增加,CSi也不再减小。这样,

MOS场效应晶体管ppt课件

T

q

ln( N A ) ni

0

对于N型半导体,

F

T q

ln( N D ) 0 ni

静电势ψ的定 义如图所示

5

而空穴和电子的浓度也可表示为ψ的函数

pP

ni

exp

q F

T

nP

ni

exp

q

T

F

当能带如上图所示向下弯曲时,ψ为正值,表面载流子的浓度 分别为

UDS较小时,导电沟道随UGS的变化

a) UGS< UT 没有沟道 b) UGS> UT 出现沟道 c) UGS>>UT 沟道增厚

23

2. 饱和工作区 此时的电流-电压特性对应与特性图中UGS=5V曲线的AB段。

导电沟道随UDS的变化

a) UDS很小沟道电阻式常数 b) UDS=UDSat开始饱和 c) UDS>>UDSat漏极电流不再增加

实际 MOS 结构的阀值电压为:

UT

U FB

U OX

2 F

QOX QB max COX

2 F

ms

28

4.3.2 影响阀值电压的其他诸因素

1. 栅氧化层厚度与质量的影响 2. 绝缘栅表面态电 荷密度QOX的影响

右图为室温下AI 栅 N 沟(P沟) MOS 的UT 随 NA(ND) 和QOX变化的理 论曲线

理想 MOS 结构的阀值电压为

UT

0

QB max COX

2

F

27

3. 实际 MOS 结构的阀值电压

在实际的 MOS 结构中,存在表面态电荷密度QOX和金属-半导 体功函数差фms。 因此,在实际MOS结构中,必须用一部分栅压去抵消它们的 影响。才能使MOS结构恢复到平带状态,达到理想MOS结构 状态。

MOS场效应管PPT课件

G

U G

U G

S NEMOS

转移特性

ID

S NDMOS

ID

S PEMOS

ID

D

ID

U

S PDMOS

ID

23

0 VGS(th) VGS

VGS(th) 0

VGS

.

VGS(th) 0 VGS

0 VGS(th VGS

)

饱和区(放大区)外加电压极性及数学模型

▪ VDS极性取决于沟道类型 N沟道:VDS > 0, P沟道:VDS < 0

▪ VGS极性取决于工作方式及沟道类型 增强型MOS管: VGS 与VDS 极性相同。 耗尽型MOS管: VGS 取值任意。

▪ 饱和区数学模型与管子类型无关

24

ID C 2 O lW X(VGS VGS()t2h)

.

临界饱和工作条件

|VGS| > |VGS(th) |, |VDS | = | VGS – 饱和区(放大区)工作VG条S(件th) |

之间PN结反偏,衬底应接电路最低电位(N沟道)或最高电

位(P沟道)。

- VD+S

U -VU+S S -VG+S G

D

P+

N+

N+

ID/mA VUS = 0

-2V -4V

P

O

VGS /V

若| VUS | 阻挡层宽度 耗尽层中负离子数

19

因VGS不变(G极正电荷量不变) 表面层中电子数 ID

根据衬底电压对ID的控制作. 用,又称U极为背栅极。

.

▪ 若考虑沟道长度调制效应

则VDS →沟道长度l →沟道电阻Ron略。

集成电路设计.pptx

双极晶体管和MOS晶体管都可用作有源电阻

MOS管有源电阻器

IDS I

I

VGS V VTP

DI

O

S

+

G+

G

V -

V-

O

I

S

D

VTN V VGS

IDS

(a)

(b)

MOS有源电阻及其I-V曲线

第23页/共66页

晶体管有源寄生电阻

双极晶体管集电区电阻 集成电路中集电区电阻Rc要比分立管的大。Rc的增大 会影响高频特性和开关性能。

第2页/共66页

Tox

N+

P

sio2

金 属

NP金s+io属2

纵向结构

横向结构

MOS 电容电容量

Cox=

Aε0 εsio2

Tox

Tox: 薄氧化层厚度;A: 薄氧化层上 金属电极的面积。

一般在集成电路中Tox 不能做的太薄,所以要想提高电容量,只能增加面积。 N+层为 了减小串联电阻及防止表面出现耗尽层。

集成电路中要制作一个30 pF的MOS电容器, 所用面积相当于25个晶体管的面积。

第3页/共66页

MOS电容 N+

SiO2 P+

AL

N+ N-epi

P-SUB

Al P+

第4页/共66页

❖ PN结电容 在PN结反偏时的势垒电容构成的电容器

❖ PN结电容与 MOS电容的数量级相当。

+

-

N+

P

N

外

P衬

第39页/共66页

第40页/共66页

CMOS反 相器工作 原理

输入端高电平时:

MOS管有源电阻器

IDS I

I

VGS V VTP

DI

O

S

+

G+

G

V -

V-

O

I

S

D

VTN V VGS

IDS

(a)

(b)

MOS有源电阻及其I-V曲线

第23页/共66页

晶体管有源寄生电阻

双极晶体管集电区电阻 集成电路中集电区电阻Rc要比分立管的大。Rc的增大 会影响高频特性和开关性能。

第2页/共66页

Tox

N+

P

sio2

金 属

NP金s+io属2

纵向结构

横向结构

MOS 电容电容量

Cox=

Aε0 εsio2

Tox

Tox: 薄氧化层厚度;A: 薄氧化层上 金属电极的面积。

一般在集成电路中Tox 不能做的太薄,所以要想提高电容量,只能增加面积。 N+层为 了减小串联电阻及防止表面出现耗尽层。

集成电路中要制作一个30 pF的MOS电容器, 所用面积相当于25个晶体管的面积。

第3页/共66页

MOS电容 N+

SiO2 P+

AL

N+ N-epi

P-SUB

Al P+

第4页/共66页

❖ PN结电容 在PN结反偏时的势垒电容构成的电容器

❖ PN结电容与 MOS电容的数量级相当。

+

-

N+

P

N

外

P衬

第39页/共66页

第40页/共66页

CMOS反 相器工作 原理

输入端高电平时:

集成电路第8章I0.ppt

偏置。 (2)两个寄生三极管的电流放大倍数乘积大于1: (3)电源所提供的最大电流大于寄生可控硅导通所需要的维持电

流Ih。

2024/9/30

18

第二节 输入保护电路

其中条件(2)的推导如下

设外界干扰引起的触发电流IAG 使Q1的EB结正偏电压大于≥0.7V。

此时Q1导通,若 IC1流过Rw产生的压降大于0.7V,就能使Q2也导

2024/9/30

12

第二节 输入保护电路

二、输入保护电路 2、上图所示可以很好保护NMOS管栅极,但是对PMOS管栅极保 护作用较差。若把二极管接在VDD和输入端之间,则对PMOS管 栅极保护作用好而对NMOS栅极保护差。 因此,CMOS IC中一般都采用双二极管保护电路,用两个二极管 和一个电阻构成的保护电路。

一旦发生闩锁效应,CMOS电路的电源和地之间就处于近似 短路的状态,这势必破坏电路的正常工作。此时只有将电源关 断,然后重新接通,电路才可能恢复正常工作。如果这种电流不 加限制,最终将使整个电路烧毁。

2024/9/30

17

第二节 输入保护电路

CMOS电路版图中的闩锁效应

产生闩锁效应的基本条件有三个: (1)外界因素使两个寄生三极管的EB结处于大于等于0.7的正向

2024/9/30

1

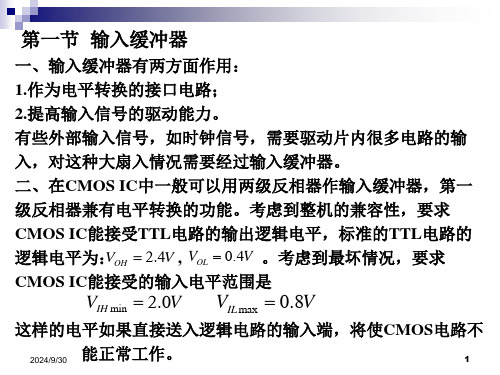

第一节 输入缓冲器

要通过输入缓冲器转换成合格的CMOS逻辑电平,再送到其他电

路的输入端。可以通过一个专门设计的CMOS反相器实现电平转

换,它的逻辑阈值设计在输入高、低电平范围之间,即

Vit

VIH min

VILmax 2

1.4V

若 VDD 5V VTN VTP 0.8V ,则要求输入级反相器的比例因子

2024/9/30

流Ih。

2024/9/30

18

第二节 输入保护电路

其中条件(2)的推导如下

设外界干扰引起的触发电流IAG 使Q1的EB结正偏电压大于≥0.7V。

此时Q1导通,若 IC1流过Rw产生的压降大于0.7V,就能使Q2也导

2024/9/30

12

第二节 输入保护电路

二、输入保护电路 2、上图所示可以很好保护NMOS管栅极,但是对PMOS管栅极保 护作用较差。若把二极管接在VDD和输入端之间,则对PMOS管 栅极保护作用好而对NMOS栅极保护差。 因此,CMOS IC中一般都采用双二极管保护电路,用两个二极管 和一个电阻构成的保护电路。

一旦发生闩锁效应,CMOS电路的电源和地之间就处于近似 短路的状态,这势必破坏电路的正常工作。此时只有将电源关 断,然后重新接通,电路才可能恢复正常工作。如果这种电流不 加限制,最终将使整个电路烧毁。

2024/9/30

17

第二节 输入保护电路

CMOS电路版图中的闩锁效应

产生闩锁效应的基本条件有三个: (1)外界因素使两个寄生三极管的EB结处于大于等于0.7的正向

2024/9/30

1

第一节 输入缓冲器

要通过输入缓冲器转换成合格的CMOS逻辑电平,再送到其他电

路的输入端。可以通过一个专门设计的CMOS反相器实现电平转

换,它的逻辑阈值设计在输入高、低电平范围之间,即

Vit

VIH min

VILmax 2

1.4V

若 VDD 5V VTN VTP 0.8V ,则要求输入级反相器的比例因子

2024/9/30

集成电路版图设计项目教程 项目2 MOS晶体管版图设计

1) 计规则分类

设计规则通常有以下两类: ➢ 1.λ准则:用单一参数λ表示版图规则,所有

的几何尺寸都与λ成线性比例。 ➢ 2.微米准则:用微米表示版图规则中最小线

宽尺寸和最小允许间隔尺寸等。

制造工艺的关键性能参数是特征尺寸,更准 确的说就是沟道长度。晶体管尺寸既决定了电 路速度,又决定了单个芯片上逻辑单元的数量。 制造工艺通常按照制造最小晶体管的长度来区 分,因此,一个制造最小沟道长度为0.35µm的 晶体管工艺叫0.35µm工艺。

以λ为单位的设计规则把尺寸定义为λ的倍数,λ的 取 值 由 工 艺 决 定 。 λ=0.5µm 的 CMOS 工 艺 也 称 0.5µm CMOS工艺;λ一般指工艺尺寸给出的最小 沟道长度,版图设计可以独立于工艺和实际的尺 寸。对于不同的工艺,只要改变λ的取值就可以了。 采用以λ为单位的设计规则会使设计规则得以简化, 而且有利于工艺按比例收缩。但以λ为单位的设计 规则有可能会造成芯片面积的浪费。

易于在工艺中实现,并能取得较高的 出来的芯片不能正常工作,即影响成品率;而工艺制造工程师

成品率。

希望芯片的成品率会高一些,所以希望线条尽可能的宽,线条

版图设计规则通常包括两个方面: 之间的距离尽可能大,但是这样又会造成芯片面积的增加。为

➢ 规定图形和图形间距的最小允许尺 了在芯片的器件集成度与成品率之间得到一个折中,必须制定

项目2 MOS晶体管版图设计

任务2.1集成电路版图设计工艺规则

2)版图设计规则

基本设计规则 主要包括: ➢ 线宽规则; ➢ 间距规则; ➢ 包围规则; ➢ 延伸规则; ➢ 交叠规则; 最小面积规则等。

➢ 1.线宽规则(Width Rule) 线宽规则通常指的是版图中多边形的最小宽度。多边形的最小宽度是关键尺寸,

2019集成电路原理课件-MOS集成电路的版图设计.ppt

(3)诱发寄生可控硅触发的三个因素: • T1、T2管的值乘积大于1,即npnpnp>1。 • T1、T2管EB结均为正向偏置。 • 电源提供的电流维持电流IH。

(4)诱发闩锁的外界条件: 射线瞬间照射,强电场感应,电源电压过冲,跳变电压,

环境温度剧变,电源电压突然增大等。

2、防止闩锁的措施 A.版图设计和工艺上的防闩锁措施

Cm=(1+KV)CGD,KV为电压放大系数。

5.1.3 寄生沟道

图5-4 寄生沟道形成示意图

场开启

——当互连跨过场氧区时,如果互连电位足够高,可能使场区 表面反型,形成寄生沟道,使本不应连通的有源区导通,造成 工作电流泄漏,使器件电路性能变差,乃至失效。

预防措施: (1)增厚场氧厚度t’OX,使V’TF,但需要增长场氧时间,对前 部工序有影响,并将造成台阶陡峭,不利于布线。 (2)对场区进行同型注入,提高衬底浓度,使V’TF。但注意 注入剂量不宜过高,以防止某些寄生电容增大,和击穿电压的 下降。 (3)版图设计时,尽量把可能产生寄生MOS管的扩散区间距 拉大,以使W/L,ron,但这样将使芯片面积,集成度。

• 使T1、T2的,npnpnp«1。工艺上采取背面掺金,中 子辐射电子辐照等降低少子寿命。

• 减少RS、RW使其远小于Ren、Rep。 • 版图中加保护环,伪集电极保护结构,内部区域与外围分割 • 增多电源、地接触孔的数目,加粗电源线、地线对电源、地

接触孔进行合理布局,减小有害的电位梯度。 • 输入输出保护。 • 采用重掺杂衬底上的外延层,阱下加p+埋层。 • 制备“逆向阱”结构。 • 采用深槽隔离技术。

B. 器件外部的保护措施 • 电源并接稳压管。 • 低频时加限流电阻(使电源电流<30mA) • 尽量减小电路中的电容值。(一般C<0.01F)

mos工作原理ppt课件

作业: P.45. 2.2.1 P.63. 2.2 2.4

• 2、结型场效应管工作时PN结必须反偏、 MOS管则由于栅极被绝缘,故场效应管的 输入阻抗大大高于三极管。

• 3、集成度高。 • 4、使用注意事项。

2-2 基本放大电路

放大电路的目的是将微弱的变化信号不失真地放大成较大的信号。 这里所讲的主要是电压放大电路。

电压放大电路可以用有输入口和输出口的四端网络表示,如图:

ID

UGS>0 UGS=0

VT 0

UGS 0

UGS<0

U DS

N沟道耗尽型MOS管的特点 当uGS=0时,就有沟道,加入uDS,就有iD。 当uGS>0时,沟道增宽,iD进一步增加。 当uGS<0时,沟道变窄,iD减小。

2-2-2 结型场效应管(J-FET)

与双极型晶体管的比较

• 1、只有多子参与导电,受温度影响较小 (热稳定性较好),抗辐射能力较强。

UGS较小时,导 电沟道相当于电

阻将D-S连接起

来,UGS越大此 电阻越小。

N

N

P

三、增强型N沟道MOS管的特性曲线

输出特性曲线

iD(mA)

4 3

2 1

uGS=6V

uGS=5V uGS=4V uGS=3V

10V

转移特性曲线 iD=f(uGS)uDS=常数

iD(mA)

4

3

2

1

u

DS

(V)2Biblioteka 46UT(VT)场效应管是电压控制元件,只有多子参与导电,输 入阻抗高,热稳定性好。

场效应管

绝缘栅场效应管 增强型

耗尽型

结型场效应管 N沟道

P沟道

N沟道 P沟道

第八章MOS场效应晶体管课件

ID

VGS 0 VT

VGS VT 0

4 、输出特性曲线 输出特性曲线是指 VGS >VT 且恒定时的VDS ~ID 曲线,

可分为以下 4 段:

① 线性区 当 VDS 很小时,沟道就象一个其阻值与 VDS 无关的固定 电阻,这时 ID 与 VDS 成线性关系,如图中的 OA 段所示:

② 过渡区 随着VDS 的增大,漏附近的沟道变薄,沟道电阻增大,曲 线逐渐下弯。当VDS 增大到VD sat(饱和漏源电压)时,漏处的 可动电子消失,这称为沟道被夹断,如图中的AB 段所示。 线性区与过渡区统称为 非饱和区,有时也统称为 线性区。

要使表面发生强反型,应使表面处的 EF Eis qFP ,这时 能带总的弯曲量是 2qFP 。

此时的表面势为:S S,inv 2FP

外加栅电压超过 VFB 的部分(VG - VFB )称为 有效栅压 。 有效栅压又可分为两部分:降在氧化层上的 VOX 与降在硅表面

附近的表面电势 S 即:VG VFB VOX S 。S 使能带发生弯 曲。表面发生强反型时 EF Eis qFP ,这时能带总的弯曲量

再随VG 而增大,表面势 S 也几乎维持 S,inv 不变。于是有:

Qn QS QA

QM QA COX VOX QA

CO( X VG VB VFB S,inv) QA

当外加 VD ( > VS ) 后,沟道中产生电势 V ( y ) ,V ( y ) 随 y 而增加,从源处的 V ( 0 ) = VS 增加到漏处的 V ( L ) = VD 。

MS 与金属种类、半导体导电类型及掺杂浓度有关。对于

Al ~ Si 系统:

MS

- 0.6 V ~ - 1.0V ( N 沟 ) (见304页图 5-15)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

二. MOS管的版图

多晶硅层(Poly): 多晶硅层的作用是定义制作多晶硅材料的区 域。最早的MOS集成电路制造工艺只能制备 一层多晶硅,而现在已经有能够制备两层多 晶硅的工艺了。对于双层多晶硅工艺,第一 层多晶硅主要用来制作栅极、导线和多晶 硅—多晶硅电容的下极板,第二层多晶硅主 要用来制作多晶硅电阻和多晶硅-多晶硅电 容的上极板。双层多晶硅工艺具有多晶硅1 和多晶硅2这两个版图层。

二. MOS管的版图

阱层(Well): 阱层定义在衬底上制备阱的区域。NMOS 管制备在P型衬底上,PMOS管制备在N 型衬底上。一块原始的半导体材料,掺入 的杂质类型只能有一种,即该衬底不是N 型就是P型。如果不对衬底进行加工处理 的话,该衬底只能制备一种MOS晶体管。 CMOS集成电路是把NMOS晶体管和 PMOS晶体管制备在同一个硅片衬底上, 为了能够制造CMOS集成电路,需要对衬 底进行处理,利用掺杂工艺在衬底上形成 一个区域,该区域的掺杂类型和衬底的掺 杂类型相反,这个区域就称为阱。

二. MOS管的版图

多晶硅

有源区

W

L

二. MOS管的版图

二. MOS管的版图

图 NMOS晶体管的版图示意图

二. MOS管的版图

三. MOS管版图设计技巧

源漏共用 MOS管的串联:

G1

G2

G1

G2

S1

D1 S2

D2

M1

M2

G1

G2

S1

D1

S2

D2

M1

M2

S1

M1 G1

A12 金属

D2

M2 G2

二. MOS管的版图

金属层: 实现金属互连。

二. MOS管的版图

接触孔层(Contact): 接触孔层定义制作接触孔的区域。MOS晶体 管的源极、漏极、栅极和衬底都要与电源或其 它元件相连接,这样才能对MOS晶体管供电 使其工作并和其它元件一起组成具有使用价值 的电路。有源区和场区的表面以及多晶硅栅极 上都有二氧化硅薄膜的存在,而二氧化硅是不 导电的,为了能进行电连接,需要将衬底和多 晶硅上某些区域上的二氧化硅去除,打开窗口, 在窗口内填塞金属,并用金属线进行连接。这 些窗口就是接触孔,其作用是实现半导体材料 和金属的欧姆接触,从而对MOS晶体管的各 个电极进行电连接。

P+注入层和N+注入层(P+ implant和N+ implant): P+注入层定义注入P+杂质离子的区域,而 N+注入层定义注入N+杂质离子的区域。由 于NMOS晶体管和PMOS晶体管的结构相同, 只是源漏区的掺杂类型相反。同时,有源区 层只是定义了源区、漏区和沟道的区域,却 没有说明源区和漏区的掺杂类型。P+注入层 和N+注入层说明了注入杂质的类型,也就 是说明了有源区的导电类型,实现了NMOS 晶体管和PMOS晶体管的区分。

源漏共用 MOS管的并联:

D1

D2

G1

M1 G2

M2 G1

S1

S1

S2

M1

D2 G2

S2 M2

三. MOS管版图设计技巧

源漏共用 MOS管的并联:

D1 G1

S1

A12

M1

D2 M2

三. MOS管版图设计技巧

源漏共用 MOS管的串联:

G1

G2

金属

S1

A12

M1

D2 M2

G1

G2

S1

A12

D2

M1

M2

三. MOS管版图设计技巧

源漏共用 MOS管的串联:

G1

G2

G3

S1

A12

A23

D3

M1

M2

M3

G1

G2

G3

S1

A12 A23

D3

M1

M2

M3

三. MOS管版图设计技巧

一. 概述

CMOS晶体管电路和其它电路(例如双极型晶体管电路)相 比较,具有电流损耗更低、面积更小、设计更加灵活的优点。 CMOS晶体管电路可用于数字电路和模拟电路,并且在一些 特定应用上开始替代双极型晶体管电路。但是,CMOS晶体 管并不具备双极型晶体管的全部性质,为了充分利用CMOS 晶体管和双极型晶体管的优点,已经出现了可将双极型晶体 管和CMOS晶体管制作在同一衬底上的工艺,即BiCMOS工 艺。

第八章 MOS场效应 晶体管

概述

MOS管的版图

MOS

源漏共用

场

效

特殊尺寸MOS管

应

MOS管版图设计技巧

晶

衬底连接和阱连接

体

管 天线效应

棍棒图

MOS管的匹配规则

一. 概述

场效应晶体管(Field Effect Transistor, FET )的发明早于 双极型晶体管,但是由于当时的集成电路制造工艺无法生长 出高质量的介质薄膜,使得场效应晶体管没有成功生产出来。 二十世纪六十年代,由于适合于栅极的绝缘介质薄膜的成功 生产,使得制造金属-氧化物-半导体场效应晶体管(Metal Oxide Semiconductor Field Effect Transistor, MOSFET,简称为MOS晶体管)成为可能。 早期的MOS晶体管由于制造工艺不成熟,存在阈值电压不稳 定、薄氧化层易被击穿等问题。随着工艺水平的不断进步, 现在制造MOS晶体管的工艺已经相当成熟了,人们已经可以 制备性能优良的CMOS晶体管电路了。

一. 概述

MOS晶体管是四端器件,具有源极(S)、漏极(D)、栅 极(G)和衬底(B)四个电极,按导电类型分为NMOS晶体 管和PMOS晶体管两种.

(a)NMOS

(b)PMOS

一. 概述

二. MOS管的版图

NMOS晶体管的立体图和俯视图

(a)立体图

(b)俯视图

二. MOS管的版图

图 PMOS晶体管的版图示意图

二. MOS管的版图

P+注入层和N+注入层(P+ implant和N+ implant): P+注入层定义注入P+杂质离子的区域,而 N+注入层定义注入N+杂质离子的区域。由 于NMOS晶体管和PMOS晶体管的结构相同, 只是源漏区的掺杂类型相反。同时,有源区 层只是定义了源区、漏区和沟道的区域,却 没有说明源区和漏区的掺杂类型。P+注入层 和N+注入层说明了注入杂质的类型,也就 是说明了有源区的导电类型,实现了NMOS 晶体管和PMOS晶体管的区分。

二. MOS管的版图

有源区层(Active): 有源区层的作用是在衬底上定义制作 有源区的区域,该区域包括源区、漏 区和沟道。在衬底上淀积厚氧化层, 利用光刻和刻蚀工艺在衬底上开窗口 并把厚氧化层除去就可形成有源区, 有源区之外的区域是场区。显然, MOS管必须而且只能制备在有源区 内。

二. MOS管的版图