数电第八章

数电PPT-第八章

第八章半导体存储器和可编程逻辑器件引言一、随机存取存储器(RAM)二、只读存储器(ROM)三、可编程逻辑器件(PLD)四、复杂的可编程逻辑器件(CPLD)1、存储系统的基本概念2、存储器的分类3、存储器的主要性能指标1、存储系统的基本概念存储器是一种接收、保存和取出信息(程序、数据、文件)的设备;一种具有记忆功能的部件;是计算机的重要组成部分。

CPU·ßËÙº¹´æM1M2M3M4......MnÍâ´æ2Íâ´æ1Íâ´æ3Íâ´æ4......Íâ´æn Ö÷´æÍâ´æ三级层次的存储器结构2、存储器分类①按用途分类②按存储器存取方式不同①.按用途分类按存储器用途可以分为主存储器和辅助存储器。

⑴主存储器(Main Memory)主存又称内存,用来存放计算机正在执行的或经常使用的程序和数据。

CPU可以直接对它进行访问,一般是由半导体存储器构成,通常装在主板上,存取速度快,但容量有限,其大小受地址总线位数的限制。

用来存放系统软件及当前运行的应用软件。

⑵辅助存储器(External Memory)•辅助存储器又称外存,是主存的后援,一般不安装在主机板上,属计算机的外部设备。

•辅存是为弥补内存容量的不足而配置的,用来存放不经常使用的程序和数据,需要时成批调入主存供CPU使用,CPU不能直接访问它。

•最广泛使用的外存是磁盘、光盘等。

辅存容量大,成本低,所存储信息既可以修改也可以长期保存,但存取速度慢。

•外存需要配置专门的驱动设备才能完成对它的访问,如硬盘、软盘驱动器等。

数字电子技术第8章可编程逻辑器件

前面介绍的FPLA的电路结构不含触发器,因此这 种FPLA只能用于设计组合逻辑电路,故称为组合型 FPLA。

为便于设计时序逻辑电路,在有些FPLA芯片内部 增加了若干触发器组成的寄存器。这种内部含有寄 存器的FPLA称为时序逻辑型FPLA,也称做可编程 逻辑时序器PLS(Programmable Logic Sequeneer)。

Q0n+1=Q3 Q2 Q1+Q3 Q2 Q1+Q3 Q2 Q1+ Q3 Q2 Q1

从上式即可写出每个触发器的驱动方程,即D端 的逻辑函数式。同时,考虑到要求具有置零功能, 故应在驱动方程中加入一项R。当置零输入信号 R=1时,在时钟信号到达后所有触发器置1,反相后 的输出得到Y3 Y2 Y1 Y0=0000。于是得到驱动方程为

图8.3.9 产生16种算术、逻辑运算的编程情况

(8-22)

十进 8.3.3PAL的应用举例

制数

二 进制 数

Y0 Y1 Y2

例8.3.1 用PAL器件设计一个数值判别电路.要求判断4位 D C B A 二进制数DCBA的大小属于0~5、6~10、11~15三个区间的 0 0 0 0 0 1 0 0 哪一个之内。 1 0 0 0 1 1 0 0

FPLA由可编程的与逻辑阵列和可编程的或逻 辑阵列以及输出缓冲器组成,如图所示。

(8-8)

PLA结构 逻辑功能可 变化的硬件 结构。

可编程

将FPLA和ROM 比较可发现,它们 的电路结构极为相 似,都是由一个与 逻辑阵列、一个或 逻辑阵列和输出缓 冲器组成。两者所 不同的是,FPLA的 与阵列可编程,而 ROM的与阵列(译 码器)是固定的。

第八章 可编程逻辑器件(PLD)

完整版数字电子技术基础全套课件 8

?

B2 B1 B0?

?? Y0 ? B2 B0

P

L

A 与 或 阵 列 图

l可编程“断开”单元:

编程实现断开状态。这

种单元又称为被编程擦

除单元。

可

固

编

定

程

不

连

连

接:

接:

连 接:

3.PLD的画法

P=ABD

P=0

Y=P1+P3+P4

互补输出的缓冲器

三态输出的缓冲器

4. PLD分类

可编程只读存储器

分类 PROM

PLA

PAL GAL

可编程逻 辑阵列

与阵列 固定

可编程 可编程 可编程

第八章

--可编程逻辑器件

教学要求

了解PLD产品的种类; 了解PLD器件的基本结构、分类、优 点及适用场合。

可编程逻辑器件( PLD)

(Programmable Logic Device)

1. PLD的基本结构

输 入…

输 输入项 与

入

门

电

阵

与项

或 门

阵

或项

输

出 电…ຫໍສະໝຸດ 输 出路列

列

路

2.连接方式

l可编程“接通”单元: 它 依 靠 用 户编 程 来实 现“接通”连接。

可编程阵 列逻辑

或阵列 可编程 可编程 固定 固定

输出电路 固定 固定 固定 可组态

通用阵列逻辑

用PLA实现逻辑函数:

用ROM实现逻辑函数是基于该逻辑函数的 最 小项表达式 F=∑mi,而用PLA实现逻辑函数是基于 该逻辑函数的最简与或表达式 F= ∑Pi,所以用PLA 来实现逻辑函数比用 ROM实现逻辑函数更简单、 灵活。

数字电子技术第8章存储器与可编程逻辑器件习题及答案

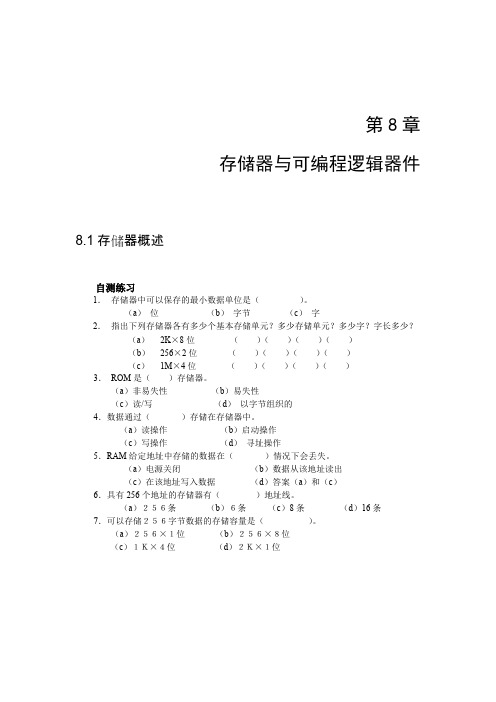

第8章存储器与可编程逻辑器件8.1存储器概述自测练习1.存储器中可以保存的最小数据单位是()。

(a)位(b)字节(c)字2.指出下列存储器各有多少个基本存储单元?多少存储单元?多少字?字长多少?(a) 2K×8位()()()()(b) 256×2位()()()()(c) 1M×4位()()()()3.ROM是()存储器。

(a)非易失性(b)易失性(c)读/写(d)以字节组织的4.数据通过()存储在存储器中。

(a)读操作(b)启动操作(c)写操作(d)寻址操作5.RAM给定地址中存储的数据在()情况下会丢失。

(a)电源关闭(b)数据从该地址读出(c)在该地址写入数据(d)答案(a)和(c)6.具有256个地址的存储器有( )地址线。

(a)256条(b)6条(c)8条(d)16条7.可以存储256字节数据的存储容量是( )。

(a)256×1位(b)256×8位(c)1K×4位 (d)2K×1位答案:1.a2.(a)2048×8;2048;2048;8(b)512;256;256;2(c)1024×1024×4;1024×1024;1024×1024;43.a4.c5.d6.c7.b8.2随机存取存储器(RAM)自测练习1.动态存储器(DRAM)存储单元是利用()存储信息的,静态存储器(SRAM)存储单元是利用()存储信息的。

2.为了不丢失信息,DRAM必须定期进行()操作。

3.半导体存储器按读、写功能可分成()和()两大类。

4.RAM电路通常由()、()和()三部分组成。

5.6116RAM有()根地址线,()根数据线,其存储容量为()位。

答案:1.栅极电容,触发器2.刷新3.只读存储器,读/写存储器4.地址译码,存储矩阵,读/写控制电路5.11,8,2K×8位8.3 只读存储器(ROM)自测练习1.ROM可分为()、()、()和()几种类型。

数电 第八章--PAL应用举例

Q1∗ = Q1Q0 + Q3Q2′Q0′ + Q3′Q2Q0′ Q0∗ = Q3′Q2′Q1′ + Q3′Q2Q1 + Q3Q2Q1′ + Q3Q2′Q1

由此可得出D触发器的驱动方程.为增加置零 功能,在驱动方程中加入置零输入信号R.当R= 1时,在CLK时钟到达后,所有的触发器被置1, 反相输出后得到Y3Y2Y1Y0=0000,计数器被置零.

Y1 = D′CBA′ + D′CBA + DC ′B′A′ + DC ′B′A + DC ′BA′ = D′CB + DC ′B′ + DC ′BA′ = D′CB + DC ′( B′ + BA′) = D′CB + DC ′( B′ + A′) = D′CB + DC ′B′ + DC ′A′ Y2 = DC ′BA + DCB′A′ + DCB′A + DCBA′ + DCBA = DC ′BA + DCB′ + DCB = DC ′BA + DC = D(C ′BA + C ) = D( BA + C ) = DC + DBA

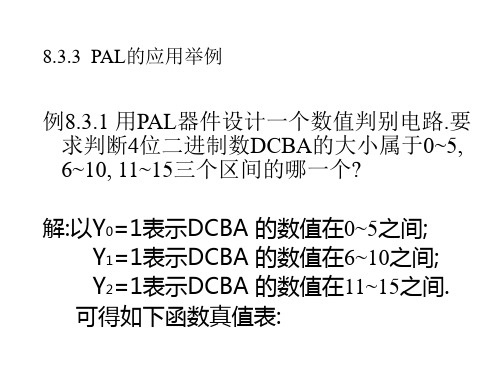

8.3.3 PAL的应用举例

例8.3.1 用PAL器件设计一个数值判别电路.要 求判断4位二进制数DCBA的大小属于0~5, 6~10, 11~15三个区间的哪一个? 解:以Y0=1表示DCBA 的数值在0~5之间; Y1=1表示DCBA 的数值在6~10之间; Y2=1表示DCBA 的数值在11~15之间. 可得如下函数真值表:

PAL中触发器的状态转换表

《数字电子技术 》课件第8章

例 2 一个四位逐次逼近型ADC电路, 输入满量程电压 为 5 V, 现加入的模拟电压Ui=4.58 V。 求:

(1) ADC (2)

解 (1) 第一步: 使寄存器的状态为1000, 送入 DAC, 由DAC转换为输出模拟电压

因为Uo二步: 寄存器的状态为1100, 由DAC转换输出的电压 因为Uo<Ui, 所以寄存器次高位的1也保留。

DAC0832芯片上各管脚的名称和功能说明如下: CS: 片选信号, 输入低电平有效。 ILE: 输入锁存允许信号, 输入高电平有效。 WR1: 输入数据选通信号, 输入低电平有效。 WR2: 数据传送选通信号, 输入低电平有效。 XFER: 数据传送控制信号, 输入低电平有效。 D0~D7: 八位输入数据信号。

图8.7 取样过程

取样电路实质上是一个受控开关。 在取样脉冲CP有效 期τ内, 取样开关接通, 使Uo=Ui; 在其他时间(TS-τ)内, 输 出Uo=0。 因此, 每经过一个取样周期, 在输出端便得到 输入信号的一个取样值。

为了不失真地用取样后的输出信号Uo来表示输入模拟 信号Ui, 取样频率fS必须满足fS≥2fmax(此式为取样定理)。 其中, fmax为输入信号Ui的上限频率(即最高次谐波分量的 频率)。模拟信号经取样后输出一系列的断续脉冲。

图 8.6 DAC0832 (a) 双缓冲器型; (b) 单缓冲器型; (c) 直通型

8.3 模/数转换器(ADC)

1. 取样和保持 取样(又称抽样或采样)是将时间上连续变化的模拟信 号转换为时间上离散的模拟信号,即转换为一系列等间隔的 脉冲。 脉冲的幅值取决于输入模拟量, 其过程如图8.7所示。 图中, Ui为模拟输入信号, CP为取样信号, Uo为取样后输出 信号。

数字电子技术基础第八章

u D I “[ ]”表示取整。 △ 称为 ADC 的单位量化电压或量化单位, 它是 ADC 的最小分辨电压。

可见,输出数字量 D 正比于输入模拟量 uI 。

EXIT

…

数模和模数转换器

A /D 转换的一般步骤

输入模拟量 输出数字量

u I( t) S

C

u I ( t)

量化 编码 电路

EXIT

数模和模数转换器

2R

2R

I0

I0 2R R

I1 A

I12R R

I2 B

I22R R

I3 C

I3

VREF I

从 A、B、C 节点向左看去,各节点对地的等效电阻均为 2R。 VREF 因此,I = R I3 I I I 2 ( I ), 3 = 2 I3 = I = = 2 = 2 ( 24 ), 2 2 24 4 I1 I2 I I I 0( I ) 1 = 2 = 2 ( 4 ),I0 = 2 = I1 = = 24 16 2 2 8 I VREF 3 2 1 0 4 即 I3 = 2 I0 , I2 = 2 I0 , I1 = 2 I0 , I 0 = 2 I0 4 2 2 R 可见,支路电流值 Ii 正好代表了二进制数位 Di 的权值 2i 。 EXIT

数模和模数转换器

模拟开关 Si 受相应数字位 Di 控制。当 Di = 1 时,开 关合向“1”侧,相应支路电流 Ii 输出;Di = 0 时,开关 合向“0”侧, Ii 流入地而不能输出。 iΣ = D3 I3 + D2 I2 + D1 I1 + D0 I0 = ( D3 23 + D2 22 + D1 21 + D0 20 ) I0 = D I0 VREF RF V R REF u = D I0 RF 4 0O ΣR F = -4 F = -D· u =- iD · 2 R 2 R RF D0 D1 D2 D3 VREF R iF Σ ∞ u = D · 对 n 位 DAC, O n - + 2 R VREF + 1 1 1 1 0 R =R 0 0 0· n 若取 S1 uO= SD F S0 , 则 2 2 S3 2R n 位 2RDAC R I12R V 2R 分成 将参考电压 I0 2 I2REF I3 2n 份,uO 是 R R DAC 的输出电压。 R 可调节 每份的 D 倍。调节 VREF VREF I0 I1 I2 I3 I

数字电子技术基础第8章可编程逻辑器件

数字电子技术基础第8章可编程逻辑 器件

PLD是70年代发展起来的新型逻辑器件,是一种通用大规模 集成电路,用于LSI和VLSI设计中,采用软件和硬件相结合的方 法设计所需功能的数字系统。相继出现了ROM、PROM、PLA、 PAL、GAL、EPLD和FPGA等,它们组成基本相似。

数字电子技术基础第8章 可编程逻辑器件

2020/11/21

数字电子技术基础第8章可编程逻辑 器件

传统的逻辑系统,当规模增大时 (SSI MSI)

焊点多,可靠性下降 系统规模增加成本升高 功耗增加 占用空间扩大

连接线与点增多 抗干扰下降

数字电子技术基础第8章可编程逻辑 器件

从逻辑器件的功能和使用方法看,最初的逻辑器件全部采用标准通用 片,后来发展到采用用户片和现场片。

通用片的功能是器件厂制造时定死的,用户只能拿来使用而不能改变 其内部功能。

通用片有门、触发器、多路开关、加法器、寄存器、计数器、译码器 等逻辑器件和随机读写存储器件。

用户片是完全按用户要求设计的VLSI器件。它对用户来讲是优化的, 但是设计周期长,设计费用高,通用性低,销售量少。用户片一般称为专 用集成电路(ASIC),但是它也向通用方向发展。

PROM----可编程存储器

P

PLA----可编程逻辑阵列

L

PAL----可编程阵列逻辑

D

GAL----通用可编程阵列逻辑

FPGA----现场可编程门阵列

ispLSI----在系统可编程大规模集成电路

数字电子技术基础第8章可编程逻辑 器件

1.与固定、或编程: 与阵列全固定,即全译码;ROM和PROM

数字电子技术基础第8章可编程逻辑 器件

数电第八章

Y Y Y

0 1 2

= = =

D C D CB DC

+ D B + D C B + D C A + DBA

三,PAL的应用 PAL的应用 器件设计一个数值判别电路. 位二进制数DCBA的 例1:用PAL器件设计一个数值判别电路.要求判断 位二进制数 : 器件设计一个数值判别电路 要求判断4位二进制数 的 大小属于0~5,6 ~ 10,11 ~ 15三个区间的哪一个之内. 三个区间的哪一个之内. 大小属于 , , 三个区间的哪一个之内 十进制数 0 1 2 3 4 5 6 7 8 9 10 11 12 二进制数 D 0 0 0 0 0 0 0 0 1 1 1 1 1 C 0 0 0 0 1 1 1 1 0 0 0 0 1 B 0 0 1 1 0 0 1 1 0 0 1 1 0 A 0 1 0 1 0 1 0 1 0 1 0 1 0 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 Y0 Y1 Y2

4. 异或输出结构 5. 运算选通输出结构 PAL规格:PAL-输入量 结构 输出量 规格: 输入量-结构 规格 输入量 结构-输出量 例:PAL14H4 14输入 4输出 输出正变量 输入 输出 PAL16R4 16输入 4输出 输出反变量 输入 输出 应用举例: 应用举例:

专用输出结构----实现组合逻辑 专用输出结构 实现组合逻辑 设计要点: 设计要点: 计算输出逻辑的最简与或式 选择PAL器件: 器件: 选择 器件 输入端 输出端 每个输出所含与项数量 进行相应编程连接, 进行相应编程连接,去除未使用的与门 寄存器输出结构----实现时序逻辑 寄存器输出结构 实现时序逻辑 设计要点: 设计要点: 计算各状态方程(驱动方程) 计算各状态方程(驱动方程)的最简与或式 选择PAL器件: 器件: 选择 器件 输入端 输出端 每个输出所含与项数量 触发器数量 进行相应编程连接, 进行相应编程连接,去除未使用的与门

数字电子技术课件 第8章_数模和模数转换器

2.转换速度

(1)建立时间tset 在输入数字量各位由全0变为全

1,或由全1变为全0,输出电压达到 某一规定值(例如最小值取LSB或 满度值的0.01%)所需要的时间

(2)转换速率SR

D/A转换器建立时间

在大信号工作时,即输入数字量的各位由全0变为全1,或由 全1变为0时,输出电压的变化率。这个参数与运算放大器的 压摆率类似。

IOUT2 +

VREF

D0

D1

D2

D3 D4

AD7520

D5 Ⅱ

D6

D7

D8

D9

RF

IOUT1 –

IOUT2 +

uO1 uO2

Q0 Q9

CP

Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8

10 位可逆计数器 加/减

计数脉冲

加减控制 电路

v0

VREF 2n

•

Rf R

n1

[ (Di

i0

• 2i )]

v01

VREF 210

•

9 i0

Di

•

2i

9

2

Di

•

2i

v02

VREF

i0

210

8.3 A/D转换器

8.3.1 A/D转换的一般过程 8.3.2 并行比较型A/D转换器 8.3.3 逐次逼近型A/D转换器 8.3.4 双积分型A/D转换器 8.3.5 A/D转换器的主要参数

8.3 A/D转换器

根据虚断有: v / R I

I

OUT 1

V

O

REF

vI

/

R u

vO (D0 20

D1 21

...D9 29 )

精品课件-数字电子技术-第8章

入端 TR

的电压低于

1 3

VDD 时,A2

输出高电平,使基本

ቤተ መጻሕፍቲ ባይዱRS

触发器翻转,Q=

1。

第8

2、基本 RS 触发器 由两个或非门 G1、G2 组成。当 R 端置 1 时,触发器置 0,输出端 OUT

为 0;当 S 端置 1 时,触发器置 1,输出端 OUT 为 1。当直接复位端 RD 加

低电平时,不管其它输入状态如何,触发器直接置 0,输出端 OUT 为 0;不使

容元件,就可以很方便地构成多谐振荡器、单稳态触发器以及施密特 触发器等脉冲的产生与整形电路。555 还可输出一定功率,可驱动 微电机、指示灯、扬声器等。它在脉冲波形的产生与变换、仪器与 仪表、测量与控制、家用电气与电子玩具等领域都有着广泛的应用。

第8

表8-1 CC7555定时器的逻辑功能表

阈值输入 TH⑥ 触发输入 TR ②

第8

555定时器按内部器件类型可分为双极型(TTL型)和单 极型(CMOS型)。TTL型产品型号的最后3位数码是555或556, CMOS型产品型号的最后4位数码是7555或7556,它们的逻辑功 能和外部引线排列完全相同。555芯片和7555芯片是单定时器, 556芯片和7556芯片是双定时器。TTL型的定时器静态功耗高, 电源电压使用范围为+5~+15V;CMOS型的定时器静态功耗 较低,输入阻抗高,电源电压使用范围为+3~+18V,且在 大多数的应用场合可以直接代换TTL型的定时器。下面以CMOS 型的CC7555

×

×

2 > 3 VDD

1

1 > 3 VDD

1

2 < 3 VDD

0

1 < 3 VDD

0

2 < 3 VDD

数电第八章57页PPT

0

vd

0

vO

1

v

0

I2

V DD V TH

0 vO

0

tw

t1

t2

I2

vO1

t

t

I2 =VTH产生如下正反馈过程:

vI2 vO vO1

迅速使 o1 = 1 o =0 电容放电 c =0

电路由暂稳态自动返回到稳态

1

0

t

vO1

vO

G1 1

t

vI Cd

vd

Rd

t

1 G2

CD

v

C

v I2 R

vO

A1

A2 B vI

A2

Q

B

Q

VCC

vI

0 vO1

t1 tw1

0 vO

tw2

0

t tw1

t

tw2 t

4. 组成噪声消除电路

如用I作为下降沿触发的计数器触发脉冲,干扰加入,就会造 成计数错误.

C

R

VCC

Cext Rext/Cext

噪声

7412

A1 1

Q

A2

Q

1D C1

vI

vO

Q

vI

B

R

vO

单稳触发器的输出脉宽应大于噪声宽度而小于信号脉宽,才可 消除噪声。

VT+

(1

R1 R2

)VTH

(3) υI1 VTH电路,维持 υ O=VOH 不变

(4)当υI下降, υI1也下降 ,只要υI1 > VTH, 则保持 υo =VOH

当 υI1 =VTH,电路产生如下正反馈 :

R2

精品课件-数字电子技术-第8章

第8章 脉冲单元电路

图8-3 施密特触发器电路

第8章 脉冲单元电路

8.2.1 施密特触发器有两个稳态(Uo=0称为0态和Uo=1称为1

态) ,在外加信号的作用下,施密特触发器两个稳态之间可 以相互转换。施密特触发器属于波形变换电路,它可以将正弦

(1) 当输入触发信号达到一定值时,输出电平发生 变化,即由一个稳态转换到另一稳态,因而称其为电平触发电

第8章 脉冲单元电路

图8-8 施密特触发器用作光控开关

第8章 脉冲单元电路

8.3 多 谐 振 荡 器

8.3.1 1. TTL与非门构成的多谐振荡器 1) 图8-9所示为电容正反馈多谐振荡器,它由两级与非门和

电容C

第8章 脉冲单元电路

图8-9 多谐振荡器

第8章 脉冲单元电路

2) 多谐振荡器的工作,主要依靠电容C的充放电,通过引起 电压Ud的变化来完成其功能。当Ub为低电平,Ua为高电平时, 称为第一暂态;当Ub为高电平,Ua为低电平时,称为第二暂态。 设起始为第一暂态,这时Ua通过门电路的内阻R0和电阻R1对电 容C充电,工作波形如图8-9所示。随着电容C的充电, 电压Ud 不断上升。 当Ud上升到Ud>VT=1.4 V时(其中VT为门限电压) ,Ud为 高电平,电路发生翻转。Ua由原来的高电平变为低电平,Ub由

(3) 555定时器构成的施密特触发器用作光控开关。 图8-8所示电路为555定时器构成的施密特触发器用作光 控开关的电路图。图中的RL为光敏电阻,有光照时电阻值小, 无光照时阻值大。有光照时,电路设计(选取合适的可变电阻 值) 使得Ui<1/3VCC,输出Uo为高电平,继电器J不动作; 无光 照时,光敏电阻大,电路设计使得Ui>2/3VCC,输出Uo为低电平, 继电器J吸合,

数字电子技术第八章

VREF 取“负”则得 VO为“正”

《数字电子技术基础》第六版

实例:AD7520

《数字电子技术基础》第六版

8.2.6 具有双极性输出的DAC 当输入数字量有±极性时, 希望输出的模拟电压也对应为±。 一、原理 例:输入为3位二进制补码。最高位为符号位,正数为0, 负数为1 补码输入 对应的 要求的

输出电压: VO RF i RF ( I 3 I 2 I1 I 0 ) VREF VREF VREF VREF RF ( d3 d 2 2 d1 3 d 0 ) R 2R 2 R 2 R V 3 2 1 0 REF ( 2 d 2 d 2 d 2 d0 ) 3 2 1 4 2

8 2 1 0 ( d 2 d 2 d 2 ) 2 1 0 3 2 000 VO 0V 001 VO 1V 111 VO 7V 100 VO 4V

*将符号位反相后接至高位输入 *将输出偏移使输入为100时,输出为0

2.偏移 4V , 使输入 100 时, VO 0

111

7 =14/15(V) 6 =12/15(V) 5 =10/15(V) 4 = 8/15(V) 3 = 6/15(V) 2 = 4/15(V) 1 = 2/15(V) 0 = 0 (V)

13/15V 6 =6/8(V) 11/15V 5 =5/8(V) 9/15V 4 =4/8(V) 7/15V 3 =3/8(V) 5/15V 2 =2/8(V) 3/15V

001 010 011 100 101 110

《数字电子技术基础》第六版

8.5 抽样保持电路

!加大输入电阻 !减小输出电阻 !Av=1

《数字电子技术基础》第六版

《数字电子技术基础》第六版

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

③暂稳态是一个不能长久保持的状态。经过一段时间 后,电路会自动返回到稳态。暂稳态的持续时间与触 发脉冲无关,仅决定于电路本身(RC延时环节)的参 数。

单稳态触发器的分类

门电路组成的单稳态触发器

按电路形式不同

MSI集成单稳态触发器 用555定时器组成的单稳态触发器

不可重复触发单稳态触发器 工作特点划分

1、施密特触发器电压传输特性及工作特点 是具有滞后特性的反相器。 (1)电路有两个稳态,是双稳电路。 (2)电路状态的翻转依赖于输入信号的维持。 输出状态取决于输入信号的幅度。 (3)具有滞后电压传输特性。 对正向增长和负向增长的输入信号,电路有 不同的阈值电平。

① 施密特触发器属于电平触发器件,当输入信号 达到某一定电压值时,输出电压会发生突变。 ② 电路有两个阈值电压。 输入信号增加和减少时, 电路的阈值电压分别是正向阈值电压(VT+)和负阈 值电压(VT-) 。

输出端 vo(3)

vI2 (2)

vo’(7) (1)

C2 +

5 k

S

1

Q

T 放电端

VCC 5kΩ

RD

0

2、工作原理

vI1

vIC

+ C1 - 5kΩ

R

&

1 G 1 Q & 0

vI2

- C2 + vO 5kΩ T

S

&

vO

①RD=0时,Q=1, vo=0,T导通。

VCC 5kΩ

RD

2、工作原理

>2VCC/3 >VCC/3

性实现延时,输出电压经延时后,反馈到开关器件输入

端,改变电路的输出状态,以获得所脉冲波形输出。

RC延时环节 开 关 电 路

基本组成

8.3.1 由门电路组成的多谐振荡器

uo 0 G1 ui1 & uo1 ui2 R G2 & C uo ui2 (uo1 ) 0 ui1 UT 0 t1 t2 t3 t

<2VCC/3 >VCC/3

vI1

vIC

+ C1 - 5kΩ

R

1

& G

vI2

- C2 + vO 5kΩ T

S

1

&

Q &

1

vO

①RD=0时,Q=1, vo=0,T导通。

f

当 f = f0 时, 电抗 X = 0 电 容 性 电 容 性

2、石英晶体振荡器 耦合电容

G1 1 C1 G2 1 vO

R

C2

R

使G1工作 在线性区

抑制高次 谐波

3、双相脉冲产生电路

石英 晶体 振荡器 vO 1 CP & 1 1J Q & Q 2

> C1

1K VCC

CP Q 1 2

{End}

Cext Rext/Cext G4 & a A1 A2 G1 & G2 & G5 & ≥1 Rint Rext Rint

B

G6 &

G7 1 G8 1 G9 1

Q

G3 &

Q

触发信号控制电路

微分型单稳态触发器

(a) 逻辑图

输出缓冲电路

电路的连接: C:外接电容 R:外接电阻或采用内部电阻

G4 & a A1 A2 G1 & G2 &

8.1 单稳态触发器 8.2 施密特触发器 8.3 多谐振荡器 8.4 555定时器及其应用

作业

8.1 单稳态触发器

8.1.1 用门电路组成的微分型单稳态触发器 8.1.2 集成单稳态触发器 8.1.3 单稳态触发器的应用

单稳态触发器的工作特点:

①电路有一个稳态和一个暂稳态,在没有外来触发信 号作用时处于稳定状态; ② 在外来触发信号作用下,电路由稳态翻转到暂稳态;

R

1

& G

vI2

- C2 + vO 5kΩ T

S

0

&

Q & 1

1

1

vO

①RD=0时,Q=1, vo=0,T导通。

②RD=1、vI1>2VCC/3、vI2>VCC/3时Q=1,vo=0,T导通

③RD=1、vI1<2VCC/3、vI2<VCC/3时Q=0,vo=1,T截止

VCC 5kΩ

RD

2、工作原理

电阻分 压器

+C - 1

5 k

vI2 (2)

vo (7) (1)

’

C2 +

5 k

S

&

1

vo(3)

电压比较器

T

集电极开路输出三极管

电压 4.5~16V 控制端 RD (4) VCC(8) 高电平

触发端 vIC(5) vI1 (6) 低电平 触发端

5 k

复位端 低电平有效

+C - 1

5 k

& R & &

vI1

vIC

+ C1 - 5kΩ

R 0

& G

vI2

- C2 + vO 5kΩ T

S 1

&

Q &

0

1

0

vO

①RD=0时,Q=1, vo=0,T导通。

②RD=1、vI1>2VCC/3、vI2>VCC/3时Q=1,vo=0,T导通

VCC 5kΩ

RD

2、工作原理

<2VCC/3 <VCC/3

vI1

vIC

+ C1 - 5kΩ

vO

t

VOH

VOL 0

{End}

8.3

多谐振荡器

8.3.1 由门电路组成的多谐振荡器 8.3.2 用施密特触发器构成波形产生电路 8.3.3 石英晶体振荡器

多谐振荡器是一种自激振荡电路,不需要外加输入 信号,就可以自动地产生出矩形脉冲。 开关器件:产生高、低电平

反馈延迟环节( RC电路):利用RC电路的充放电特

555定时器是一种将模拟功能与逻辑功能 巧妙结合在一起的中规模集成电路。该电路 功能灵活、适用范围广,只要外围电路稍作 配置,即可构成单稳触发器、多谐振荡器或 施密特触发器,因而可在定时、检测、控制、 报警等方面。

8.4

555定时器及其应用

8.4.1 555定时器 8.4.2 用555定时器组成施密特触发器

教学基本要求

1、正确理解多谐振荡器、单稳态触发器、施密特触

发器的电路组成及工作原理。 2、掌握多谐、单稳、施密特触发器MSI器件的逻辑

功能及主要指标计算。

3、掌握555定时器的工作原理。 4、掌握由555定时器组成的多谐、单稳、施密特触发 器的电路、工作原理及外接参数及电路指标的计算。

8 脉冲波形的变换与产生

回差电压(滞后电压): ΔVT= VT+-VT-

2、施密特触发器的两种电路形式

vo VOH

vO

VOH

VOL O

vI

VOL

VT- VT+

1

vI

vO

o VT - VT+

1

vI

vI

vO

反相输出施密特触发器

同相输出施密特触发器

1

vI

vO

8.2.2 集成施密特触发器

VDD TP1 vS2 TP2 vI TN5 vS5 TN4 施密特电路 TN6 VDD TP7 TN8 vO

电路的改进

VDD ui C1 R1 G1 ≥1 uo1 C R uA G2 ≥1 uo2

当ui的宽度很宽时,可在单稳态触发器的输入端加一 个RC微分电路,否则,在电路由暂稳态返回到稳态时, 由于门G1被ui封住了,会使uo2的下降沿变缓。

8.1.2 集成单稳态触发器

1. 不可重复触发的集成单稳态触发器 74121

ui 0 VDD ui VDD G2 ≥1 uA 0 t uo1 t uA t uo2 (a) 电路 0 tP (b) 波形 t

1 G1 0 C

≥1 uo1

R

1 uo2

VDD 0

(2)外加触发信号使电路由稳态翻转到暂稳态 当正触发脉冲ui到来时,门G1输出uo1由1 0。由于电容电压不 能跃变,uA也由1 0,使门G2的输出uO2变为1。这个高电平反 馈到门G1的输入端,此时即使ui的触发信号撤除,仍能维持门G1 的低电平输出。但是电路的这种状态是不能长久保持的,所以称 为暂稳态。暂稳态时,uo1=0,uo2=1。

t

t (b) 波形图

(a) 电路图

第一暂稳态及其自动翻转的工作过程

电路最初UO1=1、UO=0,电源经G1、G2对电容充电。当 Ui=Uth时,UO1减小,UO增大,电路进入第二暂稳态。

振荡周期为:T≈1.4RC

8.3.2 用施密特触发器构成波形产生电路 v

I

R

VT+ VT_

vI

C

1

vo

0

t

vo

VOH

Q

如用I作为下降沿触发 的计数器触发脉冲,干扰 vO 加入,就会造成计数错误.

单稳触发器的输出脉宽应大于噪声宽度而小于信号 脉宽,才可消除噪声。

{End}

5. 利用两个单稳态触发器可以构成方波产生器。

8.2

施密特触发器

8.2.1 用门电路组成的施密特触发器 8.2.2 集成施密特触发器 8.2.3 施密特触发器的应用

8.4.3 用555定时器组成单稳态触发器 8.4.4 用555定时器组成多谐振荡器

555定时器的封装一般有两种: 八脚圆形封装 八脚双列直插式封装。

8.4.1 555定时器

VCC(8)

5 k

1、电路 结构

RD (4) & R & Q