第八章 双极型集成电路1

第八章 大规模集成电路

9

图8-2

RAM存储矩阵的示意图

2564(256个字,每个字4位)RAM存储矩阵的 ( 示意图。 如果X0=Y0=1,则选中第一个信息单元的4个 存储单元,可以对这4个存储单元进行读出或写入。

10

(2)RAM 的读写原理 (以图8-1为例) 以图8 为例) 当CS =0时,RAM被选中工作。 0 若 A11A10A9A8A7A6A5A4A3A2A1A0=000000000000 表示选中列地址为A11A10A9A8=0000 A =0000、行地址为 A7A6A5A4A3A2A1A0=00000000的存储单元。 此时只有X0和Y0为有效,则选中第一个信息单 元的k个存储单元,可以对这k个存储单元进行读出 或写入。

20

由1024×8的 RAM扩展为4096×8的RAM ×图8-11 RAM字扩展 ×

21

字位扩展 例:将1024×4的RAM扩展为2048×8 RAM。 × × 位扩展需2片芯片,字扩展需2片芯片,共需4片 芯片。 字扩展只增加一条地址输入线A10,可用一反相 器便能实现对两片RAM片选端的控制。 字扩展是对存储器输入端口的扩展, 位扩展是对存储器输出端口的扩展。

大规模集成电路从制造工艺的角度,也可以分为两大类 大规模集成电路从制造工艺的角度,也可以分为两大类: 一类为双极型,另一类是MOS型大规模集成电路 一类为双极型,另一类是 型大规模集成电路 应用大规模集成电路后,可以有效地提高电子设备的性能, 应用大规模集成电路后,可以有效地提高电子设备的性能, 可以大大减少设备的体积和重量, 可以大大减少设备的体积和重量,降低功耗

3

一、动态MOS反相器 动态 反相器

1.动态有比 动态有比MOS反相器 动态有比 反相器 2.动态无比 动态无比MOS反相器 动态无比 反相器

数字集成电路的分类

数字集成电路的分类数字集成电路有多种分类方法,以下是几种常用的分类方法。

1.按结构工艺分按结构工艺分类,数字集成电路可以分为厚膜集成电路、薄膜集成电路、混合集成电路、半导体集成电路四大类。

图如下所示。

世界上生产最多、使用最多的为半导体集成电路。

半导体数字集成电路(以下简称数字集成电路)主要分为TTL、CMOS、ECL三大类。

ECL、TTL为双极型集成电路,构成的基本元器件为双极型半导体器件,其主要特点是速度快、负载能力强,但功耗较大、集成度较低。

双极型集成电路主要有TTL(Transistor-Transistor Logic)电路、ECL(Emitter Coupled Logic)电路和I2L(Integrated Injection Logic)电路等类型。

其中TTL电路的性能价格比最佳,故应用最广泛。

ECL,即发射极耦合逻辑电路,也称电流开关型逻辑电路。

它是利用运放原理通过晶体管射极耦合实现的门电路。

在所有数字电路中,它工作速度最高,其平均延迟时间tpd可小至1ns。

这种门电路输出阻抗低,负载能力强。

它的主要缺点是抗干扰能力差,电路功耗大。

MOS电路为单极型集成电路,又称为MOS集成电路,它采用金属-氧化物半导体场效应管(Metal Oxide Semi-conductor Field Effect Transistor,缩写为MOSFET)制造,其主要特点是结构简单、制造方便、集成度高、功耗低,但速度较慢。

MOS集成电路又分为PMOS(P-channel Metal Oxide Semiconductor,P沟道金属氧化物半导体)、NMOS(N-channel Metal Oxide Semiconductor,N沟道金属氧化物半导体)和CMOS(Complement Metal Oxide Semiconductor,复合互补金属氧化物半导体)等类型。

MOS电路中应用最广泛的为CMOS电路,CMOS数字电路中,应用最广泛的为4000、4500系列,它不但适用于通用逻辑电路的设计,而且综合性能也很好,它与TTL电路一起成为数字集成电路中两大主流产品。

电工电子技术第八章集成运算放大电路

8.1 集成运算放大器的简单介绍

• 运算放大器开环放大倍数大,并且具有深 度反馈,是一种高级的直接耦合放大电路。 它通常是作为独立单元存在电路中的。最 初是应用在模拟电子计算机上,可以独立 地完成加减、积分和微分等数学运算。早 期的运算放大器由电子管组成,自从20世 纪60年代初第一个集成运算放大器问世以 来,运算放大器才应用在模拟计算机的范 畴外,如在偏导运算、信号处理、信号测 量及波形产生等方面都获得了广泛的应用。

• 4.在集成电路中,比较合适的电阻阻值范 围大约为100 ~300 Ω。制作高阻值的电阻 成本高、占用面积大并且阻值偏差也较大 (10~20%)。因此,在集成运算放大器中 往往用晶体管恒流源代替高电阻,必须用 直流高阻值时,也常采用外接的方式。

8.1.2 集成运算放大器的简单说明

• 集成运算放大器的的电路常可分为输入级、 中间级、输出级和偏置电路四个基本组成 部分,如图8-1所示。

• 2.信号的输入 • 当有信号输入时,差动放大电路(见图8-5)的工作情况可以分为以下几种情

况。

• (1)共模输入。 • 若两管的基极加上一对大小相等、极性相同的共模信号(即vi1 = vi2),这种

输入方式称为共模输入。这将引起两管的基极电流沿着相同的方向发生变化, 集电极电流也沿相同方向变化,所以集电极电压变化的方向与大小也相同, 因此,输出电压vo = ΔvC1-ΔvC2 = 0,可见差动放大电路能够抑制共模信号。 而上述差动放大电路抑制零点漂移则是该电路抑制共模信号的一个特例。因 为输出的零点漂移电压折合到输入端,就相当于一对共模信号。

u

u

u0 Au 0

0

u+≈u-

(8-2)

• 当反向输入端有信号,而同向端接地时,u+=0,由上式 可见,u-≈u+=0。此时反向输入端的电位近似等于地电位, 因此,它是一个不接地的“地”电位端,通常称为虚地端。

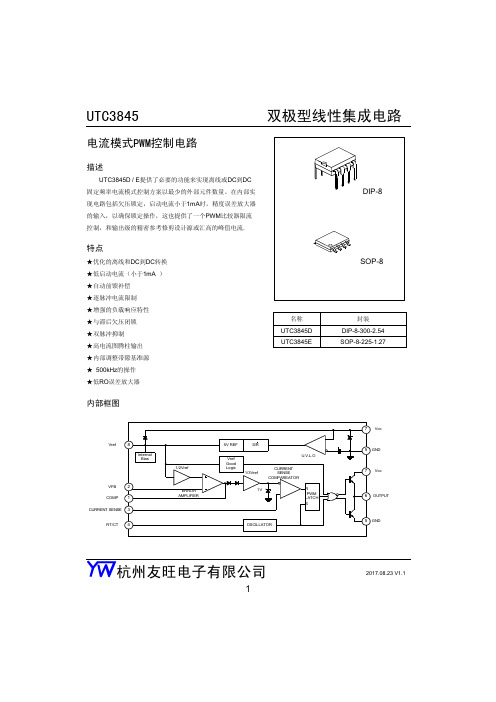

UTC3845双极型线性集成电路说明书

UTC3845 双极型线性集成电路1电流模式PWM 控制电路描述UTC3845D / E 提供了必要的功能来实现离线或DC 到DC 固定频率电流模式控制方案以最少的外部元件数量。

在内部实现电路包括欠压锁定,启动电流小于1mA 时,精度误差放大器的输入,以确保锁定操作,这也提供了一个PWM 比较器限流控制,和输出级的精密参考修剪设计源或汇高的峰值电流.特点★优化的离线和DC 到DC 转换 ★低启动电流(小于1mA ) ★自动前馈补偿 ★逐脉冲电流限制 ★增强的负载响应特性 ★与滞后欠压闭锁 ★双脉冲抑制 ★高电流图腾柱输出 ★内部调整带隙基准源 ★ 500kHz 的操作 ★低RO 误差放大器DIP-8SOP-8内部框图Vref VFB COMPCURRENT SENSERT/CT VccOUTPUTVccUTC3845双极型线性集成电路注1: Ta>25︒C,P D降额8mW/︒C.2UTC3845双极型线性集成电路3UTC3845 双极型线性集成电路4注2:这些参数仅供参考.注3测量的参数跳变点的闩锁 Vpin 2=0. 注4:增益:ΔVpin 1ΔVpin 3A=;0 ≤Vpin 3≤ 0.8V注5:调整Vcc 高于前启动阈值 15V.UTC3845 双极型线性集成电路5环路增益实验室测试电路VrefVccError Amp Adjust高峰值电流与容性负载,需要完善的接地处理技术.时间安排旁路电容应连接紧密,在的单点接地.晶体管和5kΩ的电位器用于样品振荡器波形并应用一个可调节的斜坡到引脚3到引脚5 。

欠压锁定VonVoffIccVcc在欠压锁定,输出驱动器偏置高阻抗状态。

6脚应该是一个泄放电阻,以防止启动电源开关,输出漏电流分流到地。

误差放大器配置误差放大器可以进出0.5mA 。

UTC3845双极型线性集成电路电流检测电路峰值电流(Is) 由以下公式决定:Ismax=10V/Rs.需要一个小的RC滤波器抑制开关转变。

集成电路的分类

集成电路的分类

集成电路的分类

1.按制造工艺和结构分类

可分为:半导体集成电路、膜集成电路、混合集成电路。

通常所说的集成

电路指的就是半导体集成电路。

膜集成电路又可分为薄膜和厚膜两类。

膜集

成电路和混合集成电路一般用于专用集成电路,通常称为模块。

2.按半导体工艺分类

⑴双极型集成电路

在硅片上制作双极型晶体管所生产的集成电路。

⑵MOS集成电路

在硅片制作MOS场效应管所生产的集成电路。

⑶双极型—MOS集成电路(BIMOS)

常将MOS电路作输入电路,双极型晶体管作输出电路,构成BIMOS集成电路。

3.按集成度分类

集成度是指一块硅片上含有元件数目。

表1-14给出了早期对集成度的分类:

表1-14 按集成度分类。

双极型集成运算放大器

双极型集成运算放大器的电压放大倍数一般在1000倍以上,甚至可达到10万倍以上。

2. 高输入电阻

双极型集成运算放大器的输入级采用差分放大电路,其输入电阻高达兆欧级别,可以减少 信号源的负担。

定义与特点

3. 低输出电阻

双极型集成运算放大器的输出级采用 推挽电路,其输出电阻极低,使得负 载对放大器性能的影响较小。

积分和微分运算

通过适当的外接元件,双极型集成运 算放大器可以实现信号的积分和微分 运算,用于模拟电路中的滤波器和控 制系统。

有源滤波器

低通滤波器

利用双极型集成运算放大器和适当的外接元件,可以构成低通滤波器,用于滤除信号中的高频噪声。

高通滤波器

同样利用双极型集成运算放大器和外接元件,可以构成高通滤波器,用于提取信号中的高频成分。

噪声性能

双极型集成运算放大器的噪声性能 通常优于单极型,特别是在低频范 围内。

与场效应管放大器的比较

线性范围

双极型集成运算放大器的线性范 围更广,适用于多种信号处理任 务。场效应管放大器则线性范围

相对较小。

频率响应

场效应管放大器通常具有更好的 频率响应特性,适用于高频应用。

双极型则适用于中低频应用。

温度稳定性与封装选择

温度稳定性

双极型运算放大器的性能受温度影响较大, 因此应选择具有良好温度稳定性的型号。同 时,可以在电路设计中加入温度补偿元件, 以减小温度对放大器性能的影响。

封装选择

在选择双极型运算放大器时,应考虑其封装 形式。合适的封装可以减小外部干扰,提高 放大器的可靠性。常见的封装形式有DIP、

输出电阻是指运算放大器输出端的等 效电阻,反映了输出信号的负载能力。

带宽增益乘积

第八章 数字集成电路基本单元及版图

§7.数字电路标准单元库设计简介

基本设计思想 用人工设计好的各种成熟的、优化的、 版图等高的单元电路,存储在一个单元数据 库中。根据用户的要求,把电路分成各个单 元的连接组合。通过调用单元库的这些单元, 以适当方式把它们排成几行,使芯片成长方 形,行间留出足够的空隙作为单元行间的连 线通道。利用EDA工具,根据已有的布局、 布线算法,可以自动布出用户所要求的IC。

TTL基本电路及版图实现

IC的版图设计已把电路与工艺融为一体,所以一般 较复杂的电路都是先设计实验电路(或单元电路), 根据实验电路的测试结果获得有关电路功能和电路 参数的第一手资料。 掌握了这些资料,就可以根据元件的不同要求,在 设计中采取相应措施,保证电路达到设计目标。必 要时还要调整个别工艺或工艺参数。 当然设计出的版图要经过实践不断加以改进,一个 成熟的产品一般都要经过几次改版才行。

υ1

T3 Re2

负 载

v0 -

-

GND

TTL基本电路

(1)电路组成 该电路由三部分组成: 1)由双极型晶体管T1和电阻Rb1组成电路输入级。 2)由T2、Re2和Rc2组成中间驱动电路,将单端信号 υB2转换为双端信号υB3和υB4。 3)由T3、T4、Rc4和二级管D组成输出级。 (2)工作原理 输入为高电平时,输出为低电平。 输入为低电平时,输出为高电平。

CMOS反相器

瞬态特性

我们希望反相器的上升时间和下降时间近似相等,则 需要使PMOS管的沟道宽度必须加宽到NMOS管沟道 宽度的 n / p倍左右。 V (t)

i

+VDD 0 t Vo(t) +VDD 0.9VDD 0.1VDD 0

td tf tr

双极型集成电路

双极型集成电路双极型集成电路,简称双极型IC,是一种晶体管集成电路,其特征是只有两对对极:负极(集电极)和正极(发射极)。

它以一种传统的放大方式,经常与双极型放大器、单稳放大器、一步放大器配套使用,广泛应用在电子设备和功能性元件电路中。

双极型IC的特点在于只有两对对极,而且由晶体管构成,所以它是半导体器件中一种重要的产品,也是电子器件制造的重要组成部分。

双极型IC可以完成一些复杂的功能,比如比较、空间位置检测、模拟信号处理和数字信号处理等。

双极型的晶体管装置可以进行非常复杂的处理,因此双极型IC在许多电子设备中得到广泛应用,比如电脑、手机、数码摄像机、游戏机等。

双极型集成电路模块是半导体封装的重要产品,它利用半导体封装技术,将数据、电源和信号线装载到一个封装模块中,进行多层的封装。

它的优势在于封装物的体积小,性能稳定,使用广泛,可以简化原有的电路,减少电路的故障,从而提高整个系统的可靠性。

此外,双极型集成电路的制造工艺也十分重要,一般来讲,当双极型集成电路组成比较复杂时,就需要采用更加精细、先进的制造工艺,比如利用贴片技术,单片机技术,及其他微系统技术,确保双极型集成电路的性能达到设计要求。

在量产双极型IC时,还要注意对其进行测试,以确保其性能满足设计要求。

除了本身的生产厂商外,还需要第三方的检测机构进行测试,检查双极型IC的可靠性、可用性和可编程等性能参数。

双极型集成电路是一种重要的晶体管装置,也是电子设备的重要组成部分。

它的特点是只有两对对极,并且由晶体管构成,配合双极型放大器、单稳放大器、一步放大器等电子设备,可以完成复杂的功能。

在双极型集成电路的制造过程中,除了采用先进的制造工艺之外,还需要重视测试工作,以保证可靠性和可用性。

IC基础知识及制造工艺流程

0.0008-cm(发射区)

第9页/共67页

2024/7/5

9

硅片主要技术指标

-晶向 (111)/(100) -掺杂类型/掺杂剂 P/N -电阻率 -直径/厚度 -平整度/弯曲度/翘曲度 -含氧量/含碳量 -缺陷(位错密度/层错密度) -表面颗粒

第10页/共67页

2024/7/5

10

目录

-最重要的半导体材料-硅 -构建集成电路的主要半导体器件 -关键的集成电路工艺制造技术 -集成电路技术发展趋势

第63页/共67页

2024/7/5

63

IC制造环境(3)

超纯化学药品

DRAM 64k 线宽(um) 3.0 试剂纯度 10pp

m 杂质颗粒 0.5u

颗粒含量 1000 (个/ ml) 金属杂质

256K 4M 2.0 1.0 5ppm 100pp

b

0.2u 0.1u

64M

0.5

80pp b 0.05u

等离子体 F*

扩散 吸附 反应

解吸附

第21页/共67页

2024/7/5

21

RIE刻蚀装置(Parallel Plate)

Gas

RF

2024/7/5

Pumping System

第22页/共67页

22

RIE刻蚀机 (AME8330)

第23页/共67页

2024/7/5

23

IC基础工艺(2)-刻蚀

被刻膜 SiO2 Si Al

第4页/共67页

2024/7/5

4

绝缘体/半导体/导体

-绝缘体 -半导体 -导体

电阻率=108-1018-cm 石英、玻璃、 塑料

电阻率=10-3-108-cm 锗、硅 、砷化镓 、磷化铟

集成电路第8章I0.ppt

流Ih。

2024/9/30

18

第二节 输入保护电路

其中条件(2)的推导如下

设外界干扰引起的触发电流IAG 使Q1的EB结正偏电压大于≥0.7V。

此时Q1导通,若 IC1流过Rw产生的压降大于0.7V,就能使Q2也导

2024/9/30

12

第二节 输入保护电路

二、输入保护电路 2、上图所示可以很好保护NMOS管栅极,但是对PMOS管栅极保 护作用较差。若把二极管接在VDD和输入端之间,则对PMOS管 栅极保护作用好而对NMOS栅极保护差。 因此,CMOS IC中一般都采用双二极管保护电路,用两个二极管 和一个电阻构成的保护电路。

一旦发生闩锁效应,CMOS电路的电源和地之间就处于近似 短路的状态,这势必破坏电路的正常工作。此时只有将电源关 断,然后重新接通,电路才可能恢复正常工作。如果这种电流不 加限制,最终将使整个电路烧毁。

2024/9/30

17

第二节 输入保护电路

CMOS电路版图中的闩锁效应

产生闩锁效应的基本条件有三个: (1)外界因素使两个寄生三极管的EB结处于大于等于0.7的正向

2024/9/30

1

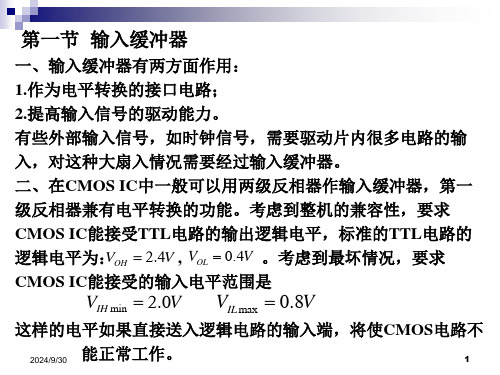

第一节 输入缓冲器

要通过输入缓冲器转换成合格的CMOS逻辑电平,再送到其他电

路的输入端。可以通过一个专门设计的CMOS反相器实现电平转

换,它的逻辑阈值设计在输入高、低电平范围之间,即

Vit

VIH min

VILmax 2

1.4V

若 VDD 5V VTN VTP 0.8V ,则要求输入级反相器的比例因子

2024/9/30

半导体集成电路课程教学大纲

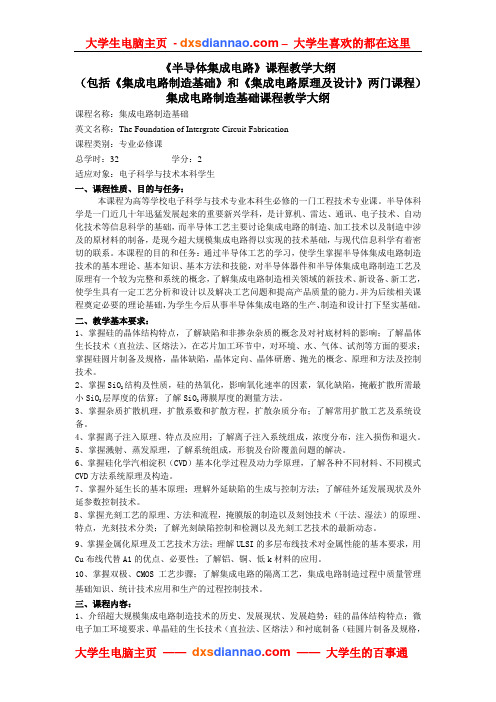

《半导体集成电路》课程教学大纲(包括《集成电路制造基础》和《集成电路原理及设计》两门课程)集成电路制造基础课程教学大纲课程名称:集成电路制造基础英文名称:The Foundation of Intergrate Circuit Fabrication课程类别:专业必修课总学时:32 学分:2适应对象:电子科学与技术本科学生一、课程性质、目的与任务:本课程为高等学校电子科学与技术专业本科生必修的一门工程技术专业课。

半导体科学是一门近几十年迅猛发展起来的重要新兴学科,是计算机、雷达、通讯、电子技术、自动化技术等信息科学的基础,而半导体工艺主要讨论集成电路的制造、加工技术以及制造中涉及的原材料的制备,是现今超大规模集成电路得以实现的技术基础,与现代信息科学有着密切的联系。

本课程的目的和任务:通过半导体工艺的学习,使学生掌握半导体集成电路制造技术的基本理论、基本知识、基本方法和技能,对半导体器件和半导体集成电路制造工艺及原理有一个较为完整和系统的概念,了解集成电路制造相关领域的新技术、新设备、新工艺,使学生具有一定工艺分析和设计以及解决工艺问题和提高产品质量的能力。

并为后续相关课程奠定必要的理论基础,为学生今后从事半导体集成电路的生产、制造和设计打下坚实基础。

二、教学基本要求:1、掌握硅的晶体结构特点,了解缺陷和非掺杂杂质的概念及对衬底材料的影响;了解晶体生长技术(直拉法、区熔法),在芯片加工环节中,对环境、水、气体、试剂等方面的要求;掌握硅圆片制备及规格,晶体缺陷,晶体定向、晶体研磨、抛光的概念、原理和方法及控制技术。

2、掌握SiO2结构及性质,硅的热氧化,影响氧化速率的因素,氧化缺陷,掩蔽扩散所需最小SiO2层厚度的估算;了解SiO2薄膜厚度的测量方法。

3、掌握杂质扩散机理,扩散系数和扩散方程,扩散杂质分布;了解常用扩散工艺及系统设备。

4、掌握离子注入原理、特点及应用;了解离子注入系统组成,浓度分布,注入损伤和退火。

北大集成电路版图设计课件_第8章 MOS场效应晶体管

V+

N阱

V-

P型衬底

三. MOS管版图设计技巧

衬底连接与阱连接 设置阱连接的经验法则是在满足设计规则的前提下,在阱的空

闲区域尽可能多地设置阱连接。比较常用的设置阱连接的方式

是用阱连接环绕MOS晶体管。设置衬底连接的经验法则也是

是在满足设计规则的前提下,在衬底的空闲区域尽可能多地设

置衬底连接。

阱

连

接

In(D / C) L (D C)

2

三. MOS管版图设计技巧

衬底连接与阱连接 制作CMOS集成电路有N阱工艺、P阱工艺和双阱工艺,无论 哪种工艺,在阱和衬底之间都存在PN结。以N阱工艺为例, 在P型衬底和N阱之间存在PN结。为了保证PN结的有效隔离, N阱的电位必须高于P型衬底的电位,最简单最可靠的方法是 将N阱接最正的电源,P型衬底接最负的电源。在版图设计中, 将设置衬底或阱连接的方式称为衬底连接或阱连接。

一. 概述

MOS晶体管是四端器件,具有源极(S)、漏极(D)、栅 极(G)和衬底(B)四个电极,按导电类型分为NMOS晶体 管和PMOS晶体管两种.

(a)NMOS

(b)PMOS

一. 概述

二. MOS管的版图

NMOS晶体管的立体图和俯视图

(a)立体图

(b)俯视图

二. MOS管的版图

图 PMOS晶体管的版图示意图

二. MOS管的版图

阱层(Well): 阱层定义在衬底上制备阱的区域。NMOS 管制备在P型衬底上,PMOS管制备在N 型衬底上。一块原始的半导体材料,掺入 的杂质类型只能有一种,即该衬底不是N 型就是P型。如果不对衬底进行加工处理 的话,该衬底只能制备一种MOS晶体管。 CMOS集成电路是把NMOS晶体管和 PMOS晶体管制备在同一个硅片衬底上, 为了能够制造CMOS集成电路,需要对衬 底进行处理,利用掺杂工艺在衬底上形成 一个区域,该区域的掺杂类型和衬底的掺 杂类型相反,这个区域就称为阱。

数字电子技术_集成电路知识概述

(c)

(d)

1、TTL与非门电路

输入级 中间级 输出级

由多发射极三极管 VT1和电阻R1组成

为典型的单变量 C1输入的分相器

为典型的复合管和 图腾柱输出形式

R1

+5V

R2 T3 R5 T5

R4

T2 T4

A B C

T1

F

T1 —多发射极 晶体管:实现 “与”运算。

R3

输入级

返回

中间级

输出级

R1

+5V

E

返回

3.3.1 简单逻辑门电路

1 二极管与门 最简单的与门可以用二极管和电阻组成。设 VCC=5v,A、B端输入的高低电平分别为 VIH=3v,VIL=0v,二极管VD1、VD2的正向导通压 降VDF=0.7v。

必有一个二极 管导通

A、B当中 有一个是低 电平0v

使F为0.7v

最简单的与门可以用二极管和电阻组成。设 VCC=5v,A、B端输入的高低电平分别为 VIH=3v,VIL=0v,二极管VD1、VD2的正向导通压 降VDF=0.7v。

T4

F

T5

R1 3k 0.7V b1 A B C “0”

R2 750

R4 100 T4

+5V

c1

T1

R3

T2

T3 3k R5

F

T5

360

uo

uo=5-uR2-ube3-ube43.4V 高电平!

逻辑关系:任意一个输入为0时,输出为1

返回

2>. 输入全为高电平(3.4V)时

电位被嵌 在2.1V 全反偏

2.中间级形式 对于功能不同的门,这部分电路不一样。例如 TTL与非门中间级就是分相器;或非门中间级就 是线与电路。 ⑴ 单变量分相器

双极型集成电路可靠性技术

3 结 论

综 上所 述,要 想全 面提 高双 极 型集成 电 路可靠性工艺 的有 效性、持久性 与耐用性,其 根本便 需要科 学控制双极 型集成 电路的各个指 标 ,比如热载子流 效应 、辐 射效应 以及静 电效 应等 ,以此来有效提 高双 极型集 成电路在实践

应用 中的可靠性与稳定性 。 通过 以上相关分析 , 接 ”,以此来减 少双 极型集 成电路对热载子流 在 日后双极型集成 电路 的应 用过 程中,要充分 把握好整体 电路组 的可靠性 ,准 确确定双极型 集成 电路 的热载子流 力以及 迁移 力,从而来保 护双极 型集成 电路在 更为均 衡与可靠的环境下

选 择科 学 的双极 型集成 电路范 围作 为提 完 成 电流 作 业 。

高双极 型集成 电路可靠性的重要步骤,应该明 确对双极 型集成 电路 范围灵活运用与科学衡量 的思想 与理念 。为了在 双极型集成 电路作业中 尽可 能的缩 小键 合丝 的磨损 程度、受热程度与 受 热范 围,要根据双 极型集 成电路 内部键合丝 自身的物 理性质 与具体变形状态,采取不 同规

参考文献

[ 1 ] 王林 , 赵 宇军 , 等人 .军用双板型数 字集 成 电路 的可 靠性 保证 [ J ] .电子 产品可 靠

实践方法下, 灵活并熟练运用 电流“ 减应区 ” 法 其原理与预留传输 电流法类似 ,对双极型集成 电路中的部分 电线进行分组式调节与测试 ,但 是其不 同点便是 电流 “ 减应 区”法会在高速作 业后对膜层进行均匀 的冷却 。这样通过均匀 的 冷却之后,使得膜层 自身 的抗应力得到释放 , 由,从而减少双极型集成 电路作业 中的误 差,

路在 实践应 用 中的可 靠性 与 实用

性

第八章双极型集成电路1

2020/7/13

47

接触孔和通孔

金属2

金属1

金属1

通

孔

接触 孔

金属2

2020/7/13

48

补充2:芯片封装工艺

2020/7/13

49

(1)封装工序流程

2020/7/13

50

(2)管芯分割工艺

2020/7/13

51

(3)芯片粘贴

2020/7/13

52

(4)引线键合

2020/7/13

53

(5)模压(塑封) (6)封装分类

• 氮化硅的化学气相淀积:中等温度(780~ 820℃)的LPCVD或低温(300℃) PECVD方法 淀积

2020/7/13

41

3、物理气相淀积(PVD)

• 蒸发:在真空系统中,金属原子获得足够的 能量后便可以脱离金属表面的束缚成为蒸汽 原子,淀积在晶片上。按照能量来源的不同 ,有灯丝加热蒸发和电子束蒸发两种

• 热分解淀积法

2020/7/13

32

进行干氧和湿氧氧化的氧化炉示意图

2020/7/13

33

2020/7/13

34

2、化学气相淀积(CVD)

• 化学气相淀积(Chemical Vapor Deposition):通 过气态物质的化学反应在衬底上淀积一层薄膜材 料的过程

• CVD技术特点:

– 具有淀积温度低、不消耗衬底材料、薄膜成分 和厚度易于控制、均匀性和重复性好、台阶覆 盖优良、适用范围广、设备简单等一系列优点

• 作为集成电路的隔离介质材料

• 作为电容器的绝缘介质材料

• 作为多层金属互连层之间的介质材料

• 作为对器件和电路进行钝化的钝化层 材料

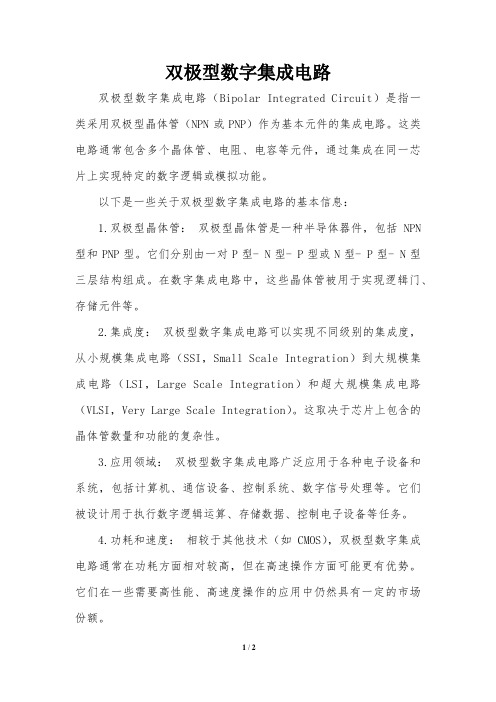

双极型数字集成电路

双极型数字集成电路双极型数字集成电路(Bipolar Integrated Circuit)是指一类采用双极型晶体管(NPN或PNP)作为基本元件的集成电路。

这类电路通常包含多个晶体管、电阻、电容等元件,通过集成在同一芯片上实现特定的数字逻辑或模拟功能。

以下是一些关于双极型数字集成电路的基本信息:1.双极型晶体管:双极型晶体管是一种半导体器件,包括NPN 型和PNP型。

它们分别由一对P型- N型- P型或N型- P型- N型三层结构组成。

在数字集成电路中,这些晶体管被用于实现逻辑门、存储元件等。

2.集成度:双极型数字集成电路可以实现不同级别的集成度,从小规模集成电路(SSI,Small Scale Integration)到大规模集成电路(LSI,Large Scale Integration)和超大规模集成电路(VLSI,Very Large Scale Integration)。

这取决于芯片上包含的晶体管数量和功能的复杂性。

3.应用领域:双极型数字集成电路广泛应用于各种电子设备和系统,包括计算机、通信设备、控制系统、数字信号处理等。

它们被设计用于执行数字逻辑运算、存储数据、控制电子设备等任务。

4.功耗和速度:相较于其他技术(如CMOS),双极型数字集成电路通常在功耗方面相对较高,但在高速操作方面可能更有优势。

它们在一些需要高性能、高速度操作的应用中仍然具有一定的市场份额。

5.逐步淘汰:随着技术的发展,CMOS(亦称为互补金属氧化物半导体)技术在数字集成电路中逐渐占据主导地位,因为它在功耗、集成度和工艺成本等方面具有优势。

因此,双极型数字集成电路在某些领域逐渐被淘汰。

需要注意的是,随着技术的不断发展,数字集成电路的设计和制造技术也在不断演进,而CMOS技术目前已成为主流。

简述双极型集成电路的工艺流程

简述双极型集成电路的工艺流程英文回答:Bipolar Integrated Circuit Fabrication Process.The fabrication process of bipolar integrated circuits involves several key steps, including:1. Substrate Preparation: The process begins with preparing the silicon substrate by cleaning and oxidizing it to form a thin layer of silicon dioxide (SiO2).2. Epitaxial Layer Formation: An epitaxial layer of silicon is deposited on the substrate to create a region with controlled electrical properties suitable for transistors.3. Isolation Diffusion: Boron or phosphorus ions are diffused into the substrate to create isolation regions, separating different components of the circuit.4. Base Diffusion: Boron or phosphorus ions arediffused into selected regions to form the transistor base regions.5. Emitter Diffusion: Phosphorus or arsenic ions are diffused into the base regions to form the transistor emitter regions.6. Contact Formation: Metal contacts are deposited and patterned to connect the different components of the circuit.7. Passivation: A layer of silicon nitride or polyimide is deposited to protect the circuit from external contaminants.8. Packaging: The circuit is encapsulated in a protective package to provide mechanical and environmental protection.中文回答:双极型集成电路的工艺流程。

双极型集成电路工艺

双极型集成电路工艺(详案)各位同学:大家好!本节课将给大家介绍双极型集成电路的制造方法和过程,也就是制作工艺。

首先我们作一些必要的知识准备,来复习一下集成电路的相关知识。

广义的集成电路通俗的讲就是我们常说的芯片,它是将若干电子元件制作在一块单晶硅片上,并用金属或多晶硅互联线将它们连结起来的具有一定功能的电路,这些半导体电子元件包括:双极型晶体管、场效应管、二极管、电阻、电感、电容等。

世界上第一块IC 是由仙童半导体公司的Robert Noyce 和德州仪器公司的Jack Kilby 于是1959年分别独自发明的。

集成电路按照不同的标准可以有很多分类。

最常见的是按照处理信号的连续性来分类,可分为模拟集成电路和数字集成电路,模拟集成电路处理的是时间连续的模拟信号,而数字集成电路处理的则是时间与幅度取值都离散的数字信号。

还有一种分类方法是按构成集成电路的有源元件的种类来划分的,若构成电路的有源元件只有双极型晶体管,则为双极型集成电路;若构成电路的有源元件只有MOS 管(场效应晶体管),则为MOS 集成电路;若电路中既有双极型晶体管,又有MOS 管,则为BiCMOS 集成电路。

以上我们简单介绍了集成电路的划分,生产每一种集成电路都需要相应的制造工艺,比如双极型集成电路需要双极型集成电路工艺,MOS 集成电路需要MOS 工艺,而BiCMOS 集成电路则需要的相应的BiCMOS 工艺等等。

双极型集成电路工艺是所有集成电路工艺中最早发明的,尽管受到CMOS 工艺的巨大挑战,它仍然在高速、模拟、功率等类型的电路中占有很重要的地位。

双极型集成电路工艺按其所采用的隔离类型可分为两类,一类是采用介质隔离,也即在器件之间制备P-N 结作电隔离区,一类采用自然隔离。

采用介质隔离双极型集成电路工艺制作的电路有TTL(晶体管—晶体管逻辑) 电路、ECL(射极耦合逻辑)电路、STTL (肖特基晶体管—晶体管逻辑)电路等,而I 2 采用P-N 结作介质隔离的双极工艺按照制作的晶体管结构又可进一步细分为三种类型,即标准的埋入集电极晶体管工艺(SBC ),集电极扩散隔离晶体管工艺(CDI ),三重扩散晶体管工艺(3D )。

电路常识性概念

输入电平 74LS TTL 电平 TTL 输出电平 电平74HCCOMS 电平 COMS 电平74HCT TTL 电平 COMS 电平电路常识性概念(3) -TTL 与CMO 集成电路2009-03-17 19:31目前应用最广泛的数字电路是 TTL 电路和CMOS 电路。

1、 TTL 电路TTL 电路以双极型晶体管为开关元件,所以又称 双极型集成电路。

双极型 数字集成电路是利用电子和空穴两种不同极性的载流子进行电传导的器件。

它具有速度高(开关速度快)、驱动能力强等优点,但其功耗较大,集成度 相对较低。

根据应用领域的不同,它分为54系列和74系列,前者为军品,一般工业设 备和消费类电子产品多用后者。

74系列数字集成电路是国际上通用的标准电路。

其品种分为六大类:74XX (标准)、74S XX (肖特基)、74LS XX (低功耗 肖特基)、74AS XX (先进肖特基)、74ALS XX (先进低功耗肖特基)、74F XX (高速)、其逻辑功能完全相同。

2、 CMO 电路MOS 电路又称场效应集成电路,属于 单极型数字集成电路。

单极型数字集 成电路中只利用一种极性的载流子(电子或空穴)进行电传导。

它的主要优点是输入阻抗高、功耗低、抗干扰能力强且适合大规模集成。

特 别是其主导产品CMOS 集成电路有着特殊的优点,如静态功耗几乎为零,输出 逻辑电平可为VDD 或VSS ,上升和下降时间处于同数量级等, 因而CMOS 集成 电路产品已成为集成电路的主流之一。

其品种包括4000系列的CMOS 电路以及74系列的高速CMOS 电路。

其中 74系列的高速 CMOS 电路又分为三大类:HC 为CMOS 工作电平:HCT 为TTL 工作电平(它可与74LS 系列互换使用):HCU 适用于无缓冲级的 CMOS 电路。

74系列高速CMOS 电路的逻辑功能和引脚排列与相应的 74LS 系列的品种相同, 工作速度也相当高,功耗大为降低。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

46

补充1:接触与互连 蒸发或溅射 →芯片表面形成金属膜 →光刻和腐蚀 →连线 集成电路中的互连线一般采用金属(铝、铜), 有时也用多晶硅(电阻率较高)。 Al是目前集成电路工艺中最常用的金属互连材 料, 但Al连线也存在一些比较严重的问题 – 电阻率偏高、浅结穿透等 Cu连线工艺有望从根本上解决该问题 – IBM、Motorola等已经开发成功 目前,互连线已经占到芯片总面积的70~80%; 且连线的宽度越来越窄,电流密度迅速增加

19

杂质横向扩散示意图

20

固态源扩散:如B2O3、P2O5、BN等

21

22

利用液态源进行扩散的装置示意图

23

24

离子注入

• 离子注入:将具有很高能量的杂质离子射 入半导体衬底中的掺杂技术,掺杂深度由 注入杂质离子的能量和质量决定,掺杂浓 度由注入杂质离子的数目(剂量)决定

– – – – – – 掺杂的均匀性好 温度低:小于600℃ 可以精确控制杂质分布 可以注入各种各样的元素 横向扩展比扩散要小得多。 可以对化合物半导体进行掺杂

30

氧化硅层的主要作用

• 在MOS电路中作为MOS器件的绝缘栅 介质,器件的组成部分 • 扩散时的掩蔽层,离子注入的(有时与 光刻胶、Si3N4层一起使用)阻挡层 • 作为集成电路的隔离介质材料 • 作为电容器的绝缘介质材料 • 作为多层金属互连层之间的介质材料 • 作为对器件和电路进行钝化的钝化层 材料

25

离子注入系统的原理示意图

26

离子注入到无定形靶中的分布情况

27

掺杂工艺存在的主要问题:对衬底晶格的损伤。

离子注入后,一般都要经过退火处理。

28

退

火

• 退火:也叫热处理,集成电路工艺中所 有的在氮气等不活泼气氛中进行的热处 理过程都可以称为退火

– 激活杂质:使不在晶格位置上的离子运动 到晶格位置,以便具有电活性,产生自由 载流子,起到杂质的作用 – 消除损伤

35

化学气相淀积(CVD) • 常压化学气相淀积(APCVD) • 低压化学气相淀积(LPCVD) • 等离子增强化学气相淀积 (PECVD)

36

APCVD反应器的结构示意图

37

LPCVD反应器的结构示意图

38

平行板型PECVD反应器的结构示意图

39

化学气相淀积(CVD)

• 单晶硅的化学气相淀积(外延):一般地,将 在单晶衬底上生长单晶材料的工艺叫做外延, 生长有外延层的晶体片叫做外延片 • 二氧化硅的化学气相淀积:可以作为金属化 时的介质层,而且还可以作为离子注入或扩 散的掩蔽膜,甚至还可以将掺磷、硼或砷的 氧化物用作扩散源 – 低温CVD氧化层:低于500℃ – 中等温度淀积:500~800℃ – 高温淀积:900℃左右

13

• 超细线条光刻技术

–甚远紫外线(EUV) –电子束光刻 –X射线 –离子束光刻

14

图形转换:刻蚀技术

• 湿法刻蚀: 利用液态化学试剂或

溶液通过化学反应进行刻蚀的方法

• 干法刻蚀: 主要指利用低压放电

产生的等离子体中的离子或游离基 (处于激发态的分子、原子及各种 原子基团等)与材料发生化学反应 或通过轰击等物理作用而达到刻蚀 的目的

• 掺杂:根据设计的需要,将各种杂质掺

杂在需要的位置上,形成晶体管、接触等

• 制膜:制作各种材料的薄膜

6

一、图形转换:光刻

7

光刻机

8

• 光刻三要素:光刻胶、掩膜版和光刻机

– 光刻胶又叫光致抗蚀剂,它是由光敏化合物、 基体树脂和有机溶剂等混合而成的胶状液体 – 光刻胶受到特定波长光线的作用后,导致其 化学结构发生变化,使光刻胶在某种特定溶 液中的溶解特性改变

31

• 热氧化法

SiO2的制备方法

– 干氧氧化 – 水蒸汽氧化 – 湿氧氧化 – 干氧-湿氧-干氧(简称干湿干)氧化 法 – 氢氧合成氧化

• 化学气相淀积法 • 热分解淀积法

32

进行干氧和湿氧氧化的氧化炉示意图

33

34

2、化学气相淀积(CVD)

• 化学气相淀积(Chemical Vapor Deposition):通过 气态物质的化学反应在衬底上淀积一层薄膜材料 的过程 • CVD技术特点: – 具有淀积温度低、不消耗衬底材料、薄膜成分 和厚度易于控制、均匀性和重复性好、台阶覆 盖优良、适用范围广、设备简单等一系列优点 – CVD方法几乎可以淀积集成电路工艺中所需要 的各种薄膜,例如掺杂或不掺杂的SiO2、多晶 硅、非晶硅、氮化硅、金属(钨、钼)等

17

二、杂质掺杂

• 掺杂:将需要的杂质掺入特定的半导体区 域中,以达到改变半导体电学性质,形成 PN结、电阻、欧姆接触 – 磷(P)、砷(As) —— N型硅 – 硼(B) —— P型硅 • 掺杂工艺:扩散、离子注入

18

扩 散

• 替位式扩散:杂质离子占据硅原子的位: – Ⅲ、Ⅴ族元素 – 一般要在很高的温度(950~1280℃)下进行 – 磷、硼、砷等在二氧化硅层中的扩散系数均远 小于在硅中的扩散系数,可以利用氧化层作为 杂质扩散的掩蔽层 • 间隙式扩散:杂质离子位于晶格间隙: – Na、K、Fe、Cu、Au 等元素 – 扩散系数要比替位式扩散大6~7个数量级

0.1um I级 35 10 级 350 100级 NA 1000级 NA

0.2um 0.3um 0.5um 7.5 3 1 75 30 10 750 300 100 NA NA 1000

5.0um NA NA NA 7

56

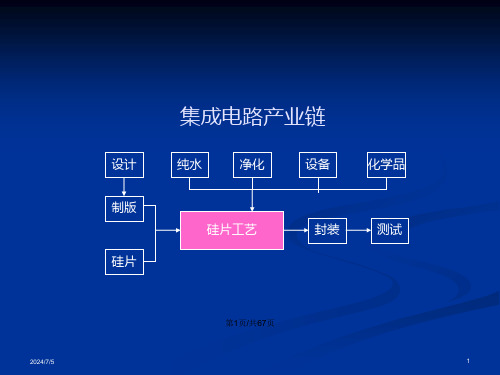

系 统 需 求 设计 掩膜版

芯片制 造过程

单晶、外 延材料

芯片检测

封装

测试

3

芯片制造过程

4

芯片制造过程

硅片 由氧化、淀积、离子注入或蒸 发形成新的薄膜或膜层

用掩膜版 重复 20-30次

曝 光

刻 蚀

测试和封装

5

§8-1 集成电路制造工艺

• 图形转换:将设计在掩膜版(类似于照

相底片)上的图形转移到半导体单晶片上

47

• •

• •

接触孔和通孔

金属2 金属1

金属1

Байду номын сангаас

通 孔

接触 孔

金属2

48

补充2:芯片封装工艺

49

(1)封装工序流程

50

(2)管芯分割工艺

51

(3)芯片粘贴

52

(4)引线键合

53

(5)模压(塑封)

(6)封装分类

54

(6)封装分类

55

补充3:半导体制造环境要求 • 主要污染源:微尘颗粒、重金属离子、有 机物残留物和钠离子等轻金属离子。 • 超净间:洁净等级主要由 微尘颗粒数/m3

40

化学气相淀积(CVD)

• 多晶硅的化学气相淀积:利用多晶硅替代金 属铝作为MOS器件的栅极是MOS集成电路技 术的重大突破之一,它比利用金属铝作为栅 极的MOS器件性能得到很大提高,而且采用 多晶硅栅技术可以实现源漏区自对准离子注 入,使MOS集成电路的集成度得到很大提高。 • 氮化硅的化学气相淀积:中等温度(780~ 820℃)的LPCVD或低温(300℃) PECVD方法 淀积

第八章

双极型集成电路

1

内容提要

• 8.1 集成电路制造工艺 • 8.2 电学隔离

• 8.3 pn结隔离集成电路工艺流程

• 8.4 IC中的元件结构与寄生效应 • 8.5 TTL门电路的工作原理和基本参数 • 8.6 TTL门电路的改进 • 8.7 双极型数字电路的版图设计

2

• 集成电路设计与制造的主要流程框架

• 退火方式:

– 炉退火 – 快速退火:脉冲激光法、扫描电子束、连 续波激光、非相干宽带频光源(如卤光灯、 电弧灯、石墨加热器、红外设备等)

29

三、制膜 1、氧化工艺

• 氧化:制备SiO2层 • SiO2的性质及其作用 SiO2是一种十分理想的电绝缘 材料,它的化学性质非常稳定, 室温下它只与氢氟酸发生化学 反应

41

3、物理气相淀积(PVD)

• 蒸发:在真空系统中,金属原子获得足够的 能量后便可以脱离金属表面的束缚成为蒸汽 原子,淀积在晶片上。按照能量来源的不同, 有灯丝加热蒸发和电子束蒸发两种 • 溅射:真空系统中充入惰性气体,在高压电 场作用下,气体放电形成的离子被强电场加 速,轰击靶材料,使靶原子逸出并被溅射到 晶片上

42

蒸

发

原

理

图

43

蒸发台

44

45

小结:集成电路工艺

• 图形转换:

– 光刻:接触光刻、接近光刻、投影光刻、 电子束光刻 – 刻蚀:干法刻蚀、湿法刻蚀

• 掺杂:

– 离子注入 – 扩散 退火

• 制膜:

– 氧化:干氧氧化、湿氧氧化等 – CVD:APCVD、LPCVD、PECVD – PVD:蒸发、溅射

• 正胶:分辨率高,在超大规模集成电路

工艺中,一般只采用正胶 • 负胶: 分辨率差,适于加工线宽≥3m 的线条

9

正胶:曝光 后可溶

负胶:曝光 后不可溶

10

光刻过程: 第一步:涂胶

第二步:预烘

11

第三步:曝光

第四步:显影

正性胶 负性胶

第五步:后烘

12

• 几种常见的光刻方法

– 接触式光刻:分辨率较高,但是容易造 成掩膜版和光刻胶膜的损伤。 – 接近式曝光:在硅片和掩膜版之间有一 个很小的间隙(10~25m),可以大大减 小掩膜版的损伤,分辨率较低 – 投影式曝光:利用透镜或反射镜将掩膜 版上的图形投影到衬底上的曝光方法, 目前用的最多的曝光方式

15

图形转换:刻蚀技术

• 湿法腐蚀:

– 湿法化学刻蚀在半导体工艺中有着广 泛应用:磨片、抛光、清洗、腐蚀 – 优点是选择性好、重复性好、生产效 率高、设备简单、成本低 – 缺点是钻蚀严重、对图形的控制性较 差