硅栅P阱CMOS反相器版图设计举例刻NMOS管S

CMOS工艺流程和MOS电路版图举例.ppt

1) 简化N阱CMOS 工艺演示

2

氧化层生长

氧化层 P-SUB

光刻1,刻N阱掩膜版

3

掩膜版

曝光

光刻胶 光刻1,刻N阱掩膜版

4

氧化层的刻蚀

光刻1,刻N阱掩膜版

5

N阱注入

光刻1,刻N阱掩膜版

6

形成N阱

N阱 P-SUB

7

氮化硅的刻蚀

二氧化硅

掩膜版

N阱

光刻2,刻有源区掩膜版

场氧的生长

二氧化硅

甘油

甘油

55

然后在表面氧化二氧化硅膜以减小后 一步氮化硅对晶圆的表面应力。

涂覆光阻(完整过程包括,甩胶→预 烘→曝光→显影→后烘→腐蚀→去除光 刻胶)。其中二氧化硅以氧化形成,氮化 硅LPCVD沉积形成(以氨、硅烷、乙硅烷 反应生成)。

56

光刻技术去除不想要的部分,此步骤为定 出P型阱区域。 (所谓光刻胶就是对光或电子束 敏感且耐腐蚀能力强的材料,常用的光阻液有 S1813,AZ5214等)。光刻胶的去除可以用臭氧烧 除也可用专用剥离液。氮化硅用180℃的磷酸去 除或含CF4气体的等离子刻蚀(RIE)。

31

多晶硅淀积

栅氧化层

多晶硅 N阱

32

光刻4,刻NMOS管硅栅, 磷离子注入形成NMOS管

NMOS管硅栅

用光刻胶做掩蔽 N阱

33

光刻5,刻PMOS管硅栅, 硼离子注入及推进,形成PMOS管

用光刻胶做掩蔽

PMOS管硅栅

N阱

34

磷硅玻璃淀积

磷硅玻璃 N阱

35

光刻6,刻孔、磷硅玻璃淀积回流 (图中有误,没刻出孔)

阈值电压调整注入 光刻3,VTP调整注入 光刻4,VTN调整注入

CMOS工艺流程版图剖面

P阱

N阱

推阱

– 退火驱入,双阱深度约1.8μm – 去掉N阱区的氧化层

43

形成场隔离区

– 生长一层薄氧化层 – 淀积一层氮化硅

– 光刻2场隔离区,非隔离区被光刻胶保护起来

– 反应离子刻蚀氮化硅 – 场区硼离子注入以防止场开启 – 热生长厚的场氧化层 – 去掉氮化硅层

44

光刻胶

31P+

11B+

49

形成第一层金属

– 淀积金属钨(W),形成钨塞

50

形成第一层金属

– 淀积金属层,如Al-Si、Al-Si-Cu合金等 – 光刻9,第一层金属版,定义出连线图形 – 反应离子刻蚀金属层,形成互连图形

51

正硅酸乙脂(TEOS)分解 650~750℃

形成穿通接触孔

– 化学气相淀积PETEOS, 等离子增强正硅酸四乙酯热分解

57

在P阱区域植入硼(+3)离子,因硅为+4价, 所以形成空洞,呈正电荷状态。(离子植入时与 法线成7度角,以防止发生沟道效应,即离子 不与原子碰撞而直接打入)。每次离子植入后必 须进行退火处理,以恢复晶格的完整性。(但高 温也影响到已完成工序所形成的格局)。

58

LOCOS (local oxidation of silicon)选择性氧 化:湿法氧化二氧化硅层,因以氮化硅为掩模会 出现鸟嘴现象, 影响尺寸的控制。二氧化硅层在 向上生成的同时也向下移动,为膜厚的0.44倍, 所以在去除二氧化硅层后,出现表面台阶现象。 湿法氧化快于干法氧化,因OH基在硅中的扩散速 度高于O2。硅膜越厚所需时间越长。

甘油

甘油

55

然后在表面氧化二氧化硅膜以减小 后一步氮化硅对晶圆的表面应力。

推荐-CMOS工艺流程版图剖面 精品

甘油

55

然后在表面氧化二氧化硅膜以减小 后一步氮化硅对晶圆的表面应力。

涂覆光阻(完整过程包括,甩胶→预 烘→曝光→显影→后烘→腐蚀→去除光 刻胶)。其中二氧化硅以氧化形成,氮化 硅LPCVD沉积形成(以氨、硅烷、乙硅烷 反应生成)。

56

光刻技术去除不想要的部分,此步骤为定 出P型阱区域。 (所谓光刻胶就是对光或电子束 敏感且耐腐蚀能力强的材料,常用的光阻液有 S1813,AZ5214等)。光刻胶的去除可以用臭氧 烧除也可用专用剥离液。氮化硅用180℃的磷酸 去除或含CF4气体的等离子刻蚀 (RIE)。

31

多晶硅淀积

栅氧化层

多晶硅 N阱

32

光刻4,刻NMOS管硅栅, 磷离子注入形成NMOS管

NMOS管硅栅

用光刻胶做掩蔽 N阱

33

光刻5,刻PMOS管硅栅, 硼离子注入及推进,形成PMOS管

用光刻胶做掩蔽

PMOS管硅栅

N阱

34

磷硅玻璃淀积

磷硅玻璃 N阱

35

光刻6,刻孔、磷硅玻璃淀积回流 (图中有误,没刻出孔)

CMOS工艺流程与MOS电路版图举例

1. CMOS工艺流程 1) 简化N阱CMOS工艺演示flash 2) 清华工艺录像:N阱硅栅CMOS工艺流程 3) 双阱CMOS集成电路的工艺设计 4) 图解双阱硅栅CMOS制作流程 2. 典型N阱CMOS工艺的剖面图 3. Simplified CMOS Process Flow 4. MOS电路版图举例

47

形成N管源漏区

– 光刻6,利用光刻胶将PMOS区保护起来 – 离子注入磷或砷,形成N管源漏区

形成P管源漏区

– 光刻7,利用光刻胶将NMOS区保护起来 – 离子注入硼,形成P管源漏区

CMOS工艺流程版图剖面

N-well, Active Region, Gate Oxide

Metal

Polysilicon

Metal

n-well

Top View VSS S

n+

ቤተ መጻሕፍቲ ባይዱ

Metal

p+

nMOSFET GD

pMOSFET DG

VDD S

Cross Section

78

Poly-silicon Layer

Top View

59

去除氮化硅和表面二氧化硅层。露出N型 阱区 域。(上述中曝光技术光罩与基片的距离 分为接触式、接近式和投影式曝光三种,常用 投影式又分为等比和微缩式。曝光会有清晰度 和分辩率,所以考虑到所用光线及波长、基片 表面平坦度、套刻精度、膨胀系数等)。

60

离子植入磷离子(+5),所以出现多 余电子,呈现负电荷状态。电荷移动速 度高于P型约0.25倍。以缓冲氢氟酸液去 除二氧化硅层。

14

P+离子注入

P+

掩膜版

光刻4,刻P+离子注入掩膜版

N阱

15

N+离子注入

N+ 光刻5,刻N+离子注入掩膜版

N阱

16

生长磷硅玻璃PSG

PSG

N阱

17

光刻接触孔

光刻6,刻接触孔掩膜版

N+

P+

N阱

18

刻铝

光刻7,刻Al掩膜版 Al

N阱

19

刻铝

VSS

Vo

VDD

N阱

20

钝化层 N阱

光刻8,刻压焊孔掩膜版

CMOS工艺流程与MOS电路版图举例

CMOS工艺流程版图剖面

71

2. 典型P阱CMOS工艺的剖面图

硅栅

薄氧化层

漏

金属

源

低氧

场氧化层 (FOX)

n-衬底

p-阱

72

CMOS process

p+

p+

p-

73

Process (Inverter)p-sub

In

GND

VDD

SGD

DGS

图例

低氧

场氧

Legend of each layer

N-well

p+

P-diffusion

52

合金 形成钝化层

– 在低温条件下(小于300℃)淀积氮化硅 – 光刻11,钝化版 – 刻蚀氮化硅,形成钝化图形

测试、封装,完成集成电路的制造工艺

CMOS集成电路采用(100)晶向的硅材料

53

4) 图解双阱硅栅 CMOS制作流程

54

首先进行表面清洗,去除wafer 表面的保护层和 杂质,三氧化二铝 必须以高速粒子撞击,并 用化学溶 液进行清洗。

64

以类似的方法,形成PMOS,植入硼 (+3)离子。 (后序中的PSG或BPSG能很好 的稳定能动钠离子,以保证MOS电压稳定)。

65

后序中的二氧化硅层皆是化学反应沉 积而成,其中加入PH3形成PSG (phosphosilicate-glass),加入B2H6形成BPSG (borophospho-silicate-glass)以平坦表面。所谓 PECVD (plasma enhanced CVD) 在普通 CVD反应空间导入电浆(等离子),使气体活 化以降低反应温度)。

形成N阱

– 初始氧化,形成缓冲层,淀积氮化硅层

最新CMOS工艺流程.版图.剖面

– 低温退火,形成C-47相的TiSi2或CoSi – 去掉氧化层上的没有发生化学反应的Ti或Co

– 高温退火,形成低阻稳定的TiSi2或CoSi2

•最新CMOS工艺流程.版图.剖面

•46

形成N管源漏区

– 光刻6,利用光刻胶将PMOS区保护起来

– 离子注入磷或砷,形成N管源漏区

形成P管源漏区

– 光刻7,利用光刻胶将NMOS区保护起来

– 离子注入硼,形成P管源漏区

•最新CMOS工艺流程.版图.剖面

•47

形成接触孔

– 化学气相淀积BPTEOS硼磷硅玻璃层 – 退火和致密 – 光刻8,接触孔版 – 反应离子刻蚀磷硅玻璃,形成接触孔

•最新CMOS工艺流程.版图.剖面

•48

形成第一层金属

– 淀积金属钨(W),形成钨塞

•最新CMOS工艺流程.版图.剖面

•最新CMOS工艺流程.版图.剖面

•39

3) 双阱CMOS集成电路的工艺设计

磷31P+

–砷75As+

P sub. 〈100〉

形成N阱

– 初始氧化,形成缓冲层,淀积氮化硅层

– 光刻1,定义出N阱

– 反应离子刻蚀氮化硅层

– N阱离子注入,先注磷31P+ ,后注砷75As+

•最新CMOS工艺流程.版图.剖面

场氧2

N阱

•最新CMOS工艺流程.版图.剖面

•29

栅氧化,开启电压调整

栅氧化层 N阱

•最新CMOS工艺流程.版图.剖面

•30

多晶硅淀积

栅氧化层

多晶硅 N阱

•最新CMOS工艺流程.版图.剖面

•31

光刻4,刻NMOS管硅栅, 磷离子注入形成NMOS管

CMOS工艺流程版图剖面

Top View

Cross-Section

79

N+ and P+ Regions

Top View

Cross-Section

Ohmic contacts

80

SiO2 Upon Device & Contact Etching

Top View

Cross-Section

81

Metal Layer – by Metal Evaporation

N-well

Legend of each layer

P-diffusion N-diffusion

Polysilicon

Metal

contact

75

Process

field oxide

field oxide

field oxide

76

3. Simplified CMOS Process Flow

Create n-well and active regions

P+

掩膜版

光刻4,刻P+离子注入掩膜版

N阱

15

N+离子注入

N+

光刻5,刻N+离子注入掩膜版

N阱

16

生长磷硅玻璃PSG

PSG

N阱

17

光刻接触孔

光刻6,刻接触孔掩膜版

N+

P+

N阱

18

刻铝

光刻7,刻Al掩膜版

Al

N阱

19

刻铝

VSS

Vo

VDD

N阱

20

钝化层

光刻8,刻压焊孔掩膜版

N阱

21

2) 清华工艺录像

CMOS工艺流程.版图.剖面

Top View

Cross-Section

79

N+ and P+ Regions

Top View

Cross-Section

Ohmic contacts

80

SiO2 Upon Device & Contact Etching

Top View

Cross-Section

81

Metal Layer – by Metal Evaporation

64

以类似的方法,形成PMOS,植入硼 (+3)离子。 (后序中的PSG或BPSG能很好 的稳定能动钠离子,以保证MOS电压稳定)。

65

后序中的二氧化硅层皆是化学反应沉 积而成,其中加入PH3形成PSG (phosphosilicate-glass),加入B2H6形成BPSG (borophospho-silicate-glass)以平坦表面。所谓 PECVD (plasma enhanced CVD) 在普通 CVD反应空间导入电浆(等离子),使气体活 化以降低反应温度)。

59

去除氮化硅和表面二氧化硅层。露出N型 阱区 域。(上述中曝光技术光罩与基片的距离 分为接触式、接近式和投影式曝光三种,常用 投影式又分为等比和微缩式。曝光会有清晰度 和分辩率,所以考虑到所用光线及波长、基片 表面平坦度、套刻精度、膨胀系数等)。

60

离子植入磷离子(+5),所以出现多 余电子,呈现负电荷状态。电荷移动速 度高于P型约0.25倍。以缓冲氢氟酸液去 除二氧化硅层。

多晶硅 栅氧化层 N阱

32

光刻4,刻NMOS管硅栅, 磷离子注入形成NMOS管

NMOS管硅栅

用光刻胶做掩蔽

N阱

p阱CMOS芯片制作工艺设计(掺杂工艺参数计算)

p阱CMOS芯片制作工艺设计目录一.设计参数要求 (2)二.设计内容 (3)1:PMOS管的器件特性参数设计计算。

(3)2:NMOS管参数设计与计算。

(4)3: p阱CMOS芯片制作的工艺实施方案; (5)工艺流程 (5)4.光刻工艺及流程图(典型接触式曝光工艺流程为例) (10)5:掺杂工艺参数计算; (12)P阱参杂工艺计算 (12)②PMOS参杂工艺计算 (13)③NMOS参杂工艺计算 (13)三:工艺实施方案 (14)四、参考资料 (18)五:心得体会 (19)一.设计参数要求1. 特性指标要求:n沟多晶硅栅MOSFET:阈值电压VTn =0.5V, 漏极饱和电流IDsat≥1mA, 漏源饱和电压VDsat ≤3V,漏源击穿电压BVDS=35V, 栅源击穿电压BVGS ≥25V, 跨导gm≥2mS, 截止频率fmax≥3GHz(迁移率µn=600cm2/V·s)p沟多晶硅栅MOSFET:阈值电压VTp = -1V, 漏极饱和电流IDsat≥1mA, 漏源饱和电压VDsat ≤3V,漏源击穿电压BVDS=35V, 栅源击穿电压BVGS =≥25V, 跨导gm≥0.5mS, 截止频率fmax≥1GHz(迁移率µp=220cm2/V·s)2. 结构参数参考值:N型硅衬底的电阻率为20Ω⋅cm;垫氧化层厚度约为600 Å;氮化硅膜厚约为1000 Å;P阱掺杂后的方块电阻为3300Ω/ ,结深为5~6μm;NMOS管的源、漏区磷掺杂后的方块电阻为25Ω/ ,结深为0.3~0.5μm;PMOS管的源、漏区硼掺杂后的方块电阻为25Ω/ ,结深为0.3~0.5μm;场氧化层厚度为1μm;栅氧化层厚度为500 Å;多晶硅栅厚度为4000 ~5000 Å。

二. 设计内容1:PMOS 管的器件特性参数设计计算.由ox B GS t E BV =得417106256=⨯≥=cmV B GS ox E BV t Å ,ox ox ox t C ε=则28103.8cm F C ox -⨯≤ GHz LV V f T GS n 12)(2max≥-=πμ得m L μ23.3≤再由mA V V LC W I T GS OXp DSAT ≥-=2)(2μ,式中(V GS -V T )≥V DS (sat),得2.12≥LW又ms V V L C W V I g T GS OX n GS D m 5.0)(≥-=∂∂=μ,得1.9≥LW2.12≥∴LW阈值电压ms fn oxoxSS SD TP t Q Q V φφε+---=2)||((max)T A SD xd eN Q =(max) 21)4(Afn s T eN xd φε=)ln(iD fn n Ne KT =φ 取D N 发现当316105-⨯=cm N D 时V V TP 05.1-=符合要求,又22L qN BV sD DS ε=得m L μ7.0≥V ms 1.1=φ2:NMOS 管参数设计与计算。

CMOS工艺流程与MOS电路版图举例

•掩膜版

Байду номын сангаас曝光

•光刻胶 •光刻1,刻N阱掩膜版

PPT文档演模板

CMOS工艺流程与MOS电路版图举 例

氧化层的刻蚀

•光刻1,刻N阱掩膜版

PPT文档演模板

CMOS工艺流程与MOS电路版图举 例

N阱注入

•光刻1,刻N阱掩膜版

PPT文档演模板

CMOS工艺流程与MOS电路版图举 例

形成N阱

•P-SUB

•N阱

•Si3N4

•N阱

•P-Si SUB

•缓冲用SiO2

PPT文档演模板

CMOS工艺流程与MOS电路版图举 例

光刻2,刻有源区,场区硼离子注入

•有源区

•有源区 •N阱

PPT文档演模板

CMOS工艺流程与MOS电路版图举 例

场氧1

PPT文档演模板

•N阱

CMOS工艺流程与MOS电路版图举 例

光刻3

PPT文档演模板

•N阱

CMOS工艺流程与MOS电路版图举 例

PPT文档演模板

场氧2

•N阱

CMOS工艺流程与MOS电路版图举 例

栅氧化,开启电压调整

PPT文档演模板

•栅氧化层 •N阱

CMOS工艺流程与MOS电路版图举 例

多晶硅淀积

•栅氧化层

•多晶硅 •N阱

PPT文档演模板

CMOS工艺流程与MOS电路版图举 例

光刻4,刻NMOS管硅栅, 磷离子注入形成NMOS管

N+离子注入

•N+ •光刻5,刻N+离子注入掩膜版

•N阱

PPT文档演模板

CMOS工艺流程与MOS电路版图举 例

生长磷硅玻璃PSG

CMOS工艺流程与MOS电路版图举例

编辑课件ppt

3

• 7、光Ⅳ---p管场区光刻(用光I的负版), p管场区注入, 调节PMOS管的开启电压, 然后生长多晶硅。

B+

PN-Si

编辑课件ppt

4

• 8、光Ⅴ---多晶硅光刻,形成多晶硅栅及 多晶硅电阻

多晶 硅 P-

N-Si

编辑课件ppt

5

• 9、光ⅤI---P+区光刻,刻去P管上的胶。 P+区注入,形成PMOS管的源、漏区及 P+保护环(图中没画出P+保护环)。

编辑课件ppt

14

2、单元配置恰当

(1)芯片面积降低10%,管芯成品率/圆 片 可提高1520%。

(2)多用并联形式,如或非门,少用串 联形式,如与非门。

(3)大跨导管采用梳状或马蹄形,小跨 导管采用条状图形,使图形排列尽可能规 整。

编辑课件ppt

15

3、布线合理

•布线面积往往为其电路元器件总面积的几倍,在多层 布线中尤为突出。

• 尽量使VDD、VSS接触孔的长边相互平行。

• 接VDD的孔尽可能离阱近一些。

• 接VSS的孔尽可能安排在阱的所有边上(P阱)。

编辑课件ppt

17

(2)尽量不要使多晶硅位于p+区域上 多晶硅大多用n+掺杂,以获得较低的电阻率 。若多晶硅位于p+区域,在进行p+掺杂时多晶 硅已存在,同时对其也进行了掺杂——导致杂 质补偿,使多晶硅。 (3)金属间距应留得较大一些(3或4)

因为,金属对光得反射能力强,使得光刻

时难以精确分辨金属边缘。应适当留以裕量。

编辑课件ppt

18

5、双层金属布线时的优化方案

(1)全局电源线、地线和时钟线用第二 层金属线。

CMOS工艺流程

Top View or Layout VDD

GND

Cross-Section View

75

Process

field oxide

field oxide

field oxide

76

3. Simplified CMOS Process Flow

Create n-well and active regions Grow gate oxide (thin oxide)

21

2) 清华工艺录像

N阱硅栅CMOS 工艺流程

22

初始氧化

23

光刻1,刻N阱

24

N阱形成

N阱

25

Si3N4淀积

Si3N4

N阱

P-Si SUB

缓冲用SiO2

26

光刻2,刻有源区,场区硼离子注入

有源区

有源区 N阱

27

场氧1

N阱

28

光刻3

N阱

29

场氧2

N阱

30

栅氧化,开启电压调整

栅氧化层 N阱

70

71

2. 典型P阱CMOS工艺的剖面图

硅栅

薄氧化层

漏

金属

源

低氧

场氧化层 (FOX)

n-衬底

p-阱

72

CMOS process

p+

p+

p-

73

Process (Inverter)p-sub

In

GND

VDD

SGD

DGS

图例

低氧

场氧

Legend of each layer

N-well

p+

CMOS反相器版图流程

m1

12

须解释的问题:

1. 有源区和场区是互补的,晶体管做在有源 区处,金属和多晶连线多做在场区上。 2. 有源区和P+,N+注入区的关系:有源区即 无场氧化层,在这区域中可做N型和P型各种 晶体管,此区一次形成。 3. 至于以后何处是NMOS晶体管,何处是 PMOS晶体管,要由P+注入区和N+注入区那 次光刻决定。

3

CMOS反相器版图流程(2)

P diffusion

2. 有源区——做晶体管的区域(G、D、S、B区), 封闭图形处是氮化硅掩蔽层,该处不会长场氧化层

4

CMOS反相器版图流程(3)

Poly gate

3. 多晶硅——做硅栅和多晶硅连线。 封闭图形处,保留多晶硅

5

CMOS反相器版图流程(4)

N+ implant

13

9

CMOS反相器版图流程(7)

via

7. 通孔——两层金属连线之间连接的端子

10

CMOS反相器版图流程(8)

Metal 2

8. 金属线2——做金属连线,封闭图形处保留铝

11

inverter: Schematic: Layout:

input

VDD m1 m2 GND VDD

output

GND

m2

有源区和pn注入区的关系有源区即无场氧化层在这区域中可做n型和p型各种晶体管此区一次形成

CMOS反相器 版图流程

1

CMOS反相器版图流程(1)

N well

P well

1. 阱——做N阱和P阱封闭图形, 窗口注入形成P管和N管的衬底

2

CMOS反相器版图流程(2)

N diffusion

CMOS工艺流程图剖面

甘油

55

然后在表面氧化二氧化硅膜以减小 后一步氮化硅对晶圆的表面应力。

涂覆光阻(完整过程包括,甩胶→预 烘→曝光→显影→后烘→腐蚀→去除光 刻胶)。其中二氧化硅以氧化形成,氮化 硅LPCVD沉积形成(以氨、硅烷、乙硅烷 反应生成)。

56

光刻技术去除不想要的部分,此步骤为定 出P型阱区域。 (所谓光刻胶就是对光或电子束 敏感且耐腐蚀能力强的材料,常用的光阻液有 S1813,AZ5214等)。光刻胶的去除可以用臭氧 烧除也可用专用剥离液。氮化硅用180℃的磷酸 去除或含CF4气体的等离子刻蚀 (RIE)。

N-diffusion Polysilicon

p-sub

Metal

contact

74

Layout and Cross-Section View of Inverter

Inverter

VDD

In

In

Out

Out

GND 图例

Legend of each layer

N-well P-diffusion N-diffusion Polysilicon

14

P+离子注入

P+

掩膜版

光刻4,刻P+离子注入掩膜版

N阱

15

N+离子注入

N+ 光刻5,刻N+离子注入掩膜版

N阱

16

生长磷硅玻璃PSG

PSG

N阱

17

光刻接触孔

光刻6,刻接触孔掩膜版

N+

P+

N阱

18

刻铝

光刻7,刻Al掩膜版 Al

N阱

19

刻铝

VSS

Vo

VDD

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

n+区/保护带

P+区保护环

版图分解: 1. 刻P阱 2. 刻P+区/保护环 3. 刻n+区/保护带 4. 刻栅、预刻接触孔 5. 刻接触孔 6. 刻Al 7. 刻纯化孔

图2 铝栅CMOS反相器版图示意图

版图分解: 1. 刻P阱 2. 刻P+区/环 3. 刻n+区 4. 刻栅、预刻接触孔 5. 刻接触孔 6. 刻Al 7. 刻纯化孔

3

版图分解: 1. 刻P阱 2. 刻P+区/环 3. 刻n+区 4. 刻栅、预刻接触孔 5. 刻接触孔 6. 刻Al 7. 刻纯化孔

4

4) 硅栅MOS版图举例 E/E NMOS反相器 刻有源区 刻多晶硅栅 刻NMOS管S、D 刻接触孔 反刻Al

图5 E/E NMOS反相器版图示意图

5. 刻NMOS管 S、 D T1 W/L=1/1

Poly Diff Al con

Vdd

P阱

Vi

Vo

6. 刻接触孔 7. 反刻Al (W/L)p=3(W/L)n

Vss

1. 刻P阱

2. 刻有源区

3. 刻多晶硅栅

4. 刻PMOS管S、D

5. 刻NMOS管S、D

6. 刻接触孔

VDD

7. 反刻Al

VDD

E/D NMOS 反相器

刻有源区 刻耗尽注入区 刻多晶硅栅 刻NMOS管S、D 刻接触孔 反刻Al

图6 E/D NMOS 反相器版图

制备耗尽型MOS管

在MOS集成电路中,有些设计需要 采用耗尽型MOS管,这样在MOS工艺过 程中必须加一块光刻掩膜版,其目的是 使非耗尽型MOS管部分的光刻胶不易被 刻蚀,然后通过离子注入和退火、再分 布工艺,改变耗尽型MOS管区有源区的 表面浓度,使MOS管不需要栅电压就可 以开启工作。 然后采用干氧-湿氧-干氧的方法 进行场氧制备,其目的是使除有源区部 分之外的硅表面生长一层较厚的SiO2层, 防止寄生MOS管的形成。

铝栅MOS器件

硅栅MOS器件

铝栅MOS工艺掩膜版的说明

• Source/Drain: Photomask (dark field)

Chromium

Cross Section

Clear Glass

• Gate: Photomask (dark field)

Chromium

Cross Section

硅栅CMOS与非门版图举例

刻P 阱 刻p + 环 刻n + 环 刻有源区 刻多晶硅栅 刻PMOS管S、D 刻NMOS管S、D 刻接触孔 反刻Al

图7 硅栅CMOS与非门版图

8

硅栅P阱CMOS反相器版图设计举例

1. 刻P阱 2. 刻有源区 3. 刻多晶硅栅 T2 W/L=3/1 4. Vi 刻PMOS管S、 Vo D

VDD

P阱

T2 W/L=3/1

Vi

Vo

T1 W/L=1/1

Vi

Vo

Vss

5) P阱硅栅单层铝布线CMOS 的工艺过程

下面以光刻掩膜版为基准,先描述 一个P阱硅栅单层铝布线CMOS集成电 路的工艺过程的主要步骤,用以说明如 何在CMOS工艺线上制造CMOS集成电 路。(见教材第7--9页,图1.12)

Al

p+

n+

1

该图的说明 a 沟道长度 3λ b GS/GD覆盖λ c p+,n+最小宽度3λ d p+,n+最小间距3λ e p阱与n+区间距2λ f 孔距扩散区最小间距 2λ g Al覆盖孔λ 孔 2λ× 3λ或 3λ× 3λ h Al栅跨越p+环λ i Al最小宽度4λ j Al最小间距3λ

2) 铝栅、硅栅MOS器件的版图

Clear Glass

• Contacts: Photomask (dark field)

Chromium

Cross Section

Clear Glass

• Metal Interconnects: Photomask (light field)

Clear Glass

Cross Section

Chromium

Vi

Vo

Vi

Vo

Vss Vss

光刻1与光刻2套刻

光刻2与光刻3套刻

光刻3与光刻4套刻

光刻4与光刻5套刻

S

ห้องสมุดไป่ตู้

刻NMOS管S、D

光刻胶保护

D 刻PMOS管S、D D

光刻胶保护

S

光刻5与光刻6套刻

VDD

光刻6与光刻7套刻

VDD VDD DD V

Vi

Vo

Vi Vi Vi

Vo

Vo

Vss

Vss

Vss

Poly Diff Al con

硅栅硅栅MOS器件工艺的流程

Process (1)刻有源区

正胶

Process (2)刻多晶硅与自对准掺杂

Self-Align Doping

Process (3)刻接触孔、反刻铝

field oxide (FOX) metal-poly insulator thin oxide

3) 铝栅工艺CMOS反相器版图举例 图2为铝栅CMOS反相器版图示意图。可见, 为了防止寄生沟道以及p管、n管的相互影响, 采用了保护环或隔离环:对n沟器件用p+环包围 起来, p沟器件用n+环隔离开,p+、n+环都以反 偏形式接到地和电源上,消除两种沟道间漏电 的可能。

CMOS集成电路工艺 --以P阱硅栅CMOS为例

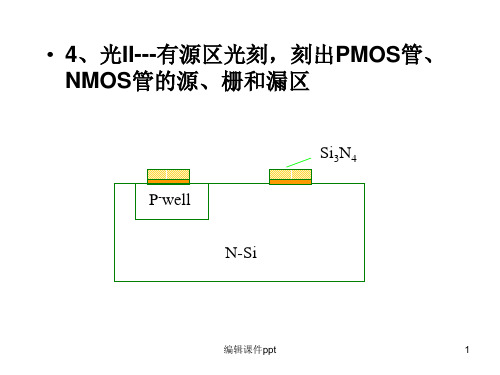

• 1、光刻I---阱区光刻,刻出阱区注入孔

SiO2

N-Si

• 2、阱区注入及推进,形成阱区

P-well

N-sub

• 3、去除SiO2,长薄氧,长Si3N4

Si3N4

薄氧

P-well N-sub