反相器的设计与仿真

cadence反相器

cadence反相器反相器版图设计与仿真⼀.实验⽬的1.熟悉Hspice的⽤法以及⽹表的规则写法1.熟悉cadence软件的使⽤以及如何利⽤cadence画版图2.熟悉对版图DRC验证和lvs检查⼆.实验器材已安装Hspice和VWware软件的电脑,和虚拟机要有cadence软件三.实验内容1)反相器的电路仿真2)Layout的认识3)反相器Layout设计4)DRC验证5)LVS验证四.实验步骤1.写好反相器的⽹表如下*lab1 inv.sp.include 'hua05.sp'.global vdd gndM1 OUT IN VDD VDD PMOS W=20u L=0.6uM2 OUT IN GND GND NMOS W=10u L=0.6uV1 VDD GND 5V2 IN GND PULSE(0 5 0ns 0.5ns 0.5ns 5ns 10ns).OPTIONS POST.tran 0.01ns 60ns.end2.在Hspice软件上仿真,看波形图是否符合3.画出反相器版图,再进⾏DRC验证,得到必须为没有错误如下:4.在linux系统⾥拷贝bd07.lvs和inv.gds和inv.sp到test-inv⽂件夹⾥,修改⽹表⽂件名为inv.sp,以及bd07.lvs和bd07.lpe的⽂件,并执⾏:CIW->File ->Export->Stream…⽣成inv.gds⽂件5.进⾏lvs检查,终端代码如下:%LOGLVS%htv%case%cir /home/icer/test-inv/inv.sp (⽹表的路径)%:con inv (⽹表中单元名)%:exit_____________________________%PDRACULA%:/g /home/icer/test-inv/bd07.lvs (LVS规则⽂件名)%:/f%.//doc/92d3bc4fa300a6c30d229f0a.html6.检查上述⽣成lvsout⽂件,看原理图与版图是否匹配7.进⾏lpe检查,⽣成PRENENT.DAT⽂件,终端代码如下:%PDRACULA%:/g /home/icer/test-inv/bd07.lpe (LVS规则⽂件名)%:/f%.//doc/92d3bc4fa300a6c30d229f0a.html8.在windows下将PRENET修改成SP⽂件,然后打开⽂件将PM和NM修改成NMOS 和PMOS,保存9.编写HFZ.sp⽂件如下:* Lab1 inv.sp********* SPICE Library **************.include 'hua05.sp'.include 'PRENET.sp'*****************************************.global vdd gndX1 IN OUT PRENETV1 VDD GND 5V2 IN GND PULSE(0 5 0ns 0.1ns 0.1ns 5ns 10ns).OPTIONS POST.tran 0.01ns 60ns.end10.将hua05.sp 和PRENET.sp,INV.sp 和HFZ.sp拷贝到同⼀个⽂件夹⾥11.⽤Hspice打开HFZ.sp⽂件,分析,看波形图如下:五.实验总结本次实验对我受益匪浅,通过本次反相器的实验,我更加熟悉了Hspice 软件和cadence软件,熟悉了利⽤这两个软件来制作⽹表,版图,以及DRC 验证,lvs检查,lpe检查。

反相器设计报告

反相器设计报告一、反相器编辑与仿真1打开S-Edit,对编辑环境进行设置,选取Setup→Colors命令,可设置背景色、前景色、选择颜色、栅格颜色与原点颜色。

在选取Setup→Grid进行格点设置。

2在Schematic Mode下选取Module→Symbol Browser命令,选取spice元件库中NMOS,PMOS,Vdd,Gnd四个模块到Schematic Mode中。

3编辑反相器,根据要求将各模块排列好并正确完成各端点连线后,加入输入输出节点并命名,再对元件参数进行设置。

原理图如下图(1)4选取Symbol Mode,建立反相器符号设置输入输出节点,处输入输出节点名称要和原理图相对应。

更改模块名称,选取Module→Rename命令命名为my_inv。

符号图下图(2)。

反相器原理图(1)反相器符号图(2)5将编辑好的反相器原理图输出成Spice文件,File→Export命令设置输出路径和输出sp格式文件,命名为my_inv,用Tspice打开my_inv.sp文件进行仿真设置,选择Edit→Insert Command命令,依次进行加载包含文件、Vdd电压值设定、IN的输入信号设定、分析设定、输出设定,本次设计的反相器的设定设定结果和仿真结果分别如下图(3)(4)。

设定结果图(3)仿真结果图(4)二、反相器布局图与仿真1.取代设定:打开L-Edit,选择File→Replace Setup命就可以将lights。

tdb文件的设定选择性的应用到目前编辑的文件中,包括格点设定、图层设定等。

2.环境设定:选择Set→Design命令,将Technology units设为Lambda单位,即设定一个Lambda为1000个Internal Unit,也设定1个Lambda等于1个Micron。

3.绘制pmos:在Layers面饭下拉列表中可选取要绘制的图层,依照PMOS图层依次画出N-WELL、Active、P Select、Poly、Active Contact、Mental1图层,每画一层图都应该进行DRC检查,如果有设计规则错误则进行修改,直至无设计规则错误,按上述步骤设计得PMOS参数为(宽W,高L)N-WELL(23,15)、Active(13,5)、P Select(17,9)、Poly (2,9)、Active Contact(2,2)、Mental1(4,4)。

反相器设计前仿与后仿流程

目录前端电路设计与仿真 (2)第一节双反相器的前端设计流程 (2)1、画双反相器的visio原理图 (2)2、编写.sp文件 (2)第二节后端电路设计 (4)一、开启linux系统 (4)2、然后桌面右键重新打开Terminal (6)双反相器的后端设计流程 (7)一、schematic电路图绘制 (7)二、版图设计 (21)画版图一些技巧: (30)三、后端验证和提取 (31)第三节后端仿真 (37)其它知识 (40)前端电路设计与仿真第一节双反相器的前端设计流程1、画双反相器的visio原理图inV DDM2M3out图1.1其中双反相器的输入为in 输出为out,fa为内部节点。

电源电压V DD=1.8V,MOS 管用的是TSMC的1.8V典型MOS管(在Hspice里面的名称为pch和nch,在Cadence里面的名称为pmos2v和nmos2v)。

2、编写.sp文件新建dualinv.txt文件然后将后缀名改为dualinv.sp文件具体实例.sp文件内容如下:.lib 'F:\Program Files\synopsys\rf018.l' TT 是TSMC用于仿真的模型文件位置和选择的具体工艺角*****这里选择TT工艺角***********划红线部分的数据请参考excel文件《尺寸对应6参数》,MOS管的W不同对应的6个尺寸是不同的,但是这六个尺寸不随着L的变化而变化。

划紫色线条处的端口名称和顺序一定要一致MOS场效应晶体管描述语句:(与后端提取pex输出的网表格式相同)MMX D G S B MNAME <L=val> <W= val > <AD= val > <AS= val > <PD= val > <PS= val > <NRD= val > <NRS= val >2.1、在wind owXP开始--程序这里打开Hspice程序2.2、弹出以下画面然后进行仿真1、打开.sp文件2、按下仿真按钮3形存放.sp文件的地址查看波形按钮按下后弹出以下对话框单击此处如果要查看内部节点的波形,双击Top 处单击这些节点即可查看波形请单击此处的Top 查看如果要查看测量语句的输出结果请查看 .MTO 文件(用记事本打开)至此前端仿真教程结束第二节后端电路设计前序(打开Cadence 软件)一、开启linux 系统双击桌面虚拟机的图标选择Power on this virtual machine 开启linux之后在桌面右键选择 Open Terminal输入 xhost local:命令按回车之后输入 su xue命令按回车,这样就进入了xue用户1、输入命令加载calibre软件的license,按回车,等到出现以下画面再关闭Terminal窗口2、然后桌面右键重新打开Terminal进入学用户,开启Cadence软件,如下图然后出现cadence软件的界面关闭这个help窗口,剩下下面这个窗口,这样cadence软件就开启了[如果在操作过程中关闭了cadence,只需要执行步骤2即可,步骤1加载calibre 的license只在linux重启或者刚开启的时候运行一次就可以了。

CMOS反相器设计与仿真报告

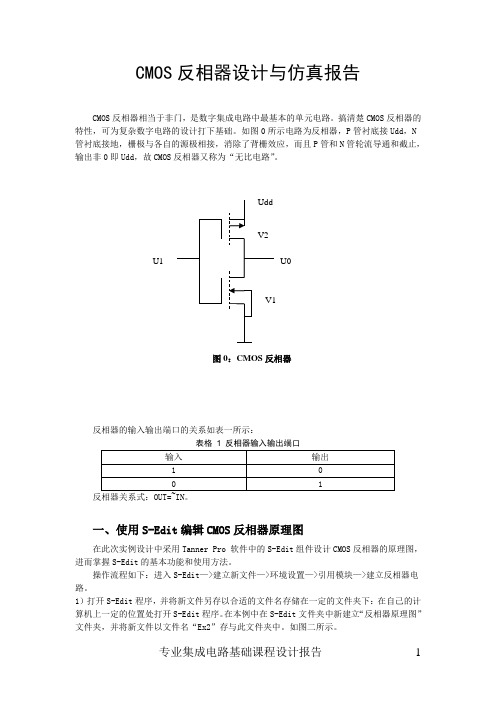

CMOS 反相器设计与仿真报告CMOS 反相器相当于非门,是数字集成电路中最基本的单元电路。

搞清楚CMOS 反相器的特性,可为复杂数字电路的设计打下基础。

如图0所示电路为反相器,P 管衬底接Udd ,N 管衬底接地,栅极与各自的源极相接,消除了背栅效应,而且P 管和N 管轮流导通和截止,输出非0即Udd ,故CMOS 反相器又称为“无比电路”。

反相器的输入输出端口的关系如表一所示:表格 1 反相器输入输出端口反相器关系式:OUT=~IN 。

一、使用S-Edit 编辑CMOS 反相器原理图在此次实例设计中采用Tanner Pro 软件中的S-Edit 组件设计CMOS 反相器的原理图,进而掌握S-Edit 的基本功能和使用方法。

操作流程如下:进入S-Edit —>建立新文件—>环境设置—>引用模块—>建立反相器电路。

1)打开S-Edit 程序,并将新文件另存以合适的文件名存储在一定的文件夹下:在自己的计算机上一定的位置处打开S-Edit 程序。

在本例中在S-Edit 文件夹中新建立“反相器原理图”文件夹,并将新文件以文件名“Ex2”存与此文件夹中。

如图二所示。

图0:CMOS 反相器图 a 另存新文件为Ex22)环境设置:S-Edit 默认的工作环境是黑底白线,但可以按照用户的喜好自行设定。

即选择Setup->Colors 命令,打开Colors 对话框,可分别设置背景色、前景色、选取颜色、栅格颜色、原点颜色和可更换颜色等。

如图二所示。

图二 环境设置3)编辑模块并浏览组件库:S-Edit 编辑方式是以模块为单位而不是以文件为单位,一个文件中可以包含多个模块,而每一个模块则表示一种基本组件或者一种电路。

每次打开一个新文件时便自动打开一个模块并命名为“Module0”;也可以重命名模块名。

方法是选择Module->Rename 命令,在弹出的对话框中的New Name 中输入符合实际电路的名称,如“inv_dc ” 即可,之后单击OK 按钮就可以。

MOS集成电路--CMOS反相器电路仿真及版图设计

MOS管集成电路设计题目:CMOS反相器电路仿真及版图设计**:***学号:***********专业:通信工程****:***2014年6月1日摘要本文介绍了集成电路设计的相关思路、电路的实现、SPICE电路模拟软件和LASI7集成电路版图设计的相关用法。

主要讲述CMOS反相器的设计目的、设计的思路、以及设计的过程,用SPICE电路设计软件来实现对反相器的设计和仿真。

集成电路反相器的实现用到NMOS和PMOS各一个,用LASI7实现了其版图的设计。

设计。

集成电路 CMOS反相器LT SPICE LASI7 关键字:集成电路目录引言 ....................................................................................................................................... - 2 -一、概述 ............................................................................................................................... - 2 -1.1MOS集成电路简介集成电路简介 .................................................................................................... - 2 -1.2MOS集成电路分类集成电路分类 .................................................................................................... - 2 -1.3MOS集成电路的优点集成电路的优点 ................................................................................................ - 3 -二、LTspice电路仿真 .......................................................................................................... - 3 -2.1SPICE简介 ................................................................................................................... - 3 -仿真过程 ..................................................................... - 3 -2.2CMOS反相器LT SPICE仿真过程2.2.1实现方案 .............................................................................................................. - 3 -2.2.2 LTspice电路仿真结果 ...................................................................................... - 5 -三、LASI版图设计 ............................................................................................................... - 5 -软件简介 ........................................................................................................ - 5 -3.1LASI软件简介版图设计原理 ......................................................................................................... - 6 -3.2版图设计原理的版图设计 .................................................................................................... - 6 -3.3LASI的版图设计四、实验结果分析 ............................................................................................................... - 8 -五、结束语 ........................................................................................................................... - 8 -参考文献 ............................................................................................................................... - 8 -引言CMOS 技术自身的巨大潜力是IC 高速持续发展的基础。

反相器设计

目录一、反相器的原理图设计二、创建符三、反相器电路前仿四、版图设计五、版图后仿六、总结一、反相器的原理图设计实验目的:1、了解Schemati c设计环境2、掌握反相器电路原理图输入方法实验内容:1、创建库和视图单元步骤:1)开启虚拟机,进入Red Hat Linux后,点击CIW窗口的file—new—library,由此可创建库,用来存放单元视图的文件夹,将库文件的路径设置在cadence目录下,Name栏输入库文件名inv,右侧Technology File栏中选择Don’t need a techfile,点击OK。

2)然后再点击file—new—cellview,创建一个单元视图,不同的单元视图存放不同的文件夹,Library Name 选取为inv,Cell Name为自己学号,点击OK,此时便会弹出Schematic Edit的空白窗口。

2、输入反相器原理图步骤:1)添加元件在Schematic Edit的窗口中,选择Add—Instance窗口,点击Browse按钮,弹出Library Browser窗口,在Library一栏中选择gpdk180,Cell一栏中选pmos。

Cellview一栏选择symbol,都选好后就可以点击close,将Library Browser窗口关闭,此时Add Instance窗口的Cell栏和View栏就会被填好。

nmos的添加方法同上。

2)添加Source和Ground方法同上,在Library一栏中选analoglib,Cell一栏选vcc,Cellview一栏选择symbol。

添加Ground方法同上。

3) 添加pin点击Add—pin会出现Add pin窗口,在Pin Name栏中输入管脚名称,设置Direction为input,同理再添加一个output管脚。

4) 连线点击Add—Wire (Narrow),在需要连线处点击即可。

3、检查并保存:点击Design—Check and Save。

CMOS反相器电路版图设计与仿真

CMO反相器电路版图设计与仿真姓名:邓翔学号:33导师:马奎本组成员:邓翔石贵超王大鹏CMO反相器电路版图设计与仿真摘要:本文是基于老师的指导下,对cade nee软件的熟悉与使用, 进行CMO反相器的电路设计和电路的仿真以及版图设计与版图验证仿真。

关键字:CMO反相器;版图设计。

Abstract:This article is based on the teacher's guida nee,familiar with cade nee software and use, for CMOS in verter circuit design and circuit simulation and Iandscape and the Iandscape design of the simulatio n.Key word : CMOS inverter;Landscape design.一引言20世纪70年代后期以来,一个以计算机辅助设计技术为代表的新的技术改革浪潮席卷了全世界,它不仅促进了计算机本身性能的进步和更新换代,而且几乎影响到全部技术领域,冲击着传统的工作模式。

以计算机辅助设计这种高技术为代表的先进技术已经、并将进一步给人类带来巨大的影响和利益。

计算机辅助设计技术的水平成了衡量一个国家产业技术水平的重要标志。

计算机辅助设计(Computer Aided Design,CAD是利用计算机强有力的计算功能和高效率的图形处理能力,辅助知识劳动者进行工程和产品的设计与分析,以达到理想的目的或取得创新成果的一种技术。

它是综合了计算机科学与工程设计方法的最新发展而形成的一门新兴学科。

计算机辅助设计技术的发展是与计算机软件、硬件技术的发展和完善,与工程设计方法的革新紧密相关的。

采用计算机辅助设计已是现代工程设计的迫切需要。

电子技术的发展使计算机辅助设计(CAD)技术成为电路设计不可或缺的有力工具。

CMOS反相器版图设计与仿真报告

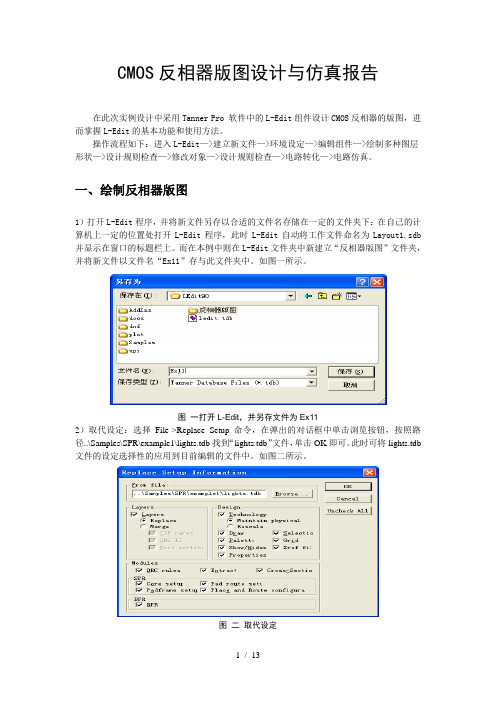

CMOS反相器版图设计与仿真报告在此次实例设计中采用Tanner Pro 软件中的L-Edit组件设计CMOS反相器的版图,进而掌握L-Edit的基本功能和使用方法。

操作流程如下:进入L-Edit—>建立新文件—>环境设定—>编辑组件—>绘制多种图层形状—>设计规则检查—>修改对象—>设计规则检查—>电路转化—>电路仿真。

一、绘制反相器版图1)打开L-Edit程序,并将新文件另存以合适的文件名存储在一定的文件夹下:在自己的计算机上一定的位置处打开L-Edit程序,此时L-Edit自动将工作文件命名为Layout1.sdb 并显示在窗口的标题栏上。

而在本例中则在L-Edit文件夹中新建立“反相器版图”文件夹,并将新文件以文件名“Ex11”存与此文件夹中。

如图一所示。

图一打开L-Edit,并另存文件为Ex112)取代设定:选择File->Replace Setup命令,在弹出的对话框中单击浏览按钮,按照路径..\Samples\SPR\example1\lights.tdb找到“lights.tdb”文件,单击OK即可。

此时可将lights.tdb 文件的设定选择性的应用到目前编辑的文件中。

如图二所示。

图二取代设定3)编辑组件:L-Edit编辑方式是以组件(Cell)为单位而不是以文件为单位,一个文件中可以包含多个组件,而每一个组件则表示一种说明或者一种电路版图。

每次打开一个新文件时便自动打开一个组件并命名为“Cell0”;也可以重命名组件名。

方法是选择Cell->Rename 命令,在弹出的对话框中的Rename cell as文本框中输入符合实际电路的名称,如本设计中采用组件名“inv”即可,之后单击OK按钮。

如图三所示。

图三重命名组件为inv4)设计环境设定:绘制布局图必须要有确实的大小,因此要绘图前先要确认或设定坐标与实际长度的关系。

反相器的版图设计实验报告

实验报告:反相器的版图设计与实现

1. 实验目的

1.1 熟悉软件的基本使用;

1.2 了解Schematic设计环境

1.3 掌握反相器电路的原理图输入方法、仿真及版图绘制方法;

2. 实验内容:

1)、反相器的电路及仿真:

○1电路图:

○2激励信号(以表格的形式给出)

Function DC

voltage/V Voltage1

/V

Voltage2

/V

Period

/S

Pulse

width/S

Vdd dc 1.8\\\\ gnd dc0\\\\·A pulse\ 1.80400n200n

○3电路图的仿真结果。

2)、二与非门的版图及仿真:○1版图(写出版图的面积)

版图面积大约为:10*5=50 um2

○2版图的后仿提取网表

○3激励信号(以表格的形式给出)

Function DC

voltage/V Voltage1

/V

Voltage2

/V

Period

/S

Pulse

width/S

Vdd dc 1.8\\\\ gnd dc0\\\\ A pulse\ 1.80400n200n

○4版图的仿真结果。

3、收获与感悟:

通过这次反相器的实验,我基本学会了layout的过程,已经能够完成电路图、版图的制作和电路的仿真、寄生参数提取、电路后仿真。

这次实验完成比较简单,在老师的带领下我们都能很好地完成老师要求的任务,第一次接触这个软件,还有很多不太懂的地方,希望在以后的实验中能够多多练习,熟练地掌握整个版图设计的过程。

.。

反相器的设计与仿真

0.18umCMOS反相器的设计与仿真2016311030103 吴昊一.实验目的在SMIC 0.18um CMOS mix-signal环境下设计一个反相器,使其tpHL=tpLH,并且tp越小越好。

利用这个反相器驱动2pf电容,观察tp。

以这个反相器为最小单元,驱动6pf电容,总延迟越小越好。

制作版图,后仿真,提取参数。

二.实验原理1.反相器特性1、输出高低电平为VDD和GND,电压摆幅等于电源电压;2、逻辑电平与器件尺寸无关;3、稳态是总存在输出到电源或者地通路;4、输入阻抗高;5、稳态时电源和地没通路;2.开关阈值电压Vm和噪声容限Vm的值取决于kp/kn所以P管和N管的宽长比值不同,Vm的值不同。

增加P管宽度使Vm移向Vdd,增加N管宽度使Vm移向GND。

当Vm=1/2Vdd时,得到最大噪声容限。

要使得噪声容限最大,PMOS部分的尺寸要比NMOS大,计算结果是3.5倍,实际设计中一般是2~2.5倍。

3.反向器传播延迟优化1、使电容最小(负载电容、自载电容、连线电容)漏端扩散区的面积应尽可能小输入电容要考虑:(1)Cgs 随栅压而变化(2)密勒效应(3)自举电路2、使晶体管的等效导通电阻(输出电阻)较小:加大晶体管的尺寸(驱动能力)但这同时加大自载电容和负载电容(下一级晶体管的输入电容)3、提高电源电压提高电源电压可以降低延时,即可用功耗换取性能。

但超过一定程度后改善有限。

电压过高会引起可靠性问题.当电源电压超过2Vt 以后作用不明显.4、对称性设计要求令Wp/Wn=μp/μu 可得到相等的上升延时和下降延时,即tpHL=tpLH。

仿真结果表明:当P,N管尺寸比为1.9时,延时最小,在2.4时为上升和下降延时相等。

4.反相器驱动能力考虑1.单个反相器驱动固定负载tp0为反相器的本征延迟,S是反向尺寸与参照反相器尺寸的比值。

tp0与门的尺寸大小无关而仅与工艺及版图有关。

无负载时,增加门的尺寸不能减少延迟。

反相器实验

深圳大学实验报告课程名称:数字集成电路设计

实验项目名称:反相器

学院:信息工程学院

专业:集成电路设计与集成系统

指导教师:

报告人:学号:

实验时间:2014.12.21

实验报告提交时间:2015.1.4

教务处制

一、实验目的

设计一个反相器,通过spectre 仿真,并绘制其版图,通过DRC 和LVS 验证。

二、实验内容

在完成spectre 仿真

完成版图设计

通过DRC 验证

通过LVS 验证

完成实验报告

三、实验步骤

1.绘制反相器原理图

2.反相器仿真

仿真结果截图如下

3.反相器版图设计

4.LVS验证

四、实验中遇到的问题

主要都是在元器件的边缘的放置的问题,因为层次太多,所以首次进行验证的时候报错

很多。

六、实验心得

这是第一次进行版图设计,所以很多地方会出现缺漏,所以基本花了一天的时间进行设计,尤其是很多细节的问题的影响更是大,对软件的不熟悉和对硬件排版的知识的缺乏使我重新设计了两三遍,获得最后的设计成功的时候真的是非常高兴的。

想要对这一门技术有所掌握,必须得投入大量的时间和精力。

指导教师批阅意见:

成绩评定:

指导教师签字:

年月日备注:

注:1、报告内的项目或内容设置,可根据实际情况加以调整和补充。

2、教师批改学生实验报告时间应在学生提交实验报告时间后10日内。

CMOS反相器电路设计

论文题目:CMOS反相器电路设计、仿真及版图设计学生姓名:欧阳倩学号:20131060189专业:通信工程任课教师:梁竹关摘要:本文着重介绍了LTspice和LASI软件的相关设计原理和简单的设计操作,对此,我首先将从电路的工作原理方面介绍CMOS4反相器的结构、特性及其电路工作原理。

了解其工作原理是进行仿真和版图设计的基础。

然后我选择利用LTspice来进行CMOS反相器的设计仿真以此来证实其设计正确性,之后采用LASI画出符合工业设计的CMOS反相器的版图。

通过本次设计实验可以更加了解CMOS4反相器的工作原理,并掌握了CMOS4反相器的基本设计方法。

关键词:CMOS反相器LTspice LASI版图设计封装测试目录第一章引言 (4)第二章CMOS反相器 (4)2.1 CMOS反相器的结构原理 (4)2.2 CMOS反相器的特性分析 (5)第三章CMOS反相器的电路仿真 (8)3.1CMOS反相器的电路图设计 (9)3.2 CMOS反相器的仿真及结果分析 (11)第四章CMOS反相器的版图设计 (12)结束语 (20)参考文献 (21)引言现在是一个电子信息高速发展得时代,电子产品无处不在,我们也越来越离不开各式各样的电子产品,集成电路作为电子产品的核心同样也受到了重视,电子设计也是当今社会的一大焦点问题,怎样才能设计出集性能、高效、便捷、低价为一体的电路器件又是当下人们急需解决的任务,因此培养集成设计人才也是众多高校重视的任务。

以MOS管作为开关元件的门电路称为MOS门电路。

由于MOS型集成门电路具有制造工艺简单、集成度高、功耗小以及抗干扰能力强等优点,因此它在数字集成电路产品中占据相当大的比例。

与TTL门电路相比,MOS门电路的速度较低。

MOS门电路有三种类型:使用P沟道管的PMOS电路、使用N沟道管的NMOS电路和同时使用PMOS和NMOS管的CMOS电路。

其中CMOS性能更优,因此CMOS门电路是应用较为普遍的逻辑电路之一。

CMOS反相器版图设计与仿真报告

CMOS反相器版图设计与仿真报告在此次实例设计中采用Tanner Pro 软件中的L-Edit组件设计CMOS反相器的版图,进而掌握L-Edit的基本功能和使用方法。

操作流程如下:进入L-Edit—>建立新文件—>环境设定—>编辑组件—>绘制多种图层形状—>设计规则检查—>修改对象—>设计规则检查—>电路转化—>电路仿真。

一、绘制反相器版图1)打开L-Edit程序,并将新文件另存以合适的文件名存储在一定的文件夹下:在自己的计算机上一定的位置处打开L-Edit程序,此时L-Edit自动将工作文件命名为Layout1.sdb并显示在窗口的标题栏上。

而在本例中则在L-Edit文件夹中新建立“反相器版图”文件夹,并将新文件以文件名“Ex11”存与此文件夹中。

如图一所示。

图一打开L-Edit,并另存文件为Ex112)取代设定:选择File->Replace Setup命令,在弹出的对话框中单击浏览按钮,按照路径..\Samples\SPR\example1\lights.tdb找到“lights.tdb”文件,单击OK即可。

此时可将lights.tdb文件的设定选择性的应用到目前编辑的文件中。

如图二所示。

图二取代设定3)编辑组件:L-Edit编辑方式是以组件(Cell)为单位而不是以文件为单位,一个文件中可以包含多个组件,而每一个组件则表示一种说明或者一种电路版图。

每次打开一个新文件时便自动打开一个组件并命名为“Cell0”;也可以重命名组件名。

方法是选择Cell->Rename 命令,在弹出的对话框中的Rename cell as文本框中输入符合实际电路的名称,如本设计中采用组件名“inv”即可,之后单击OK按钮。

如图三所示。

图三重命名组件为inv4)设计环境设定:绘制布局图必须要有确实的大小,因此要绘图前先要确认或设定坐标与实际长度的关系。

基于Tanner Pro软件的反相器设计与仿真

文档来源为:从网络收集整理.word版本可编辑.欢迎下载支持.集成电路课程设计报告基于Tanner Pro软件的反相器设计与仿真姓名:温炳林班级:09电科一班学号:指导老师:王建日期:华南农业大学工程学院摘要本文对Tanner Pro中的5种软件进行了简单的介绍,包括S-Edit, T-Spice, W-Edit, L-Edit与 LVS。

根据Tanner Pro软件的设计流程,本文着重描述利用Tanner Pro软件进行反相器电路图、版图设计和仿真的每个步骤,给出了电路图符号、电路图、版图以及仿真结果,LVS对比结果。

软件设计步骤主要包括了利用S-Edit进行反相器原理图、电路图符号的设计,T-Spice进行原理图仿真、sp网表文件的输出,L-Edit进行反相器版图的设计、版图转化文件的输出,T-Spice进行版图仿真。

最后利用LVS将电路图的输出文件与版图的转化的文件进行对比。

关键字:Tanner Pro 反相器 NMOS版图 PMOS版图目录1 关于Tanner Pro的设计与仿真 (1)1.1 Tanner Pro软件简介 (1)1.2 Tanner Pro软件的设计流程 (1)2 反相器电路图与版图的整体设计 (1)2.1 反相器电路图和符号的设计与仿真 (1)2.1.1 反相器电路图和符号的设计 (1)2.1.2 反相器原理图的仿真 (2)2.2 反相器的版图设计与仿真 (2)............................................. 错误!未定义书签。

2.2.2 反相器版图的仿真 (4)2.3 利用LVS对电路图和布局图结果对比 (5)3 结论 (5)4 体会心得 (5)1 关于Tanner Pro的设计与仿真1.1 Tanner Pro软件简介Tanner Pro 是一套集成电路设计软件,包括 S-Edit, T-Spice, W-Edit, L-Edit与 LVS。

反相器设计前仿与后仿流程

目录前端电路设计与仿真 (2)第一节双反相器的前端设计流程 (2)1、画双反相器的visio原理图 (2)2、编写.sp文件 (2)第二节后端电路设计 (4)一、开启linux系统 (5)2、然后桌面右键重新打开Terminal (8)双反相器的后端设计流程 (9)一、schematic电路图绘制 (9)二、版图设计 (32)画版图一些技巧: (48)三、后端验证和提取 (49)第三节后端仿真 (58)其它知识 (61)前端电路设计与仿真第一节双反相器的前端设计流程1、画双反相器的visio原理图inV DDM2M3out图1.1其中双反相器的输入为in 输出为out,fa为内部节点。

电源电压V DD=1.8V,MOS 管用的是TSMC的1.8V典型MOS管(在Hspice里面的名称为pch和nch,在Cadence里面的名称为pmos2v和nmos2v)。

2、编写.sp文件新建dualinv.txt文件然后将后缀名改为dualinv.sp文件具体实例.sp文件内容如下:.lib 'F:\Program Files\synopsys\rf018.l' TT 是TSMC用于仿真的模型文件位置和选择的具体工艺角*****这里选择TT工艺角***********划红线部分的数据请参考excel文件《尺寸对应6参数》,MOS管的W不同对应的6个尺寸是不同的,但是这六个尺寸不随着L的变化而变化。

划紫色线条处的端口名称和顺序一定要一致MOS场效应晶体管描述语句:(与后端提取pex输出的网表格式相同)MMX D G S B MNAME <L=val> <W= val > <AD= val > <AS= val > <PD= val > <PS= val > <NRD= val > <NRS= val >2.1、在wind owXP开始--程序这里打开Hspice程序2.2、弹出以下画面然后进行仿真1、打开.sp文件2、按下仿真按钮3形存放.sp文件的地址查看波形按钮按下后弹出以下对话框单击此处如果要查看内部节点的波形,双击Top处单击这些节点即可查看波形如果有多个子电路请单击此处的Top查看如果要查看测量语句的输出结果请查看.MTO文件(用记事本打开)至此前端仿真教程结束第二节后端电路设计前序(打开Cadence软件)一、开启linux系统双击桌面虚拟机的图标选择Power on this virtual machine 开启linux之后在桌面右键选择 Open Terminal 输入 xhost local:命令按回车之后输入 su xue命令按回车,这样就进入了xue用户1、输入命令加载calibre软件的license,按回车,等到出现以下画面再关闭Terminal窗口2、然后桌面右键重新打开Terminal 进入学用户,开启Cadence软件,如下图然后出现cadence软件的界面关闭这个help窗口,剩下下面这个窗口,这样cadence软件就开启了[如果在操作过程中关闭了cadence,只需要执行步骤2即可,步骤1加载calibre 的license只在linux重启或者刚开启的时候运行一次就可以了。

CMOS反相器电路版图设计与仿真

CMOS反相器电路版图设计与仿真姓名:邓翔学号:1007010033导师:马奎本组成员:邓翔石贵超王大鹏CMOS反相器电路版图设计与仿真摘要:本文是基于老师的指导下,对cadence软件的熟悉与使用,进行CMOS反相器的电路设计和电路的仿真以及版图设计与版图验证仿真。

关键字:CMOS反相器;版图设计。

Abstract:This article is based on the teacher's guidance, familiar with cadence software and use, for CMOS inverter circuit design and circuit simulation and landscape and the landscape design of the simulation.Key word:CMOS inverter;Landscape design.一引言20世纪70年代后期以来,一个以计算机辅助设计技术为代表的新的技术改革浪潮席卷了全世界,它不仅促进了计算机本身性能的进步和更新换代,而且几乎影响到全部技术领域,冲击着传统的工作模式。

以计算机辅助设计这种高技术为代表的先进技术已经、并将进一步给人类带来巨大的影响和利益。

计算机辅助设计技术的水平成了衡量一个国家产业技术水平的重要标志。

计算机辅助设计(Computer Aided Design,CAD)是利用计算机强有力的计算功能和高效率的图形处理能力,辅助知识劳动者进行工程和产品的设计与分析,以达到理想的目的或取得创新成果的一种技术。

它是综合了计算机科学与工程设计方法的最新发展而形成的一门新兴学科。

计算机辅助设计技术的发展是与计算机软件、硬件技术的发展和完善,与工程设计方法的革新紧密相关的。

采用计算机辅助设计已是现代工程设计的迫切需要。

电子技术的发展使计算机辅助设计(CAD)技术成为电路设计不可或缺的有力工具。

第一节基本逻辑门设计与仿真(反相器、与非门)

第⼀节基本逻辑门设计与仿真(反相器、与⾮门)⼀、1bits反相器1.电路符号2.真值表3.电路原理图4.verilog设计代码module inverter_gate(A,Y);input A;output Y;assign Y = ~ A;endmodule5.仿真代码//testbench of inverter_gate`timescale 1ns/10psmodule inverter_gate_testbench;reg aa;wire yy;//instantiation moduleinverter_gate U1(.A(aa),.Y(yy));initial begin#0 aa <= 0;#10 aa <= 1;#10 aa <= 0;#10 aa <= 1;#10 aa <= 0;#10 aa <= 1;#10 $stop;endendmodule6.仿真结果⼆、1bits与⾮门1.电路符号2.真值表3.电路原理图 两个NMOS串联和两个PMOS并联4.verilog设计代码module nand_gate(input A,B,output Y);assign Y = ~(A&B);endmodule5.仿真代码//Testbench of nand_gate`timescale 1ns/10psmodule nand_gate_testbench();reg aa,bb;wire yy;//instantiation the modulenand_gate U1(.A(aa),.B(bb),.Y(yy));// aa and bb signalinitial begin#0 aa <= 0; bb <= 0;#20 aa <= 0; bb <= 1;#10 aa <= 1; bb <= 0;#20 aa <= 1; bb <= 1;#20 $stop;endendmodule6.仿真结果三、其它知识点1.reg型变量必须使⽤⾮阻塞赋值,即使⽤ “<=”。

反相器设计实验

实验一反相器电路设计一、实验目的和内容掌握反相器电路的设计流程。

完成反相器电路的设计和仿真,完成版图的设计及其DRC、LVS和LPE,最后完成后仿真。

二、实验器材1.计算机2.Cadence版图设计工具Virtuoso软件3.Hspice模拟电路仿真软件三、实验说明1.熟悉版图设计工具Virtuoso软件的操作,使用Virtuoso绘制反相器版图(Layout),利用Diva的DRC文件做设计规则检查,利用LVS文件做电路和版图的一致性检查。

2.熟悉Hspice软件的操作,使用Hspice验证反相器的电路特性。

四、SPICE仿真过程如何利用HSPICE对反相器电路进行仿真?以下是参考步骤:(1)利用windows自带的记事本编辑仿真程序,并把文件命名为inverter.sp。

(2)在记事本内编辑inverter.sp文件,程序说明如下:*Lab1Inverter.sp*********SPICE Library**************.include'hua05.sp'***************************************.global VDD GNDM1OUT IN VDD VDD PMOS W=20u L=0.6uM2OUT IN GND GND NMOS W=10u L=0.6uV1VDD GND5V2IN GND PULSE(050ns0.5ns0.5ns5ns10ns).OPTIONS POST.tran0.01ns100ns.end利用HSPICE对网表进行仿真,结果如下图所示:五、反相器Layout设计1.反相器的设计的设计经过以下几步:画n-well→PMOS和NMOS的active区→形成poly-si和栅氧化层→形成NMOS的源漏的掺杂→形成PMOS的源漏的掺杂→形成contact孔以及欧姆接触的重掺杂→形成金属层→金属层标注。

至此就完成了反相器Layout的设计。

反相器设计前仿与后仿流程

目录前端电路设计与仿真 (2)第一节双反相器的前端设计流程 (2)1、画双反相器的visio原理图 (2)2、编写.sp文件 (2)第二节后端电路设计 (5)一、开启linux系统 (5)2、然后桌面右键重新打开Terminal (6)双反相器的后端设计流程 (8)一、schematic电路图绘制 (8)二、版图设计 (25)画版图一些技巧: (35)三、后端验证和提取 (37)第三节后端仿真 (44)其它知识 (48)前端电路设计与仿真第一节双反相器的前端设计流程1、画双反相器的visio原理图inV DDM2M3out图1.1其中双反相器的输入为in 输出为out,fa为内部节点。

电源电压VDD=1.8V,MOS管用的是TSMC的1.8V典型MOS管(在Hspice里面的名称为pch和nch,在Cadence里面的名称为pmos2v和nmos2v)。

2、编写.sp文件新建dualinv.txt文件然后将后缀名改为dualinv.sp文件具体实例.sp文件内容如下:.lib 'F:\Program Files\synopsys\rf018.l' TT 是TSMC用于仿真的模型文件位置和选择的具体工艺角*****这里选择TT工艺角***********划红线部分的数据请参考excel文件《尺寸对应6参数》,MOS管的W 不同对应的6个尺寸是不同的,但是这六个尺寸不随着L的变化而变化。

划紫色线条处的端口名称和顺序一定要一致MOS场效应晶体管描述语句:(与后端提取pex输出的网表格式相同) MMX D G S B MNAME <L=val> <W= val > <AD= val > <AS= val > <PD= val > <PS= val > <NRD= val > <NRS= val >2.1、在windowXP开始--程序这里打开Hspice程序2.2、弹出以下画面然后进行仿真1、打开.sp文件2、按下仿真按钮3形存放.sp文件的地址查看波形按钮按下后弹出以下对话框单击此处如果要查看内部节点的波形,双击Top处单击这些节点即可查看波形如果有多个子电路请单击此处的Top查看如果要查看测量语句的输出结果请查看 .MTO文件(用记事本打开)至此前端仿真教程结束第二节后端电路设计前序(打开Cadence软件)一、开启linux系统双击桌面虚拟机的图标选择Power on this virtual machine开启linux之后在桌面右键选择 Open Terminal输入 xhost local:命令按回车之后输入 su xue命令按回车,这样就进入了xue用户1、输入命令加载calibre软件的license,按回车,等到出现以下画面再关闭Terminal窗口2、然后桌面右键重新打开Terminal进入学用户,开启Cadence软件,如下图然后出现cadence软件的界面关闭这个help窗口,剩下下面这个窗口,这样cadence软件就开启了[如果在操作过程中关闭了cadence,只需要执行步骤2即可,步骤1加载calibre的license只在linux重启或者刚开启的时候运行一次就可以了。

实验一、反相器设计

实验一反相器设计一、实验目的1.学习tanner-pro中的s-edit,t-sipice和w-edit软件,完成inv的原理图设计与分析2.熟悉L-edit的使用,掌握L-edit进行集成电路版图设计的方法;3.掌握N/P MOS晶体管的工艺步骤、“N阱设计规则”。

4.掌握反相器的调试和性能指标测试方法5.掌握对反相器进行LVS的步骤与方法二、预习要求1、根据性能和指标要求,设计并计算电路的有关参数。

2、掌握s-edit编辑环境,设计inv的原理图3、掌握t-sipice和w-edit仿真环境,完成反相器的仿真4、掌握L-edit编辑环境,设计inv的版图5、掌握t-sipice和w-edit仿真环境,完成版图反相器的仿真6、掌握lvs环境变量7、写出预习报告三、反相器的设计方法1、确定电路(选择PMOS管、NMOS管)。

2、选择VDD和GND。

3、加入工作电源进行分析4、确定工艺规则。

5、绘制INV版图。

6、加入工作电源进行分析7、LVS比较四、实验内容1、设计一个具有反相器功能的电路。

反相器inv由一对互补的nmos和pmos管构成,通过对输入信号翻转完成输出信号,翻转时间长短有你nmos和pmos 工艺和尺寸决定,直接反映反相器的速度。

2、对所设计的电路进行设计、调试3、对电路的性能指标进行测试仿真,并改变设计参数(如沟道比等),对结果进行比较分析。

画出上述晶体管对应的版图,并且要求画出的版图在电学上,物理几何上,以及功能一致性上正确,版图的设计参考样式如下:4、版图规则/一致性检查对所设计的版图进行DRC、ERC规则检查对所设计的版图进行LVS一致性检查5、后仿真与改进对于设计的版图是否能够达到优异的性能,需要通过提取版图上的寄生参数,对含有版图寄生参数的电路进行仿真才能知道,很多时候版图上错误的走线,布图方法会导致致命的错误。

对于CMOS反相器版图设计,需要进行以下仿真:给反相器一个阶越信号的输入,观察反相器的输出信号的变化。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

0.18umCMOS反相器的设计与仿真

2016311030103 吴昊

一.实验目的

在SMIC 0.18um CMOS mix-signal环境下设计一个反相器,

使其tpHL二tpLH,并且tp越小越好。

利用这个反相器驱动2pf电容,

观察tp。

以这个反相器为最小单元,驱动6pf电容,总延迟越小越好。

制作版图,后仿真,提取参数。

二.实验原理

1•反相器特性

1、输出高低电平为VDD和GND电压摆幅等于电源电压;

2、逻辑电平与器件尺寸无关;

3、稳态是总存在输出到电源或者地通路;

4、输入阻抗高;

5、稳态时电源和地没通路;

2•开关阈值电压Vm和噪声容限

Vm的值取决于kp/kn

L " W

k = -

所以P管和N管的宽长比值不同,Vm的值不同。

增加P管宽度使Vm移向Vdd,增加N管宽度使Vm移向GNB 当Vm=1/2Vdd时, 得到最大噪声容限。

要使得噪声容限最大,PMOS部分的尺寸要比NMOS大,计算结果是3.5倍,实际设计中一般是2~2.5倍。

3•反向器传播延迟优化

1、使电容最小(负载电容、自载电容、连线电容)

漏端扩散区的面积应尽可能小

输入电容要考虑:(1)Cgs随栅压而变化

(2)密勒效应

(3)自举电路

2、使晶体管的等效导通电阻(输出电阻)较小:

加大晶体管的尺寸(驱动能力)

但这同时加大自载电容和负载电容(下一级晶体管的输入电容)

3、提咼电源电压

提高电源电压可以降低延时,即可用功耗换取性能。

但超过一定程度后改善有限。

电压过高会引起可靠性问题•当电源电压超过2Vt 以后作用不明显.

4、对称性设计要求

令Wp/Wn二卩p/卩u可得到相等的上升延时和下降延时,即tpHL 二tpLH。

仿真结果表明:当P, N管尺寸比为1.9时,延时最小,在2.4时为上升和下降延时相等。

4•反相器驱动能力考虑

1•单个反相器驱动固定负载

tp= 0.69切0 (1 + Ce.xt/S Ci re f)-

tp0为反相器的本征延迟,S是反向尺寸与参照反相器尺寸的比值。

tp0与门的尺寸大小无关而仅与工艺及版图有关。

无负载时,增加门的尺寸不能减少延迟。

有负载时,S很大时(大于等于10)使反相器延迟趋于本征延迟,因此继续加大尺寸不会有什么改善而只会显著增加面积。

、

2•反相器驱动大负载电容(反相器链)

给定负载CL,给定输入电容Cin时,可由公式

得到尺寸放大系数f和反相器级数N的关系。

又因为驱动大负载电容时最优f=3.6, tp最小。

所以即可以确定

一个正确的反相器级数N来最小化延迟。

三.实验内容

1•反相器设计

经过不断的调整与仿真,在保证VM=1/2 (VDD)=900mv同时尽量减小延时,最终确定Wp/Wn=47u/15u,管子较大为了确保反相器链的级

数不会过多

反相器电路图:反相器符号图: 反相器仿真图:

•<>UBJI Md匸曲'/\UJO O6~山八關申国:圧巨国甲

:<>oa

2T M

业山“」日jQ$IQ£ FE 血

由tran仿真结果可知,tpHL=0.09ns^tpLH

利用这个反相器驱动2pf电容,观察tran仿真结果:

由图可知tp为2ns,延迟较大,可见单个反相器的驱动能力有限

输入栅电容计算:

Pmos电容参数:

IS.7270856f

16,3051250s

-15.6S09D21f

-46.1998300a

-216 29G5349y

15 C9S6501f

-15.G9069O9f

1 11471030c

-is 72S3oegf

-19 69BG396f

55.O0293O9f

-19 e589SS2f

32.1589001f

S2.7S61092f

-1 7764000a

-66.8012646Z

-19P7033377f

19.7051809f

194.3B47329p

pmos 输入栅电容二Cgs+Cgd=19.659f+19.698ff Nmos电容参数:

dhb G329S»7f

dbd-g G97BM7f

cbg-LGE.7UE07G*

cbs37Z3SB54r

©db-2

cdd35597L2S8f

cdg-15

C da-IT1UDE€Q£

cgb QGEUaSu

cqd-IS5D0B567E

egg JI. 7911322(

-153073098f

叮日1-4534厂任f

门7IT

csb-2G735b40f

esd-1020541114f

c«g<5e i270SEf

20£M4804f

Nmos 输入栅电容二Cgs+Cgd=15.307f+15.500f Cgi n=19.659f+19.698f+5.307f+15.500f=70.164ff

DRG

Tope"

二 nV 、0 RMUff

■a

o f a

.n h e c sr 】

REEUr d o

■ c u

chsck^eTW_mclgB1GIWa

・ c m =5-岁 Dsmsulu

E 田 田

□

E 电 回\ a % s V a \ 田%田

\z €l -

X

^ewleuq 严::孟

二

左芝

—豐 W MWI4

NWI5

N R L 2亡 NRL3

z

H 'n MFII5

NRIB

Z H I 7

F V1匚

2.设计反相器链驱动6pf电容

参数计算:

反相器链级数N的计算:

由公共F二CL/Cgin,1=6pf/70.164ff=85.5

因为反相器链的最优尺寸放大比例f=3.6,又知道F=85.5所以可由f =N F得N=lnF/lnf=3.472,

即反相器链的级数N为4时,延迟最小。

延迟tp计算:

『叫。

(1+孙/了)tpO为反相器空载延迟=0.09ns

r为自载系数~ 1

所以计算可得tp=1.44ns

Tran仿真:

由图可知,tp~ 1.49ns,符合理论计算值的结果。

表明通过反相器链有效增强了其驱动能力。

皿亡h 叱歐 Mlkf Cell i 釘 1)R«£u1 I ^tilacltd

Ihile File FHthftBM /h >*«■ /usec 1 /lit/1drc >_S MC MBP _P^caljDlQ^hij (LcHj = afilij1B33 加E HUB.

Mtfi d^nalty af JHJfe! p-al;terTl-]勺 H *DRC:

Eile i ;»ew tlighfighl Joohi 韭indcw Setup

L / M “ 换奋克审 F 吹

TopWll mvjian i Pe suits (in 6 of 311 Cl>?qrs) ■»■ ChKK f ctlll

田I d Bkj&w —i&dgfl^ch&zfc d 田

# NW_1 a Z NW_2>

a m ✓ NW_Zh

0 ✓ NW_3

0 田 # NW_4 0

* NW_& 0 IS # NRJ

0 国 ✓ NR_2

0 B ✓ NRJ

a 厨 # NR_4

a E J * NIR.5 0 圍 # NR_B 0 ✓ NRJ 0 S3 # NIR.B a Ch^cifc Miw.^a. C#ll uni^liw 1 科片wk 1 SaiicWd H 口仃

■ g 0 1) Check i.*iM_9a a Ce^l ir<i-.3n 4-vtrte^ PHyg 帥

u. tubs ・ 'Ji.aia :E S»P -31 870

36 Ml. I DSS I c w ■ n«

LVS:

PEX

实验小结:

通过本次实验,使我对Candence工具使用更加熟练。

加强了我我对反相器的静态特性和动态特性的理解。

从一个设计者的角度,我学会了如何加强反相器稳定性,优化驱动能力,减小传播延迟,节省版图面积。