反相器设计

CMOS反相器的版图设计

实验一:CMOS反相器的版图设计一、实验目的1、创建CMOS反相器的电路原理图(Schematic)、电气符号(symbol)以及版图(layout);2、利用’gpdk090’工艺库实例化MOS管;3、运行设计规则验证(Design Rule Check,DRC)确保版图没有设计规则错误。

二、实验要求1、打印出完整的CMOS反相器的电路原理图以及版图;2、打印CMOS反相器的DRC报告。

三、实验工具Virtuoso四、实验内容1、创建CMOS反相器的电路原理图;2、创建CMOS反相器的电气符号;3、创建CMOS反相器的版图;4、对版图进行DRC验证。

1、创建CMOS反相器的电路原理图及电气符号图首先创建自己的工作目录并将/home/iccad/cds.lib复制到自己的工作目录下(我的工作目录为/home/iccad/iclab),在工作目录内打开终端并打开virtuoso(命令为icfb &).在打开的icfb –log中选择tools->Library Manager,再创建自己的库,在当前的对话框上选择File->New->Library,创建自己的库并为自己的库命名(我的命名为lab1),点击OK后在弹出的对话框中选择Attach to an exiting techfile并选择gpdk090_v4.6的库,此时Library manager的窗口应如图1所示:图1 创建好的自己的库以及inv创建好自己的库之后,就可以开始绘制电路原理图,在Library manager窗口中选中lab1,点击File->New->Cell view,将这个视图命名为inv(CMOS反相器)。

需要注意的是Library Name一定是自己的库,View Name是schematic,具体如图2所示:图2 inv电路原理图的创建窗口点击OK后弹出schematic editing的对话框,就可以开始绘制反相器的电路原理图(schematic view)。

CMOS反相器的分析与设计

CMOS反相器的分析与设计CMOS反相器由一对互补金属氧化物半导体场效应晶体管(n型MOSFET和p型MOSFET)组成。

n型MOSFET和p型MOSFET分别由n型沟道和p型沟道构成。

它们的沟道接在一起,形成一个共用的沟道。

根据输入电压的高低,CMOS反相器能够在输出端产生相反的电平。

CMOS反相器的工作原理是利用MOSFET的负阈值特性,即当输入电压高于一些阈值电压时,MOSFET处于关断状态;当输入电压低于阈值电压时,MOSFET处于导通状态。

CMOS反相器由这两个互补的MOSFET构成,保证了输入电压上升时一个MOSFET关闭,另一个MOSFET打开,输出电压下降;输入电压下降时,一个MOSFET打开,另一个MOSFET关闭,输出电压上升。

这样就实现了电平的反转。

1.确定输入输出电平:根据电路的需求,确定输入输出电平的高低电压范围,并根据具体电路的工作电压确定电源电压。

2.选择适当的MOSFET:根据设计要求,选择合适的n型MOSFET和p 型MOSFET,以满足工作电流和电压要求。

3.确定电阻参数:根据MOSFET的特性,选择合适的电阻参数来限制输入电流和确定电路的放大倍数。

4.确定电容参数:根据电路的带宽要求,确定输入和输出端的负载电容。

5.确定工作频率:根据电路的工作频率要求,确定MOSFET的开启和关闭时间。

6.进行电路仿真:通过电路仿真软件,验证设计的正确性和性能。

CMOS反相器的设计可以通过电路仿真软件如LTSpice来实现。

首先,根据设计要求选择适当的MOSFET,并确定电源电压和电阻电容参数。

然后,通过电路仿真软件搭建CMOS反相器电路,并进行仿真分析。

通过观察输入电压和输出电压的波形曲线,验证电路的正确性和性能。

如果需要进一步优化电路性能,可以通过调整各个元器件的参数来实现。

总结起来,CMOS反相器是一种常见的数字逻辑门电路,利用MOSFET的特性来实现输入输出电平的反转。

CMOS反相器的版图设计基础教学课件

确保布局合理,能够正常执行电路功能,能够方便后面的布线操作,使电路 布线最简化。

布线 根据电路的连接关系(连接表)在指定区域(面积、形状、层次)百分

之百完成连线。布线主要要考虑布线是否均匀,连线长度是否合理,能否布 通以及能否减少寄生效应等因素。

P+有源区注入 P-Select

N阱 N-Well

多晶 poly

有源区 Active 接触孔 contact

绘制版图

MOS管之间的连接

S

G

B

D

IN

OUT

D

G

B

S

B

VDD

D

G

S

IN

OUT

S

G

D

B

GND

版图修改

为了保证版图尺寸,必须要对版图进行修改(edit),主要操作有: 取消上步操作 (undo)、重复操作 (redo) 移动 (move)、复制 (copy) 拉伸 (stretch)、 删除 (delete)、旋转 (rotate)。

栅氧层 多晶层 介质层 金属层

器件物理层

版图图层与物理层的关系与区别

衬底 N+掺杂区 (源、漏)

栅氧层 多晶层 介质层 金属层

阱区 (well) 有源区 (active) N、P选择性参杂 (select) 多晶层 (poly) 接触孔 (contact) 金属层 (metal)

版图绘制流程

元器件版图绘制 正确反映元器件的尺寸、管脚和特性。

绘制版图的几个注意事项

晶体管尺寸必须与电路中的尺寸一致; 版图中各图层需遵循设计规则的限定; 布局时,器件摆放尽量紧凑; 布线时金属宽度和间距需满足设计规则要求; 器件之间的连接关系必须完全与电路图中的连接关系相对应。

四CMOS反相器的设计

四CMOS反相器的设计CMOS反相器是一种使用互补金属氧化物半导体(CMOS)技术制造的电子电路元件,它能够将输入信号反向输出。

由于CMOS反相器具有低功耗、高噪声免疫性、广泛的电源电压范围和快速的切换速度等优点,因此被广泛应用于数字电路中。

接下来,我将详细介绍CMOS反相器的设计过程。

首先,我们需要选择适当的CMOS反相器拓扑结构。

在CMOS技术中,两种常见的CMOS反相器拓扑结构为P型金属氧化物半导体(PMOS)和N型金属氧化物半导体(NMOS)的串联结构,以及PMOS和NMOS的并联结构。

在本文中,我们选择串联结构的CMOS反相器作为设计示例。

接下来,我们需要设计PMOS和NMOS管的尺寸。

在CMOS技术中,尺寸设计对电路性能具有重要影响。

一般来说,PMOS管的尺寸应大于NMOS 管,以提高输出驱动能力。

此外,尺寸设计也需要考虑功耗和响应时间等因素。

在设计过程中,可以使用模拟电路设计工具进行参数优化,以获得最佳的尺寸方案。

接下来是电路的布线设计。

在CMOS反相器的布线设计中,需要考虑动态电压降、互连电容和电感等因素的影响。

在布线设计过程中,应将线宽和间距等参数进行折衷考虑,以满足电路性能和面积效益的要求。

设计完成后,需要进行电路的仿真验证和性能评估。

常用的仿真工具有HSPICE、LTSpice等。

在仿真过程中,可以通过输入不同的信号,并观察输出响应以评估电路的性能。

在CMOS反相器的设计中,还需要考虑到工艺和温度等因素的影响。

由于CMOS工艺受制于设备尺寸和工艺过程的变化,工艺参数的变化会导致电路性能产生偏差。

此外,温度对CMOS电路的性能也有显著影响,因此在设计中需要对工艺和温度进行适当的补偿。

最后,在设计完CMOS反相器后,还需要进行实际的制造和测试验证。

在制造过程中,需要遵循CMOS工艺流程,并进行工艺参数的控制和调整。

在测试验证过程中,可以使用专业的测试设备进行电路性能的测试和评估,以验证设计的正确性和可靠性。

cmos反相器逻辑电路设计的方法

cmos反相器逻辑电路设计的方法CMOS反相器是基本的逻辑门之一,可以用来构建更复杂的逻辑电路。

以下是设计CMOS反相器逻辑电路的方法:

1.选择合适的器件:CMOS反相器由PMOS和NMOS组成,

需要选择合适的器件来满足电路的要求。

通常,PMOS

的沟道为空穴,具有高电导率,适合作为开关,而NMOS

的沟道为电子,具有低电导率,适合作为负载。

2.设计电路结构:根据反相器的设计要求,设计电路结构,

包括PMOS和NMOS的排列方式、输入和输出的连接方式

等。

3.确定参数:根据电路的要求,确定参数,如阈值电压、

静态电流、动态电流等。

4.进行模拟验证:使用电路模拟软件进行验证,确认电路

的功能和性能是否达到设计要求。

5.进行版图设计:根据电路设计的要求,进行版图设计,

包括器件的排列、布线、电学参数的优化等。

6.进行制造和测试:将版图提交给制造厂家进行制造,并

进行测试,确认电路的性能和可靠性是否符合设计要

求。

需要注意的是,在设计CMOS反相器逻辑电路时,需要考虑电路的稳定性、速度、功耗等因素,以满足实际应用的要求。

同时,还需要遵循基本的电路设计规则和安全规范,如避免电流过大、避免信号过冲等。

CMOS反相器特性设计

电子科学与应用物理学院器件与工艺课程设计报告课题名称:CMOS反相器特性设计姓名: 王宏宇专业班级:指导老师:宣晓峰小组成员:日期:2015-2016学年第2学期一、课程设计的目的在大三学年第二学期我们学习了《半导体器件物理》、《半导体集成电路基础》以及《集成电路制造技术基础(双语)》等专业课程,对BJT和MOS器件的工作原理和制备方法有了初步的了解以及一定的认识。

此时,在老师的指导下,结合具体设计内容,同时利用已经学过的知识,进行一次与器件和工艺有关的课程设计,不仅可以让我们对课堂内学习的知识有更多的了解,同时还可以掌握课程设计的完整过程和各个环节、基本方法和途径,学习使用虚拟机,mdraw,dessis,inspect等现代电路设计工具,并结合所学理论完成预定题目的综合性设计。

与此同时,多人合作分工协作,可以培养团队精神和意识,提高我们理论联系实际的能力。

二、课程设计的内容与题目要求内容:CMOS反相器特性设计目标:设计一个CMOS反相器(由一个NMOS,一个PMOS构成,一个电容器作为模拟负载),优化其开关性能和开关时的瞬态电流。

1)运用MDRAW工具分别设计一个栅长为0.18m的NMOS和一个PMOS,在MDRAW下对器件必要的位置进行网格加密;2)先通过dessis模拟确定NMOS和PMOS的转移特性,确定器件结构、掺杂及阈值电压等无错误。

3)再根据设计目标,确定反相器的网表,其负载电容取3e-14F(模拟在应用中存在的寄生电容、后级输入电容以及版图中的连线电容等);4)编制dessis模拟程序,在模拟程序中设定反相器中各组件的连接,分析此器件在一个2V的矩形脉冲信号下的开关特性;5)应用INSPECT工具对比输入信号、输出信号和电流信号,查看其开关性能;6)计算其上升延时t ri0.1/0.9;7)假定输出高电平U oh(驱动逻辑电平1时的最低输出电压)=Vdd-0.2V、输出低电平U il(驱动逻辑电平0时的最高输出电压)=0.2V,由此确定此反相器的输入高电平U ih(能确认为1的最低电压)、输入低电平U il(能确认为0的最高电压);8)调节PMOS和NMOS的结构(栅宽、栅氧厚度、掺杂等),优化其上升延时、静态电流和状态变化时的开关电流(会导致同步开关噪声SSN)。

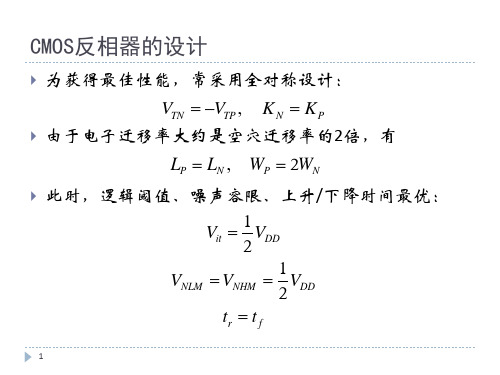

CMOS反相器的设计

KN=3.46×10-5 (A/V2),

考察噪声容限:VNLM= Vit=2.43V=0.49 VDD,

11

VNHM=VDD- Vit=2.57V=0.51 VDD

tpHL tpLH 2 CLVHL 1 tpHL f 2 Iav,HL 1 N tp CLVLH 1 tpLH r 2 Iav,LH 1 P

9

例 题

设计一个CMOS反相器,使最大噪声容限不小于0.44 VDD,且驱动1pF负载电容时上升、下降时间不大于 10ns,设VDD = 5V,VTN = 0.8V,VTP = -1V,Cox = 4.6×10-8 F/cm2,μn = 500 cm2/Vs、μp = 200 cm2/Vs。

完成能够实现设计要求的集成电路产品 设计要求:

功能 可靠性 速度 面积 功耗

3

1、反相器的可靠性

噪声容限:逻辑阈值点

把Vit做为允许的输入高电平和 低电平极限 VNLM=Vit VNHM=VDD-Vit VTN 1 K r VDD VTP VNLM与VNHM中较小的 Vin 决定最大直流噪声容限 1 1 K

10

1 1 Kr Vit = VTN 1 K r VDD VTP 1 1 Kr K r VTN VDD VTP 1 Kr

1 t r r P 2 2(1 ) ln (1 P ) P

0.1

1.9 2 P 0.1

1

CMOS反相器的设计

实际情况:不可能获得完全对称设计

输入信号较差:考虑噪声容限 负载电容较大:考虑速度 对于大部分内部电路(扇出为1):考虑面积

四、CMOS反相器的设计

二、电路前端设计

确定电路结构 确定所使用的器件 逻辑功能 功耗输出驱动能力 输入电流

CMOS反相器的设计 CMOS反相器的设计

CMOS反相器的设计 CMOS反相器的设计

1. 确定电路结构

CMOS反相器的设计 CMOS反相器的设计

2. 确定所使用的器件 确定MOS管的宽长比。 管的宽长比。 确定 管的宽长比 宽长比过大——版图使用面积大 版图使用面积大 宽长比过大 宽长比过小——版图无法加工 版图无法加工 宽长比过小 思路: 思路: • • 管的宽长比。 (1)利用版图规则确定 )利用版图规则确定NMOS管的宽长比。 管的宽长比 管宽长比为NMOS管的 倍。 管的2倍 (2)PMOS管宽长比为 ) 管宽长比为 管的

5. 输出驱动能力

CMOS反相器的设计 CMOS反相器的设计

5. 输出驱动能力

CMOS反相器的设计 CMOS反相器的设计

输出驱动能力的计算: 输出驱动能力的计算

I=U/R=2.5/3.3k=0.75mA

6. 输入电流

CMOS反相器的设计 CMOS反相器的设计

6. 输入电流

CMOS反相器的设计 CMOS反相器的设计

CMOS反相器的设计 CMOS反相器的设计

Layout (Design) Rules (II)

poly1 (多晶硅一层 : 多晶硅一层): 多晶硅一层 3a . minimum poly1 width 0.6um 3b . minimum poly1 spacing 1.0um 3c . poly1 extension past ndiff or pdiff 0.4um Metal1(金属一层 : 金属一层): 金属一层 4a . minimum metal1 width 0.8um 4b . minimum metal1 spacing 1.0um Metal2(金属二层): 6a . minimum metal2 width 1.0um 6b . minimum metal2 spacing 1.0um

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VDD

Contacts Out Metal 1

GND 7

4、反相器的功耗

PD CL fVD2D

增加器件宽长比会增加电容

电路速度增加也会提高功耗

电源电压的增加

功耗暂时不作为反相器设计的约束

8

Vit = VTN 1 Kr VDD VTP KrVTN VDD VTP

1 1 Kr

1 Kr

反相器设计:综合 tp tpHL tpLH 2

利用可靠性、速度和面积约束中 的两个就可以得到一组Wp和Wn

对称反相器:对于NMOS和

tpHL CLVHL f

Iav,HL

1

1N

2

tpLH CLVLH r

Iav,LH

1

1P

2

PMOS阈值基本相等的工艺,设

计Kr=1

对称反相器具有最大的噪声容限 和相等的上升和下降延迟,在没 有具体设计要求情况下是相对优 化的设计

1 1 Kr

VNLM与VNHM中较小的 决定最大直流噪声容限

Vit = VTN 1 Kr VDD VTP KrVTN VDD VTP

1 1 Kr

1 Kr

4

Vit = VTN 1 Kr VDD VTP KrVTN VDD VTP

1 1 Kr

1 Kr

可靠性:噪声容限

面向可靠性最优的设计目标, 噪声容限最大就是使得Vit= Vdd/2

1 1 Kr

Vit = VTN 1 Kr VDD VTP

1 1 Kr

KrVTN VDD VTP 1 Kr

tr

r

P 0.1 (1 P )2

1 2(1P )

ln

1.92 P 0.1

CL

r

K PVDD

αN=VTN/VDD=0.16, αP=-VTP/VDD=0.2 则 tr=1.85τr=10ns, τr=5.4ns

2

CMOS 反相器的设计

完成能够实现设计要求的集成电路产品 设计要求:

功能 可靠性 速度 面积 功耗

3

1、反相器的可靠性

噪声容限:逻辑阈值点

把Vit(Vth)做为允许的输入高电 平和

低电平极限

VNLM=Vit

Vin VTN

1 Kr VDD VTPVNHM=VDD-Vit

RP RN RW

Delay (D): tpHL = (ln 2) RNCL

tpLH = (ln 2) RPCL

栅电容:

W

C gin

3 Wunit

Cunit

14

Inverter with Load

CP = 2CN 2W

Delay

W

Cint

CL

CN Delay = 0.69RW(Cint + CL)= 0.69RW Cint(1+ CL /Cint)

CMOS反相器

4.1 CMOS反相器的直流特性 4.2 CMOS反相器的瞬态特性 4.3 CMOS反相器的设计

1

CMOS反相器

VDD

Vin

反相器的逻辑符号

Vin

Vout

VDD

Vou t

t

Input

Output

反相器的设计变量包括NMOS

GND

和PMOS的宽度和长度

实际的设计变量就是NMOS和 PMOS的宽度(Wp和Wn)

tpLH CLVLH r

Iav,Wp和Wn 的一个方程

tp

1 2

r

Kr

1

1

N

2

1

1 P2

6

3、反相器的面积

减小器件的宽度可以减小面积

例如最小面积的要求可以采用 最小尺寸的器件尺寸

N Well PMOS

In

利用面积的设计要求可以得到 Polysilicon Wp和Wn的一个方程

11

反相器链的设计

12

反相器链

In

Out

CL

当电路扇出(负载电容)较大的时候,如何有效进行驱动

如果负载电容给定: 则为了获得最小In到Out的延迟,应该用多少级反相器, 如何确定每级反相器的器件尺寸?

13

2W

Inverter Delay

• 采用对称反相器

W

•WP = 2WN =2W •approx. equal resistances RN = RP • approx. equal rise tpLH and fall tpHL delays

在反相器的设计中通过器件尺 寸的设计保持电路满足噪声容 限的要求

利用噪声容限的设计要求可以

得到Wp和Wn的一个方程

5

2、反相器的速度

一般用反相器的平均 延迟时间表示速度

也可以分别用上升和 下降延迟时间表示

tp tpHL tpLH 2

tpHL CLVHL f

Iav,HL

1

1N

2

Cgin, j

,

Cgin,N 1

CL

17

Optimal Tapering In

for Given N

12

Ou

t

N

CL

Delay equation has N - 1 unknowns, Cgin,2 – Cgin,N Minimize the delay, find N - 1 partial derivatives

9

例题

设计一个CMOS反相器,使最大噪声容限不 小于0.44 VDD,且驱动1pF负载电容时上升、 下降时间不大于10ns,设VDD = 5V,VTN = 0.8V,VTP = -1V,Cox = 4.6×10-8 F/cm2, μn = 500 cm2/Vs、μp = 200 cm2/Vs。

10

Delay (Internal) + Delay (Load)

Load(CL)

15

Delay Formula Cgin

Delay ~ RW Cint CL

Cint

CL

t p 0.69RW Cint 1 CL / Cint t p0 1 f /

Cint = Cgin with 1

f = CL/Cgin - effective fanout 反相器的本征延迟:tp0 = 0.69RwCint

W

RP RN RW

C gin

3 Wunit

Cunit

16

Apply to Inverter Chain

In

Out

1

2

N

CL

tp = tp1 + tp2 + …+ tpN

t pj

~

RW Cint 1

Cgin, j1

Cgin, j

tp

N

tp, j

j 1

tp0

N i 1

1

Cgin, j1

得到:KP=3.7×10-5 (A/V2) W 8

L P

同理得到: tf=1.73τf=10ns , τf =5.78ns

KN=3.46×10-5 (A/V2),

W 3 L N

考察噪声容限:VNLM= Vit=2.43V=0.49 VDD,

VNHM=VDD- Vit=2.57V=0.51 VDD