集成电路基础实验cadence反相器设计

cadence实验:PMOS、NMOS设计步骤

PMOS、NMOS 版图设计尺寸参考说明:数字1、2、3……代表画版图时,第一层、第二层、第三层……或说成第一步、第二步、第三步……,一步一步做下来。

一、PMOS版图有关尺寸参考1、THIN (薄氧化层):与DIFF(扩散区/有源区)等价,在画版图时可以用DIFF代替。

长度3.4 宽度1.2 (默认单位um)2、GPOL Y:多晶硅导电层做mos管的栅极,可以用POL Y1代替,也可以做互连线。

长:2.4 宽:0.4 离有源区(即上面的THIN)左边缘1.5u ,比有源区上下各长出0.6u3、CONT:引线孔,连接金属与多晶硅/有源区,第一层金属的接点。

大小0.4*0.4 离有源区上边缘0.4 左边缘0.34、METAL1:第一层金属,用于水平布线,如电源和地,器件之间的连接必须依靠它。

大小:0.8*0.8 离CONT各0.25、THIN(或DIFF):大小1.0*1.0 离CONT各0.3 , 或离METAL1 各0.16、PPIMP (或PIMP):P型注入掩膜。

长:4.0 宽:1.8 离有源区上边缘0.3 ,离有源区左边缘0.37、NWELL:N阱,不仅用在制造P型器件,常在隔离的时候也看到它。

长6.5宽5.7 ,离PPIMP 左边缘1.2 ,离PPIMP 上边缘2.78、再另外做一个节点:CONT(0.4*0.4),METAL1(0.8*0.8),THIN (1.0*1.0)在已经画好图形的上方,CONT 离PPIMP 上端1.35 ,离NWELL 左端1.8 9、在新节点上加一个NPIMP(或NIMP):N型注入掩膜,大小为1.7*1.7 ,离THIN 各0.35二、NMOS版图有关尺寸参考1、THIN :长3.4 宽0.42、GPLOY :与PMOS 相同离有源区(即上面的THIN)左边缘1.5u ,比有源区上下各长出0.6u3、CONT :0.4*0.4 ,离有源区上边缘0.3 ,左边缘0.34、METAL1 :与PMOS 相同5、THIN :与PMOS 相同6、NPIMP :长4.0 宽1.6 离有源区上边缘0.3 ,离有源区左边缘0.37、再另外做一个节点:CONT(0.4*0.4),METAL1(0.8*0.8),THIN (1.0*1.0)在已画好图形的下方,CONT 离NPIMP 下端1.15 ,离NPIMP 左端0.6 8、在新节点上加一个PPIMP:大小1.7*1.7 离THIN 各0.35第三部分:画一个反相器时要做一个输入引脚1、GPOL Y:大小为1.6*1.6 (大小可以随意),离PMOS 的NWELL 下边缘0.7u(距离可以随意),此线框进入PMOS与NMOS 相连的GPOL Y 深度为0.2 。

实验一、Cadence软件操作步骤

实验一基本门电路设计——电路仿真一、实验内容:完成CMOS 反相器的电路设计完成CMOS 反相器的电路设计实验目的掌握基本门电路的设计方法掌握基本门电路的设计方法熟悉Cadence 的设计数据管理结构,以及定制设计的原理图输入、电路仿真、版图设计、版图验证工具的使用二、实验目的:基于csmc05工艺,完成一个具有逻辑反相功能的电路设计要求:设计要求:1.反相器的逻辑阈值在Vdd/2附近,即噪声容限最大2.反相器的版图高度限制为24微米,电源和地线宽度各为2微米3.反相器宽度限制为mos 器件不折栅4.为了给顶层设计留出更多的布线资源,版图中只能使用金属1和多晶硅作为互连线,输入,输出和电源、地线等pin脚必须使用金属15.版图满足设计规则要求,并通过LVS 检查三、设计过程:启动icfb1.建立自己的设计库2.用Virtuoso Schematic Composer 画电路图3. 在Analog Design Environment中进行电路仿真4. 用Virtuoso (XL)Layout Editer 画版图5. 利用diva 工具进行DRC检查,用dracula进行DRC和LVS验证。

四、实验步骤1.Cadence软件操作步骤:(1).点击桌面虚拟机快捷方式图标;(2).打开虚拟机(存放路径:F:\cadence);(3).启动虚拟机(4).单击右键,Open Teminal,弹出终端对话框,输入Cadence启动命令icfb&(&是后台运行的意思)。

2.. 新建一个库建立自己的Design Lib第一步:CIW-> Tools-Library manager第二步:File-New弹出“New Library ”对话框,在“Name”项填写要建的design lib的名字,这里是“lesson1”,选择“Attach to an existing techfile”第三步:弹出”Attach Design Library to Technology File”对话框,在“Technology Library”中选择st023.新建一个电路图(1)File->New->Cellview(2)弹出“Create New File”对话框,“Library Name”项选择“lesson1”“Cell Name”项填入”inv”,“Tool”项选择”Composer-Schematic”“Tool”项确定后, 相应的“View Name”项会出现内容因而无需输入”,点击“OK”后就进入Virtuso Schematic。

反相器设计 candence

Experiment one: inverter design●The purpose of the experiment1、Learning and mastering the cadence graphical input and simulation method;2、master the principle and design method of basic inverter;3、master inverter voltage transmission characteristic curve of VTC test method●Experimental contentThis experiment is mainly using cadence software to design a basic inverter, and the simulation tool analog artist (spectre) to test the inverter voltage transfer characteristic curve, and rendering and inverter layout verification●Experimental procedure1.The inverter principle drawing in the cadence environment asshown in the figure.2.Simulation of the voltage transfer characteristic curve of INV3.In the figure chosen to connect the input and output of the inverter wire simulation4.simulation result5.Output waveform6.Draw a CMOS inverter. Painting layout should be strictly following thedesign rules (tsmc0.25rule.pdf), that is, to meet the minimum spacing, minimum bounding, minimum extension, minimum width, etc.. The drawing process of inverter layout7.DRC(design rule check)Design rule checkExperimental summaryThrough the experiment, I learned how to use the cadence design of inverter circuit, and simulation, and also learn the drawing and inverter layout verification, make me have a more profound understanding of the circuit simulation. These experiences will benefit me in my study and work in the future.。

集成电路实验报告

班级:XX姓名:XXX学号:XXXXXX指导老师:XXX实验日期:XXXX年XX月XX日一、实验目的1. 理解集成电路的基本组成和工作原理。

2. 掌握基本的集成电路设计方法,包括原理图设计、版图设计、仿真分析等。

3. 学习使用集成电路设计软件,如Cadence、LTspice等。

4. 通过实验加深对集成电路理论知识的理解,提高动手能力和问题解决能力。

二、实验内容本次实验主要包括以下内容:1. 原理图设计:使用Cadence软件绘制一个简单的CMOS反相器原理图。

2. 版图设计:根据原理图,使用Cadence软件进行版图设计,并生成GDSII文件。

3. 仿真分析:使用LTspice软件对设计的反相器进行仿真分析,测试其性能指标。

4. 版图与原理图匹配:使用Cadence软件进行版图与原理图的匹配,确保设计正确无误。

三、实验步骤1. 原理图设计:- 打开Cadence软件,选择原理图设计模块。

- 根据反相器原理,绘制相应的电路符号,包括NMOS和PMOS晶体管、电阻和电容等。

- 设置各个元件的参数,如晶体管的尺寸、电阻和电容的值等。

- 完成原理图设计后,保存文件。

2. 版图设计:- 打开Cadence软件,选择版图设计模块。

- 根据原理图,绘制晶体管、电阻和电容的版图。

- 设置版图规则,如最小线宽、最小间距等。

- 完成版图设计后,生成GDSII文件。

3. 仿真分析:- 打开LTspice软件,选择仿真模块。

- 将GDSII文件导入LTspice,生成对应的原理图。

- 设置仿真参数,如输入电压、仿真时间等。

- 运行仿真,观察反相器的输出波形、传输特性和功耗等性能指标。

4. 版图与原理图匹配:- 打开Cadence软件,选择版图与原理图匹配模块。

- 将原理图和版图导入匹配模块。

- 进行版图与原理图的匹配,检查是否存在错误或不一致之处。

- 修正错误,确保版图与原理图完全一致。

四、实验结果与分析1. 原理图设计:- 成功绘制了一个简单的CMOS反相器原理图,包括NMOS和PMOS晶体管、电阻和电容等元件。

cadence反相器

cadence反相器反相器版图设计与仿真⼀.实验⽬的1.熟悉Hspice的⽤法以及⽹表的规则写法1.熟悉cadence软件的使⽤以及如何利⽤cadence画版图2.熟悉对版图DRC验证和lvs检查⼆.实验器材已安装Hspice和VWware软件的电脑,和虚拟机要有cadence软件三.实验内容1)反相器的电路仿真2)Layout的认识3)反相器Layout设计4)DRC验证5)LVS验证四.实验步骤1.写好反相器的⽹表如下*lab1 inv.sp.include 'hua05.sp'.global vdd gndM1 OUT IN VDD VDD PMOS W=20u L=0.6uM2 OUT IN GND GND NMOS W=10u L=0.6uV1 VDD GND 5V2 IN GND PULSE(0 5 0ns 0.5ns 0.5ns 5ns 10ns).OPTIONS POST.tran 0.01ns 60ns.end2.在Hspice软件上仿真,看波形图是否符合3.画出反相器版图,再进⾏DRC验证,得到必须为没有错误如下:4.在linux系统⾥拷贝bd07.lvs和inv.gds和inv.sp到test-inv⽂件夹⾥,修改⽹表⽂件名为inv.sp,以及bd07.lvs和bd07.lpe的⽂件,并执⾏:CIW->File ->Export->Stream…⽣成inv.gds⽂件5.进⾏lvs检查,终端代码如下:%LOGLVS%htv%case%cir /home/icer/test-inv/inv.sp (⽹表的路径)%:con inv (⽹表中单元名)%:exit_____________________________%PDRACULA%:/g /home/icer/test-inv/bd07.lvs (LVS规则⽂件名)%:/f%.//doc/92d3bc4fa300a6c30d229f0a.html6.检查上述⽣成lvsout⽂件,看原理图与版图是否匹配7.进⾏lpe检查,⽣成PRENENT.DAT⽂件,终端代码如下:%PDRACULA%:/g /home/icer/test-inv/bd07.lpe (LVS规则⽂件名)%:/f%.//doc/92d3bc4fa300a6c30d229f0a.html8.在windows下将PRENET修改成SP⽂件,然后打开⽂件将PM和NM修改成NMOS 和PMOS,保存9.编写HFZ.sp⽂件如下:* Lab1 inv.sp********* SPICE Library **************.include 'hua05.sp'.include 'PRENET.sp'*****************************************.global vdd gndX1 IN OUT PRENETV1 VDD GND 5V2 IN GND PULSE(0 5 0ns 0.1ns 0.1ns 5ns 10ns).OPTIONS POST.tran 0.01ns 60ns.end10.将hua05.sp 和PRENET.sp,INV.sp 和HFZ.sp拷贝到同⼀个⽂件夹⾥11.⽤Hspice打开HFZ.sp⽂件,分析,看波形图如下:五.实验总结本次实验对我受益匪浅,通过本次反相器的实验,我更加熟悉了Hspice 软件和cadence软件,熟悉了利⽤这两个软件来制作⽹表,版图,以及DRC 验证,lvs检查,lpe检查。

cadence 使用 实验二——反相器版图绘制

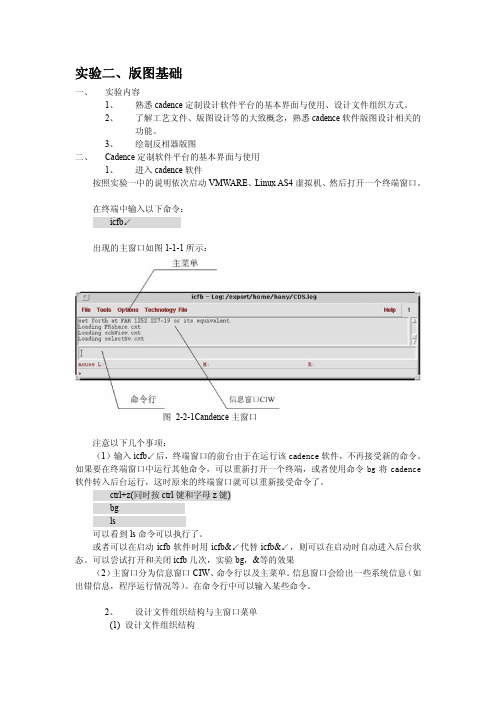

(2)、建立反相器设计单元(cell)的版图视图(layout view)。 在 主 窗 口 中 FileàNewàcell view, 或 者 Library Manager 窗 口 中 使 用 菜 单 FileàNewàCell View,弹出的窗口中确定 Library Name 为前面新建的设计库(1), Cell Name 可以自己决定,例如我们输入 inv_1 (2),View Name 输入“layout”(3),此 项也可以不填,通过下面的 Tool 下拉菜单选中 Virtuoso,则会自动改变为 layout。 最 后点“OK”(4)。

IM

第二层多晶硅电阻阻挡层

PC poly Cap,用作多晶硅电容上极板和多晶硅电阻的第二层多晶硅

详细的工艺信息请参考设计规则(0.6umDPDMMixedSignalTechnologyTopological DesignRule.pdf),本次实验将会用到的层为 TB、TO、GT、SP、SN、W1、A1、W2、A2

TB

tub,n阱,作为pmos器件衬底

TO

Thin Oxide,有源区,作为mos的源漏区

GT gate,多晶硅1,作为mos栅极

SP

P+注入区

SN N+注入区

W1 接触孔,金属1到多晶硅和有源区的接触孔

A1

铝1,第一层金属

W2 通孔1,金属1和金属2的接触孔

A2

铝2,第二层金属

CP bond pad,pad开孔

本课程中使用csmc双硅双金属混合信号工艺主要的设计层包括tbtubn阱作为pmos器件衬底thinoxide有源区作为mos的源漏区gtgate多晶硅1作为mos栅极spp注入区snn注入区w1接触孔金属1到多晶硅和有源区的接触孔a1铝1第一层金属w2通孔1金属1和金属2的接触孔a2铝2第二层金属cpbondpadpad开孔im第二层多晶硅电阻阻挡层pcpolycap用作多晶硅电容上极板和多晶硅电阻的第二层多晶硅详细的工艺信息请参考设计规则06umdpdmmixedsignaltechnologytopologicaldesignrulepdf本次实验将会用到的层为tbtogtspsnw1a1w2a2这些图层对于我们的设计工具来说是通过工艺文件来进行定义的

反相器cadence

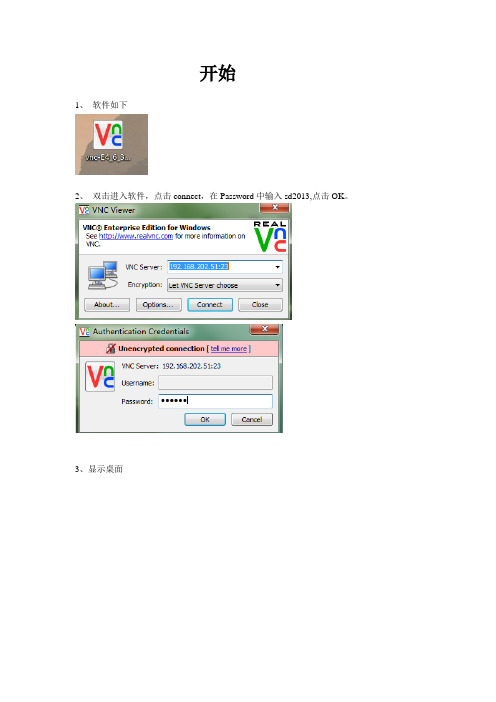

开始1、软件如下2、双击进入软件,点击connect,在Password中输入sd2013,点击OK。

3、显示桌面4、打开终端,即点击鼠标右键,选择open terminal5、在终端内输入pwd,即可显示当前工作目录。

ls 显示目录下的内容。

我们可以建立VLSI 文件夹,即输入mkdir VLSI;cd VLSI即进入VLSI文件夹;输入icfb & ,再点击回车,就会出现如图所示的CIW(Command Interpreter Window),即命令解释窗。

6、建新库,在库里面我们将画出反相器电路图、振荡器电路图和版图三个cell。

①在CIW中,点击File→New→Library...;②在New Library对话框内输入库名,例如ring_osc;并在Technology File 中选择第一项,compile a new techfile.,然后点击Browse,在打开的FILE Browser中的File中输入/tools/cadence/cds5141/tools.lnx86/dfII/samples/techfile,点击回车,下拉辐条,找到sample2003.tf,点击OK一路返回,将提示tf文件加载成功。

反相器篇7、建立新文件,先画反相器电路图①在CIW中,选File→New→Cell view...,=>“Create New File”对话框。

②在Library Name,选刚建的库zdq, ③在Cell Name中输入单元名,inv,④点击Tool文本区右端的按钮,出现下拉菜单。

选择Composer-Schematic,在View Name内自动生成Schematic。

⑤按OK键=>“Virtuoso Schematic Editing”(电路图编辑窗)。

8、加器件①选命令Add→Instance...<i>,出现“Add Instance”对话框。

基于Cadence的模拟集成电路设计

2.1

Cadence初次启动之前需要如下一些配置文件:

.cshrc文件:有关一些Cadence必需的环境变量,如Cadence软件的路径及license。

.cdsenv文件:包含Cadence各种工具的一些初始设置。

.cds.lib文件:用户库的管理文件,在第一次运行Cadence时自动生成。

.cdsinit文件:包含Cadence的一些初始化设置以及快捷键设置。

进入连线命令后,于起点单击左键,再于终点单击左键。画完一段导线后,此时并没有退出画线命令,可以继续画连接线,直到画完所所有的连接线后,按ESC退出画线命令。连好线的电路图如图3.7所示,其中左右两条水平导线是后在连连接端口用的。

还可以对画好的线进行命名,键入快捷键L(小写),在弹出的对话框中输入线名,比如a,点击Hide,然后将字母a移动到要命令的线附近点击左键放下,如果名字离线较远,则要求再单击所要命名的线。

如图1.1Cadence模拟集成电路设计流程

本实验指导书针对以上流程,通过设计一个简单的缓冲器的原理图到最终的版图,对Cadence的Composer,Analog Desing Environment,Virtuoso,Assura等各大功能模块逐一做个简单介绍。此外还包括一些Cadence平台的知识介绍。Cadence开发了自己的编程语言skill以及相应的编译器,整个Cadence可以理解为一个搭建在skill语言平台上的可执行文件集。初学者对此可以不用理会,当用户深入后,可以用skill语言对Cadence设计工具进行扩展。

图3.5选择了元件后的添加器件窗口

可以发现Library,Cell,View等都自动填上了相应的信息。同时多出了一些参数列表(拖动滚动条可以看到更多)。点击Hide隐藏当前窗口,此时鼠标对应有一个PMOS的symbol,此时按r键,可以旋转PMOS,继续点击鼠标左键,否则按ESC取消当前的放置器件命令。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

题目:反相器分析与设计

姓名:白进宝

学院:微电子与固体电子学院

学号:201722030523

签名:教师签名:

摘要

CMOS指互补金属氧化物(PMOS管和NMOS管)共同构成的互补型MOS集成电路制造工艺,它的特点是低功耗。

由于CMOS中一对MOS组成的门电路在瞬间看,要么PMOS导通,要么NMOS导通,要么都截至,比线性的三极管(BJT)效率要高得多,因此功耗很低。

本次设计的是反相器,通过电路搭建前仿真,实现其功能。

然后进行版图设计,提取寄生参数后进项后仿真。

关键词:CMOS、反相器、低功耗、集成电路版图

1、技术指标要求

面积:100um2

速度:大于1GHz

功耗:功耗与电源电压、工作速度、负载等诸多因素有关。

2、电路搭建

工艺库:smic18mmrf

器件参数:

设置NMOS与PMOS宽长比。

电路结构:

如图,电路结构。

有两级反相器组成,第二级为负载,因为在实际电路中电路都是带载的。

分别作NMOS和PMOS的直流输出特性曲线,NMOS的阈值电压大约为0.5V左右,PMOS的阈值电压大约为0.6V左右。

3、仿真

(1)进行直流传输特性仿真分析

图一电源电压为5V,图二电源电压为2V。

可以看到图二的特性比图一好,这是由于降低的电压,从而使特性变好。

继续降低电源电压为1V后,特性更好。

但是当降到200mV时,特性反而变差。

这是由于当电压降到接近于阈值电压或更低时,管子无法导通,性能变差。

(2)瞬态特性分析

瞬态特性分析,反相器实现非门的功能。

将时间轴拉长,可以看到当输出反向时,存在一个过冲现象,这是由于栅漏电容造成。

(3)工作频率分析

上图为反相器没有带负载的情况下测出的下降时间,下图为带一个反相器测出的下降时间。

从而我们可以得出电路的扇出越多,性能越差,所以在数字电路中,我们尽量将扇出控制在4以内。

更多的扇出将通过组合电路多级实现。

由图可得上升时间为23.85ps,下降时间为29.25ps。

工作频率=1/(2×max(上升时间,下降时间))=17GHz

(4)功耗分析

如以上两幅图,分别在电源电压5V和2V的情况下动态电流分析。

5V时电流峰值为1mA左右,2V时电流峰值为300uA左右。

4、版图

版图设计是将模拟优化后的电路转化成一系列几何图形,这些几何图形包含了集成电路尺寸大小、各层拓扑定义等有关元件的物理信息。

如图为在cadence版图软件中绘制的反相器的版图。

面积为20um×10um=200um2 5、后仿真

以上两幅图为后仿真的交流仿真图。

由图可得上升时间为82.33ps,下降时间为70.69ps。

工作频率=1/(2×max(上升时间,下降时间))=6.07GHz。

显然画出版图提取寄生参数后性能变差,工作频率变小。

左图为前仿真的直流输出特性曲线,右图为后仿真的直流输出特性曲线,通过对比可以看出,两者区别不大。

6、对比技术指标完成情况

(1)工作速度。

前仿真的速度为17GNz,后仿真的速度为6GHz,设计指标为1GNz。

(2)面积。

版图的面积为200um2,设计指标为100um2,与设计指标有一定差距。

(3)功耗。

降低电源电压可以降低功耗,通过以上仿真可以看出电压由5V变为2V后动态电流也急剧下降。

减小输入信号的上升下降时间也可以降低功耗。

7、总结

本次设计大反相器部分指标达到了设计要求,部分没有达到设计要求。

(1)在直流传输特性分析中减小电压能一定程度上提高性能。

但是当降到200mV时,特性反而变差。

这是由于当电压降到接近于阈值电压或更低时,管子无法导通,性能变差。

(2)在进行动态仿真时,当输出反向时,存在一个过冲现象,这是由于栅漏电容造成,是由于器件本身的寄生参数造成的。

在降低电压的同时这个过冲现象就会越来越明显。

(3) 进行直流传输特性仿真分析时,降低电压从而使特性变好。

继续降低电源电压为1V后,特性更好。

但是当降到200mV时,特性反而变差。

从NMOS和PMOS的直流输出特性曲线看出NMOS的阈值电压大约为0.5V左右,PMOS的阈值电压大约为0.6V左右。

当电压降到接近于阈值电压或更低时,管子无法导通,性能变差。

(4)电路的扇出越多,性能越差,所以在数字电路中,我们尽量将扇出控制在4以内。

更多的扇出将通过组合电路多级实现。