CMOS反相器电路版图设计与仿真

MOS集成电路--CMOS反相器电路仿真及版图设计

MOS管集成电路设计题目:CMOS反相器电路仿真及版图设计*名:***学号:***********专业:通信工程指导老师:***2014年6月1日摘要本文介绍了集成电路设计的相关思路、电路的实现、SPICE电路模拟软件和LASI7集成电路版图设计的相关用法。

主要讲述CMOS反相器的设计目的、设计的思路、以及设计的过程,用SPICE电路设计软件来实现对反相器的设计和仿真。

集成电路反相器的实现用到NMOS和PMOS各一个,用LASI7实现了其版图的设计。

关键字:集成电路CMOS反相器LT SPICE LASI7目录引言 ....................................................................................................................................... - 2 -一、概述 ............................................................................................................................... - 2 -1.1MOS集成电路简介.................................................................................................... - 2 -1.2MOS集成电路分类.................................................................................................... - 2 -1.3MOS集成电路的优点................................................................................................ - 3 -二、LTspice电路仿真 .......................................................................................................... - 3 -2.1SPICE简介 ................................................................................................................... - 3 -2.2CMOS反相器LT SPICE仿真过程 ..................................................................... - 3 -2.2.1实现方案 .............................................................................................................. - 3 -2.2.2 LTspice电路仿真结果 ...................................................................................... - 5 -三、LASI版图设计 ............................................................................................................... - 5 -3.1LASI软件简介........................................................................................................ - 5 -3.2版图设计原理......................................................................................................... - 6 -3.3LASI的版图设计.................................................................................................... - 6 -四、实验结果分析 ............................................................................................................... - 8 -五、结束语 ........................................................................................................................... - 8 -参考文献 ............................................................................................................................... - 8 -引言CMOS技术自身的巨大潜力是IC高速持续发展的基础。

CMOS反相器版图设计

XXXXXXX实验报告课程名称:集成电路设计实验名称:CMOS反相器版图设计学号姓名:指导教师评定:____________________________ 签名:_____________________________一、实验目的1、了解集成电路版图设计流程。

2、利用L-Edit 进行NMOSFET 版图设计。

3、利用L-Edit 进行CMOS反相器设计。

二、实验器材计算机一台,Tanner L-Edit软件三、实验原理CMOS 反相器由PMOS 和NMOS 晶体管组成,利用PMOS晶体管版图和NMOS 晶体管版图可以完成COMS反相器版图的设计。

四、实验步骤1、设计PMOS晶体管版图。

2、设计N MOS晶体管版图。

3、设计CMOS反相器版图:(1)启动版图编辑器L-Edit。

(2)新建文件。

新建一个Layout 文件,文件的设置信息可以从前面创建的文件中复制。

(3) 对文件进行重命名。

将L-Edit 编辑器默认的文件名Layout 改为Inverter。

(4) 设置格点与坐标。

格点与坐标的设定方式与创建PMOS 晶体管时设定的方法一致。

(5) 调用PMOS 和NMOS 晶体管作为例化单元。

使用Cell---Instance 命令来调用PMOS 单元。

在出现的Select Cell to Instance 对话框中,通过点击Browse按钮浏览到“MOS”文件,可以看到该文件下面有PMOS 和NMOS 两个单元,点击PMOS,然后点击“OK”,可以看到Inverter 文件cell0 单元的版图已经添加了PMOS 单元。

利用同样的方法,可以将NMOS 单元也添加进来。

(6) 连接PMOS 和NMOS 晶体管的栅极。

从CMOS 反相器电路可知,PMOS晶体管和NMOS 晶体管的栅极要连在一起作为反相器的输入端,所以在放置这两个晶体管的时候可以将两者的栅极对准,以便连接。

具体操作是,选择Layer的多晶硅(Poly)层和方框绘图工具后,在版图区域中画一个宽度与晶体管栅极相等的多晶硅矩形,如图1 所示。

CMOS反相器原理图版图的仿真设计

集成电路专业学年论文论文题目:CMOS反相器原理图版图设计与仿真学院:电子工程学院年级:2008级专业:集成电路设计与集成系统姓名:学号:指导教师:2011年 7月 8日摘要门电路是构成各种复杂数字电路的基本逻辑单元,掌握各种门电路的逻辑功能和电气特性,对于正确使用数字集成电路是十分必要的。

MOS门电路:以MOS管作为开关元件构成的门电路。

MOS门电路,尤其是CMOS门电路具有制造工艺简单、集成度高、抗干扰能力强、功耗低、价格便宜等优点,得到了十分迅速的发展。

所谓CMOS (Complementary MOS),是在集成电路设计中,同时采用两种MOS器件:NMOS和PMOS,并通常配对出现的一种电路结构。

CMOS电路及其技术已成为当今集成电路,尤其是大规模电路、超大规模集成电路的主流技术。

反相器是数字电路中的一种基本功能模块。

将两个串行反相器的输出作为一位寄存器的输入就构成了锁存器。

锁存器、数据选择器、译码器和状态机等精密数字符件都需要使用基本反相器。

因此此次针对CMOS反相器原理图、版图设计与仿真也是很有必要的自己学会了Tanner EDA软件的使用。

也进一步了解了CMOS反相器直流特性瞬态特性和版图的绘制。

关键词CMOS;反相器;Tanner EDA;设计;仿真;版图;AbstractThe complex digital circuits are constituted by the basic gate circuits,and the Gate circuits is the logic cells.Grasp at various kinds of logic gates' functions and electrical characteristics for the proper use of digital integrated circuits is essential. MOS gate[1]: The MOS tube as a switching element constitute the gate. MOS gate, especially a CMOS gate with simple manufacturing process, high integration, anti-interference ability, low power consumption, cheap, etc., has been very rapid development. The so-called CMOS (Complementary MOS), is in IC Design, while using two MOS devices: NMOS and PMOS, and the emergence of a circuit is usually paired structure. CMOS circuits and technology has become today's integrated circuits, especially large-scale circuits, VLSI mainstream technology.Inverter is a basic digital circuit modules. The two serial output of the inverter as a register input to constitute a latch. Latch, data selectors, decoders and state machines and other precision parts are required to use a few characters in the basic inverter.Therefore, the schematic for the CMOS inverter layout design and simulation is necessary to learn their own Tanner EDA software. Further understanding of the transient characteristics of CMOS inverter DC characteristics and layout drawing.Key wordsCMOS; inverter; TannerEDA; design; simulation; territory;目录摘要 (II)Abstract (III)前言 (3)第一章使用S-Edit编辑设计CMOS反相器原理图 (4)1.1绘制CMOS反相器原理图 (4)1.1.1进入S-Edit建立新文件 (4)1.1.2环境设置环境设置 (4)1.1.3编辑模块并浏览组件库 (5)1.1.4从组件库引用模块 (5)1.1.5编辑反相器 (6)1.1.6加入输入输出端口 (7)1.1.7反相器的输出成果 (7)1.2反相器瞬态分析 (8)1.2.1进入S-Edit编辑文件 (8)1.2.2输出成Spice文件 (8)1.2.3加载包含文件 (9)1.2.4插入分析设定和输出设定命令 (10)1.2.5进行模拟 (11)1.3反相器直流分析 (12)1.3.1 进入S-Edit (12)1.3.2 加入工作电源和输入直流信号 (12)1.3.3 编辑直流电压源 (13)1.3.4 输出spice文件 (13)1.3.5分析设定和输出设定 (14)1.3.6进行模拟 (115)1.3.7结果分析 (116)第二章使用S-Edit编辑设计CMOS反相器原理图 (17)2.1绘制反相器版图的前期设置工作 (17)2.1.1 打开L-Edit软件新建版图文件 (17)2.1.2 取代设定 (17)2.1.3编辑组件 (17)2.1.4设计环境设定 (17)2.2绘制反相器 (18)2.2.1 编辑PMOS (18)2.2.2 编辑NMOS (18)2.2.3 其他部分 (20)2.3使用T-Spice进行版图设计仿真 (21)结论 (22)参考文献 (23)前言CMOS结构的主要优点是电路的静态功耗非常小,电路结构简单规则,使得它可以用于大规模集成电路、超大规模集成电路。

CMOS反相器电路设计

经典文论文题目:CMOS反相器电路设计、仿真及版图设计学生姓名:欧阳倩学号:20131060189专业:通信工程任课教师:梁竹关摘要:本文着重介绍了LTspice和LASI软件的相关设计原理和简单的设计操作,对此,我首先将从电路的工作原理方面介绍CMOS4反相器的结构、特性及其电路工作原理。

了解其工作原理是进行仿真和版图设计的基础。

然后我选择利用LTspice来进行CMOS反相器的设计仿真以此来证实其设计正确性,之后采用LASI画出符合工业设计的CMOS反相器的版图。

通过本次设计实验可以更加了解CMOS4反相器的工作原理,并掌握了CMOS4反相器的基本设计方法。

关键词:CMOS反相器LTspice LASI版图设计封装测试目录第一章引言 (4)第二章CMOS反相器 (4)2.1 CMOS反相器的结构原理 (4)2.2 CMOS反相器的特性分析 (5)第三章CMOS反相器的电路仿真 (8)3.1 CMOS反相器的电路图设计 (9)3.2 CMOS反相器的仿真及结果分析 (11)第四章CMOS反相器的版图设计 (12)结束语 (20)参考文献 (21)引言现在是一个电子信息高速发展得时代,电子产品无处不在,我们也越来越离不开各式各样的电子产品,集成电路作为电子产品的核心同样也受到了重视,电子设计也是当今社会的一大焦点问题,怎样才能设计出集性能、高效、便捷、低价为一体的电路器件又是当下人们急需解决的任务,因此培养集成设计人才也是众多高校重视的任务。

以MOS管作为开关元件的门电路称为MOS门电路。

由于MOS型集成门电路具有制造工艺简单、集成度高、功耗小以及抗干扰能力强等优点,因此它在数字集成电路产品中占据相当大的比例。

与TTL门电路相比,MOS门电路的速度较低。

MOS门电路有三种类型:使用P沟道管的PMOS电路、使用N沟道管的NMOS电路和同时使用PMOS和NMOS管的CMOS电路。

其中CMOS性能更优,因此CMOS门电路是应用较为普遍的逻辑电路之一。

CMOS反相器电路版图设计与仿真

CMO反相器电路版图设计与仿真姓名:邓翔学号:33导师:马奎本组成员:邓翔石贵超王大鹏CMO反相器电路版图设计与仿真摘要:本文是基于老师的指导下,对cade nee软件的熟悉与使用, 进行CMO反相器的电路设计和电路的仿真以及版图设计与版图验证仿真。

关键字:CMO反相器;版图设计。

Abstract:This article is based on the teacher's guida nee,familiar with cade nee software and use, for CMOS in verter circuit design and circuit simulation and Iandscape and the Iandscape design of the simulatio n.Key word : CMOS inverter;Landscape design.一引言20世纪70年代后期以来,一个以计算机辅助设计技术为代表的新的技术改革浪潮席卷了全世界,它不仅促进了计算机本身性能的进步和更新换代,而且几乎影响到全部技术领域,冲击着传统的工作模式。

以计算机辅助设计这种高技术为代表的先进技术已经、并将进一步给人类带来巨大的影响和利益。

计算机辅助设计技术的水平成了衡量一个国家产业技术水平的重要标志。

计算机辅助设计(Computer Aided Design,CAD是利用计算机强有力的计算功能和高效率的图形处理能力,辅助知识劳动者进行工程和产品的设计与分析,以达到理想的目的或取得创新成果的一种技术。

它是综合了计算机科学与工程设计方法的最新发展而形成的一门新兴学科。

计算机辅助设计技术的发展是与计算机软件、硬件技术的发展和完善,与工程设计方法的革新紧密相关的。

采用计算机辅助设计已是现代工程设计的迫切需要。

电子技术的发展使计算机辅助设计(CAD)技术成为电路设计不可或缺的有力工具。

CMOS反相器版图设计与仿真报告

CMOS反相器版图设计与仿真报告在此次实例设计中采用Tanner Pro 软件中的L-Edit组件设计CMOS反相器的版图,进而掌握L-Edit的基本功能和使用方法。

操作流程如下:进入L-Edit—>建立新文件—>环境设定—>编辑组件—>绘制多种图层形状—>设计规则检查—>修改对象—>设计规则检查—>电路转化—>电路仿真。

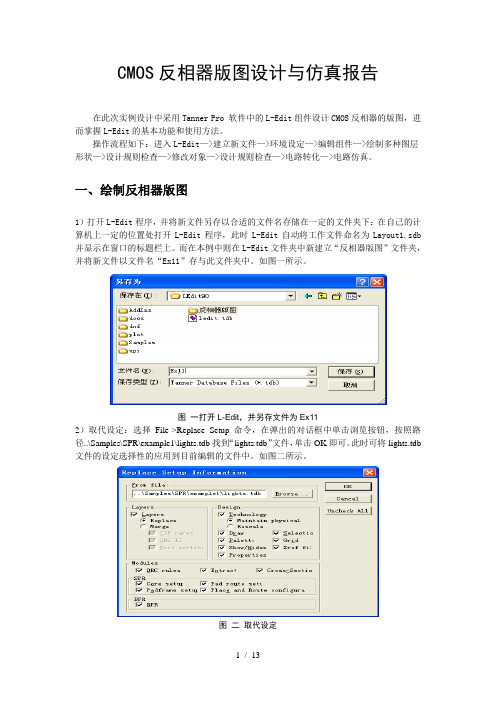

一、绘制反相器版图1)打开L-Edit程序,并将新文件另存以合适的文件名存储在一定的文件夹下:在自己的计算机上一定的位置处打开L-Edit程序,此时L-Edit自动将工作文件命名为Layout1.sdb 并显示在窗口的标题栏上。

而在本例中则在L-Edit文件夹中新建立“反相器版图”文件夹,并将新文件以文件名“Ex11”存与此文件夹中。

如图一所示。

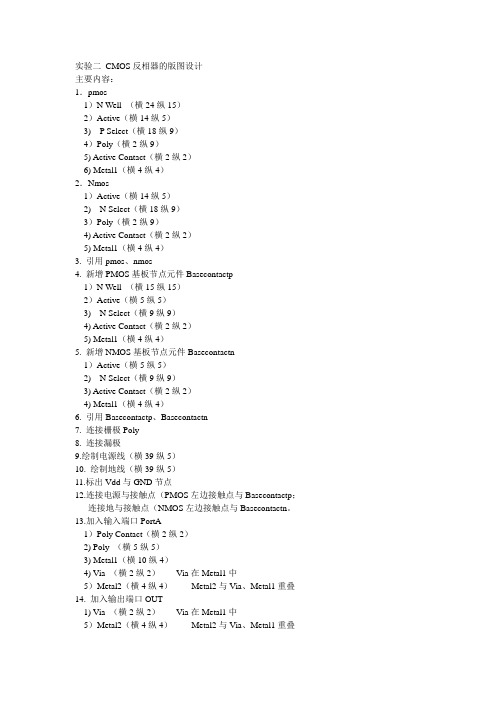

图一打开L-Edit,并另存文件为Ex112)取代设定:选择File->Replace Setup命令,在弹出的对话框中单击浏览按钮,按照路径..\Samples\SPR\example1\lights.tdb找到“lights.tdb”文件,单击OK即可。

此时可将lights.tdb 文件的设定选择性的应用到目前编辑的文件中。

如图二所示。

图二取代设定3)编辑组件:L-Edit编辑方式是以组件(Cell)为单位而不是以文件为单位,一个文件中可以包含多个组件,而每一个组件则表示一种说明或者一种电路版图。

每次打开一个新文件时便自动打开一个组件并命名为“Cell0”;也可以重命名组件名。

方法是选择Cell->Rename 命令,在弹出的对话框中的Rename cell as文本框中输入符合实际电路的名称,如本设计中采用组件名“inv”即可,之后单击OK按钮。

如图三所示。

图三重命名组件为inv4)设计环境设定:绘制布局图必须要有确实的大小,因此要绘图前先要确认或设定坐标与实际长度的关系。

实验二 CMOS反相器版图设计

实验二CMOS反相器的版图设计主要内容:1.pmos1)N Well (横24纵15)2)Active(横14纵5)3) P Select(横18纵9)4)Poly(横2纵9)5) Active Contact(横2纵2)6) Metal1(横4纵4)2.Nmos1)Active(横14纵5)2) N Select(横18纵9)3)Poly(横2纵9)4) Active Contact(横2纵2)5) Metal1(横4纵4)3. 引用pmos、nmos4. 新增PMOS基板节点元件Basecontactp1)N Well (横15纵15)2)Active(横5纵5)3) N Select(横9纵9)4) Active Contact(横2纵2)5) Metal1(横4纵4)5. 新增NMOS基板节点元件Basecontactn1)Active(横5纵5)2) N Select(横9纵9)3) Active Contact(横2纵2)4) Metal1(横4纵4)6. 引用Basecontactp、Basecontactn7. 连接栅极Poly8. 连接漏极9.绘制电源线(横39纵5)10. 绘制地线(横39纵5)11.标出Vdd与GND节点12.连接电源与接触点(PMOS左边接触点与Basecontactp;连接地与接触点(NMOS左边接触点与Basecontactn。

13.加入输入端口PortA1)Poly Contact(横2纵2)2) Poly (横5纵5)3) Metal1(横10纵4)4) Via (横2纵2)----- Via在Metal1中5)Metal2(横4纵4)------ Metal2与Via、Metal1重叠14. 加入输出端口OUT1) Via (横2纵2)----- Via在Metal1中5)Metal2(横4纵4)------ Metal2与Via、Metal1重叠。

数字集成电路第5章 CMOS反相器的设计

输入高电平时的噪声容限为

VTH VOH VON VDD VON

输入低电平时的噪声容限为

VNL VOFF VOL VOFF

第一章 概

论

5.2CMOS反相器的直流噪声容限

1.由极限输出电平定义的噪声容限

第一章 概

论

5.2CMOS反相器的直流噪声容限

2.由单位增益点定义的噪声容限 在增益为0和增益很大的输入电平的区域之间必然存在单位增益点,即

第一章 概

论

5.1 CMOS反相器的直流特性

在直流情况下,反相器没有输出电流,总满足

I DN I DP

(1)

V V

in

TN

0

(如ab段)

在此范围内,NMOS管截止,PMOS管工作在线性区

I DN I DP 0

KP

V in V TP V DD V in V TP V out 0

KN KP

,则可以得到

3 1 VC1 VDD VT 8 4

VC 2

5 1 VDD VT 8 4

这种情况下,CMOS反相器的输入高电平和输入低电平的噪声容限相等,

VTH VNL

3 1 VDD VT 8 4

第一章 概

论

5.2CMOS反相器的直流噪声容限

2.由单位增益点定义的噪声容限

特点:

Vin作为PMOS和NMOS的共栅极; Vout作为共漏极; VDD作为PMOS的源极和体端; GND作为NMOS的源极和体端

第一章 概

论

5.1 CMOS反相器的直流特性

第一章 概

论

5.1 CMOS反相器的直流特性

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CMOS反相器电路版图设计与仿真

姓名:邓翔

学号:1007010033

导师:马奎

本组成员:邓翔石贵超王大鹏

CMOS反相器电路版图设计与仿真

摘要:本文是基于老师的指导下,对cadence软件的熟悉与使用,进行CMOS反相器的电路设计和电路的仿真以及版图设计与版图验证仿真。

关键字:CMOS反相器;版图设计。

Abstract:This article is based on the teacher's guidance, familiar with cadence software and use, for CMOS inverter circuit design and circuit simulation and landscape and the landscape design of the simulation.

Key word:CMOS inverter;Landscape design.

一引言

20世纪70年代后期以来,一个以计算机辅助设计技术为代表的新的技术改革浪潮席卷了全世界,它不仅促进了计算机本身性能的进步和更新换代,而且几乎影响到全部技术领域,冲击着传统的工作模式。

以计算机辅助设计这种高技术为代表的先进技术已经、并将进一步给人类带来巨大的影响和利益。

计算机辅助设计技术的水平成了衡量一个国家产业技术水平的重要标志。

计算机辅助设计(Computer Aided Design,CAD)是利用计算机强有力的计算功能和高效率的图形处理能力,辅助知识劳动者进行工程和产品的设计与分析,以达到理想的目的或取得创新成果的一种技术。

它是综合了计算机科学与工程设计方法的最新发展而形成的一门新兴学科。

计算机辅助设计技术的发展是与计算机软件、硬件技术的发展和完善,与工程设计方法的革新紧密相关的。

采用计算机辅助设计已是现代工程设计的迫切需要。

电子技术的发展使计算机辅助设计(CAD)技术成为电路设计不可或缺的有力工具。

国内外电子线路CAD软件的相继推出与版本更新,是CAD技术的应用渗透到电子线路与系统设计的各个领域,如电路图和版图的绘制、模拟电路仿

真、工艺模拟与仿真、逻辑电路分析、优化设计、印刷电路板的布线等。

CAD 技术的发展使得电子线路设计的速度、质量、精确度得以保证。

顺应集成电路发展的要求,集成电路CAD,确切地说是整个电子设计自动化必须要有更大的发展。

随着集成电路与计算机的迅速发展,以CAD为基础的EDA技术渗透到电子系统和专用集成电路设计的各个环节。

一个能完成比较复杂的VLSI设计的EDA系统一般包括10-20个CAD工具,涉及从高层次数字电路的自动综合、数字系统仿真、模拟电路仿真到各种不同层次的版图设计和校验工具,完成自顶向下的VLSI设计的各个环节和全部过程。

为满足日益增大的信息处理能力的需求,主要从实现图形最小尺寸的工艺精度和提高单位面积晶体管数目的集成度两个方面来努力,还要综合考虑满足电路功能以及工作频率和功耗的性能指标。

CMOS技术自身的巨大发展潜力是IC高速持续发展的基础。

集成电路制造水平发展到深亚微米工艺阶段,CMOS的低功耗、高速度和高集成度得到了充分的体现。

二 CMOS反相器在cadence中的电路设计与仿真

2.1 CMOS反相器的工作原理及电路图:

CMOS反相器由一个P沟道增强型MOS管和一个N沟道增强型MOS管串联组成。

通常P沟道管作为负载管,N沟道管作为输入管。

这种配置可以大幅降低功耗,因为在两种逻辑状态中,两个晶体管中的一个总是截止的。

处理速率也能得到很好的提高,因为与NMOS型和PMOS型反相器相比,CMOS反相器的电阻相对较低。

首先通过vpn连接进入服务器,在服务器下面mkdir创建自己的文件夹然后在自己文件夹下使用icfb&命令打开软件。

在打开的窗口中file—>new—>设计电路图。

在打开的窗口中file—>open—>打开设计好的电路图

2.2 进行电路仿真

点击右上方的Tools选择Analog Environment仿真原理图。

在弹出的窗口中选择setup—>Model Library选择模型库。

选择模型库/user2/benke1/process/csmc/6S05DPTM-

ST3600/05HVCDTST3600V101/s05hvcdtst3600v101.scs。

赋值到Model Library File中Section(opt.)tt_5v.点击Add添加

进行仿真输入和输出,时间的设置

得到电路的仿真结果:

由图可知,电路设计是正确的。

三 CMOS 反相器版图的设计与DRC 验证

3.1 版图设计

在打开的窗口中file—>open—>版图文件。

同样在instance中添加元件,设计设计版图。

元件放置好以后根据原理图设置长宽比。

位置摆放好以后选中元器件,点击Edit—>Hierarchy—

>Flatten

最后得到的版图如下图:

3.2 DRC版图验证

在2013—>dengxiang—>inv目录下新建两个文件夹mkdir gds drc 。

一个用于放置版图的gds文件,另一个用于放置drc的规则文件和生成的drc 文件。

将下面目录下的文件拷到新建的drc目录下:

/user2/benke1/process/csmc/6S05DPTM-

ST3600/0.5um5VVGS40VVDSST3600BCDDraculaCommandFile-FAB1

V890:/user2/benke1/process/csmc/6S05DPTMST3600/0.5um5VVGS40VVDSST 3600BCDDraculaCommandFile-FAB1>cp drac_drc_metal1.rul

/user2/benke6/2013/dengxiang/inv/drc。

用vi打开修改如下:把INDISK设置为自己的目录

/user2/benke6/2013/dengxiang/inv/gds/inv.gds

接着将在icfb打开的cadence窗口中配置stream。

在打开的窗口中选择Library Browser选择inv—>inv—>layout在Run Directory中填入新建的gds文件夹路径:/user2/benke6/2013/dengxiang/inv/gds

接着在drc目录下执行:PDRACULA回车后执行:/g ./drac_drc_metal1.rul

接着执行/f生成文件如图:

执行:./开始drc校验。

出现上图证明DRC验证结束。

Drc校验完以后打印drc的路/user2/benke6/2013/dengxiang/inv/drc。

在版图设计窗口中点击tools—>Dracula Interactive然后在菜单栏点击DRC —>Setup将打印的路径复制到Dracula Data Path中点击OK。

四结论

时代在发展,CAD越来越重要,本文只是对集成电路CAD的基本了解和使用,还有很多要学的东西,唯有不断努力才能改变世界!。