GM8283C_数据手册,RGB转LVDS,TTL转LVDS

GM8285C产品资料

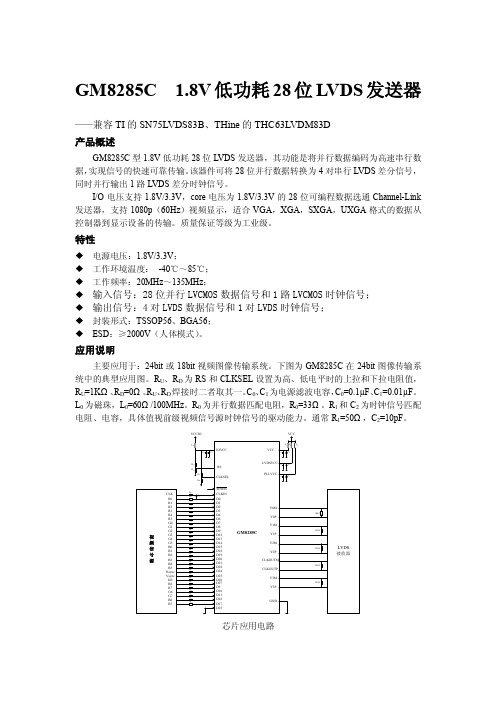

GM8285C 1.8V低功耗28位LVDS发送器——兼容TI的SN75LVDS83B、THine的THC63LVDM83D产品概述GM8285C型1.8V低功耗28位LVDS发送器,其功能是将并行数据编码为高速串行数据,实现信号的快速可靠传输。

该器件可将28位并行数据转换为4对串行LVDS差分信号,同时并行输出1路LVDS差分时钟信号。

I/O电压支持1.8V/3.3V,core电压为1.8V/3.3V的28位可编程数据选通Channel-Link 发送器,支持1080p(60Hz)视频显示,适合VGA,XGA,SXGA,UXGA格式的数据从控制器到显示设备的传输。

质量保证等级为工业级。

特性◆电源电压:1.8V/3.3V;◆工作环境温度:-40℃~85℃;◆工作频率:20MHz~135MHz;◆输入信号:28位并行LVCMOS数据信号和1路LVCMOS时钟信号;◆输出信号:4对LVDS数据信号和1对LVDS时钟信号;◆封装形式:TSSOP56、BGA56;◆ESD:≥2000V(人体模式)。

应用说明主要应用于:24bit或18bit视频图像传输系统。

下图为GM8285C在24bit图像传输系统中的典型应用图。

R U、R D为RS和CLKSEL设置为高、低电平时的上拉和下拉电阻值,R U=1KΩ、R D=0Ω。

R U、R D焊接时二者取其一。

C0、C1为电源滤波电容,C0=0.1µF、C1=0.01µF。

L0为磁珠,L0=60Ω/100MHz。

R0为并行数据匹配电阻,R0=33Ω。

R1和C2为时钟信号匹配电阻、电容,具体值视前级视频信号源时钟信号的驱动能力。

通常R1=50Ω,C2=10pF。

芯片应用电路。

转接口IC大全-RGB互转LVDS-LVDS或RGB转MIPI-MIPI转LVDS或RGB-LVDS或RGB转EDP-HDMI转LVDS或MHL

转接IC详细介绍EDP输出NCS8801:LVDS转EDP、RGB转EDP 封装QFN562560*1600用于手机、平板、转接板、液晶驱动板、广告机、可视门铃等等控制器到显示设备上MIPI输出SDD2828:RGB转MIPI 支持1920*1200分辨率,封装QFN68用于手机、平板、转接板、控制器到显示设备上LVDS输出GM8283:TTL或RGB转LVDS 支持1366*768,封装TTSOP56用于手机、平板、转接板、控制器到显示设备上GM8285:是GM8283升级版本,在电压和分辨率改动。

ZA7783:MIPI转LVDS,MIPI转RGB, 封装是QFN64 用于手机、平板、转接板、控制器到显示设备上ICN6201:MIPI转LVDS 封装QFN48支持分辨率1920*1200用于手机、车载、转接板、平板等控制器到显示设备上LT8668:HDMI1.3/VGA/YPBPR转双路LVDS并带音频输出,支持1080P,运用到MONIT OR等显示设备上。

LT8668EX:HDMI1.4/VGA/MHL转4路的LVDS并带音频输出,支持4K*2K,运用到MONI TOR等显示设备上。

HDMI输出LT8818:RGB转HDMI/MHL BGA64 (4.5*4.5MM)用到车联网上的车载上。

移动电话,数码相机,便携式媒体播放器,掌上游戏机,和数码摄像机。

LT8612:HDMI/MHL转HDMI RGB,YUV 支持到1960*1080 ,封装LQFP-80L。

LT8612EX:HDMI/MHL转HDMI RGB,YUV支持4K*2K, LQFP-80LLT8611EX:DP转HDMI/DVI,支持分辨率1080P,封装QFN48 ,运用电脑主板、显卡,DP to HDMI/DVI电缆适配器,1对1DP中继器LT8618:HDMI1.3发射芯片,TTL/RGB转HDMI,支持1080P 60Hz,封装64 pin QFN或80-pin LQFP主要用于HD-pylayer, PMP, STB, Mobile-phone等HDMI输出设备。

GM8283C

TXCLKOUT+/TXCLKOUT- 正/反相输出 LVDS 时钟信号,满足 EIA/TIA-644 标准。

2

成都国腾电子技术股份有限公司

28 位可编程数据选通发送器

数据手册

GM8283C

引脚符号

PWR DWN VCC GND

PLLVCC PLLGND LVDSVCC LVDSGND

表 2 (续)

5 参数指标

5.1 极限工作条件

a)电源电压(VCC)……………………………… -0.5V~4V b) 输入电压 (VI) ……………………………… -0.5V~VCC +0.5V c) 输出电压 (VO) ………………………………-0.5V~VCC +0.5V d) 贮存温度(Th)(10s)………………………………260℃ e) 工作温度(Tstg)………………………………-65℃~150℃

5.2 推荐工作条件

表 3 推荐工作条件

符号

参数

最小

典型

最大

VCC

电源电压

3.0

3.3

3.6

VCCPP

电源电压噪声幅值

-

-

100

tCIP

输入时钟周期

11.1

-

100.0

tCIT

输入时钟转换时间

1.0

3.0

6.0

tCIH

输入时钟高电平时间

0.35tCIP

0.50tCIP

0.65tCIP

tCIL

输入时钟低电平时间

TXOUT1

TXIN9 -1

TXIN8 -1

TXIN 18

TXIN 15

TXIN 14

TXIN 13

TTL-LVDS转换板

TOPRO LVDS-R6B接收板使用说明TOPRO LVDS-R6B(Low Voltage Differential Signal低压差分信号)接收板是北京拓普华科电子显示技术有限责任公司基于THINE公司的THC63LVDF64A LVDS接收芯片的基础上开发的LVDS接收板,用于将LCD控制器输出的LVDS信号转换成TTL液晶显示信号。

具有传输距离远、幅射小,抗干扰性强、EMI特性好等特点。

其主要用途如下:1.将主板的LVDS信号转换成TTL信号,驱动TTL接口的液晶屏;2.与发送板配合使用,发送板将主板的TTL信号转换成LVDS信号,接收板再将LVDS 信号转换成TTL液晶显示信号输出,驱动液晶显示屏,从而实现主板和液晶屏之间的长距离驱动,或降低系统的EMI。

一、接收板外形二、接收板布局:J1:LVDS输入接口 J2:TTL输入接口三、接口定义:1.LVDS输入端J1:接头型号:DF14-20S-1.25C(HIROSE)引脚符号功能1 GND 电源地2 GND 电源地3 NC 无电气连接4 NC 无电气连接5 GND 电源地6 CK+ 时钟信号7 CK- 时钟信号8 GND 电源地9 D2+ 显示数据10 D2- 显示数据11 GND 电源地12 D1+ 显示数据13 D1- 显示数据14 GND 电源地15 D0+ 显示数据16 D0- 显示数据17 GND 电源地18 GND 电源地19 Vcc 逻辑电源20 Vcc 逻辑电源2.TTL输入端J2:接头型号:44PIN2.0插座引脚符号功能1 NC 无电气连接2 NC 无电气连接3 GND 电源地4 GND 电源地5 Vcc 逻辑电源6 Vcc 逻辑电源7 NC 无电气连接8 GND 电源地9 NC 无电气连接10 NC 无电气连接11 B0 蓝色显示数据第0位12 B1 蓝色显示数据第1位13 B2 蓝色显示数据第2位14 B3 蓝色显示数据第3位15 B4 蓝色显示数据第4位16 B5 蓝色显示数据第5位17 NC 无电气连接18 NC 无电气连接19 G0 绿色显示数据第0位20 G1 绿色显示数据第1位21 G2 绿色显示数据第2位22 G3 绿色显示数据第3位23 G4 绿色显示数据第4位24 G5 绿色显示数据第5位25 NC 无电气连接26 NC 无电气连接27 R0 红色显示数据第0位28 B1 红色显示数据第1位29 B2 红色显示数据第2位30 B3 红色显示数据第3位31 B4 红色显示数据第4位32 B5 红色显示数据第5位33 NC 无电气连接34 NC 无电气连接35 CK 点时钟36 VS 场频37 DE 使能信号38 HS 行频39 NC 无电气连接40 NC 无电气连接41 NC 无电气连接42 NC 无电气连接43 NC 无电气连接44 NC 无电气连接四、适用范围:本LVDS接收板适用于18位(RGB各6位)的TTL输出;分辨率可支持:640X480、800X600、1024X768TTL输出端与液晶屏之间的距离建议不要超过50CM。

液晶显示器LVDS接口液晶面板RGB信号解析

图1 单路6bit LVDS接口液晶面板信号 对于双路6bit LVDS接口(见图2),需要6对差分数据线,其中,奇路3对,即RX00-和RX00+,RX01- 和RX01+,RXO2-和RX02+;偶路3 对,即RXE0-习阳RXE0+,RXE1-和RXE1+,RXE2-和RXE2+。这6对差分数据线可以传输6×7bit=42hit,除奇路(OR0~OR5、OG0~OG5、 OB0 ~OB5 )和 偶 路( ER 0 ~ER 5 、EG 0 ~ EC 5、EB0 ~ EB5)占 去 36 bit , 还剩下 6bit , HS 、VS 、 DE信 号占 3b it ,还 空余 3b it(若 HS 、 VS信 号 不传 输,将空余5bit)。

图3单路8bit LVDS接口液晶面板信号 对于双路8bit LVDS接口(见图4),需要8对差分数据线,其中,奇路4对,即RX00-和RX00+,RX01-和RX01+,RX02-和RX02+,RX03和RX03+;偶路3对,即RXE0-和RXE0+,RXE1-和RXE1+,RXE2-和RXE2+,RXE3-和RXE3+。这8对差分数据线可以传输8×7bit=56bit, 除奇路(OR0~OR7、OG0~OG7、OB0~OB7)和偶路(BR0~ER7、EG0~EG7、EB0~EB7)占去48bit,还剩下8bit,HS、VS、DE信号占 3bit,还空余5bit(若HS、VS信号不传输,将空余7bit)。

对于单路6bit LVDS接口(见图1),需要3对差分数据线,即RX0-和RX0十,RX1-和RX1+,RX2-和RX2+。因每对差分数据线可以传输7bit数 据,这样,3对差分数据线可以传输3×7bit=21 bit,除R0~R5、G0~G5、B0~B5占去18bit,还剩下3bit用于传输HS(行同步)、VS(场同步)、 DE(有效数据选通)信号(若HS、VS信号不传输,将空余2bit)。

瑞星微方案RK3066维修SOP

平板电脑MID瑞星微方案RK3066主控原理与维修实例N70_HD配置:主控ARM:RK3066双核电源PMU:TPS659102 网络WIFI:USB-ZHWIFI-06 ROM:美光Flash 8GB RAM:现代256M x4=1GB 音频处理AMP:ALC3224Q LVDS上屏IC:GM8283 C、SN75LVDS83A 、DTC34LM85AM 触摸IC:GT813单片机铺助IC:方向传感:MC3230A 充电IC:HX6202 5v供电:TCS9208 核供电小IC:SY8009B 外设供电切换:TT9106HRE机型:N8O双擎。

配置:主控ARM:RK3066双核电源PMU:TPS659102 网络WIFI:RK901 ROM:美光Flash 8GB RAM:现代256M x4=1GB 音频处理AMP:ALC5631Q LVDS上屏IC:GM8283 C、SN75LVDS83A铺助IC:方向传感:MC3230A 充电IC:MP2611 5v供电:TCS9208 核供电小IC:SY8009B 外设供电切换:TT9106HRE 屏驱供电CD1561背光供电:RT9293B测试参数:是不接电池测试,用外接电源测试的。

开机故障例1:故障表现:自动开机,自动充电。

损坏器件:充电IC,型号:mp2611。

原理图:例2:故障表现:不开机。

故障分析:喇叭锡焊点呈针状,刺触到LCD显示屏铁外壳,造成喇叭输出短路。

而大电流,可能电池保护不开机。

例3 :故障表现:开机死机。

维修方法:重升级,‘下载Boot失败’。

重吹ARM,重升级通过,开机正常。

例4:故障表现:开机后显示‘启动停止’。

维修方法:软件故障,重升级。

例5:故障表现:有时能开机开机死机开机时间长无录音电量不足。

维修方法:估计分析ARM虚焊,重吹ARM,装机开机正常。

例6:故障表现:开机死机。

维修方法软件故障,重升级,OK。

例7:故障表现:不开机,接外电源,电流跳变正常,但黑屏。

液晶显示器“TTL、LVDS”输出接口概述

液晶显示器“TTL、LVDS”输出接口概述1.TTL输出接口概述TTL(Transistor Transistor Logic)即晶体管-晶体管逻辑,TTL电平信号由TTL器件产生。

TTL器件是数字集成电路之一大门类,它采用双极型工艺制造,具有高速度、低功耗和品种多等特点。

TTL接口属于并行方式传输数据之接口,采用这种接口时,不必在液晶显示器之驱动板端和液晶面板端使用专用之接口电路,而是由驱动板主控芯片输出之TTL数据信号经电缆线直接传送到液晶面板之输人接口。

由于TTL接口信号电压高、连线多、传输电缆长,因此,电路之抗干扰能力比较差,而且容易产生电磁干扰(EMI)。

在实际应用中,TTL接口电路多用来驱动小尺寸(15in以下)或低分辨率之液晶面板。

另外,在笔记本电脑中也常使用1TL接口形式。

2.TTL输出接口之分类TTL输出接口可分为以下几类:(1)单路(或单通道)6bit TTL输出接口这种接口电路中,采用单路方式传输,每个基色信号采用6bit数据(R0~R5,CO~G5,B0~B5)。

由于基色RGB数据为18bit,因此,也称18位或18bit TTL接口。

(2)双路6bit TTL输出接口这种接口电路中,采用双路方式传输,每个基色信号采用6bit数据(奇路为0RO~OR5,OG 0~OG5,OB0~OB5;偶路为BRO~ER5,EC0~EG5,EB0~EB5)。

由于基色ROB数据为36bit,因此,也称36位或36bit rrL接口。

(3)单路8bit TTL输出接口这种接口电路中,采用单路方式传输,每个基色信号采用8bit数据(R0~R7,G0~G7,B0~B7)。

由于基色RGB数据为24bit,因此,也称24位或24bit 1TL接口。

(4)双路8bit TTL输出位接口这种接口电路中,采用双路方式传输,每个基色信号采用8bit数据(奇路为OR0~OR7,OG 0~0G7,OB0~OB7;偶路为ER0~ER7,EC0~EG7,EB0~EB7),由于基色RGB数据为48bit,因此,也称48位或48bit TTL接口。

GM8285C数据手册

为低,时钟下降沿采样数据。

关断控制端,默认下拉;

为高,芯片正常输出; 为低,关断芯片,输出为高阻态。

2

成都国腾电子技术股份有限公司

1.8V 低功耗 28 位 LVDS 发送器

数据手册

GM8285C

端口符号

LVDS 端口 Y0P,Y0M Y1P,Y1M Y2P,Y2M

TSSOP56

端口序号

表 1(续)

VIOVCC=VPLLVCC=VLVDSVCC=VCC=1.62V , VRS=VIOVCC和GND,RL=100Ω

所有电源电压为 3.6V,VO=0V,RL=100Ω 所有电源电压为 3.6V,V SHTDN =0V,VO=0V

VIOVCC=1.98V或 3.6V,VPLLVCC=VLVDSVCC=VCC=3.3V,

IIN

VIN=VIOVCC或GND

-25

25

μA

输入钳位电压

VCL ICL=-18mA,VIOVCC=3.6V,VPLLVCC=VLVDSVCC=VCC=3.3V

-

-1.5

V

差分输出电压 VOD

共模输出电压 VOS

旧版

当前版本

文档页数

文档页数

10

11

QQ2245658446

当前版本时间:2013 年 07 月

主题(和旧版本相比的主要变化) 增加 BGA56 封装

如果您有技术、交付或价格方面的任何问题,请联系成都国腾电子技术股份有限公司的相关办公室或 当地的代理商,或访问官方网站: 谢谢!

B3

LVCMOS 输入

功能说明

LVCMOS 输入信号,默认下拉; 18bit 应用时,未使用输入端,应下拉

到 GND。

液晶显示器TTL及LVDS电路

液晶显示器“TTL、LVDS”输出接口概述1.TTL输出接口概述TTL(Transistor Transistor Logic)即晶体管-晶体管逻辑,TTL 电平信号由TTL器件产生。

TTL器件是数字集成电路的一大门类,它采用双极型工艺制造,具有高速度、低功耗和品种多等特点。

TTL接口属于并行方式传输数据的接口,采用这种接口时,不必在液晶显示器的驱动板端和液晶面板端使用专用的接口电路,而是由驱动板主控芯片输出的TTL数据信号经电缆线直接传送到液晶面板的输人接口。

由于TTL接口信号电压高、连线多、传输电缆长,因此,电路的抗干扰能力比较差,而且容易产生电磁干扰(EMI)。

在实际应用中,TTL接口电路多用来驱动小尺寸(15in以下)或低分辨率的液晶面板。

另外,在笔记本电脑中也常使用1TL接口形式。

2.TTL输出接口的分类TTL输出接口可分为以下几类:(1)单路(或单通道)6bit TTL输出接口这种接口电路中,采用单路方式传输,每个基色信号采用6bit数据(R0~R5,CO~G5,B0~B5)。

由于基色RGB数据为18bit,因此,也称18位或18bit TTL接口。

(2)双路6bit TTL输出接口这种接口电路中,采用双路方式传输,每个基色信号采用6bit数据(奇路为0RO~OR5,OG0~OG5,OB0~OB5;偶路为BRO~ER5,EC0~EG5,EB0~EB5)。

由于基色ROB数据为36bit,因此,也称36位或36bit rrL接口。

(3)单路8bit TTL输出接口这种接口电路中,采用单路方式传输,每个基色信号采用8bit数据(R0~R7,G0~G7,B0~B7)。

由于基色RGB数据为24bit,因此,也称24位或24bit 1TL接口。

(4)双路8bit TTL输出位接口这种接口电路中,采用双路方式传输,每个基色信号采用8bit数据(奇路为OR0~OR7,OG0~0G7,OB0~OB7;偶路为ER0~ER7,EC0~EG7,EB0~EB7),由于基色RGB数据为48bit,因此,也称48位或48bit TTL接口。

液晶屏LVDS,TTL,RSDS接口样式的区别方法

液晶屏LVDS,TTL,RSDS接口样式的区别方法分类:嵌入式很多初学者对于如何区分屏的接口类型很是头疼,是LVDS屏,TTL屏还是RSDS 屏?总是很难搞清出。

如何快速识别出液晶屏的接口类型则需要一些经验的,下面从屏的屏线接口的样式来对接口类型做出分类的介绍,帮助大家快速识别屏的接口类型。

以下方法是个人认识,不足之处请大家谅解。

(1) TTL屏接口样式:D6T(单6位TTL):31扣针,41扣针。

对应屏的尺寸主要为笔记本液晶屏(8寸,10寸,11寸,12寸),还有部分台式机屏15寸为41扣针接口。

S6T(双6位TTL):30+45针软排线,60扣针,70扣针,80扣针。

主要为台式机的14寸,15寸液晶屏。

D8T(单8位TTL):很少见S8T(双8位TTL):有,很少见80扣针(14寸,15寸)2)LVDS屏接口样式:D6L(单6位LVDS):14插针,20插针,14片插,30片插(屏显基板100欧姆电阻的数量为4个)主要为笔记本液晶屏(12寸,13寸,14寸,15寸)D8L(单8位LVDS):20插针(5个100欧姆)(15寸)S6L(双6位LVDS):20插针,30插针,30片插(8个100欧姆)(14寸,15寸,17寸)S8L(双8位LVDS):30插针,30片插(10个100欧姆电阻)(17寸,18寸,19寸,20寸,21寸)(3)RSDS屏接口样式:50排线,双40排线,30+50排线。

主要为台式机(15寸,17寸)液晶屏。

常规LVDS接口液晶屏定义20PIN单6定义:1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11:R2- 12:R2+ 13:地 14:CLK- 15:CLK+ 16空 17空 18空 19 空 20空每组信号线之间电阻为(数字表120欧左右)20PIN双6定义:1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:R1- 8:R1+ 9:R2- 10:R2+ 11:CLK- 12:CLK+ 13:RO1- 14:RO1+ 15:RO2- 16:RO2+ 17:RO3- 18:RO3+ 19:CLK1- 20:CLK1+每组信号线之间电阻为(数字表120欧左右)20PIN单8定义:1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11:R2- 12:R2+ 13:地 14:CLK- 15:CLK+ 16:R3- 17:R3+每组信号线之间电阻为(数字表120欧左右)30PIN单6定义:1:空2:电源3:电源 4:空 5:空 6:空 7:空 8:R0- 9:R0+ 10:地 11:R1- 12:R1+ 13:地 14:R2- 15:R2+ 16:地 17:CLK- 18:CLK+ 19:地 20:空- 21:空 22:空 23:空 24:空 25:空 26:空 27:空 28空 29空 30空每组信号线之间电阻为(数字表120欧左右)30PIN单8定义:1:空2:电源3:电源 4:空 5:空 6:空 7:空 8:R0- 9:R0+ 10:地 11:R1- 12:R1+ 13:地 14:R2- 15:R2+ 16:地 17:CLK- 18:CLK+ 19:地 20:R3- 21:R3+ 22:地 23:空 24:空 25:空 26:空 27:空 28空 29空 30空每组信号线之间电阻为(数字表120欧左右)30PIN双6定义:1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11:R2- 12:R2+ 13:地 14:CLK- 15:CLK+ 16:地 17:RS0- 18:RS0+ 19:地 20:RS1- 21:RS1+ 22:地 23:RS2- 24:RS2+ 25:地 26:CLK2- 27:CLK2+每组信号线之间电阻为(数字表120欧左右)30PIN双8定义:1:电源2:电源3:电源 4:空 5:空 6:空 7:地 8:R0- 9:R0+ 10:R1- 11:R1+ 12:R2- 13:R2+ 14:地 15:CLK- 16:CLK+ 17:地 18:R3- 19:R3+ 20:RB0-21:RB0+ 22:RB1- 23:RB1+ 24:地 25:RB2- 26:RB2+ 27:CLK2- 28:CLK2+ 29:RB3- 30:RB3+每组信号线之间电阻为(数字表120欧左右)一般14PIN、20PIN、30PIN为LVDS接口。

GM8283C_数据手册,RGB转LVDS,TTL转LVDS

5.2 推荐工作条件

表 3 推荐工作条件

符号

参数

最小

典型

最大

VCC

电源电压

3.0

3.3

3.6

VCCPP

电源电压噪声幅值

-

-

100

tCIP

输入时钟周期

11.1

-

100.0

tCIT

输入时钟转换时间

1.0

3.0

6.0

tCIH

输入时钟高电平时间

0.35tCIP

0.50tCIP

0.65tCIP

tCIL

输入时钟低电平时间

TXCLKOUT+/TXCLKOUT- 正/反相输出 LVDS 时钟信号,满足 EIA/TIA-644 标准。

香港众鑫微电子有限公司

金R 15013505758 Q10862894

2

28 位可编程数据选通发送器

数据手册

GM8283C

引脚符号

PWR DWN VCC GND

PLLVCC PLLGND LVDSVCC LVDSGND

5 参数指标

5.1 极限工作条件

a)电源电压(VCC)……………………………… -0.5V~4V b) 输入电压 (VI) ……………………………… -0.5V~VCC +0.5V c) 输出电压 (VO) ………………………………-0.5V~VCC +0.5V d) 贮存温度(Th)(10s)………………………………260℃ e) 工作温度(Tstg)………………………………-65℃~150℃

2 特征

a) 电源电压:3.0V~3.6V; b) 工作温度范围:−40~85℃; c) 锁相环内部全集成,无需外部元件; d) 输入时钟频率:10MHz~90MHz; e) 总数据率:2520Mbps; f) 通道压缩比:28:4; g) 输入信号:28 bits LVTTL/LVCMOS 数据和 1 路 LVTTL/LVCMOS 时钟信号; h) 输出信号:满足 EIA/TIA-644 标准的 4 路 LVDS 数据流和 1 路 LVDS 时钟信号; i) 封装形式:TSSOP56; j) 器件等级:工业级; k) 适合 VGA、SVGA、XGA、SXGA(dual pixel)、UXGA(dual pixel)等格式的数据从

ZA7783DATASHEET,MIPI转LVDS,MIPI转RGB888,RGB转LVDS

ZA7783 DATASHEET ZA7783 Display Interface ConverterDatasheetVersion 0.7Revision HistoryVer. Date Author Content0.5 2013-5-14 Dai Jin 1. Initial release0.6 2013-9-29 Jiang Bo 1. Add typical application circuit2. Add package information3. Add functional block diagram0.7 2014-2-12 Jiang Bo 1. Change LVDS_ATO to DVDD18ZA7783 DATASHEETTable of Contents1. OVERVIEW (3)2. TARGET APPLICATIONS (3)3. FEATURE DESCRIPTION (3)4. FUNCTIONAL BLOCK DIAGRAM (5)5. PIN CONFIGURATION (6)6. TYPICAL APPLICATION CIRCUIT (9)7. PACKAGE INFORMATION (10)ZA7783 DATASHEET 1. OverviewZA7783 is a bridge chip which supports three kinds of display interfaces:●MIPI DSI RX Interface (1 Clock Lane + 4 Data Lanes)●LVDS TX Interface (1 Clock Lane + 4 Data Lanes)●MIPI DPI TX/RX Interface (PCLK + RGB888 + VSYNC + HSYNC +DATAEN)The chip bridges these display interfaces in three working modes:●MODE1: MIPI DSI RX => LVDS TX●MODE2: MIPI DSI RX => DPI TX●MODE3: DPI RX => LVDS TXBesides, there is also an I2C control interface (XCLK + I2C_SCL + I2C_SDA) for the host chip (AP or BB) to access ZA7783’s software registers.Analog IPs of ZA7783 are supplied by 3.3V voltage (typical). For Digital IOs, the host interface (XCLK + I2C_SCL + I2C_SDA) is supplied by DVDD18 (PIN32), while the DPI interface (PCLK + RGB888 + VSYNC + HSYNC + DATAEN) is supplied by DVDD33 (PIN45 and PIN59). Thus, ZA7783 is able to bridge AP or BB with 1.8V IO to RGB Panel with 3.3V IO. Besides, an embedded LDO converts 3.3V to 1.2V to supply the chip’s internal digital logic. In addition, an embedded POR implements a power on reset to the whole chip.2. Target ApplicationsTablet PC3. Feature DescriptionMIPI DSI RX Interface●Compliant to MIPI DSI V1.01 and MIPI D-PHY V1.00● 1 Clock Lane + 4 Data Lanes●Data rate up to 600Mbps per data lane (300MHz high-speed clock on clock lane)● 2.4Gbps bandwidth on four data lanes in total, giving a display resolution up to1366x768 24bpp @ 60fps●Only support MIPI DSI Video Mode (Non-Burst Mode with Sync Pulses) and all lanesare unidirectional from the host chip to the bridge chipZA7783 DATASHEET ●Only support using all of the four data lanes, in other words, using part of them is notsupported●Support multiple packets within a single high-speed transmission●Ignore received virtual channel field●Only the following packet data types are supported:6'h01=Sync Event, V Sync Start (Short)6'h11=Sync Event, V Sync End (Short)6'h21=Sync Event, H Sync Start (Short)6'h31=Sync Event, H Sync End (Short)6'h08=End of Transimission packet (EoTp) (Short)6'h09=Null Packet, no data (Long)6'h19=Blanking Packet, no data (Long)6'h2E=Loosely Packed Pixel Stream, 18-bit RGB, 6-6-6 Format (Long)6'h3E=Packed Pixel Stream, 24-bit RGB, 8-8-8 Format (Long) The other packet data types cannot be handled and must not be sent to ZA7783!●Ignore received ecc field●Ignore received checksum field●RGB565 Packed Pixel Stream and RGB666 Packed Pixel Stream are not supported●For a data lane, the connection of Dp/Dn can be exchanged●The order of the four data lanes can be configured●Dither function for converting RGB888 to RGB666LVDS TX Interface●Compliant to LVDS Spec● 1 Clock Lane + 4 Data Lanes●Support RGB888 and RGB666RGB888: 1 Clock Lane + 4 Data LanesRGB666: 1 Clock Lane + 3 Data Lanes●Support NS Mode and JEIDA Mode●The polarity of VSYNC/HSYNC/DATAEN can be configured●For a data lane, the connection of Dp/Dn can be exchanged●The order of the four data lanes can be configured●Dither function for converting RGB888 to RGB666DPI TX/RX Interface●PCLK + RGB888 + VSYNC + HSYNC + DATAEN●The edge of PCLK can be configured●The polarity of VSYNC/HSYNC/DATAEN can be configuredI2C Interface●An external clock XCLK should be provided (e.g. 26MHz)●Up to 400Kbps●I2C Slave ID is 0x37ZA7783 DATASHEET 4. Functional Block DiagramZA7783 DATASHEET5. Pin ConfigurationR4R5R6R7DVDD12AVDD33MIPI_CLKPMIPI_CLKN MIPI_D0P MIPI_D0NMIPI_D1PMIPI_D1N MIPI_D2P MIPI_D2N MIPI_D3PMIPI_D3N M I P I _A V D D 33M I P I _R E X TM I P I _B G V D D 33L V D S _A V D D 33L V D S _D 0PL V D S _D 0NL V D S _D 1PL V D S _D 1NL V D S _C L K PL V D S _C L K NL V D S _D 2PL V D S _D 2NL V D S _D 3PL V D S _D 3NL V D S _P L L V D D 33D V D D 18I2C_SDAI2C_SCLXCLK B0B1B2B3DVSSB4B5B6B7DVDD33DATAEN HSYNCVSYNC G 0G 1G 2G 3D V S SG 4G 5G 6G 7P C L KD V D D 33R 0R 1R 2R 3D V S SNo. Name Description1 R42 R53 R64 R7 DPI R[7:4]5DVDD12LDO 1.2V Output (connected to 1uF ceramic cap) Digital Core 1.2V Power Supply 6 AVDD33 LDO 3.3V Power Supply7 MIPI_CLKPZA7783 DATASHEET9 MIPI_D0P 10 MIPI_D0N 11 MIPI_D1P 12 MIPI_D1N 13 MIPI_D2P 14 MIPI_D2N 15 MIPI_D3P 16 MIPI_D3N MIPI DSI RX Data Lane 0~317 MIPI_AVDD33 MIPI PHY 3.3V Power Supply18 MIPI_REXT Tie a 24KOhm resistor (1% accuracy) to analog ground 19 MIPI_BGVDD33 MIPI PHY 3.3V BandGap Supply 20 LVDS_AVDD33 LVDS TX 3.3V Power Supply 21 LVDS_D0P 22 LVDS_D0N LVDS TX Data Lane 0 23 LVDS_D1P 24 LVDS_D1N LVDS TX Data Lane 1 25 LVDS_CLKP 26 LVDS_CLKN LVDS TX Clock Lane 27 LVDS_D2P 28 LVDS_D2N LVDS TX Data Lane 2 29 LVDS_D3P 30 LVDS_D3N LVDS TX Data Lane 331 LVDS_PLLVDD33LVDS TX 3.3V PLL Supply 32 DVDD18Digital IO 1.8V Power SupplyThis power supply is for XCLK/I2C_SCL/I2C_SDA. 33 I2C_SDA I2C Serial Data Line 34 I2C_SCL I2C Serial Clock Line 35 XCLK XCLK Input (e.g. 26MHz) 36 B0 37 B1 38 B2 39 B3 DPI B[3:0] 40 DVSS Digital Ground 41 B4 42 B5 43 B6 44 B7 DPI B[7:4]45 DVDD33 Digital IO 3.3V Power SupplyThis power supply is for DPI IF, including PCLK, R7~0, G7~0, B7~0, VSYNC, HSYNC, and DATAEN. 46 DATAEN DPI Data Enable 47 HSYNC DPI HSYNC 48 VSYNC DPI VSYNC 49 G0 50 G1 51 G2 52 G3 DPI G[3:0] 53 DVSS Digital Ground 54 G4 55 G5 DPI G[7:4]ZA7783 DATASHEET57 G758 PCLK DPI Pixel Clock59 DVDD33 Digital IO 3.3V Power SupplyThis power supply is for DPI IF, including PCLK, R7~0,G7~0, B7~0, VSYNC, HSYNC, and DATAEN.60 R061 R1DPI R[3:0]62 R263 R364 DVSS Digital GroundEP(65) AVSS Analog Ground for LDO, MIPI PHY, and LVDS TXZA7783 DATASHEET 6. Typical Application CircuitZA7783 DATASHEET 7. Package InformationZA7783 is provided in 8x8 QFN64 package, 0.4 pitch.。

2代LVDS-VGA信号转换器说明书V1.3

2代LVDS-VGA信号转换器说明书V1.3“LVDS-VGA信号转换器Ⅱ型”使⽤说明书⼀产品简介(⼀)简介1《LVDS-VGA信号转换器Ⅱ型》⽤于将输⼊信号为LVDS格式的信号,转换成VGA 格式的信号输出。

本产品基于常⽤接⼝设计,兼容市场上主流的液晶显⽰⾯板,包括LG、三星、奇美、夏普、龙腾⼴电等品牌的各类型号。

完全⽀持液晶⾯板刷新率:50 Hz/60Hz液晶⾯板。

⽀持最⾼分辨率为1920*1080*60Hz。

(对于⾼清主板⽀持⼀组LVDS信号输⼊)(⼆)主要功能本产品主要是⽤于LCD TV的⽣产和维修过程中,解决不需要LCD屏即可调试及维修各种电路主板的⼯装设备。

本产品优点:1.采⽤本设备作为调试和维修⼯装,可以避免因调试和维修各种不同规格参数的液晶⾯板匹配不同电路主板时,所需要的⼤量终端液晶⾯板。

不再需要液晶⾯板作为调试和维修⼯装材料,经济实⽤。

2.接⼊不同的线序转换板,即可实现⽀持不同分辨率的主板信号的接⼊。

便于操作⼈员的使⽤。

3.采⽤本设备作为调试和维修⼯装,可以有效避免使⽤液晶⾯板作为维修⼯装时,在调试和维修过程中,故障的主板可能输出异常的信号和电压,所导致液晶⾯板损坏的情况,具有很⾼的安全性。

本产品可将液晶电视功能主板输出的LVDS信号,转换成VGA信号,再将VGA信号送到任⼀款带有VGA接⼝的电视机或显⽰器即可进⾏调试和维修。

(三)主要参数●尺⼨:25mm×60mm×100mm●输⼊接⼝:⽀持单组LVDS差分信号,(⾼清的可以从两组中选取⼀组接⼊)两路32针、2mm间距插座;●输出接⼝:标准的DB15 VGA接⼝●电源⽀持:外置5V/500mA直流电源;●显⽰⽀持:最⾼分辨率1920*1080*60Hz●⼯作环境:温度-10℃~50℃,湿度5%~85%表1-1:“LVDS线序转换板”输⼊接⼝所兼容液晶屏接⼝对照表:⼆模块说明(⼀) LVDS-VGA信号转换器Ⅱ型1、下图为《LVDS-VGA信号转换器Ⅱ型》实物图。

液晶显示器TTL及LVDS电路

液晶显示器“TTL、LVDS”输出接口概述1.TTL输出接口概述TTL(Transistor Transistor Logic)即晶体管-晶体管逻辑,TTL 电平信号由TTL器件产生。

TTL器件是数字集成电路的一大门类,它采用双极型工艺制造,具有高速度、低功耗和品种多等特点。

TTL接口属于并行方式传输数据的接口,采用这种接口时,不必在液晶显示器的驱动板端和液晶面板端使用专用的接口电路,而是由驱动板主控芯片输出的TTL数据信号经电缆线直接传送到液晶面板的输人接口。

由于TTL接口信号电压高、连线多、传输电缆长,因此,电路的抗干扰能力比较差,而且容易产生电磁干扰(EMI)。

在实际应用中,TTL接口电路多用来驱动小尺寸(15in以下)或低分辨率的液晶面板。

另外,在笔记本电脑中也常使用1TL接口形式。

2.TTL输出接口的分类TTL输出接口可分为以下几类:(1)单路(或单通道)6bit TTL输出接口这种接口电路中,采用单路方式传输,每个基色信号采用6bit数据(R0~R5,CO~G5,B0~B5)。

由于基色RGB数据为18bit,因此,也称18位或18bit TTL接口。

(2)双路6bit TTL输出接口这种接口电路中,采用双路方式传输,每个基色信号采用6bit数据(奇路为0RO~OR5,OG0~OG5,OB0~OB5;偶路为BRO~ER5,EC0~EG5,EB0~EB5)。

由于基色ROB数据为36bit,因此,也称36位或36bit rrL接口。

(3)单路8bit TTL输出接口这种接口电路中,采用单路方式传输,每个基色信号采用8bit数据(R0~R7,G0~G7,B0~B7)。

由于基色RGB数据为24bit,因此,也称24位或24bit 1TL接口。

(4)双路8bit TTL输出位接口这种接口电路中,采用双路方式传输,每个基色信号采用8bit数据(奇路为OR0~OR7,OG0~0G7,OB0~OB7;偶路为ER0~ER7,EC0~EG7,EB0~EB7),由于基色RGB数据为48bit,因此,也称48位或48bit TTL接口。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数据手册

GM8283C

图 3 GM8283C 与“4:28 接收器”联用典型应用图 7.2 应用说明

1)输入的 28 bits 数据与参考时钟为同步关系,可选择用上升沿采样或下降沿采样, 如下图 4 所示:

a)上升沿采样(RFC 为高电平电压)

b)下降沿采样(RFC 为低电平电压) 图 4 输入并行数据与输入参考时钟关系图

ns

1.88 3.56

5.24 6.92 8.60

香港众鑫微电子有限公司

金R 15013505758 Q10862894

4

28 位可编程数据选通发送器

数据 BIT6 输出与时钟输 出的相对时间 时钟延迟时间

锁相环建立时间 关断延迟时间 输入时钟抖动

6 机械尺寸

td6

9.88

tCDD

TA=25℃,VCC=3.3V

TXOUT1+

数据输出端

18

TXIN17

数据输入端

46

TXOUT1-

数据输出端

19

TXIN18

数据输入端

47

TXOUT0+

数据输出端

20

TXIN19

数据输入端

48

TXOUT0-

数据输出端

21

GND

TX 数字地端

49

LVDSGND

LVDS 地端

22

TXIN20

数据输入端

50

TXIN27

数据输入端

23

TXIN21

5.2 推荐工作条件

表 3 推荐工作条件

符号

参数

最小

典型

最大

VCC

电源电压

3.0

3.3

3.6

VCCPP

电源电压噪声幅值

-

-

100

tCIP

输入时钟周期

11.1

-

100.0

tCIT

输入时钟转换时间

1.0

3.0

6.0

tCIH

输入时钟高电平时间

0.35tCIP

0.50tCIP

0.65tCIP

tCIL

输入时钟低电平时间

控制器到显示设备的传输。

3 封装及引脚功能说明

1)引出端排列:如图 1 所示:

图 1 GM8283C 引脚排布图

香港众鑫微电子有限公司

金R 15013505758 Q10862894

1

28 位可编程数据选通发送器

数据手册

GM8283C

2)引脚功能说明如表 1 所示。 表 1 芯片引脚功能说明

引出端号

RL=100Ω,

f=10MHz

CL≤10pF

f=90MHz

极限值

最小

最大

2.0

VCC

GND

0.8

-

-1.5

-

15

-10

-

250

450

-

35

1.125

1.375

-

35

-

-5

-

±10

-

90

-

30

-

90

单位

V V V μA μA mV mV V mV mA μA μA

mA

动态参数如表 5 所示。

特性

LVDS 差分输出上升时间 (20%~80%)

在每一时钟周期内,24 bits 的 RGB 数据和 3 bits 的控制数据分别在 4 个 LVDS 串行通 道中传输,单通道数据率最高可达 630Mbps。

本器件与 DS90CR285、DS90CR287、DS90CF383、DS90C383、DS90C385、SN65LVDS93、 SN75LVDS81、SN75LVDS83 兼容,并可与 GM8284、DS90CR286、DS90CR288、DS90CF384、 DS90CF386、SN65LVDS94、SN75LVDS82 配对使用。

当前版本时间:2012 年 2 月 主题(和旧版本相比的主要变化)

香港众鑫微电子有限公司 金R 15013505758 Q10862894

28 位可编程数据选通发送器

数据手册

GM8283C

1 概述

GM8283C 型 28 位可编程数据选通发送器主要用于视频/图像传输中的发送部分,它可将 并行输入的 28 bits LVTTL/LVCMOS 数据转换为 4 路串行 LVDS 数据流。输入时钟经内部锁相 后,同频率输出,同时转换为 LVDS 差分形式,并保持与输出串行数据流的同步关系;时钟 频率为 10MHz~90MHz。

5 参数指标

5.1 极限工作条件

a)电源电压(VCC)……………………………… -0.5V~4V b) 输入电压 (VI) ……………………………… -0.5V~VCC +0.5V c) 输出电压 (VO) ………………………………-0.5V~VCC +0.5V d) 贮存温度(Th)(10s)………………………………260℃ e) 工作温度(Tstg)………………………………-65℃~150℃

TXIN9 -1

TXIN8 -1

TXIN 18

TXIN 15

TXIN 14

TXIN 13

TXIN 12

TXIN 9

TXIN 8

TXOUT0

TXIN1 -1

TXIN0 -1

前一周期

TXIN 7

PLLVCC

PLL 电源端

7

TXIN9

数据输入端

35

PLLGND

PLL 地端

8

TXIN10

数据输入端

36

LVDSGND

LVDS 地端

9

VCC

TX 数字电源端

37

TXOUT3+

数据输出端

10

TXIN11

数据输入端

38

TXOUT3-

数据输出端

11

TXIN12

数据输入端

39

TXCLKOUT+

时钟输出端

12

数据手册

GM8283C

5.3 静态参数

静态参数如表 4 所示。

特性

符号

输入高电平电压

VIH

输入低电平电压

VIL

输入钳位电压

VCL

输入电流

IIN

差分输出电压幅度 互补态差分输出电压变化

共模输出电压幅度 互补态共模输出电压变化

输出短路电流 输出高阻态电流 关断模式电源电流 最坏情况模式

电源电流

5.4 动态参数

tr tf td0 td1 td2 td3 td4 td5

表 5 动态特性参数

条件 -40℃≤TA≤85℃,

VCC=3.3V

最小

- RL=100Ω,CL≤10pF

-

f=85MHz,RL=100Ω, CL≤10pF

-0.2 1.48

3.16

4.48

6.52

8.20

极限值 最大

单位

1.5 ns

1.5

0.2

符号

功能说明

引出端号

符号

功能说明

1

VCC

PAD 电源端

29

GND

TX 数字地端

2

TXIN5

数据输入端

30

TXIN26

数据输入端

3

TXIN6

数据输入端

31

TXCLKIN

时钟输入端

4

TXIN7

数据输入端

32

PWR DWN

关断输入端

5

GND

PAD 地端

33

PLLGND

PLL 地端

6

TXIN8

数据输入端

34

2 特征

a) 电源电压:3.0V~3.6V; b) 工作温度范围:−40~85℃; c) 锁相环内部全集成,无需外部元件; d) 输入时钟频率:10MHz~90MHz; e) 总数据率:2520Mbps; f) 通道压缩比:28:4; g) 输入信号:28 bits LVTTL/LVCMOS 数据和 1 路 LVTTL/LVCMOS 时钟信号; h) 输出信号:满足 EIA/TIA-644 标准的 4 路 LVDS 数据流和 1 路 LVDS 时钟信号; i) 封装形式:TSSOP56; j) 器件等级:工业级; k) 适合 VGA、SVGA、XGA、SXGA(dual pixel)、UXGA(dual pixel)等格式的数据从

VOD △VOD VOS △VOS IOS IOZ ICCZ

ICCW

表 4 静态特性参数

条件 -40℃≤TA≤85℃,VCC=3.3V

ICL=-18mA VIN=0.4V,2.5V或VCC

VIN=GND

RL=100Ω

VO=0V, RL=100Ω

PWR DWN =0V,VO=0V或VCC

PWR DWN =0V, 输出为三态

LVDS 差分输出下降时间 (80%~20%)

数据 BIT0 输出相对时钟 输出延迟时间

数据 BIT1 输出与时钟输 出的相对时间

数据 BIT2 输出与时钟输 出的相对时间

数据 BIT3 输出与时钟输 出的相对时间

数据 BIT4 输出与时钟输 出的相对时间

数据 BIT5 输出与时钟输 出的相对时间

符号

TXCLKOUT+/TXCLKOUT- 正/反相输出 LVDS 时钟信号,满足 EIA/TIA-644 标准。

香港众鑫微电子有限公司

金R 15013505758 Q10862894

2

28 位可编程数据选通发送器

数据手册

GM8283C

引脚符号

PWR DWN VCC GND