Task parallel skeletons for irregularly structured problems

samples_for_parallel_programming -回复

samples_for_parallel_programming -回复什么是并行编程?并行编程是一种编程方法,用于同时运行多个计算任务以提高程序的执行速度和性能。

它使得程序能够有效地利用多个处理器、内核或计算资源,以在同一时间内完成多个任务。

为什么需要并行编程?随着计算机硬件的发展,一台计算机不再只有单个处理器或核心。

现代计算机往往具有多个处理器或核心,这为程序的并行执行提供了机会。

并行编程可以将任务分解为多个子任务,并使它们在不同的处理器或核心上同时运行,从而提高程序的性能。

什么是并行计算?并行计算是指在多个处理器或核心上同时执行计算任务。

这种计算方式可以加速任务的完成,提高计算性能。

并行计算可以采用多种方法,例如数据并行、任务并行和流水线并行等。

数据并行是指将数据分成多个部分,然后将这些数据部分分配给不同的处理器或核心进行计算。

每个处理器或核心独立地处理自己的数据部分,最后将结果合并。

这种方式适用于需要对大量数据进行计算的任务。

任务并行是指将计算任务分成多个子任务,并将这些子任务分配给不同的处理器或核心进行执行。

每个处理器或核心独立地执行自己的子任务,最后将结果合并。

这种方式适用于需要同时执行多个独立任务的情况。

流水线并行是指将计算任务分成多个阶段,并将每个阶段分配给不同的处理器或核心进行处理。

每个处理器或核心按照一定的顺序执行自己的阶段,然后将结果传递给下一个处理器或核心。

这种方式适用于需要按照一定的顺序进行计算的任务。

并行编程的优势是什么?并行编程的优势在于提高程序的执行速度和性能。

通过将任务并行化,程序能够更有效地利用计算机的硬件资源,从而加速程序的执行。

并行编程还可以解决一些计算问题,如大规模数据处理、复杂模拟和高性能计算等。

并行编程也可以提高程序的可扩展性和灵活性。

随着计算机硬件的发展,我们可以通过增加处理器或核心的数量来提高计算性能。

通过并行编程,程序可以利用这些额外的处理器或核心,从而实现更好的可扩展性。

并行计算 期末考试复习背诵要点

复习要点1、Parallel computing并行计算,sequential computing串行计算,instruction指令,multiple多数据,communication通信,exclusive互斥,concurrent 并发,recursive递归,data数据,exploratory探索,speculative投机,block cyclic循环块,randomized block随机块,distribution分配,graph partitioning 图划分,speedup加速比,efficiency效率,cost费用,Amdahl’s law,architecture构架,fundimental functions基本函数,synchronization同步,matrix mulitiplication矩阵乘,matrix transposition 矩阵转置,bitonci sorting双调排序,odd-even sorting奇偶排序,Shortest path,minimum spanning tree,connected components,maximal independent set,2、SMP(对称多处理机连接)MPP (Massive Parallel Processors 大规模并行)Cluster of Workstation(工作站机群)Parallelism(并行化), pipelining(流水线技术), Network topology(网络拓扑结构), diameter of a network(网络直径), bisection width(对分宽度), data decomposition(数据分解), task dependency graphs(任务依赖图), granularity(粒度), concurrency(并发), process(进程), processor(处理器), linear array(线性阵列), mesh(格网), hypercube(超立方体), reduction(规约), prefix-sum(前缀和), gather(收集), scatter(散发), threads(线程), mutual exclusion(互斥), shared address space(共享地址空间), synchronization(同步), the degree of concurrency(并发度), Dual of a communication operation(通信操作的对偶操作)3、并行计算与串行计算在算法设计主要不同点:(1)具有强大的处理器互连关系(2)并行计算依赖并行计算模型上的,如共享内存,共享地址空间或消息传递。

并行程序设计导论第四章课后题答案(2024)

2024/1/29

1

目录

2024/1/29

• 课后题概述与解题思路 • 并行计算基本概念回顾 • 数据并行和任务并行编程技巧 • 同步与通信机制在并行程序中的应用 • 性能评价与调试方法分享 • 实例分析:典型课后题解答过程展示

2

01 课后题概述与解题思路

2024/1/29

并行化设计

将程序中的可并行部分进行并行处理,利用多核CPU或分布式系统的 计算能力提高程序性能。

数据结构优化

根据问题的特点选择合适的数据结构,以减少内存占用和提高数据访 问效率。

代码优化

通过编译器优化选项、内联函数、减少函数调用等手段提高代码执行 效率。

22

06 实例分析:典型课后题解 答过程展示

并行性能优化

通过分析并行程序的性能瓶颈,采用合适的优化策略,如减少通信 开销、提高缓存利用率等,提高并行程序的执行效率。

14

04 同步与通信机制在并行程 序中的应用

2024/1/29

15

同步机制原理及作用

2024/1/29

同步机制原理

通过设定同步点或同步操作,确保并 行程序中的各个进程或线程在关键点 上达到一致状态,避免数据竞争和结 果不确定性。

重点复习并行程序设计的基本概念、原理和方法,理解并掌握相关术语和定义。通过对比和分析选项,找出 正确答案。

简答题

在理解基本概念的基础上,结合实际应用场景和问题背景,进行深入分析和思考。注意答案的条理性和逻辑 性,尽量用简洁明了的语言进行表述。

编程题

首先明确题目要求和目标,设计合理的算法和数据结构。在编写代码时,注意并行化策略的选择和实现,以 及同步和通信机制的处理。最后对程序进行测试和调试,确保正确性和性能。

诺瓦科技无线LED控制卡LED多媒体播放器TB6详细参数说明书

Taurus SeriesMultimedia PlayersTB6Specifications Doc u ment V ersion:V1.3.2Doc u ment Number:NS120100361Copyright © 2018 Xi'an NovaStar Tech Co., Ltd. All Rights Reserved.No part of this document may be copied, reproduced, extracted or transmitted in any form or by any means without the prior written consent of Xi’an NovaStar Tech Co., Ltd.Trademarkis a trademark of Xi’an NovaStar Tech Co., Ltd.Statementwww.novastar.techi Table of ContentsTable of ContentsYou are welcome to use the product of Xi’an NovaStar Tech Co., Ltd. (hereinafter referred to asNovaStar). This document is intended to help you understand and use the product. For accuracy and reliability, NovaStar may make improvements and/or changes to this document at any time and without notice. If you experience any problems in use or have any suggestions, please contact us via contact info given in document. We will do our best to solve any issues, as well as evaluate and implement any suggestions.Table of Contents (ii)1 Overview (1)1.1 Introduction (1)1.2 Application (1)2 Features (3)2.1 Synchronization mechanism for multi-screen playing (3)2.2 Powerful Processing Capability (3)2.3 Omnidirectional Control Plan (3)2.4 Synchronous and Asynchronous Dual-Mode (4)2.5 Dual-Wi-Fi Mode .......................................................................................................................................... 42.5.1 Wi-Fi AP Mode (5)2.5.2 Wi-Fi Sta Mode (5)2.5.3 Wi-Fi AP+Sta Mode (5)2.6 Redundant Backup (6)3 Hardware Structure (7)3.1 Appearance (7)3.1.1 Front Panel (7)3.1.2 Rear Panel (8)3.2 Dimensions (9)4 Software Structure (10)4.1 System Software ........................................................................................................................................104.2 Related Configuration Software .................................................................................................................105 Product Specifications ................................................................................................................ 116 Audio and Video Decoder Specifications (13)6.1 Image .........................................................................................................................................................136.1.1 Decoder (13)6.1.2 Encoder (13)6.2 Audio ..........................................................................................................................................................146.2.1 Decoder (14)6.2.2 Encoder (14)www.novastar.tech ii Table of Contents6.3 Video ..........................................................................................................................................................156.3.1 Decoder (15)6.3.2 Encoder ..................................................................................................................................................16iii1 Overview1 Overview 1.1 IntroductionTaurus series products are NovaStar's second generation of multimedia playersdedicated to small and medium-sized full-color LED displays.TB6 of the Taurus series products (hereinafter referred to as “TB6”) feature followingadvantages, better satisfying users’ requirements:●Loading capacity up to 1,300,000 pixels●Synchronization mechanism for multi-screen playing●Powerful processing capability●Omnidirectional control plan●Synchronous and asynchronous dual-mode●Dual-Wi-Fi mode ●Redundant backup Note:If the user has a high demand on synchronization, the time synchronization module isrecommended. For details, please consult our technical staff.In addition to solution publishing and screen control via PC, mobile phones and LAN,the omnidirectional control plan also supports remote centralized publishing andmonitoring.1.2 ApplicationTaurus series products can be widely used in LED commercial display field, such asbar screen, chain store screen, advertising machine, mirror screen, retail store screen,door head screen, on board screen and the screen requiring no PC.Classification of Taurus’ application cases is shown in Table 1-1. Table1 Overview2 Features 2.1 Synchronization mechanism for multi-screen playingThe TB6 support switching on/off function of synchronous display.When synchronous display is enabled, the same content can be played on differentdisplays synchronously if the time of different TB6 units are synchronous with oneanother and the same solution is being played.2.2 Powerful Processing CapabilityThe TB6 features powerful hardware processing capability:● 1.5 GHz eight-core processor●Support for H.265 4K high-definition video hardware decoding playback●Support for 1080P video hardware decoding● 2 GB operating memory●8 GB on-board internal storage space with 4 GB available for users2.3 Omnidirectional Control PlanCO.,LTD.●More efficient: Use the cloud service mode to process services through a uniform platform. For example, VNNOX is used to edit and publish solutions, and NovaiCare is used to centrally monitor display status.● More reliable: Ensure the reliability based on active and standby disaster recovery mechanism and data backup mechanism of the server.● More safe: Ensure the system safety through channel encryption, data fingerprint and permission management.● Easier to use: VNNOX and NovaiCare can be accessed through Web. As long as there is internet, operation can be performed anytime and anywhere. ●More effective: This mode is more suitable for the commercial mode of advertising industry and digital signage industry, and makes information spreading more effective.2.4 Synchronous and Asynchronous Dual-ModeThe TB6 supports synchronous and asynchronous dual-mode, allowing more application cases and being user-friendly.When internal video source is applied, the TB6 is in asynchronous mode; when HDMI-input video source is used, the TB6 is in synchronous mode. Content can be scaled and displayed to fit the screen size automatically in synchronous mode. Users can manually and timely switch between synchronous and asynchronous modes, as well as set HDMI priority.2.5 Dual-Wi-Fi ModeThe TB6 have permanent Wi-Fi AP and support the Wi-Fi Sta mode, carrying advantages as shown below:●Completely cover Wi-Fi connection scene. The TB6 can be connected to throughself-carried Wi-Fi AP or the external router.●Completely cover client terminals. Mobile phone, Pad and PC can be used to login TB6 through wireless network.●Require no wiring. Display management can be managed at any time, havingimprovements in efficiency.TB6’s Wi-Fi AP signal strength is related to the transmit distance and environment.Users can change the Wi-Fi antenna as required.2.5.1 Wi-Fi AP ModeUsers connect the Wi-Fi AP of a TB6 to directly access the TB6. The SSID is “AP +the last 8 digits of the SN”, for example, “AP10000033”, and the default password “12345678”.Configure an external router for a TB6 and users can access the TB6 by connectingthe external router. If an external router is configured for multiple TB6 units, a LAN canbe created. Users can access any of the TB6 via the LAN.is2.5.2 Wi-Fi Sta Mode2.5.3 Wi-Fi AP+Sta ModeIn Wi-Fi AP+ Sta connection mode, users can either directly access the TB6 oraccess internet through bridging connection. Upon the cluster solution, VNNOX andNovaiCare can realize remote solution publishing and remote monitoring respectivelythrough the Internet.TB6 Specifications 2 Features2.6Redundant BackupTB6 support network redundant backup and Ethernet port redundant backup.●Network redundant backup: The TB6 automatically selects internet connectionmode among wired network or Wi-Fi Sta network according to the priority.●Ethernet port redundant backup: The TB6 enhances connection reliabilitythrough active and standby redundant mechanism for the Ethernet port used toconnect with the receiving card.Hardware Structure3 Hardware Structure 3.1 AppearancePanelHardware StructureNote: All product pictures shown in this document are for illustration purpose only. Actual product may vary.Table 3-1 Description of TB6 front panelFigure 3-2 Rear panel of the TB6Note: All product pictures shown in this document are for illustration purpose only. Actual product may vary.Table 3-2 Description of TB6 rear panelHardware StructureUnit: mm4 Software Structure4 Software Structure4.1 System Software●Android operating system software●Android terminal application software●FPGA programNote: The third-party applications are not supported.4.2 Related Configuration SoftwareT5 Product Specifications 5 Product Specifications5 Product SpecificationsAntennaTECH NOVASTARXI'ANTaurus Series Multimedia Players TB6 Specifications6 Audio and Video Decoder Specifications6Specifications6.1 Image6.1.1 DecoderCO.,LTD.6.2 AudioH.264.。

NVIDIA 动态并行ISM文档说明书

Introduction to Dynamic Parallelism Stephen JonesNVIDIA CorporationImproving ProgrammabilityDynamic Parallelism Occupancy Simplify CPU/GPU Divide Library Calls from Kernels Batching to Help Fill GPU Dynamic Load Balancing Data-Dependent ExecutionRecursive Parallel AlgorithmsWhat is Dynamic Parallelism?The ability to launch new grids from the GPUDynamicallySimultaneouslyIndependentlyCPU GPU CPU GPU Fermi: Only CPU can generate GPU work Kepler: GPU can generate work for itselfWhat Does It Mean?CPU GPU CPU GPU GPU as Co-ProcessorAutonomous, Dynamic ParallelismData-Dependent ParallelismComputationalPower allocated toregions of interestCUDA Today CUDA on KeplerDynamic Work GenerationInitial GridStatically assign conservativeworst-case gridDynamically assign performancewhere accuracy is requiredFixed GridCPU-Controlled Work Batching CPU programs limited by singlepoint of controlCan run at most 10s of threadsCPU is fully consumed withcontrolling launchesCPU Control Threaddgetf2 dgetf2 dgetf2CPU Control Threaddswap dswap dswap dtrsm dtrsm dtrsmdgemm dgemm dgemmCPU Control ThreadMultiple LU-Decomposition, Pre-KeplerCPU Control ThreadCPU Control ThreadBatching via Dynamic ParallelismMove top-level loops to GPURun thousands of independent tasksRelease CPU for other workCPU Control ThreadCPU Control ThreadGPU Control Threaddgetf2 dswap dtrsm dgemm GPU Control Thread dgetf2 dswap dtrsm dgemm GPU Control Threaddgetf2dswapdtrsmdgemmBatched LU-Decomposition, Kepler__device__ float buf[1024];__global__ void dynamic(float *data) {int tid = threadIdx.x; if(tid % 2)buf[tid/2] = data[tid]+data[tid+1]; __syncthreads();if(tid == 0) {launch<<< 128, 256 >>>(buf); cudaDeviceSynchronize(); }__syncthreads();cudaMemcpyAsync(data, buf, 1024); cudaDeviceSynchronize(); }Programming Model BasicsCode ExampleCUDA Runtime syntax & semantics__device__ float buf[1024];__global__ void dynamic(float *data) {int tid = threadIdx.x; if(tid % 2)buf[tid/2] = data[tid]+data[tid+1]; __syncthreads();if(tid == 0) {launch<<< 128, 256 >>>(buf); cudaDeviceSynchronize(); }__syncthreads();cudaMemcpyAsync(data, buf, 1024); cudaDeviceSynchronize(); }Code ExampleCUDA Runtime syntax & semanticsLaunch is per-thread__device__ float buf[1024];__global__ void dynamic(float *data) {int tid = threadIdx.x; if(tid % 2)buf[tid/2] = data[tid]+data[tid+1]; __syncthreads();if(tid == 0) {launch<<< 128, 256 >>>(buf); cudaDeviceSynchronize(); }__syncthreads();cudaMemcpyAsync(data, buf, 1024); cudaDeviceSynchronize(); }Code ExampleCUDA Runtime syntax & semanticsLaunch is per-threadSync includes all launches by any thread in the block__device__ float buf[1024];__global__ void dynamic(float *data) {int tid = threadIdx.x; if(tid % 2)buf[tid/2] = data[tid]+data[tid+1]; __syncthreads();if(tid == 0) {launch<<< 128, 256 >>>(buf); cudaDeviceSynchronize(); }__syncthreads();cudaMemcpyAsync(data, buf, 1024); cudaDeviceSynchronize(); }CUDA Runtime syntax & semanticsLaunch is per-threadSync includes all launches by any thread in the blockcudaDeviceSynchronize() does not imply syncthreadsCode Example__device__ float buf[1024];__global__ void dynamic(float *data) {int tid = threadIdx.x; if(tid % 2)buf[tid/2] = data[tid]+data[tid+1]; __syncthreads();if(tid == 0) {launch<<< 128, 256 >>>(buf); cudaDeviceSynchronize(); }__syncthreads();cudaMemcpyAsync(data, buf, 1024); cudaDeviceSynchronize(); }Code ExampleCUDA Runtime syntax & semanticsLaunch is per-threadSync includes all launches by any thread in the blockcudaDeviceSynchronize() does not imply syncthreadsAsynchronous launches only__device__ float buf[1024];__global__ void dynamic(float *data) {int tid = threadIdx.x; if(tid % 2)buf[tid/2] = data[tid]+data[tid+1]; __syncthreads();if(tid == 0) {launch<<< 128, 256 >>>(buf); cudaDeviceSynchronize(); }__syncthreads();cudaMemcpyAsync(data, buf, 1024); cudaDeviceSynchronize(); }Code ExampleCUDA Runtime syntax & semanticsLaunch is per-threadSync includes all launches by any thread in the blockcudaDeviceSynchronize() does not imply syncthreadsAsynchronous launches only(note bug in program, here!)__global__ void libraryCall(float *a,float *b, float *c) {// All threads generate datacreateData(a, b);__syncthreads();// Only one thread calls library if(threadIdx.x == 0) {cublasDgemm(a, b, c);cudaDeviceSynchronize();}// All threads wait for dtrsm__syncthreads();// Now continueconsumeData(c);} CPU launcheskernelPer-block datagenerationCall of 3rd partylibrary3rd party libraryexecutes launchParallel useof resultSimple example: QuicksortTypical divide-and-conquer algorithmRecursively partition-and-sort dataEntirely data-dependent executionNotoriously hard to do efficiently on Fermi3 2 6 3 9 14 25 1 8 7 9 2 58 3 2 6 3 9 1 4 2 5 1 8 7 9 2 58 2 1 2 1 2 36 3 94 5 8 7 9 5 8 3 6 3 4 5 8 7 58 1 2 2 2 3 3 4 1 5 6 7 8 8 9 95 eventually...Select pivot valueFor each element: retrieve valueRecurse sort into right-handsubsetStore left if value < pivotStore right if value >= pivotall done?Recurse sort into left-hand subset NoYes__global__ void qsort(int *data, int l, int r) {int pivot = data[0];int *lptr = data+l, *rptr = data+r;// Partition data around pivot valuepartition(data, l, r, lptr, rptr, pivot);// Launch next stage recursively if(l < (rptr-data))qsort<<< ... >>>(data, l, rptr-data); if(r > (lptr-data))qsort<<< ... >>>(data, lptr-data, r); }。

kylins18作业指导书

kylins18作业指导书英文回答:The KylinS18 homework guide is a comprehensive resource that provides guidance and assistance for completing assignments. It is designed to help students understand the requirements of their assignments and provide them withtips and strategies for successfully completing them.The guide is divided into several sections, each focusing on a different aspect of the assignment process. The first section provides an overview of the assignment, including its purpose and objectives. It also includes a breakdown of the specific tasks that need to be completed and any specific guidelines or instructions that need to be followed.The next section of the guide offers tips andstrategies for conducting research and gathering information for the assignment. It provides advice on howto effectively use different sources, such as books, articles, and online resources, to gather relevant information. It also offers guidance on how to critically evaluate and analyze the information gathered to ensure its accuracy and relevance to the assignment.The guide also includes a section on organizing and structuring the assignment. It provides tips on how to create an outline or plan for the assignment to ensure that all necessary information is included and that the assignment flows logically and coherently. It also offers advice on how to effectively use headings, subheadings, and other formatting techniques to make the assignment visually appealing and easy to navigate.In addition to providing guidance on the content and structure of the assignment, the guide also offers tips on how to effectively communicate and present the information. It provides advice on how to write clearly and concisely, how to effectively use language and tone to engage the reader, and how to properly cite and reference sources to avoid plagiarism.Overall, the KylinS18 homework guide is a valuable resource for students. It provides comprehensive guidance and assistance for completing assignments, and offers tips and strategies for conducting research, organizing and structuring the assignment, and effectively communicating and presenting the information. By following the guidance provided in the guide, students can improve their assignment skills and achieve better results.中文回答:《KylinS18作业指导书》是一本全面的资源,为完成作业提供指导和帮助。

并行计算模型设计与优化方法

并行计算模型设计与优化方法随着科技的不断发展和计算能力的不断提高,越来越多的计算问题需要使用并行计算来解决。

并行计算是指将一个大问题分解成若干个小问题,通过同时处理这些小问题来加快计算速度的方法。

本文将讨论并行计算模型的设计和优化方法,以及如何利用这些方法来提高计算效率。

在进行并行计算之前,需要确定合适的并行计算模型。

常见的并行计算模型包括Fork-Join模型、Pipeline模型和Master-Worker模型等。

Fork-Join模型是将一个大任务分解成多个子任务,等待所有子任务完成后再进行下一步操作。

Pipeline模型是将一个大任务分解成多个互相依赖的小任务,并通过管道来传递数据。

Master-Worker模型是将一个大任务分解成多个独立的子任务,由主节点协调和控制子任务的执行。

在设计并行计算模型时,需要考虑以下几个因素:任务的拓扑结构、通信开销、负载平衡和数据分布策略。

任务的拓扑结构决定了任务之间的依赖关系,通信开销是指在任务之间传递数据所需的时间和资源,负载平衡是指将任务分配给不同的处理单元时,任务之间的负载是否均衡,数据分布策略是指将数据分配给不同的处理单元时的策略。

在优化并行计算性能时,可以采取以下几种方法:并行度增加、任务调度优化、数据布局优化和通信优化。

并行度增加是指增加并行计算的规模,使用更多的处理单元来处理任务,从而提高计算速度。

任务调度优化是指合理地将任务分配给不同的处理单元,以避免负载不均衡和资源浪费。

数据布局优化是指将数据分配给不同的处理单元时,尽量减少数据的传输开销,使得数据的访问更加高效。

通信优化是指优化任务之间的通信模式和通信方式,减少通信的开销。

在实际应用中,除了设计和优化并行计算模型外,还需要考虑一些其他的因素。

例如,硬件环境的选择和配置,包括处理器的类型和数量、内存的大小和带宽等。

软件环境的选择和配置,包括操作系统的选择和配置、编译器的选择和配置等。

对于不同的应用场景,还可以采用一些特定的技术和算法,例如GPU加速、分布式并行计算等。

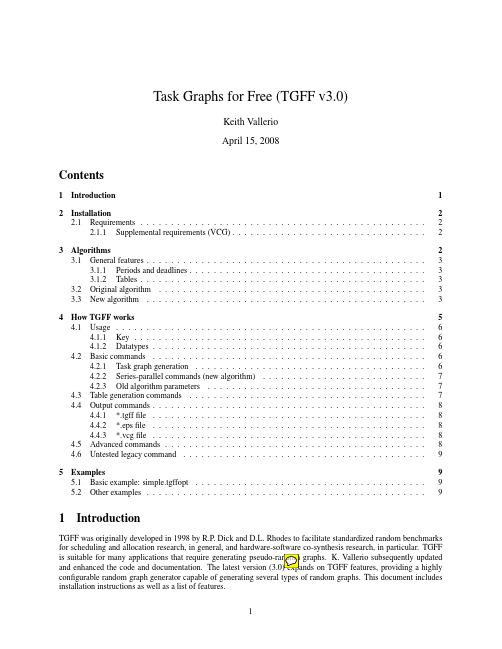

TGEF(3.0)

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

TGFF can generate visual graphs in both EPS and VCG formats. The EPS files should be readable by any postscript viewing program. The VCG format files require the graph visualization program VCG to view the files, but provides color and better zoom ability. VCG is a very useful graph visualization program which can be found at: • http://rw4.cs.uni-sb.de/users/sander/html/gsvcg1.html. TGFF is still useful without this program, but I highly recommend using it. If you are unfamiliar with VCG, the basic keys you need to know are: • ‘=’: Zoom in • ‘-’: Zoom out • ‘q’: Quit • Arrows: Move the graph left, right, up and down

intriguing properties of neural networks 精读

intriguing properties of neural networks 精读Intriguing Properties of Neural NetworksIntroduction:Neural networks are a type of machine learning model inspired by the human brain's functioning. They are composed of interconnected nodes known as neurons that work together to process and analyze complex data. Neural networks have gained immense popularity due to their ability to learn, adapt, and make accurate predictions. In this article, we will delve into some of the intriguing properties of neural networks and explore how they contribute to their success in various fields.1. Non-linearity:One of the key properties of neural networks is their ability to model nonlinear relationships in data. Traditional linear models assume a linear relationship between input variables and the output. However, neural networks introduce non-linear activation functions that allow them to capture complex patterns and correlations. This property enables neural networks to excel in tasks such as image recognition, natural language processing, and voice recognition.2. Parallel Processing:Neural networks possess the remarkable ability to perform parallel processing. Unlike traditional algorithms that follow a sequential execution path, neural networks operate by simultaneously processing multiple inputs in parallel. This parallel architecture allows for faster and efficientcomputations, making neural networks suitable for handling large-scale datasets and real-time applications.3. Distributed Representation:Neural networks utilize distributed representation to process and store information. In traditional computing systems, data is stored in a centralized manner. However, neural networks distribute information across interconnected neurons, enabling efficient storage, retrieval, and association of knowledge. This distributed representation enhances their ability to learn complex patterns and generalize from limited training examples.4. Adaptability:Neural networks exhibit a high degree of adaptability, enabling them to adjust their internal parameters and optimize their performance based on changing input. Through a process called backpropagation, neural networks continuously learn from the errors they make during training. This iterative learning process allows them to adapt to new data and improve their accuracy over time. The adaptability of neural networks makes them robust to noise, varying input patterns, and changing environments.5. Feature Extraction:Neural networks are adept at automatically extracting relevant features from raw data. In traditional machine learning approaches, feature engineering is often a time-consuming and manual process. However, neural networks can learn to identify important features directly from the input data. This property eliminates the need for human intervention and enables neuralnetworks to handle complex, high-dimensional data without prior knowledge or domain expertise.6. Capacity for Representation:Neural networks possess an impressive capacity for representation, making them capable of modeling intricate relationships in data. Deep neural networks, in particular, with multiple layers, can learn hierarchies of features, capturing both low-level and high-level representations. This property allows neural networks to excel in tasks such as image recognition, where they can learn to detect complex shapes, textures, and objects.Conclusion:The intriguing properties of neural networks, such as non-linearity, parallel processing, distributed representation, adaptability, feature extraction, and capacity for representation, contribute to their exceptional performance in various domains. These properties enable neural networks to tackle complex problems, make accurate predictions, and learn from diverse datasets. As researchers continue to explore and enhance the capabilities of neural networks, we can expect these models to revolutionize fields such as healthcare, finance, and autonomous systems.。

replica_parallel_workers 参数

replica_parallel_workers 参数

replica_parallel_workers 参数是用于设置并行工作进程数量的参数。

它通常用于分布式计算或并行处理环境中,以加速数据读取和处理。

当设置 replica_parallel_workers 参数时,它指定了用于并行读取副本数据的进程数量。

这意味着在读取数据时,可以同时使用多个工作进程来并行读取数据,从而提高数据读取的效率。

这个参数的设置取决于你的计算环境、数据集大小和网络带宽等因素。

通常,你可以通过调整这个参数来优化数据读取的性能。

但是,需要注意的是,增加并行工作进程数量也会增加系统的资源消耗,因此需要根据实际情况进行权衡和调整。

请注意,具体的参数名称和用法可能因不同的编程语言、框架或工具而有所不同。

因此,在使用replica_parallel_workers 参数时,建议查阅相关文档或参考示例代码以了解更详细的信息和用法。

samples_for_parallel_programming -回复

samples_for_parallel_programming -回复什么是并行编程?在计算机科学领域中,并行编程是指同时执行多个计算任务的一种编程模型。

与之相对的是串行编程,即按照顺序逐个执行计算任务。

虽然串行编程很直观简单,但随着计算机硬件的发展,多核处理器和分布式计算系统的出现,使并行编程变得更加重要。

并行编程可以显著提高计算机程序的性能和效率。

通过同时执行多个计算任务,可以最大限度地利用计算机的资源,例如多个CPU核心或分布式计算节点。

这样,就可以加快计算速度,提高系统的响应能力和处理能力。

然而,并行编程也带来了许多挑战。

它需要有效地将计算任务分解为多个独立的子任务,并协调它们的执行。

并行执行时还可能面临资源竞争和数据一致性等问题。

因此,为了实现高效的并行编程,开发人员需要选择合适的并行编程模型和技术,并掌握并行算法、并行数据结构和并发控制等相关知识。

在并行编程中,有多种并行编程模型可供选择。

其中一种常见的模型是共享内存模型。

在这种模型中,多个线程或进程共享同一块内存区域,并通过读写该内存来进行通信。

另一种常见的模型是消息传递模型。

在这种模型中,不同的线程或进程通过发送和接收消息进行通信。

两种模型各有优劣,选择适合具体应用的模型非常重要。

为了支持并行编程,许多编程语言提供了并行编程的扩展或库。

例如,Java 提供了并行程序设计的扩展,如并行循环和并行库。

C++也有一些并行编程的库和框架,例如OpenMP和CUDA。

此外,还有一些专门用于并行编程的语言,例如CUDA和OpenCL,它们针对特定的硬件体系结构进行了优化。

在进行并行编程时,需要注意一些相关的编程技巧和优化策略,以提高并行程序的性能。

例如,任务划分和负载平衡是非常重要的。

任务划分应该将计算任务合理地分配给不同的线程或进程,以确保它们能够充分利用计算资源。

而负载平衡则是指尽量使各个计算任务的执行时间接近,以避免某些任务成为性能瓶颈。

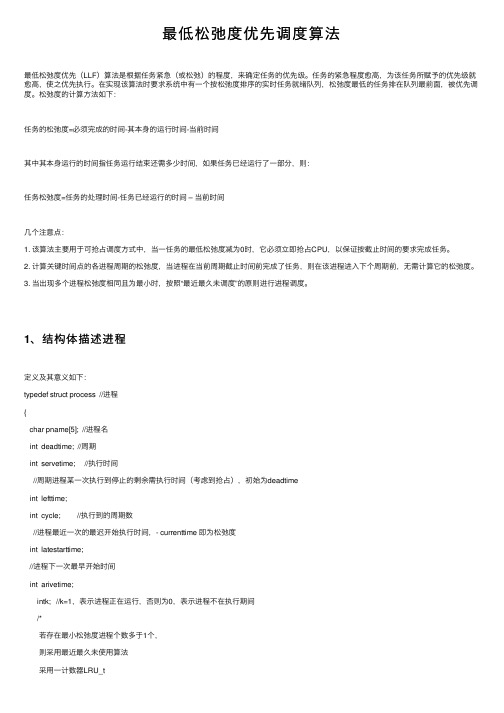

最低松弛度优先调度算法

最低松弛度优先调度算法最低松弛度优先(LLF)算法是根据任务紧急(或松弛)的程度,来确定任务的优先级。

任务的紧急程度愈⾼,为该任务所赋予的优先级就愈⾼,使之优先执⾏。

在实现该算法时要求系统中有⼀个按松弛度排序的实时任务就绪队列,松弛度最低的任务排在队列最前⾯,被优先调度。

松弛度的计算⽅法如下:任务的松弛度=必须完成的时间-其本⾝的运⾏时间-当前时间其中其本⾝运⾏的时间指任务运⾏结束还需多少时间,如果任务已经运⾏了⼀部分,则:任务松弛度=任务的处理时间-任务已经运⾏的时间 – 当前时间⼏个注意点:1. 该算法主要⽤于可抢占调度⽅式中,当⼀任务的最低松弛度减为0时,它必须⽴即抢占CPU,以保证按截⽌时间的要求完成任务。

2. 计算关键时间点的各进程周期的松弛度,当进程在当前周期截⽌时间前完成了任务,则在该进程进⼊下个周期前,⽆需计算它的松弛度。

3. 当出现多个进程松弛度相同且为最⼩时,按照“最近最久未调度”的原则进⾏进程调度。

1、结构体描述进程定义及其意义如下:typedef struct process //进程{char pname[5]; //进程名int deadtime; //周期int servetime; //执⾏时间//周期进程某⼀次执⾏到停⽌的剩余需执⾏时间(考虑到抢占),初始为deadtimeint lefttime;int cycle; //执⾏到的周期数//进程最近⼀次的最迟开始执⾏时间,- currenttime 即为松弛度int latestarttime;//进程下⼀次最早开始时间int arivetime;intk; //k=1,表⽰进程正在运⾏,否则为0,表⽰进程不在执⾏期间/*若存在最⼩松弛度进程个数多于1个,则采⽤最近最久未使⽤算法采⽤⼀计数器LRU_t*/intLRU_t;}process;2、循环队列存储进程定义及其意义如下:typedef struct sqqueue //循环队列{process *data[queuesize];int front,rear;} sqqueue;重难点分析1、实时系统可调度条件当实时系统中有M个硬实时任务,它们的处理时间可表⽰为Ci ,周期时间表⽰为Pi,则在采⽤N个处理机的系统中,必须满⾜限制条件:Σ<=N系统才是可调度的。

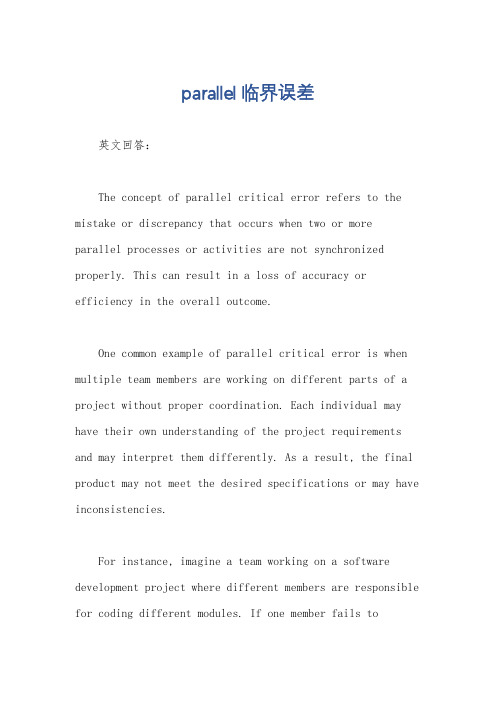

parallel临界误差

parallel临界误差英文回答:The concept of parallel critical error refers to the mistake or discrepancy that occurs when two or moreparallel processes or activities are not synchronized properly. This can result in a loss of accuracy or efficiency in the overall outcome.One common example of parallel critical error is when multiple team members are working on different parts of a project without proper coordination. Each individual may have their own understanding of the project requirements and may interpret them differently. As a result, the final product may not meet the desired specifications or may have inconsistencies.For instance, imagine a team working on a software development project where different members are responsible for coding different modules. If one member fails toproperly communicate the changes made in their module to the rest of the team, it can lead to conflicts and errors when integrating the different modules together. This can result in a parallel critical error where the final software does not function as intended.Another example can be seen in manufacturing processes. If different machines or production lines are not synchronized properly, it can lead to errors in the final product. For instance, in an assembly line, if one machine is producing parts at a faster rate than another machine,it can cause a bottleneck and lead to inefficiencies in the overall production process.中文回答:并行临界误差是指当两个或多个并行的过程或活动没有正确同步时发生的错误或差异。

parallelstream copyonwritearraylist -回复

parallelstream copyonwritearraylist -回复CopyOnWriteArrayList 是一个线程安全的并发容器类,它是Java 集合框架中的一员,用于在多线程环境下进行数据操作。

本文将一步一步回答关于ParallelStream 和CopyOnWriteArrayList 的问题。

第一步:了解ParallelStream 和CopyOnWriteArrayList 的基本概念和用途ParallelStream 是Java 8 中引入的一个并行流框架,它允许对集合进行并行操作,从而提高程序的性能。

CopyOnWriteArrayList 是一个具有并发读取和写入安全性的列表容器类,它提供了一种在并发场景下进行数据操作的解决方案。

第二步:深入了解ParallelStream 的工作原理ParallelStream 是通过分割输入数据流,创建多个线程对数据进行并行处理的。

具体而言,它根据当前可用的CPU 内核数目将数据流分割成多个子任务,并行执行这些子任务,然后将结果合并为一个最终的输出。

这种方式可以充分利用多核CPU 的性能,加快处理速度。

第三步:详细说明CopyOnWriteArrayList 的实现原理和特点CopyOnWriteArrayList 内部使用一个数组来存储元素,每当有写操作(添加、修改或删除元素)发生时,它都会创建并复制一份全新的数组。

同时,该类还通过使用volatile 关键字来保证其内部数组的可见性。

因此,每次写操作都不会影响到已有的读操作,实现了并发的读写安全性。

第四步:分析ParallelStream 在处理CopyOnWriteArrayList 时的优势和适用场景ParallelStream 可以在处理CopyOnWriteArrayList 时发挥出一些优势。

由于CopyOnWriteArrayList 在写操作时创建了一个新的数组,因此在读操作时并不受到写操作的影响,这意味着在并行流操作中读取数据是安全的。

回家后你必须先写作业英语

When you return home,its essential to prioritize your homework as part of your daily routine.Here are some steps to follow to ensure you manage your time effectively and complete your assignments efficiently:1.Create a Schedule:Develop a homework schedule that suits your afterschool activities and personal commitments.This will help you allocate specific time slots for each subject.2.Choose a Quiet Place:Find a quiet and comfortable place in your home where you can focus without distractions.This could be your bedroom,a study room,or a corner of the living room.3.Gather Your Materials:Before you start,gather all the necessary materials such as textbooks,notebooks,pens,and any other resources you might need.4.Break Down Tasks:If you have multiple assignments,break them down into smaller, manageable tasks.This will make it easier to tackle each one systematically.5.Start with the Most Challenging:Some students find it helpful to start with the most difficult or timeconsuming assignment first,while their energy levels are high.6.Stay Organized:Keep your notes and assignments e folders or binders to separate work by subject or project.7.Take Regular Breaks:Short breaks can help maintain focus and prevent e techniques like the Pomodoro Technique,where you work for25minutes and then take a 5minute break.e Tools and Resources:Utilize tools like dictionaries,thesauruses,and educational websites to help with your homework.If youre stuck,dont hesitate to ask for help from parents,tutors,or classmates.9.Review Your Work:Once youve completed an assignment,review it to check for errors or areas that could be improved.This is also a good time to clarify any points youre unsure about.10.Stay Consistent:Make a habit of doing your homework as soon as you get home. Consistency is key to developing good study habits.11.Prepare for the Next Day:After finishing your homework,take a few minutes to organize your bag and prepare for the next days classes.This can include packing yourhomework,gathering materials for the next days assignments,and reviewing the schedule.12.Stay Healthy:Dont forget to eat a healthy snack and stay hydrated while youre working.Physical wellbeing is crucial for maintaining focus and energy.By following these steps,you can ensure that youre not only completing your homework but also developing good study habits that will serve you well throughout your academic career.。

TI 多内核编程指南

Application ReportSPRAB27B—August 2012Multicore Programming GuideMulticore Programming and Applications/DSP Systems AbstractAs application complexity continues to grow, we have reached a limit on increasingperformance by merely scaling clock speed. To meet the ever-increasing processingdemand, modern System-On-Chip solutions contain multiple processing cores. Thedilemma is how to map applications to multicore devices. In this paper, we present aprogramming methodology for converting applications to run on multicore devices.We also describe the features of Texas Instruments DSPs that enable efficientimplementation, execution, synchronization, and analysis of multicore applications.Contents1Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32Mapping an Application to a Multicore Processor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32.1Parallel Processing Models. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32.2Identifying a Parallel Task Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93Inter-Processor Communication. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143.1Data Movement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143.2Multicore Navigator Data Movement. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173.3Notification and Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173.4Multicore Navigator Notification Methods. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .224Data Transfer Engines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .234.1Packet DMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .234.2EDMA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .244.3Ethernet. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .244.4RapidIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .244.5Antenna Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .254.6PCI Express. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .254.7HyperLink. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .255Shared Resource Management. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .265.1Global Flags. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .265.2OS Semaphores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .265.3Hardware Semaphores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .265.4Direct Signaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .266Memory Management. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .276.1CPU View of the Device. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .286.2Cache and Prefetch Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .296.3Shared Code Program Memory Placement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .306.4Peripheral Drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .326.5Data Memory Placement and Access. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .337DSP Code and Data Images . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .347.1Single Image . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .347.2Multiple Images . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .347.3Multiple Images with Shared Code and Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .347.4Device Boot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .357.5Multicore Application Deployment (MAD) Utilities. . . . . . . . . . . . . . . . . . . . . . . . . . . . .368System Debug. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .388.1Debug and Tooling Categories. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .388.2Trace Logs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .398.3System Trace. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .509Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5110References. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52 Page 2 of 52Multicore Programming Guide SPRAB27B—August 20121IntroductionFor the past 50 years, Moore’s law accurately predicted that the number of transistorson an integrated circuit would double every two years. To translate these transistorsinto equivalent levels of system performance, chip designers increased clockfrequencies (requiring deeper instruction pipelines), increased instruction levelparallelism (requiring concurrent threads and branch prediction), increased memoryperformance (requiring larger caches), and increased power consumption (requiringactive power management).Each of these four areas is hitting a wall that impedes further growth:•Increased processing frequency is slowing due to diminishing improvements inclock rates and poor wire scaling as semiconductor devices shrink.•Instruction-level parallelism is limited by the inherent lack of parallelism in theapplications.•Memory performance is limited by the increasing gap between processor andmemory speeds.•Power consumption scales with clock frequency; so, at some point, extraordinarymeans are needed to cool the device.Using multiple processor cores on a single chip allows designers to meet performancegoals without using the maximum operating frequency. They can select a frequency inthe sweet spot of a process technology that results in lower power consumption. Overallperformance is achieved with cores having simplified pipeline architectures relative toan equivalent single core solution. Multiple instances of the core in the device result indramatic increases in the MIPS-per-watt performance.2Mapping an Application to a Multicore ProcessorUntil recently, advances in computing hardware provided significant increases in theexecution speed of software with little effort from software developers. Theintroduction of multicore processors provides a new challenge for software developers,who must now master the programming techniques necessary to fully exploit multicoreprocessing potential.Task parallelism is the concurrent execution of independent tasks in software. On asingle-core processor, separate tasks must share the same processor. On a multicoreprocessor, tasks essentially run independently of one another, resulting in moreefficient execution.2.1Parallel Processing ModelsOne of the first steps in mapping an application to a multicore processor is to identifythe task parallelism and select a processing model that fits best. The two dominantmodels are a Master/Slave model in which one core controls the work assignments onall cores, and the Data Flow model in which work flows through processing stages as ina pipeline.2.1.1Master/Slave ModelThe Master/Slave model represents centralized control with distributed execution. Amaster core is responsible for scheduling various threads of execution that can beallocated to any available core for processing. It also must deliver any data required bythe thread to the slave core. Applications that fit this model inherently consist of manysmall independent threads that fit easily within the processing resources of a singlecore. This software often contains a significant amount of control code and oftenaccesses memory in random order with multiple levels of indirection. There isrelatively little computation per memory access and the code base is usually very large.Applications that fit the Master/Slave model often run on a high-level OS like Linuxand potentially already have multiple threads of execution defined. In this scenario, thehigh-level OS is the master in charge of the scheduling.The challenge for applications using this model is real-time load balancing because thethread activation can be random. Individual threads of execution can have verydifferent throughput requirements. The master must maintain a list of cores with freeresources and be able to optimize the balance of work across the cores so that optimalparallelism is achieved. An example of a Master/Slave task allocation model is shownin Figure1.Figure1Master / Slave Processing ModelOne application that lends itself to the Master/Slave model is the multi-user data linklayer of a communication protocol stack. It is responsible for media access control andlogical link control of a physical layer including complex, dynamic scheduling and datamovement through transport channels. The software often accesses multi-dimensionalarrays resulting in very disjointed memory access.Page 4 of 52Multicore Programming Guide SPRAB27B—August 2012One or more execution threads are mapped to each core. Task assignment is achievedusing message-passing between cores. The messages provide the control triggers tobegin execution and pointers to the required data. Each core has at least one task whosejob is to receive messages containing job assignments. The task is suspended until amessage arrives triggering the thread of execution.2.1.2Data Flow ModelThe Data Flow model represents distributed control and execution. Each coreprocesses a block of data using various algorithms and then the data is passed toanother core for further processing. The initial core is often connected to an inputinterface supplying the initial data for processing from either a sensor or FPGA.Scheduling is triggered upon data availability. Applications that fit the Data Flowmodel often contain large and computationally complex components that aredependent on each other and may not fit on a single core. They likely run on a realtimeOS where minimizing latency is critical. Data access patterns are very regular becauseeach element of the data arrays is processed uniformly.The challenge for applications using this model is partitioning the complexcomponents across cores and the high data flow rate through the system. Componentsoften need to be split and mapped to multiple cores to keep the processing pipelineflowing regularly. The high data rate requires good memory bandwidth between cores.The data movement between cores is regular and low latency hand-offs are critical. Anexample of Data Flow processing is shown in Figure2.Figure2Data Flow Processing ModelOne application that lends itself to the Data Flow model is the physical layer of acommunication protocol stack. It translates communications requests from the datalink layer into hardware-specific operations to affect transmission or reception ofelectronic signals. The software implements complex signal processing using intrinsicinstructions that take advantage of the instruction-level parallelism in the hardware.The processing chain requires one or more tasks to be mapped to each core.Synchronization of execution is achieved using message passing between cores. Data ispassed between cores using shared memory or DMA transfers.2.1.3OpenMP ModelOpenMP is an Application Programming Interface (API) for developingmulti-threaded applications in C/C++ or Fortran for shared-memory parallel (SMP)architectures.OpenMP standardizes the last 20 years of SMP practice and is a programmer-friendlyapproach with many advantages. The API is easy to use and quick to implement; oncethe programmer identifies parallel regions and inserts the relevant OpenMPconstructs, the compiler and runtime system figures out the rest of the details. The APImakes it easy to scale across cores and allows moving from an ‘m’ core implementationto an ‘n’ core implementation with minimal modifications to source code. OpenMP issequential-coder friendly; that is, when a programmer has a sequential piece of codeand would like to parallelize it, it is not necessary to create a totally separate multicoreversion of the program. Instead of this all-or-nothing approach, OpenMP encouragesan incremental approach to parallelization, where programmers can focus onparallelizing small blocks of code at a time. The API also allows users to maintain asingle unified code base for both sequential and parallel versions of code.2.1.3.1FeaturesThe OpenMP API consists primarily of compiler directives, library routines, andenvironment variables that can be leveraged to parallelize a program.Compiler directives allow programmers to specify which instructions they want toexecute in parallel and how they would like the work distributed across cores. OpenMPdirectives typically have the syntax “#pragma omp construct [clause [clause]…].” Forexample, “#pragma omp section nowait” where section is the construct and nowait is aclause. The next section shows example implementations that contain directives.Library routines or runtime library calls allow programmers to perform a host ofdifferent functions. There are execution environment routines that can configure andmonitor threads, processors, and other aspects of the parallel environment.There are lock routines that provide function calls for synchronization. There aretiming routines that provide a portable wall clock timer. For example, the libraryroutine “omp_set_num_threads (int numthreads)” tells the compiler how manythreads need to be created for an upcoming parallel region.Finally, environment variables enable programmers to query the state or alter theexecution features of an application like the default number of threads, loop iterationcount, etc. For example, “OMP_NUM_THREADS” is the environment variable thatholds the total number of OpenMP threads.Page 6 of 52Multicore Programming Guide SPRAB27B—August 20122.1.3.2ImplementationThis section contains four typical implementation scenarios and shows how OpenMPallows programmers to handle each of them. The following examples introduce someimportant OpenMP compiler directives that are applicable to these implementationscenarios. For a complete list of directives, see the OpenMP specification available onthe official OpenMP website at .Create Teams of Threads Figure3 shows how OpenMP implementations are based on a fork-join model. AnOpenMP program begins with an initial thread (known as a master thread) in asequential region. When a parallel region is encountered—indicated by the compilerdirective “#pragma omp parallel”—extra threads called worker threads areautomatically created by the scheduler. This team of threads executes simultaneouslyto work on the block of parallel code. When the parallel region ends, the program waitsfor all threads to terminate, then resumes its single-threaded execution for the nextsequential region.Figure3OpenMP Fork-Join ModelTo illustrate this point further, it is useful to look at an implementation example.Figure4 on page8 shows a sample OpenMP Hello World program. The first line in thecode includes the omp.h header file that includes the OpenMP API definitions. Next,the call to the library routine sets the number of threads for the OpenMP parallel regionto follow. When the parallel compiler directive is encountered, the scheduler spawnsthree additional threads. Each of the threads runs the code within the parallel regionand prints the Hello World line with its unique thread id. The implicit barrier at the endof the region ensures that all threads terminate before the program continues.Figure4Hello World Example Using OpenMP Parallel Compiler DirectiveShare Work Among Threads After the programmer has identified which blocks of code in the region are to be runby multiple threads, the next step is to express how the work in the parallel region willbe shared among the threads. The OpenMP work-sharing constructs are designed to doexactly this. There are a variety of work-sharing constructs available; the following twoexamples focus on two commonly-used constructs.The “#pragma omp for” work-sharing construct enables programmers to distribute afor loop among multiple threads. This construct applies to for loops where subsequentiterations are independent of each other; that is, changing the order in which iterationsare called does not change the result.To appreciate the power of the for work-sharing construct, look at the following threesituations of implementation: sequential; only with the parallel construct; and both theparallel and work-sharing constructs. Assume a for loop with N iterations, that does abasic array computation.Page 8 of 52Multicore Programming Guide SPRAB27B—August 2012The second work-sharing construct example is “#pragma omp sections” which allowsthe programmer to distribute multiple tasks across cores, where each core runs aunique piece of code. The following code snippet illustrates the use of this work-sharingconstruct.Note that by default a barrier is implicit at the end of the block of code. However,OpenMP makes the nowait clause available to turn off the barrier. This would beimplemented as “#pragma omp sections nowait”.2.2Identifying a Parallel Task ImplementationIdentifying the task parallelism in an application is a challenge that, for now, must betackled manually. TI is developing code generation tools that will allow users toinstrument their source code to identify opportunities for automating the mapping oftasks to individual cores. Even after identifying parallel tasks, mapping and schedulingthe tasks across a multicore system requires careful planning.A four-step process, derived from Software Decomposition for MulticoreArchitectures[1], is proposed to guide the design of the application:1.Partitioning — Partitioning of a design is intended to expose opportunities forparallel execution. The focus is on defining a large number of small tasks in orderto yield a fine-grained decomposition of a problem.munication — The tasks generated by a partition are intended to executeconcurrently but cannot, in general, execute independently. The computation tobe performed in one task will typically require data associated with another task.Data must then be transferred between tasks to allow computation to proceed.This information flow is specified in the communication phase of a design.bining — Decisions made in the partitioning and communication phasesare reviewed to identify a grouping that will execute efficiently on the multicorearchitecture.4.Mapping — This stage consists of determining where each task is to execute.2.2.1PartitioningPartitioning an application into base components requires a complexity analysis of thecomputation (Reads, Writes, Executes, Multiplies) in each software component and ananalysis of the coupling and cohesion of each component.For an existing application, the easiest way to measure the computational requirementsis to instrument the software to collect timestamps at the entry and exit of each moduleof interest. Using the execution schedule, it is then possible to calculate the throughputrate requirements in MIPS. Measurements should be collected with both cold andwarm caches to understand the overhead of instruction and data cache misses.Estimating the coupling of a component characterizes its interdependence with othersubsystems. An analysis of the number of functions or global data outside thesubsystem that depend on entities within the subsystem can pinpoint too manyresponsibilities to other systems. An analysis of the number of functions inside thesubsystem that depend on functions or global data outside the subsystem identifies thelevel of dependency on other systems.A subsystem's cohesion characterizes its internal interdependencies and the degree towhich the various responsibilities of the module are focused. It expresses how well allthe internal functions of the subsystem work together. If a single algorithm must useevery function in a subsystem, then there is high cohesion. If several algorithms eachuse only a few functions in a subsystem, then there is low cohesion. Subsystems withhigh cohesion tend to be very modular, supporting partitioning more easily.Partitioning the application into modules or subsystems is a matter of finding thebreakpoints where coupling is low and cohesion is high. If a module has too manyexternal dependencies, it should be grouped with another module that together wouldreduce coupling and increase cohesion. It is also necessary to take into account theoverall throughput requirements of the module to ensure it fits within a single core.2.2.2CommunicationAfter the software modules are identified in the partitioning stage it is necessary tomeasure the control and data communication requirements between them. Controlflow diagrams can identify independent control paths that help determine concurrenttasks in the system. Data flow diagrams help determine object and datasynchronization needs.Control flow diagrams represent the execution paths between modules. Modules in aprocessing sequence that are not on the same core must rely on message passing tosynchronize their execution and possibly require data transfers. Both of these actionscan introduce latency. The control flow diagrams should be used to create metrics that Page 10 of 52Multicore Programming Guide SPRAB27B—August 2012assist the module grouping decision to maximize overall throughput. Figure 5 shows anexample of a control flow diagram.Figure 5Example Control Flow DiagramData flow diagrams identify the data that must pass between modules and this can beused to create a measure of the amount and rate of data passed. A data flow diagramalso shows the level of interaction between a module and outside entities. Metricsshould be created to assist the grouping of modules to minimize the number andamount of data communicated between cores. Figure 6 shows an example diagram.Figure 6Example Data Flow Diagram2.2.3CombiningThe combining phase determines whether it is useful to combine tasks identified by thepartitioning phase, so as to provide a smaller number of tasks, each of greater size.Combining also includes determining whether it is worthwhile to replicate data orcomputation. Related modules with low computational requirements and highcoupling are grouped together. Modules with high computation and highcommunication costs are decomposed into smaller modules with lower individualcosts.2.2.4MappingMapping is the process of assigning modules, tasks, or subsystems to individual cores.Using the results from Partitioning, Communication, and Combining, a plan is madeidentifying concurrency issues and module coupling. This is also the time to consideravailable hardware accelerators and any dependencies this would place on softwaremodules.Subsystems are allocated onto different cores based on the selected programmingmodel: Master/Slave or Data Flow. To allow for inter-processor communicationlatency and parametric scaling, it is important to reserve some of the available MIPS,L2 memory, and communication bandwidth on the first iteration of mapping. After allthe modules are mapped, the overall loading of each core can be evaluated to indicateareas for additional refactoring to balance the processing load across cores.In addition to the throughput requirements of each module, message passing latencyand processing synchronization must be factored into the overall timeline. Criticallatency issues can be addressed by adjusting the module factoring to reduce the overallnumber of communication steps. When multiple cores need to share a resource like aDMA engine or critical memory section, a hardware semaphore is used to ensuremutual exclusion as described in Section5.3. Blocking time for a resource must befactored into the overall processing efficiency equation.Embedded processors typically have a memory hierarchy with multiple levels of cacheand off-chip memory. It is preferred to operate on data in cache to minimize theperformance hit on the external memory interface. The processing partition selectedmay require additional memory buffers or data duplication to compensate forinter-processor-communication latency. Refactoring the software modules to optimizethe cache performance is an important consideration.When a particular algorithm or critical processing loop requires more throughput thanavailable on a single core, consider the data parallelism as a potential way to split theprocessing requirements. A brute force division of the data by the available number ofcores is not always the best split due to data locality and organization, and requiredsignal processing. Carefully evaluate the amount of data that must be shared betweencores to determine the best split and any need to duplicate some portion of the data. Page 12 of 52Multicore Programming Guide SPRAB27B—August 2012The use of hardware accelerators like FFT or Viterbi coprocessors is common inembedded processing. Sharing the accelerator across multiple cores would requiremutual exclusion via a lock to ensure correct behavior. Partitioning all functionalityrequiring the use of the coprocessor to a single core eliminates the need for a hardwaresemaphore and the associated latency. Developers should study the efficiency ofblocking multicore access to the accelerator versus non-blocking single core accesswith potentially additional data transfer costs to get the data to the single core.Consideration must be given to scalability as part of the partitioning process. Criticalsystem parameters are identified and their likely instantiations and combinationsmapped to important use cases. The mapping of tasks to cores would ideally remainfixed as the application scales for the various use cases.The mapping process requires multiple cycles of task allocation and parallel efficiencymeasurement to find an optimal solution. There is no heuristic that is optimal for allapplications.2.2.5Identifying and Modifying the Code for OpenMP-based ParallelizationOpenMP provides some very useful APIs for parallelization, but it is the programmer'sresponsibility to identify a parallelization strategy, then leverage relevant OpenMPAPIs. Deciding what code snippets to parallelize depends on the application code andthe use-case. The 'omp parallel' construct, introduced earlier in this section, canessentially be used to parallelize any redundant function across cores. If the sequentialcode contains 'for' loops with a large number of iterations, the programmer canleverage the 'omp for' OpenMP construct that splits the 'for' loop iterations acrosscores.Another question the programmer should consider here is whether the applicationlends itself to data-based or task-based partitioning. For example, splitting an imageinto 8 slices, where each core receives one input slice and runs the same set ofalgorithms on the slice, is an example of data-based partitioning, which could lend itselfto the 'omp parallel' and 'omp for' constructs. In contrast, if each core is running adifferent algorithm, the programmer could leverage the 'omp sections' construct to splitunique tasks across cores.。

并行编程(ParallelFramework)

并⾏编程(ParallelFramework)前⾔并⾏编程:通过编码⽅式利⽤多核或多处理器称为并⾏编程,多线程概念的⼀个⼦集。

并⾏处理:把正在执⾏的⼤量的任务分割成⼩块,分配给多个同时运⾏的线程。

多线程的⼀种。

并⾏编程分为如下⼏个结构:1.并⾏的LINQ或PLINQ2.Parallel类3.任务并⾏结构4.并发集合5.SpinLock和SpinWait这些是.NET 4.0引⼊的功能,⼀般被称为PFX(Parallel Framework,并⾏框架)。

Parallel类和任务并⾏结构称为TPL(Task Parallel Library,任务并⾏库)。

并⾏框架(PFX)当前CPU技术达到瓶颈,⽽制造商将关注重点转移到提⾼内核技术上,⽽标准单线程代码并不会因此⽽⾃动提⾼运⾏速度。

利⽤多核提升程序性能通常需要对计算密集型代码进⾏⼀些处理:1.将代码划分成块。

2.通过多线程并⾏执⾏这些代码块。

3.结果变为可⽤后,以线程安全和⾼性能的⽅式整合这些结果。

传统多线程结构虽然实现功能,但难度颇⾼且不⽅便,特别是划分和整理的步骤(本质问题是:多线程同时使⽤相同数据时,出于线程安全考虑进⾏锁定的常⽤策略会引发⼤量竞争)。

⽽并⾏框架(Parallel Framework)专门⽤于在这些应⽤场景中提供帮助。

PFX:⾼层由两个数据并⾏API组成:PLINQ或Parallel类。

底层包含任务并⾏类和⼀组另外的结构为并⾏编程提供帮助。

基础并⾏语⾔集成查询(PLINQ)语⾔集成查询(Language Integrated Query,LINQ)提供了⼀个简捷的语法来查询数据集合。

⽽这种由⼀个线程顺序处理数据集合的⽅式我们称为顺序查询(sequential query)。

并⾏语⾔集成查询(Parallel LINQ)是LINQ的并⾏版。

它将顺序查询转换为并⾏查询,在内部使⽤任务,将集合中数据项的处理⼯作分散到多个CPU上,以并发处理多个数据项。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Task Parallel Skeletons for IrregularlyStructured ProblemsPetra HofstedtDepartment of Computer Science,Dresden University of Technology,hofstedt@inf.tu-dresden.deAbstract.The integration of a task parallel skeleton into a functionalprogramming language is presented.Task parallel skeletons,as other al-gorithmic skeletons,represent general parallelization patterns.They areintroduced into otherwise sequential languages to enable the develop-ment of parallel applications.Into functional programming languages,they naturally are integrated as higher-order functional forms.We show by means of the example branch-and-bound that the introduc-tion of task parallel skeletons into a functional programming languageis advantageous with regard to the comfort of programming,achievinggood computation performance at the same time.1IntroductionMost parallel programs were and are written in imperative languages.In many of these languages,the programmer has to use low-level constructs to express par-allelism,synchronization and communication.To support platform-independent development of parallel programs standards and systems have been invented, e.g.MPI and PVM.In functional languages,such supporting libraries have been added in rudimentary form only recently.Hence,the advantages of functional programs,such as their ability to state powerful algorithms in a short,abstract and precise way,cannot be combined with the ability to control the parallel execution of processes on parallel architectures.Our aim is to remedy that situation.A functional language has been extended by constructs for data and task parallel programming.We want to provide com-fortable tools to exploit parallelism for the user,so that she is burdened as few as possible with communication,synchronization,load balancing,data and task distribution,reaching at the same time good performance by exploitation of parallelism.The extension of functional languages by algorithmic skeletons is a promising approach to introduce data parallelism as well as task parallelism into these languages.As demonstrated for imperative languages,e.g.by Cole[3],there are several approaches how to introduce skeletons into functional languages as higher-order The work of this author was supported by the‘Graduiertenkolleg Werkzeuge zum effektiven Einsatz paralleler und verteilter Rechnersysteme’of the German Research Foundation(DFG)at the Dresden University of Technology.parallel forms.However,most authors concentrated on data parallel skeletons, e.g.[1],[4],[5].Hence,our aim has been to explore the promising concept of task parallel skeletons for functional languages by integrating them into a functional language.A major focus of our work is on reusability of methods implemented as skeletons.Algorithmic skeletons are integrated into otherwise sequential languages to express parallelization patterns.In our approach,currently skeletons are im-plemented in a lower-level imperative programming language,but presented as higher-order functions in the functional language.Implementation-details are hidden within the skeletons.In this way,it is possible to combine expressiveness andflexibility of the sequential functional language with the efficiency of paral-lel special purpose algorithms.Depending on the type of parallelism exploited, skeletons are distinguished in data and task parallel ones.Data parallel skele-tons apply functions on multiple data at the same time.Task parallel skeletons express which elements of a computation may be executed in parallel.The im-plementation in the underlying system determines the number and the location of parallel processes that are generated to execute the task parallel skeleton.2The Branch-and-Bound Skeleton in a Functional LanguageBranch-and-bound methods are systematic search techniques for solving discrete optimization problems.Starting with a set of variables with afinite set of dis-crete values(a domain)assigned to each of the variables,the aim is to assign a value of the corresponding domain to each variable in such a way that a given objective function reaches a minimum or a maximum value and several con-straints are satisfied.First,mutually disjunct subproblems are generated from a given initial problem by using an appropriate branching rule(branch).For each of the generated subproblems an estimation(bound)is computed.By means of this estimation,the subproblem to be branched next is chosen(select)and decomposed(branched).If the chosen problem cannot be branched into further subproblems,its solution(if existing)is an optimal solution.Subproblems with non-optimal or inadmissible variable assignments can be eliminated during the computation(elimination).The four rules branch,bound,select and elim-ination are called basic rules.The principal difference between parallel and sequential branch-and-bound algorithms lies in the way of handling the generated knowledge.Subproblems generated from problems by decomposition and knowledge about local and global optima belong to this knowledge.While with sequential branch-and-bound one processor generates and uses the complete knowledge,the distribution of work causes a distribution of knowledge,and the interaction of the processors working together to solve the problem becomes necessary.Starting point for our implementation was the functional language DFS (‘D atenparallele f unktionale S prache’[6]),which already contained data par-allel skeletons for distributed arrays.DFS is an experimental programming lan-guage to be used on parallel computers.The language is strict and evaluates DFS-programs in a call-by-value strategy accordingly.To give the user the possibility to exploit parallelism in a very comfortable way,we have extended the functional language DFS by task parallel skeletons. One of them was a branch-and-bound skeleton.The user provides the basic rules branch,bound,select and elimination using the functional language.Then she can make a function call to the skeleton as follows:branch&bound branch bound select elimination problem.A parallel abstract machine(PAM)represents the runtime environment for DFS.The PAM consists of a number of interconnected nodes communicating by messages.Each node consists of three units:the message administration unit, which handles the incoming and outgoing messages,the skeleton unit,which is responsible for skeleton processing,and the reduction unit,which performs the actual computation.Skeletons are the only source of parallelism in the programs.To implement the parallel branch-and-bound skeleton,several design deci-sions had to be made with the objective of good computation performance and high comfort.In the following,the implementation is characterized according to Trienekens’classification([7])of parallel branch-and-bound algorithms.Table1.Classification by Trienekensknowledge sharing global/local knowledge basecomplete/partial knowledge baseupdate strategyknowledge use access strategyreaction strategydividing the work units of workload balancing strategysynchronicity synchronicity of each processbasic rules branch,bound,select,elimination Each process uses a local partial knowledge base containing only a part of the complete generated knowledge.In this way,the bottleneck arising from the access of all processes to a shared knowledge base is avoided,but at the expense of the actuality of the knowledge base.A process stores newly generated knowledge at its local knowledge base only;if a local optimum has been computed,the value is broadcasted to all other processes(update strategy).When a process hasfinished a subtask,it accesses its local knowledge base, to store the results at the knowledge base and to get a new subtask to solve.If a process receives a message containing a local optimum,the process compares this optimum with its actual local optimum and the bounds of the subtasks still to be solved(access strategy).A process receiving a local optimum from another processfirstfinishes its actual task and then reacts according to the receivedmessage(reaction strategy).This may result in the execution of unnecessary work.But the extent of this work is small because of the high granularity of the distributed work.A unit of work consists of branching a problem into subproblems and comput-ing the bounds of the newly generated subproblems.The load balancing strategy is simple and suited to the structure of the computation,because new subprob-lems are generated during computation.If a processor has no more work,it asks its neighbours one after the other for work.If a processor receives a request for work,it returns a unit of work–if one is available–to the asking processor.The processor sends that unit of work which is nearest to the root of the problem tree and has not been solved yet.The implemented distributed algorithm works asynchronously.The basic rules are provided by the user using the functional language.3Performance EvaluationTo evaluate the performance of task parallel skeletons,we implemented branch-and-bound for the language DFS as a task parallel skeleton in C for a GigaClus-ter GCel1024with1024transputers T805(30MHz)(each with4MByte local memory)running the operating system Parix.Performance measurements for several machine scheduling problems–typical applications of the branch-and-bound method–were made to demonstrate the advantageous application of skeletons.In the following,three cases of a machine scheduling problem for2machines and5products have been considered.The number of possible orders of machine allocation is5!=120.This very small problem size is sufficient to demonstrate the consequences for the distribution of work and the computation performance,if the part of the problem tree,which must be computed,has a different extent.In case(a)the complete problem tree had to be generated.In case(b)only one branch of the tree had to be computed. Case(c)is a case where a larger part of the problem tree than in case(b)had to be computed.Each of the machine scheduling problems has been defined first in the standard functional way and second by use of the branch-and-bound skeleton.The measurements were made using different numbers of processors.First we counted branching steps,i.e.we measured the average overall num-ber of decompositions of subproblems of all processors working together in the computation of the problem.These measurements showed the extend of the computed problem tree working sequentially and parallelly.It became obvious that the overall number of branching steps is increasing in the case of a small number of to be branched subproblems.The local partial knowledge bases and the asynchronous behaviour of the algorithm cause the execution of unnecessary work.If the whole problem tree had to be generated,we observed a decrease of the average overall number of branching steps with increasing number of proces-sors.This behaviour is called acceleration anomaly([2]).Acceleration anomalies occur if the search tree generated in the parallel case is smaller than the one generated in the sequential case.This can happen in the parallel case because ofbranching several subproblems at the same time.Therefore it is possible tofind an optimum earlier than in the sequential case.Acceleration anomalies cause a disproportional decrease of the average maximum number of branching steps per processor with increasing number of processors,a super speedup.Table2.Average overall number of reduction steps1proc.1proc.4proc.6proc.8proc.16proc.functional skeleton skeleton skeleton skeleton skeleton(a)17197207271848,21792,91074,9709,3(b)5447138,0218,6299,0451,6(c)138118179,8261,8258,6484,8Table3.Average maximum number of reduction steps per processor1proc.1proc.4proc.6proc.8proc.16proc.functional skeleton skeleton skeleton skeleton skeleton(a)1719720727896,0710,2390,5113,1(b)544743,244,747,046,4(c)13811865,566,160,951,7To compare sequential functional programs with programs defined by means of skeletons,we counted reduction steps.The reduction steps include besides branching a problem,the computation of a bound of the optimal solution of a subproblem,the comparison of these bounds for selection and elimination of a subproblem from a set of to be solved subproblems,and the comparison of bounds to determine an optimum.Table2shows the average overall number of reduction steps of all processors participating in the computation.In Table3the average maximum numbers of reduction steps per processor are given.Table2 and Table3clearly show the described effect of an acceleration anomaly.Because the set of reduction steps contains comparison steps of the operation‘selection of subproblems from a set of to be solved subproblems’,the distribution of work causes a decrease of the number of comparison steps for this operation at each processor.Looking at both Table2and Table3it becomes apparent that the numbers of reduction steps in the sequential cases of(a),(b),and(c)of the computation of the problemfirst defined in the standard functional way and second using the skeleton differ.That is caused by different styles of programming in func-tional and imperative languages.In case(a)an obvious decrease of the average maximum number of reduction steps per processor(Table3)caused by the dis-tribution of the subproblems onto several processors is observable.At the same time the average overall number of reduction steps(Table2)is also decreasingas explained before.The distribution of work onto several processors yields a large increase of efficiency in cases when a large part of the problem tree must be computed.In case(b)the average maximum number of reduction steps per processor nearly does not change while the overall number of reduction steps is increasing,because,firstly,subproblems,which are to be branched,are dis-tributed,and secondly,a larger part of the problem tree is computed.Because in case(b)the solution can be found in a short time,working parallelly as well as sequentially,the use of several processors produces overhead only.In case (c)the same phenomena as in case(b)are observable.Moreover,the average maximum number of reduction steps decreases to nearly50%in case of parallel computation in comparison to the sequential computation.4ConclusionThe concept,implementation,and application of task parallel skeletons in a functional language were presented.Task parallel skeletons appear to be a nat-ural and elegant extension to functional programming languages.This has been shown using the language DFS and a parallel branch-and-bound skeleton as an example.Performance evaluations showed that using the implemented skeleton forfinding solutions for a machine scheduling problem is performance better, especially if a large part of the problem tree has to be generated.Also in the case of the necessity to compute a smaller part of the problem tree only,a dis-tribution of work is advantageous.Acknowledgements The author would like to thank Herbert Kuchen and Hermann H¨a rtig for discussions,helpful suggestions and comments. References1.Botorog,G.H.,Kuchen,H.:Efficient Parallel Programming with Algorithmic Skele-tons.In:Boug,L.(Ed.):Proceedings of Euro-Par’96,Vol.1.LNCS1123.1996.2.de Bruin, A.,Kindvater,G.A.P.,Trienekens,H.W.J.M.:Asynchronous ParallelBranch and Bound and Anomalies.In:Ferreira,A.:Parallel algorithms for irregu-larly structured problems.Irregular’95.LNCS980.1995.3.Cole,M.:Algorithmic Skeletons:Structured Management of Parallel Computation.MIT Press.1989.4.Darlington,J.,Field,A.J.,Harrison,P.G.,Kelly,P.H.J.,Sharp,D.W.N.,Wu,Q.,While,R.L.:Parallel Programming Using Skeleton Functions.In:Bode,A.(Ed.): Parallel Architectures and Languages Europe:5th International PARLE Confer-ence.LNCS694.1993.5.Darlington,J.,Guo,Y.,To,H.W.,Yang,J.:Functional Skeletons for Parallel Co-ordination.In:Haridi,S.(Ed.):Proceedings of Euro-Par’95.LNCS966.1995.6.Park,S.-B.:Implementierung einer datenparallelen funktionalen Programmier-sprache auf einem Transputersystem.Diplomarbeit.RWTH Aachen1995.7.Trienekens,H.W.J.M.:Parallel Branch and Bound Algorithms.Dissertation.Uni-versit¨a t Rotterdam1990.。