第3章 i2c of

c语言程序设计案例教程第二版答案

c语言程序设计案例教程第二版答案篇一:C语言程序设计案例教程第3章参考答案C语言程序设计案例教程(第二版)廖湖声叶乃文周珺人民邮电出版社第三章习题参考答案习题3-1#include<tdio.h>#include<math.h>intmain(){inti,j,c=0;//c用来控制一行输出元素的个数for(i=2;i<100;i++)//判断从2到100之间那个数为素数{ for(j=2;j<=qrt(i);j++)//判断到i的平方根即可减少循环次数{ if(i%j==0)break;}if(j>qrt(i)){printf("%5d",i);c++;//每输出一个数计数器加1if(c%5==0)printf("\n");}}return0;}习题3-2#include<tdio.h>intmain(){inti,n;//n为从键盘上接收的数printf("请输入一个正整数:");canf("%d",&n);for(i=2;i<n;i++)//从2~n依次查找满足条件的数{if(n%i==0)//判断i是否为n的因子printf("%5d",i);}printf("\n");return0;}习题3-3#include<tdio.h>/某韩信点兵问题穷举法实例某/intmain(){intn;printf("假设韩信带兵在1000~10000人之间,则可能的人数为:\n");for(n=1000;n<10000;n++){if(n%5==1&&n%6==5&&n%7==4&&n%11==10)printf("%7d",n);}printf("\n");return0;}习题3-4#include<tdio.h>intmain(){inti,j,k,n;//i,j,k分别为水仙花数n的百位、十位、个位printf("所有的水仙花数为:");for(n=100;n<1000;n++)//对每个三位数进行分解、判断{i=n/100;j=n/10%10;k=n%10;if(n==i某i某i+j某j某j+k某k某k)//判断该三位数是否是其各位数立方和printf("%5d",n);}printf("\n");return0;}习题3-5#include<tdio.h>intmain()int=0,i=99;while(i>=1){=+i某(i+1)某(i+2);i=i-2;}printf("1某2某3+3某4某5+...+99某100某101=%d\n",);return0;}习题3-6#include<tdio.h>intmain(){inta,n,i,a,an;printf("请输入a和n的值:");canf("%d,%d",&a,&n);a=an=a;for(i=2;i<=n;i++)an=an某10+a;//计算第i项,即i个aa=a+an;//累加求和} printf("a+aa+aaa+...+aa...a=%d\n",a);return0;}习题3-7#include<tdio.h>intmain(){intn=1,i;printf("请输入猴子吃桃子的天数:");canf("%d",&i);while(i>1){n=(n+1)某2;i--;}printf("最初有%d个桃子\n",n);return0;}篇二:c语言程序设计教程(第2版)课后题及模拟题参考答案习题1.............................................................. .. (4)1-1填空题............................................................. . (4)1-2思考题............................................................. . (4)1-3编程题............................................................. . (5)习题2.............................................................. .. (6)2-1单选题............................................................. . (6)2-2思考题............................................................. (6)习题3.............................................................. .. (7)3-1选择题............................................................. . (7)题............................................................. (7)3-3编程题............................................................. (8)习题4.............................................................. .. (11)4-1单选题............................................................. . (11)4-2填空题............................................................. . (11)4-3编程题............................................................. (11)习题5.............................................................. .. (16)5-1单选题............................................................. (16)5-2填空题............................................................. (16)题............................................................. .. (16)习题6.............................................................. . (22)6-1单选题............................................................. . (22)6-2填空题............................................................. (22)6-3编程题............................................................. .. (22)习题7.............................................................. . (25)7-1单选题................... (25)7-2填空题............................................................. (25)7-3编程题............................................................. .. (25)习题8.............................................................. . (26)8-1单选题............................................................. (26)8-2填空题............................................................. (26)8-3编程题............................................................. .. (26)习题9............................................................... (30)9-1单选题.............................................................. . (30)9-2填空题.............................................................. . (30)9-3编程题.............................................................. (30)习题10............................................................. . (38)10-1单选题............................................................. .. (38)10-2填空题............................................................. . (38)10-3编程题............................................................. (38)习题11............................................................. .. (41)11-1单选题............................................................. (41)11-2填空题............................................................. (41)习题12............................................................. . (42)12-1单选题............................................................. (42)12-2填空题............................................................. . (42)实验篇............................................................. . (43)实验1熟悉ViualC++6.0可视化集成开发环境 (43)实验2顺序结构程序设计 (43)实验3选择结构程序设计 (43)实验4循环结构程序设计 (44)实验5函数............................................................. . (47)实验6数组............................................................. . (54)实验7指针............................................................. . (58)实验8结构体和共用体 (61)实验9文件............................................................. (63)实验10综合编程 (64)模拟试卷(一)参考答案 (65)模拟试卷(二)参考答案 (67)习题11-1填空题1.函数2.主函数main(),主函数main()3.主函数main()4.函数首部,函数体5.{,}6./某,某/7.顺序结构,选择结构,循环结构8..c,.obj,.e某e1-2思考题1.结构化程序设计是指:为使程序具有一个合理的结构以保证程序正确性而规定的一套如何进行程序设计的原则。

adum1201 电路设计 i2c 隔离

adum1201 电路设计 i2c 隔离1.我们需要为i2c通信设计一个隔离电路。

(We need to design an isolation circuit for i2c communication.)2.这个电路需要能够有效地隔离i2c信号。

(This circuit needs to effectively isolate the i2c signal.)3.我们要确保隔离电路不会影响i2c通信的稳定性。

(We need to ensure that the isolation circuit will not affect the stability of i2c communication.)4.隔离电路需要能够传输i2c数据信号。

(The isolation circuit needs to be able to transmit i2c data signals.)5.我们需要考虑隔离电路对i2c通信速度的影响。

(We need to consider the impact of the isolation circuit on the speed of i2c communication.)6.这个电路需要满足i2c通信的标准要求。

(This circuit needs to meet the standard requirements for i2c communication.)7.我们需要选择合适的隔离元件来设计这个电路。

(We need to select the appropriate isolation components to design this circuit.)8.这个隔离电路需要能够在不同工作条件下都能正常工作。

(This isolation circuit needs to function properly under different working conditions.)9.我们需要保证隔离电路对i2c数据的传输不会出现误差。

外包业务管理制度

外包业务管理制度湖南****科技发展有限公司湖南****科技发展有限公司外包项目管理制度外包项目管理制度目录第1章总则 ..................................................................... (1)1.1 编制目的 ..................................................................... . (1)1.2 外包定义 ..................................................................... . (1)1.3 适用范围 ..................................................................... . (1)1.4 外包方式 ..................................................................... . (1)1.5 外包管理人员 ..................................................................... ......................................... 1 第2章外包项目要求 ..................................................................... .. (2)2.1 外包战略 ..................................................................... . (2)2.2 承包商的选择 ..................................................................... .. (2)2.3 外包项目计划书 ..................................................................... . (2)2.4 外包业务流程 ..................................................................... .. (2)2.5 项目管理角色 ..................................................................... .. (3)2.6 风险因素的识别 ..................................................................... ..................................... 4 第3章项目外包过程管理 ..................................................................... (4)3.1 考核和管控 ..................................................................... (4)3.2 项目管理的要求 ..................................................................... . (5)3.3 人员管理要求 ..................................................................... .. (6)3.4 项目验收要求 ..................................................................... .. (7)3.5 违约行为的处理 ..................................................................... ..................................... 7 第4章附则 ..................................................................... (8)第1章总则1.1 编制目的为使本公司外包项目管理更加规范合理,约束参不外包项目人员的行为,确保项目外包期间公司信誉的维护,幵提升业务效率,实现项目外包的戓略目标,特制定本制度。

DSP-IIC

一般DSP上面都集成了I2C模块,这样在连接外部器件时可以很方便的控制外部的器件。

I2C 基本上都是用于外部控制的,因为是是串行总线。

在我们的实验板上I2C总线连接到了两个从设备上面,一个是我们的eeprom,另一个是我们的音频芯片AIC23。

通过I2C协议我们写入和读取eeprom数据,控制AIC23的声音一些属性!简介一下I2C协议的规则:一. 技术性能:工作速率有100K和400K两种;支持多机通讯;支持多主控模块,但同一时刻只允许有一个主控;由数据线SDA和时钟SCL构成的串行总线;每个电路和模块都有唯一的地址;每个器件可以使用独立电源二. 基本工作原理:以启动信号START来掌管总线,以停止信号STOP来释放总线;每次通讯以START开始,以STOP结束;启动信号START后紧接着发送一个地址字节,其中7位为被控器件的地址码,一位为读/写控制位R/W,R/W位为0表示由主控向被控器件写数据,R/W为1表示由主控向被控器件读数据;当被控器件检测到收到的地址与自己的地址相同时,在第9个时钟期间反馈应答信号;每个数据字节在传送时都是高位(MSB)在前;写通讯过程:1. 主控在检测到总线空闲的状况下,首先发送一个START信号掌管总线;2. 发送一个地址字节(包括7位地址码和一位R/W);3. 当被控器件检测到主控发送的地址与自己的地址相同时发送一个应答信号(ACK);4. 主控收到ACK后开始发送第一个数据字节;5. 被控器收到数据字节后发送一个ACK表示继续传送数据,发送NACK表示传送数据结束;6. 主控发送完全部数据后,发送一个停止位STOP,结束整个通讯并且释放总线;读通讯过程:1. 主控在检测到总线空闲的状况下,首先发送一个START信号掌管总线;2. 发送一个地址字节(包括7位地址码和一位R/W);3. 当被控器件检测到主控发送的地址与自己的地址相同时发送一个应答信号(ACK);4. 主控收到ACK后释放数据总线,开始接收第一个数据字节;5. 主控收到数据后发送ACK表示继续传送数据,发送NACK表示传送数据结束;6. 主控发送完全部数据后,发送一个停止位STOP,结束整个通讯并且释放总线;DSP中IIC模块框图:1. 总线空闲状态SDA和SCL两条信号线都处于高电平,即总线上所有的器件都释放总线,两条信号线各自的上拉电阻把电平拉高;2. 启动信号START时钟信号SCL保持高电平,数据信号SDA的电平被拉低(即负跳变)。

电路分析基础(英文版)课后答案第三章

0 = ¡26i1 ¡ 90i2 + 124i3

[a] Solving, i1 = 5 A; therefore the 80 V source is delivering 400 W to the circuit.

[b] Solving, i3 = 2:5 A; therefore p8− = (6:25)(8) = 50 W

v1 + v1 ¡ v2 = 4:5

1

8

53

54 CHAPTER 3. Techniques of Circuit Analysis

v2 + v2 ¡ v1 + v2 ¡ 30 = 0

12 8

4

Solving, v1 = 6 V v2 = 18 V Thus, i = (v1 ¡ v2)=8 = ¡1:5 A v = v2 + 2i = 15 V

DE 3.8 Use the lower node as the reference node. Let v1 = node voltage across the 7.5 − resistor and v2 = node voltage across the 2.5 − resistor. Place the dependent voltage source inside a supernode between the node voltages v and v2. The node voltage equations are

3

Techniques of Circuit Analysis

Drill Exercises

DE 3.1 [a] 11,8 resistors, 2 independent sources, 1 dependent source

I2C通讯协议(英文原版)I2C_Spec_en

Connecting devices with different logic levels . . . . . . . . . . . . . . . . . . . . . . . . . 43 Operation of the level shifter . . . . . . . . . . . 44

FORMATS WITH 7-BIT ADDRESSES . . . .13

7-BIT ADDRESSING . . . . . . . . . . . . . . . . .15

Definition of bits in the first byte . . . . . . . . 15 General call address . . . . . . . . . . . . . . . . . 16 START byte . . . . . . . . . . . . . . . . . . . . . . . 17 CBUS compatibility . . . . . . . . . . . . . . . . . . 18

Version 1.0 - 1992. . . . . . . . . . . . . . . . . . . . 3 Version 2.0 - 198. . . . . . . . . . . . . . . . . . . . . 3 Version 2.1 - 1999. . . . . . . . . . . . . . . . . . . . 3 Purchase of Philips I2C-bus components . . 3 THE I2C-BUS BENEFITS DESIGNERS AND MANUFACTURERS . . . . . . . . . . . . . . .4

光模块I2C通信自动化测试系统设计

现代电子技术Modern Electronics TechniqueJan. 2024Vol. 47 No. 22024年1月15日第47卷第2期0 引 言光模块是光纤通信系统的核心部件之一,可以用于实现光纤通信和无线光通信等多种通信方式,广泛应用于数据中心、云计算、移动通信、军事、医疗、航空航天等领域。

通过将数据信号转换为光信号传输,光模块可以实现高速、长距离、大容量、高质量的数据传输,从而满足人们对信息通信不断增长的需求[1]。

I 2C 通信协议是一种串行通信协议,用于连接集成电路之间的通信,也称为二线制串行总线[2]。

在光模块中,I 2C 通信具有重要作用,主机通过它实现对光模块的故障监测和诊断,了解光模块的工作状态和异常情况,及时采取措施进行维修或更换[3]。

同时主机还可以通过I 2C 通信控制光模块的参数和设置,实现在线升级固件等[4]。

I 2C 支持多个光模块的串行连接,可以方便地实现光模块之间的串行连接和控制,简化系统的结构和控制[5]。

XFP 、SFP+光模块一般采用SFF8472协议[6];SFP28或QSFP28光模块一般采用8636协议[7];QSFP 、QSFP+、QSFP‐DD 一般采用CMIS 协议[8];另外还有QSFP 协议、SFP‐DD 协议、SFF8077协议[9]等适用于不同类型的光模块。

这些协议中针对I 2C 通信方式都做了明确的要求。

不同协议规定模块有不同的设备地址,比如:8472协议有两个设备地址A0、A2;而8636协议有一个设备地址A0。

另外,不同协议还规定了不同的页选、密码输入区域、用户可写区等。

本文设计一套测试系统,可兼容不同的协议,针对I 2C 相关性能进行测试。

通过PC 上位机控制示波器和I 2C 测试工装实现自动化测试。

本文设计了一套I 2C 指令字符编码规则,通过解析指令将可执行的高低信号序DOI :10.16652/j.issn.1004‐373x.2024.02.018引用格式:王安忆,王衡,王洪义,等.光模块I 2C 通信自动化测试系统设计[J].现代电子技术,2024,47(2):95‐99.光模块I 2C 通信自动化测试系统设计王安忆, 王 衡, 王洪义, 王 麟(青岛海信宽带多媒体技术有限公司, 山东 青岛 266000)摘 要: 光模块是光纤通信系统的核心部件,不同速率、不同封装的光模块均需通过I 2C 通信方式与主机进行监控数据交换,并实时执行主机发送的控制指令,因此介绍一种针对光模块I 2C 通信的测试系统。

I2C实例解析

实例解析linux内核I2C体系结构(1)一、概述谈到在linux系统下编写I2C驱动,目前主要有两种方式,一种是把I2C设备当作一个普通的字符设备来处理,另一种是利用linux I2C驱动体系结构来完成。

下面比较下这两种驱动。

第一种方法的好处(对应第二种方法的劣势)有:●思路比较直接,不需要花时间去了解linux内核中复杂的I2C子系统的操作方法。

第一种方法问题(对应第二种方法的好处)有:●要求工程师不仅要对I2C设备的操作熟悉,而且要熟悉I2C的适配器操作;●要求工程师对I2C的设备器及I2C的设备操作方法都比较熟悉,最重要的是写出的程序可移植性差;●对内核的资源无法直接使用。

因为内核提供的所有I2C设备器及设备驱动都是基于I2C子系统的格式。

I2C适配器的操作简单还好,如果遇到复杂的I2C适配器(如:基于PCI的I2C适配器),工作量就会大很多。

本文针对的对象是熟悉I2C协议,并且想使用linux内核子系统的开发人员。

网络和一些书籍上有介绍I2C子系统的源码结构。

但发现很多开发人员看了这些文章后,还是不清楚自己究竟该做些什么。

究其原因还是没弄清楚I2C子系统为我们做了些什么,以及我们怎样利用I2C子系统。

本文首先要解决是如何利用现有内核支持的I2C适配器,完成对I2C设备的操作,然后再过度到适配器代码的编写。

本文主要从解决问题的角度去写,不会涉及特别详细的代码跟踪。

二、I2C设备驱动程序编写首先要明确适配器驱动的作用是让我们能够通过它发出符合I2C标准协议的时序。

在Linux内核源代码中的drivers/i2c/busses目录下包含着一些适配器的驱动。

如S3C2410的驱动i2c-s3c2410.c。

当适配器加载到内核后,接下来的工作就要针对具体的设备编写设备驱动了。

编写I2C设备驱动也有两种方法。

一种是利用系统给我们提供的i2c-dev.c来实现一个i2c 适配器的设备文件。

然后通过在应用层操作i2c适配器来控制i2c设备。

AVS10CB-AVS10CBI-AVS100CB中文资料

0.89 Vreg

4.6

V

0.7 Vreg

0.3 Vreg

650

mV

+ 10

µA

VSWON (pin 8)

Low Threshold of Trip Point (switching-on of triac triggering) (3)

VSWOFF (pin 8)

High Threshold of Trip Point (switching-off of triac triggering) (3)

Min. - 12 VSS - 0.5 - 40 - 60

0

Max. 0.5 0.5 + 40 + 150 + 70

TRIAC AVS10CB / AVS10CBI / AVS100CB Tj = +25°C (unless otherwise specified)

Symbol

Parameter

VDRM

ITM = 11A (tp = 10ms, Tj = 25°C)

VDRM rated Gate open

Tj = 25°C AVS10/AVS100 Tj = 110°C AVS10 Tj = 700°C AVS100

Min. 0.2

Max.

Unit

V

1.75

V

10

µA

500

µA

500

µA

CONTROLLER AVS2ACP08 Toper = 25°C (unless otherwise specified)

TRIAC

.HIGH EFFICIENCY AND SAFETY SWITCHING .UNINSULATED PACKAGE :

Kinetis MCUs I2C Timing Configuration说明书

1IntroductionThe I 2C module is popular in most applications. Kinetis MCUs provide strong features on the I 2C module, which is compatible with the I 2C-bus specification and easy to interface with other devices. However, incorrect configuration may cause potential timing issues. This document shows how to configure the I 2C timing of a slave device to meet application needs which apply to Kinetis parts that contain I2C IP instead of LPI2C.2OverviewThe I 2C specification defines detailed timing specifications to enable the I 2C device to follow the same standard and make different devices working together. Figure 1. on page 1 shows the timing definition for tSU:DAT.Figure 1.Definition of I2C timingThe Kinetis IP provides register I2Cx_F to tune the timing. The reference manual provides the reference table on how to impact the I 2C baud rate and data hold time. For the slave mode, this register also heavily impacts the timing and incorrect settings mayContents1 Introduction..........................................12 Overview...............................................13 Timing issues caused byincorrect settings..............................24 Tuning the timing using registerI2Cx_F................................................35 Conclusion. (5)6 References...........................................57 Revision history.. (5)AN12377Tuning I2C Timing In Slave ModeRev. 1 — April 2019Application Notecause timing issues. There might not be a clear explanation in the reference manual, but it must be consulted to get a correct configuration.3Timing issues caused by incorrect settingsWhen configuring the I 2C for a master device, most users know how to configure the I2Cx_F register to get the expected baud rate. However, when enabling it in the slave mode, users are not aware of the I2Cx_F function during the timing tuning and do nothing with the I2Cx_F register. In most customer applications, this possibly causes a timing issue. For example, when it works in the slave mode after events (interrupt of receiving new data or transmitting complete) occur, the slave device drives the SCL low by clock stretching and waits to handle I 2C events. It releases the SCL together with the SDA after writing/reading the I 2C data register when the I2Cx_F is set to 0. This causes the master to detect a wrong signal and fail to meet the SDA setup time requirement.Figure 2.on page 2 shows the captured waveform.Figure 2.I2C signals with clock stretching Figure 3. on page 3 shows the clock stretching timing.Timing issues caused by incorrect settingsFigure 3.Clock stretching timingFigure 3. on page 3 shows the SDA and SCL release at almost the same time. For the I2C timing definition to match the values in Figure 4. on page 3, the tSU:DA T minimum value must be around 100 ns in the fast mode and 250 ns in the standard mode. Therefore, the above timing violates the specification.The tSU:DA T timing and the I2C specification give the characteristic parameters shown in Figure 4. on page 3.Figure 4.Characteristics of tSU:DAT4Tuning the timing using register I2Cx_FConfigure the I2Cx_F register to fix the timing issue and get the tSU:DA T using this formula:SDA setup time = I2C module clock period (s) x mul x SDA setup valueNote to keep the SBRC bit field to be 0 in the I2Cx_C2 register when using this solution. Get the SDA setup value from T able 1. I2C setup value on page 4.Table 1.I2C setup valueICR (hex)SDA SetupValueICR(hex)SDA SetupValueICR(hex)SDA SetupValueICR(hex)SDA SetupValue021016206430256 131120218031320 231220228032320 341324239633384 441424249634384 5515282511235448 6616322612836512 7917442717637704 8618322812838512 98194029160396400A101A402A1603A6400B121B482B1923B7680C121C482C1923C7680D141D562D2243D8960E161E642E2563E10240F221F882F3523F1408ICR : register value of bit field ICR of I2C_FSDA Setup Value : number of I2C function clockTable 1. I2C setup value on page 4 is just for reference. Set the I2Cx_F to have a sufficient margin to meet the I Ctiming.For example, when the I2CxF is set to 0x02 and the I2C module clock frequency is 48 MHz, the setup time is calculated as: Setup time = 1/48 MHz * 1 * 3 = 62.5 nsWhen the I2Cx_F value and the setup time value are bigger, they can get a longer margin by setting the big value to I2Cx_F. However, this causes the I2C bus to drop due to clock stretching. Clock stretching happens in the below condition. At the start of a single-bit communication, the master sends the first SCL clock on the bus and the slave samples this pulse and compares it with its own I2Cx_F configuration. If the slave’s baud rate is lower than the master’s baud rate, I2C IP begins to stretch the bus. For example, if the master’s baud rate is 400 kHz and the slave’s baud rate is configured to be 100 kHz by the I2Cx_F register, the final I2C SCL bus period is composed by the slave’s 100-kHz SCL low period time and master’s 400-kHz SCL high period time. The bus period is 0.5 * (1 / 100 K + 1 / 400 K) seconds, so the SCL bus is about 160 kHz.It is recommended to set the slave's baud rate higher than the master baud rate and give a sufficient margin to meet the I2C timing.Conclusion 5ConclusionThis document introduces a way to tune the I2C timing and meet the specifications by setting I2CxF correctly, which helps customers to solve I2C timing issues.6References•I²C-bus Specification, Version 6.0, 4th of April 2014•KL16 Sub-Family Reference Manual with Addendum (document KL16P80M48SF4RM)•Kinetis KL03 reference manual (document KL03P24M48SF0RM)7Revision historyT able 2. Revision history on page 5 summarizes the changes done to this document since the initial release.Table 2.Revision historyHow To Reach Us Home Page: Web Support: /support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. “Typical” parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including “typicals,” must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: / SalesTermsandConditions.While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer’s applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HIT AG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, ST ARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C‑5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C‑Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and word marks and the Power and logos and related marks are trademarks and service marks licensed by .© NXP B.V. 2019.All rights reserved.For more information, please visit: Forsalesofficeaddresses,pleasesendanemailto:**********************Date of release: April 2019Document identifier: AN12377。

c第3章(1)

结束

【例5.5】 计算器程序(源程序)

switch (op) { case '+': /*处理加法*/ printf("%d + %d = %d\n", data1, data2, data1 + data2); 程序源代码 break; case '-': /*处理减法*/ printf("%d - %d = %d\n", data1, data2, data1 - data2); break; case '*': /*处理乘法*/ printf("%d * %d = %d\n", data1, data2, data1 * data2); break; case '/': /*处理除法*/ if (0 == data2) printf("Division by zero!\n"); else printf("%d/%d = %d\n", data1, data2, data1/data2); break; default: printf("Invalid operator! \n"); }

程序的顺序结构和选择结构

几个遗留问题

实数与0的比较

float n = 0.001; if( n==0 ) { …… }

if (a > b) { max = a; } else { max = b; }

程序的顺序结构和选择结构

单分支控制的if条件语句

有多条语句时必须加{ } 如果不加{ }会怎样? if (a > b) max = a; printf("max=%d\n",max); else max = b; printf("max=%d\n",max);

南京邮电大学C语言课件第3章

第3章顺序结构程序设计3.1 顺序结构程序的基本操作3.2 格式输出函数3.3 格式输入函数3.4 字符输出函数3.5 字符输入函数3.6 习题3.1 顺序结构程序设计的基本操作•如何在程序中给变量赋值•如何进行数据的输入输出?数据的输入与输出应包括以下几项:●用于输入或输出的设备。

●输入或输出数据的格式。

●输入或输出的具体内容。

在C语言中,提供了用于输入与输出的函数,在这些函数中,键盘是标准输入设备,显示器是标准输出设备。

输出设备输入设备另外要注意,如果在程序中要使用C语言所提供的输入函数或输出函数,则在使用前(即在程序的开头)应该使用包含命令将C语言中输入与输出的库函数包含进来。

#include "stdio.h"3.2 格式输出函数C●printf (“格式控制”,输出表) ;格式控制部分要用一对双撇号括起来,它用于说明输出项目所采用的格式。

输出表中的各项目指出了所要输出的内容。

在格式控制中,用于说明输出数据格式的格式说明符总是以%开头,后面紧跟的是具体的格式。

用于输出的常用格式说明符有以下几种。

●十进制形式 %d 或 %md 用于基本整型%ld 或 %mld 用于长整型%u 或 %mu 用于无符号基本整型%lu 或 %mlu 用于无符号长整型●八进制形式 %o 或 %mo 用于基本整型%lo 或 %mlo 用于长整型●十六进制形式 %x 或 %mx 用于基本整型%lx 或 %mlx 用于长整型m 表示输出的整型数据所占总宽度(即列数),当实际数据的位数不 到m 位时,数据前面将用空格补满。

如果在格式说明符中没有用m 来说明 数据所占的宽度,则以输出数据的实际位数为准。

如果在格式说明符中说 明了宽度m ,但实际输出的数据位数大于m ,则也以输出数据的实际位数 为准进行输出。

整型格式说明符3.2.13.2.2 实型格式说明符%f 或%m.nf●十进制数形式●指数形式%e 或%m.ne在输出实型数据时,格式说明符中的m表示整个数据所占的宽度,n表示小数点后面所占的位数。

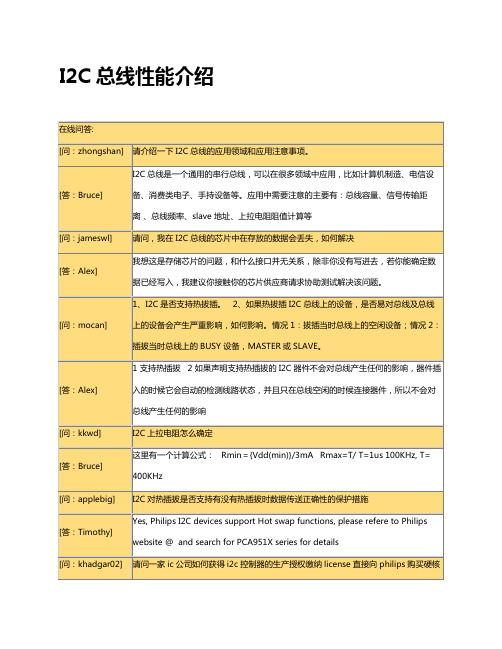

I2C总线性能介绍(疑问解答)二

I2C总线的传输速度有多高它的数据完整性和安全性如何

[答:Bruce]

I2C总线理论上传输速度可以为100KHz(标准)、400KHz(快速)和(高速)。目前还没有成熟的速率的产品。I2C总线是板内总线,总线内部有地址管理和仲裁机制,在总线容量、slave地址等技术指标正确的情况下,数据的完整性和安全性是有保证的

I2C的layout时,对线长、线宽、线距有没有要求

[答:Timothy]

Just remember the max C value on the bus is 400pf.

[问:applebig]

PCA9512对正在使用状态的器件拔出时有什么保护吗比如主发状态的期间拔出时,由谁来发出stop信号

[答:Paul]

[答:Paul]

I2C protocol define each chip one unique slaveif you communicate to several identical ICs, I2C address should be different.If not, the same address ICs will be replied at the same time.

[问:qihong]

请问lpc系列单片机的iic接口是否支持热插拔

[答:Alex]

不支持,I2C总线上的热插拔需要专门的器件支持,比如PCA9511

[问:chenhezhi]

I2C总线在连续写EEPROM时容易出现什么问题,100K的传输速率。

[答:Alex问:david_liao]

I2C总线为同步总线,对抖动性能没有要求

[问:zmyf]

请问高速I2C一般使用多少的波特率呢我们一般使用80K/100Kbits/S,有最优值吗

i2c的接收端电路原理

i2c的接收端电路原理I2C, short for Inter-Integrated Circuit, is a widely used serial communication protocol in the field of microelectronics. It allows multiple devices to communicate with each other using only two wires: a data line (SDA) and a clock line (SCL). I2C has become popular due to its simplicity, flexibility, and ability to connect multiple devices on the same bus. It is commonly used in sensors, memory chips, and other peripheral devices in embedded systems.I2C接口为微电子领域中的一种常用串行通信协议,简称为I2C。

它允许多个设备通过两根线(数据线SDA和时钟线SCL)进行通信。

由于其简单性、灵活性和连接多个设备在同一总线上的能力,I2C已经变得非常流行。

它通常用于嵌入式系统中的传感器、存储芯片和其他外围设备。

At the heart of the I2C protocol lies the concept of a master and multiple slaves. The master is typically a microcontroller or another integrated circuit that initiates communication on the bus. The slaves are devices that respond to the master's commands and can be addressed individually. This allows for efficient communicationbetween different components in a system, with the master controlling the flow of data on the bus.I2C协议的核心概念是主设备和多个从设备。

机器人等级考试五级教材思考题答案

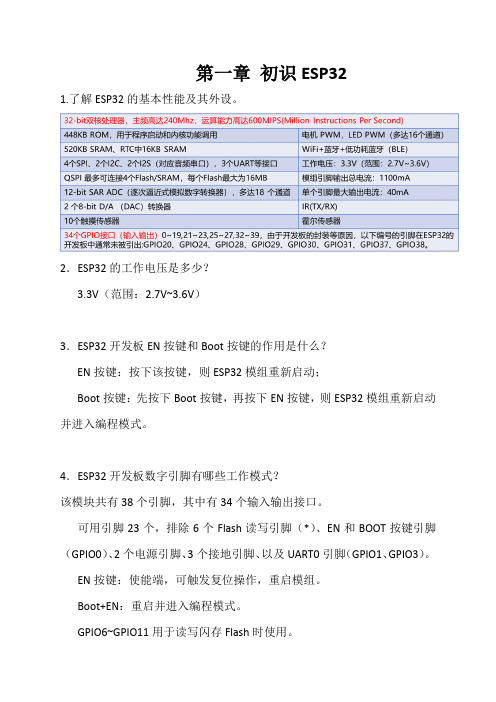

第一章初识ESP321.了解ESP32的基本性能及其外设。

2.ESP32的工作电压是多少?3.3V(范围:2.7V~3.6V)3.ESP32开发板EN按键和Boot按键的作用是什么?EN按键:按下该按键,则ESP32模组重新启动;Boot按键:先按下Boot按键,再按下EN按键,则ESP32模组重新启动并进入编程模式。

4.ESP32开发板数字引脚有哪些工作模式?该模块共有38个引脚,其中有34个输入输出接口。

可用引脚23个,排除6个Flash读写引脚(*)、EN和BOOT按键引脚(GPIO0)、2个电源引脚、3个接地引脚、以及UART0引脚(GPIO1、GPIO3)。

EN按键:使能端,可触发复位操作,重启模组。

Boot+EN:重启并进入编程模式。

GPIO6~GPIO11用于读写闪存Flash时使用。

16个ADC引脚ESP32模块上有10个引脚对电容变化很敏感。

可以将这些引脚连接到某些焊盘(PCB上的焊盘),并将它们用作触摸开关。

I2C:SDA和SCL引脚用于I2C通信。

SPI:4个SPI接口(SPI0、SPI1、VSPI和HSPI),可用于连接显示屏、SD / microSD存储卡模块、外部闪存等。

5.ESP32模拟输出分别有哪几种方式?采用LEDC模拟输出的步骤是什么?方式1:LEDC:基于PWM调制的16通道模拟输出;方式2:SigmfaDelta: 基于SigmaDelta调制的8通道模拟输出;方式3:DAC:硬件(DAC)实现的2个通道的模拟输出。

采用LEDC模拟输出的步骤:LEDC(LED Control)是基于PWM调制实现模拟输出。

引脚不直接产生PWM信号,通过通道产生,一共有16个通道,编号0~15。

实现PWM输出,先设置指定通道PWM参数:频率、分辨率、占空比,然后将该通道映射到指定引脚,该引脚输出对应通道的PWM信号6.如何在多个引脚实现同步模拟输出?先设置指定通道channel的PWM参数,然后将该通道映射到指定引脚。

i2cserialbusv2参数

i2cserialbusv2参数English Answer:The i2cserialbusv2 kernel module provides a serial bus interface for I2C devices. It supports both I2C master and slave modes, and can be used with a variety of I2C devices, including sensors, actuators, and displays.The i2cserialbusv2 kernel module has a number of parameters that can be used to configure its behavior. These parameters are listed below:name The name of the serial bus interface. This parameter is optional, and if it is not specified, adefault name will be generated.addr The I2C address of the device. This parameter is optional, and if it is not specified, the default address will be used.clock The clock frequency of the I2C bus. This parameter is optional, and if it is not specified, the default clock frequency will be used.mode The mode of the I2C bus. This parameter can beset to either "master" or "slave". If it is not specified, the default mode is "master".speed The speed of the I2C bus. This parameter can be set to either "low" or "high". If it is not specified, the default speed is "low".timeout The timeout value for I2C transactions. This parameter is optional, and if it is not specified, the default timeout value will be used.debug The debug level for the I2C serial bus interface. This parameter can be set to either "0" or "1". If it isnot specified, the default debug level is "0".The i2cserialbusv2 kernel module can be used toconfigure and manage I2C devices. It provides a simple andeasy-to-use interface for interacting with I2C devices, and it supports a wide range of I2C devices.Chinese Answer:i2cserialbusv2内核模块为I2C设备提供了一个串行总线接口。

i2c的pec值 -回复

i2c的pec值-回复I2C (Inter-Integrated Circuit) is a popular communication protocol used in electronic systems for devices to exchange data. One essential feature of I2C is its ability to ensure reliable communication by implementing the PEC (Packet Error Checking) feature. In this article, we will delve into the details of the I2C PEC and explore how it contributes to the overall data integrity and system robustness.To understand the PEC value in I2C, we need to first comprehend the basics of the I2C protocol itself. I2C is a synchronous,multi-master, and multi-slave protocol that enables devices to communicate with each other over a shared bus. It utilizes two wires, namely SDA (Serial Data Line) and SCL (Serial Clock Line), for bidirectional serial data transfer.The I2C PEC is a mechanism that adds an additional byte to each transmitted packet. This byte is calculated based on the data bytes in the packet, creating a checksum that enables error detection. The PEC calculation follows a specific algorithm, ensuring that errors in the transmitted data can be identified by the receiving device.The PEC value is generated using a CRC (Cyclic Redundancy Check) algorithm. CRC is a mathematical technique widely used for detecting errors in data transmission. It involves the use of polynomial division to generate a checksum that captures the essence of the data being transmitted. The polynomial used in I2C PEC calculations is known as the "I2C CRC-8" polynomial.Let's explore the step-by-step process of calculating and verifying the PEC value in an I2C transmission:Step 1: InitializationBefore starting the calculation, both the transmitting and receiving devices should agree on using the PEC feature. They need to set the appropriate control registers or configurations to enable PEC calculation and checking.Step 2: Transmitting DeviceWhen the transmitting device desires to send data to the receiving device, it starts by generating the PEC value. To calculate the PEC, the transmitting device follows these steps:- Initialize the CRC with an initial value (typically 0xFF).- Begin iterating over the data bytes in the packet, one by one.- At each iteration, perform a XOR (exclusive OR) operation between the current data byte and the current CRC value.- Shift the CRC value eight bits to the right.- Perform XOR operations with the I2C CRC-8 polynomial depending on the value of the LSB (Least Significant Bit) of the shifted CRC value.- Repeat the previous two steps until all data bytes have been processed.- The final CRC value obtained is the PEC value.Step 3: TransmissionOnce the PEC value is calculated, the transmitting device appends it as an additional byte at the end of the transmission packet. This packet, including the PEC byte, is then sent over the I2C bus to the receiving device. The receiving device starts the process of PEC verification.Step 4: Receiving DeviceUpon receiving the packet, the receiving device performs PEC verification to ensure the integrity of the transmitted data. The steps followed by the receiving device to verify the PEC are asfollows:- Initialize the CRC value with the same initial value as the transmitting device (typically 0xFF).- Begin iterating over the received data bytes, excluding the PEC byte.- Perform the same CRC calculation steps as performed by the transmitting device.- The final calculated CRC value should be zero if no errors are detected.Step 5: Error DetectionThe receiving device compares the calculated CRC value with the received PEC byte. If they match, it indicates that the data transmission was successful. However, if the calculated CRC does not match the received PEC, an error in the data transmission is detected.In conclusion, the PEC value in I2C plays a critical role in ensuring reliable data transmission. By employing the CRC algorithm, it enables error detection, enhancing the overall integrity of exchanged data. The step-by-step process of calculating andverifying the PEC value ensures that errors can be detected and appropriate measures can be taken to maintain the reliability and robustness of the system.。

i2c write和i2c block write -回复

i2c write和i2c block write -回复I2C (Inter-Integrated Circuit) is a widely used communication protocol that allows for easy data exchange between multiple devices. One of the main functionalities of I2C is the ability to write data to devices connected on the bus. In this article, we will explore two specific methods for writing data over I2C: I2C Write and I2C Block Write.I2C Write is a basic operation in which a single byte or a series of bytes is sent from the master device to a slave device on the I2C bus. It is commonly used when the data being transmitted doesn't exceed the maximum supported transmission length of the slave device. Let's take a closer look at the steps involved in performing an I2C Write operation.Step 1: Start ConditionThe master device initiates the communication by sending a Start condition on the bus. This indicates the beginning of a new transmission.Step 2: AddressingThe master then sends the 7-bit address of the slave device it wantsto write to. The eighth bit of the address indicates whether it is a write operation (0) or a read operation (1).Step 3: AcknowledgmentThe addressed slave device responds with an acknowledgment (ACK) if it is present on the bus and ready to receive data. If the slave device doesn't respond, it may indicate that it is not connected or is busy.Step 4: Data TransmissionThe master sends the data byte(s) it wants to write to the slave device. After each byte, the slave device provides an ACK to acknowledge receipt of the data.Step 5: Stop ConditionOnce all the data has been transmitted, the master device sends a Stop condition to indicate the end of the communication.The I2C Write operation works well for transmitting small amounts of data. However, in certain cases where larger data blocks need to be transferred, the I2C Block Write method is more suitable.I2C Block Write is an extension of the I2C Write operation that allows the master device to transmit a series of data blocks to the slave device. This method is particularly ideal when the slave device supports the transmission of block data. The steps involved in an I2C Block Write operation are similar to the I2C Write operation, with a few differences.Step 1: Start ConditionInitiate the communication by sending a Start condition on the bus.Step 2: AddressingSend the slave device's address, indicating a write operation.Step 3: AcknowledgmentWait for the slave device's acknowledgment.Step 4: Block TransmissionThe master device starts sending multiple data bytes to the slave device, constituting a block of data. The number of bytes per block is dictated by the capabilities of the slave device.Step 5: Block Address IncrementationSome slave devices support an auto-increment feature. In such cases, the master can send a control byte indicating the number of data bytes being transmitted in a block and increment the address pointer automatically.Step 6: AcknowledgmentThe slave device acknowledges each block of data received.Step 7: Stop ConditionOnce all the data blocks have been transmitted, the master device sends a Stop condition to end the communication.The I2C Block Write method allows for efficient transmission of larger data blocks. However, it requires support from both the master and slave devices. If the slave device doesn't support this method, it might not respond correctly, leading to potential data corruption or communication failure.In conclusion, both I2C Write and I2C Block Write operations provide mechanisms for writing data over the I2C bus. The choice between the two methods depends on the nature and size of thedata to be transmitted, as well as the capabilities of the slave device. Understanding and utilizing these operations empowers developers to effectively communicate with I2C-enabled devices in various applications.。

i2c使用场景

i2c使用场景I2C (Inter-Integrated Circuit) is a widely used communication protocol for connecting different electronic devices in a variety of applications. It provides a straightforward and efficient way to transmit data between devices, making it ideal for various scenarios. In this article, we will explore some typical use cases of I2C and discuss the related considerations and challenges.1. Interfacing with sensors: Many sensors, such as temperature sensors, humidity sensors, and gas sensors, use I2C as their primary communication interface. I2C allows these sensors to transmit the measured data to microcontrollers or other devices for further analysis and processing. For example, in environmental monitoring systems, I2C enables the connection between sensors and data loggers or control units.2. Controlling peripheral devices: I2C can be used to control various peripheral devices, including LCD displays, LED controllers, motor drivers, and audio codecs. For instance, I2C is commonly employed in display modules to communicate with microcontrollers and update the content displayed on the screen.3. Communication between microcontrollers: I2C facilitates communication between multiple microcontrollers or between a master and multiple slave devices. This enables the development of complex systems where different microcontrollers work together to perform specific tasks. For example, in robotics applications, I2C can be used to exchange information between different microcontrollers responsible for sensor data collection, motor control, and decision-making.4. Memory extension: I2C is utilized for extending the memory of microcontrollers or other devices. EEPROM (Electrically Erasable Programmable Read-Only Memory) chips connected via I2C enable additional storage capacity for storing data or firmware. This is commonly found in embedded systems where the primary memory of microcontrollers may be limited.5. Calibration and configuration of devices: I2C allows for easy calibration and configuration of various devices in different environments. For instance, in smart home systems, I2C can be used to configure sensors, such as motion sensors and light sensors, based on specific user preferences or environmental conditions.6. Industrial automation: I2C finds its application in industrial automation systems for communication between intelligent sensors, actuators, and controllers. This enables efficient data exchange and control in factory automation, process control, and monitoring systems. I2C helps in building scalable and modular industrial systems by enabling easy integration of various devices.Considerations and Challenges:While I2C offers many advantages, it is essential to consider a few key points in its implementation:1. Addressing: Each I2C device needs a unique address for identification. Address conflicts can occur if multiple devices have the same address, resulting in communication errors. Proper planning and addressing assignment are crucial to avoid such conflicts.2. Bus capacitance: I2C operates on an open-drain bus, where devices share a common line for communication. The total capacitance of the I2C bus can impact the signal integrity and limit the maximum achievable communication speed. Repeaters or buffers may be required for large and complex systems to overcome signal degradation.3. Clock synchronization: I2C relies on a shared clock signal for communication. Ensuring proper synchronization between devices is necessary to prevent data corruption. Clock stretching, where a device holds the clock line low, may introduce timing challenges that need to be handled correctly.4. Grounding and noise: Proper grounding techniques and noise suppression methodologies are crucial to maintaining reliable communication in I2C systems. Noise and voltage spikes can interfere with signals and disrupt data transfer. Ground loops should be avoided, and appropriate decoupling capacitors should be implemented.In conclusion, I2C is a versatile and widespread communication protocol used in a wide range of applications. Whether it is interfacing with sensors, controlling peripheral devices, or enabling communication between microcontrollers, I2C provides a reliable and efficient solution. However, challenges related to addressing, bus capacitance, clock synchronization, and noise must be carefully considered and addressed for successful implementation.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

软件学院

SoC

Slide 17/37

可重用标准模型

软核和硬核

和芯片整体一起综合的模块 事先硬化的模块 全定制设计的模块

软件学院

SoC

Slide 18/37

硬

片上系统设计范例

核

软 核

软件学院 SoC Slide 19/37

SoC范例中的软核和硬核 SoC范例中的软核和硬核

硬核

微处理器:设计比较复杂,时序要求严格; 微处理器:设计比较复杂,时序要求严格; 存储器:人工在晶体管级设计完成, 存储器:人工在晶体管级设计完成,严重依赖于 设计工艺。 设计工艺。

全定制集成电路设计方法: 全定制集成电路设计方法:

设计者自行设计出集成电路的掩膜版图, 设计者自行设计出集成电路的掩膜版图,由集成 自行设计出集成电路的掩膜版图 电路制造者根据版图数据制造集成电路。 制造者根据版图数据制造集成电路 电路制造者根据版图数据制造集成电路。

软件学院

SoC

Slide 14/37

半定制设计:基于标准单元。 半定制设计:基于标准单元。基于综合的设 计。

软件学院

SoC

Slide 21/37

时序收敛设计(逻辑) 时序收敛设计(逻辑)

接口设计

大型芯片设计, 大型芯片设计,内部连线延迟不确定性 VDSM工艺中,线负载电容引起的延迟可能比门延 工艺中,线负载电容引起的延迟可能比门延 工艺中 迟大得多 时序驱动布局、 时序驱动布局、布线工具可以处理一些时序上的问 题 但不能更正结构设计中的根本错误(流水级不够) 但不能更正结构设计中的根本错误(流水级不够)

软件学院

SoC

Slide 11/37

设计层次(5) 设计层次(5)

电路级(CMOS反向器)

软件学院

SoC

Slide 12/37

现代IC设计层次 现代IC设计层次 IC

抽象层次 时序单位 基本单元 进程及通信 运算的控制 、运算、 时 理时 、 、 图

SoC Slide 13/37

电路的功能描述 自然语言描述或者相互通 信的进程 行为有限状态机、数据流 图、控制流图 程、 有限状态机 理图 C 电 、电流的 程 元 图、

SoC

Slide 29/37

时序收敛设计(物理) 时序收敛设计(物理)

硬核选择和设计 硬核可能影响全芯片的布局 布线、 布局、 硬核可能影响全芯片的布局、布线、关键路径延 迟等问题 挑选或设计硬核之前, 挑选或设计硬核之前,硬核和可综合的软核的规 布局、布线策略需提前确定 提前确定。 划、布局、布线策略需提前确定。 例子 时钟分配 芯片面积、时钟频率、 芯片面积、时钟频率、目标库起到关键作用 在芯片设计早期, 在芯片设计早期,确定时钟分配结构

ASIC半定制与全定制( ASIC半定制与全定制(2) 半定制与全定制

抽象层次 时序单位 基本单元 进程及通信 运算的控制 电路的功能描述 自然语言描述或者相互通 信的进程 行为有限状态机、数据流 图、控制流图 程、 有限状态机 理图 元 图、

前 端

系统级 算法级 级

数据处理 运算步 时 级

后 端

版图规划(Floorplanning) 版图规划 规划应在设计过程的早期开始 芯片的面积是决定芯片能否满足时序、 芯片的面积是决定芯片能否满足时序、性能和费 是决定芯片能否满足时序 用目标的关键 RTL规划 规划 物理级划分结果与逻辑级划分结果不一致 划分策略

尽可能早的定义逻辑层 把一套全局约束分为多套 划分扫描链并定义IO管脚 基于物理关系定义物理层 划分扫描链并定义 管脚

可重用标准模型

经过良好设计的 核是 核是SoC设计成功的关键 设计成功的关键 经过良好设计的IP核是 设计

规范化:保证产品之间的一致性、 规范化:保证产品之间的一致性、可支持性和易 集成性; 集成性; 简单化:使其易分析、易处理验证、易时序收敛; 简单化:使其易分析、易处理验证、易时序收敛; 局部化:发现问题比解决问题更重要。 局部化:发现问题比解决问题更重要。采用缓冲 的设计方法,使系统局部化;系统级的设计问题 的设计方法,使系统局部化; 不会影响到模块内部。 不会影响到模块内部。

设计层次(2) 设计层次(2)

算法级(温度控制) 熄火 熟了 等待 降温 温度到 达门限

软件学院 SoC Slide 6/37

新任务 升温 温度到 达门限

喂狗

焦了

阶段切换

现代IC设计层次 现代IC设计层次 IC

抽象层次 时序单位 前 端 系统级 算法级 级 后 端 数据处理 运算步 时 基本单元 进程及通信 运算的控制 、运 算、 电路的功能描述 自然语言描述或者相互通信 的进程 行为有限状态机、数据流图、 控制流图 程、 限状态机 元 图、有

软件学院

SoC

Slide 30/37

可验证设计

Design for Verification, DFV

目的:确保验证过的模块或芯片具有 目的:确保验证过的模块或芯片具有100%的功能正 % 确性

基本方法

基于断言 基于断言(Assertion)的验证 断言 的验证 独立的多级接口设计

自底向上的验证策略

软件学院

SoC

Slide 22/37

时序收敛设计(逻辑) 时序收敛设计(逻辑)

接口设计规则

核的输入、 核的输入、输出接口都应该是寄存器的 (Registered) 使得每个模块内部时序问题局部化 使得每个模块内部时序问题局部化 任何一个模块作为单元进行综合时, 任何一个模块作为单元进行综合时,应使用寄存器 综合时 输出 任何一个模块作为单元进行版图规划时, 任何一个模块作为单元进行版图规划时,应使用寄 版图规划时 存器输入和输出

软核

其他模块软核

硬化: 的过程。 硬化:从RTL到GDS II 的过程。 到

软件学院

SoC

Slide 20/37

可重用标准模型

全定制设计

花费较大, 花费较大,提高性能 用于不适合综合的模块(最新 处理器) 用于不适合综合的模块(最新Inter 处理器) 存储器、模拟电路、高速协议的物理层接口 存储器、模拟电路、 使用全定制设计完成系统中的少量关键模块

软件学院 SoC Slide 32/37

可启动和可调试设计

应在设计的开始阶段就开发启动和调试策略 应考虑到芯片第一次上电可能不工作 在芯片中设计相应的调试单元 可控性(Controllability) 可控性 每个核都能够被关闭、 每个核都能够被关闭、开启 在大多数功能仍可正常操作的前提下, 在大多数功能仍可正常操作的前提下,进入调试模式 可观性(Observability) 可观性 增加附加电路, 增加附加电路,以提高可观性 在调试模式下,通过复用 引脚 引脚, 在调试模式下,通过复用I/O引脚,引出重要信号

软件学院

SoC

Slide 7/37

设计层次(3) 设计层次(3)

寄存器级(数字信号处理) MUX 寄存器 时钟 寄存器 选择 时钟

ALU 寄存器 时钟

软件学院 SoC Slide 8/37

现代IC设计层次 现代IC设计层次 IC

抽象层次 时序单位 前 端 系统级 算法级 级 后 端 级 数据处理 运算步 时 时 基本单元 进程及通信 运算的控制 电路的功能描述 自然语言描述或者相互通信 的进程 行为有限状态机、数据流图、 控制流图 元 图、有

软件学院 SoC Slide 28/37

时序收敛设计(物理) 时序收敛设计(物理)

综合策略 自底向上(Bottom-Up)的综合方法 的综合方法 自底向上 芯片级综合组织连接模块、 芯片级综合组织连接模块、修改输出驱动缓冲 顶层的核分为两部分:内部核和输出缓冲器 顶层的核分为两部分:内部核和

软件学院

、运算、 程、 限状态机 、 理图

软件学院

SoC

Slide 9/37

设计层次(4) 设计层次(4)

逻辑门级(RS触发器) S Q

R

Q

软件学院

SoC

Slide 10/37

现代IC设计层次 现代IC设计层次 IC

抽象层次 时序单位 前 端 系统级 算法级 级 后 端 电路级 级 数据处理 运算步 时 时 理时 C 基本单元 进程及通信 运算的控制 、运算、 、 、 电 电路的功能描述 自然语言描述或者相互通信 的进程 行为有限状态机、数据流图、 控制流图 程、 限状态机 理图 、电流的 程 元 图、有

软件学院 SoC

键盘控制

Slide 4/37

现代IC设计层次 现代IC设计层次 IC

抽象层次 时序单位 前 端 系统级 算法级 数据处理 运算步 基本单元 进程及通信 运算的控制 电路的功能描述 自然语言描述或者相互通信 的进程 行为有限状态机、数据流图、 控制流图

后 端

软件学院

SoC

Slide 5/37

Slide 2/37

现代IC设计层次 现代IC设计层次 IC

抽象层次 时序单位 基本单元 进程及通信 电路的功能描述 自然语言描述或者相互通信 的进程

前 端

系统级

数据处理

后 端

软件学院

SoC

Slide 3/37

设计层次(1) 设计层次(1)

系统级 信号转换 数据采集 预处理 火候控制 意外处理 中心主控 机械控制 调料控制 数据存储 LCD显示控制

软件学院

SoC

Slide 0/37

提

纲

相关知识 概述 系统级设计问题

软件学院

SoC

Slide 1/37

典型IC设计流程

系统设计 算法设计 RTL设计 系统验证 算法验证 RTL验证 逻辑综合 向foundry提交网表 Foundry进行版图设计 后仿真

软件学院 SoC

后端流程

前端流程

Foundry返回最终网表 foundry流片