工业以太网协议栈FPGA IP核的实现

基于FPGA的100BASE-TX工业以太网中继器的设计与实现

基于FPGA的100BASE-TX工业以太网中继器的设计与实现周学勋【摘要】In order to improve the performance in real-time and certainty of Industrial Ethernet network,an Ethernet repeater based on FPGA is pared with traditional Ethernet repeater,the repeater uses FPGA chip for data processing,with low-latency features.The Ethernet interface of the repeater uses a professional Ethernet PHY chip,and uses FPGA for data processing,the FPGA procedures including simultaneous detection module,synchronization regeneration module,dual-port RAM and the central control unit.Experimental results show that the Ethernet repeater is compatible with standard Ethernet devices based onpared with traditional Ethernet repeater,the latency is much lower.%为了提高工业以太网的实时性和确定性,设计出一种基于FPGA的以太网中继器。

与传统的以太网中继器相比,该中继器采用FPGA芯片实现数据的处理,具有延时小的特点。

该中继器以太网接口部分采用专业的以太网PHY芯片,数据的转发则由FPGA来完成,FPGA程序包括同步检测模块、同步再生模块、双口RAM 及中央控制模块等几个模块。

FPGA开发全攻略——IP核

FPGA开发全攻略——IP核5.7 FPGA设计的IP和算法应用基于IP的设计已成为目前FPGA设计的主流方法之一,本章首先给出IP的定义,然后以FFT IP核为例,介绍赛灵思IP核的应用。

5.7.1 IP核综述IP(Intelligent Property) 核是具有知识产权核的集成电路芯核总称,是经过反复验证过的、具有特定功能的宏模块,与芯片制造工艺无关,可以移植到不同的半导体工艺中。

到了SOC 阶段,IP核设计已成为ASIC电路设计公司和FPGA提供商的重要任务,也是其实力体现。

对于FPGA 开发软件,其提供的IP核越丰富,用户的设计就越方便,其市场占用率就越高。

目前,IP核已经变成系统设计的基本单元,并作为独立设计成果被交换、转让和销售。

从IP核的提供方式上,通常将其分为软核、硬核和固核这3类。

从完成IP核所花费的成本来讲,硬核代价最大;从使用灵活性来讲,软核的可复用使用性最高。

( 这部分内容前面已经阐述,这里再重申一下)软核(Soft IP Core)软核在EDA设计领域指的是综合之前的寄存器传输级(RTL) 模型;具体在FPGA设计中指的是对电路的硬件语言描述,包括逻辑描述、网表和帮助文档等。

软核只经过功能仿真,需要经过综合以及布局布线才能使用。

其优点是灵活性高、可移植性强,允许用户自配置;缺点是对模块的预测性较低,在后续设计中存在发生错误的可能性,有一定的设计风险。

软核是IP 核应用最广泛的形式。

固核(Firm IP Core)固核在EDA设计领域指的是带有平面规划信息的网表;具体在FPGA设计中可以看做带有布局规划的软核,通常以RTL 代码和对应具体工艺网表的混合形式提供。

将RTL描述结合具体标准单元库进行综合优化设计,形成门级网表,再通过布局布线工具即可使用。

和软核相比,固核的设计灵活性稍差,但在可靠性上有较大提高。

目前,固核也是IP核的主流形式之一。

硬核(Hard IP Core)硬核在EDA 设计领域指经过验证的设计版图;具体在FPGA 设计中指布局和工艺固定、经过前端和后端验证的设计,设计人员不能对其修改。

基于FPGAIP核的FIR设计与实现

佳的频率特性和衰耗特性 , 无论通带还是阻带都

较 为平坦 , 过渡 带窄 , 好地接 近理 想滤波 器 的响 更

应。

须确 保 已 经 安 装 了 D P B i e 具 。进 入 I S ul r工 d P

( 方通 用 电子集 团有 限 公司微 电子部 苏州 256 ) 北 113 摘 要 随着数 字 电路技 术 的 高速 发展 和 高性 能 F G 的普及 , PA 为解 决二 频 机械 抖 动偏 频激 光 陀

螺 中的 因机械 抖动 带 来的信 号噪 声提 供 了新 的选择 和方 法 。FR滤 波 器可 以满足 系统对 幅度 和相 位特 I 性 的严 格要 求 , 免 模 拟 滤 波 器 的温 漂 和 随机 噪 声 等 问题 , 避 而且 具 有精 确 的线性 相 位 和稳 定 的 系统。

免费 I oe 同 时结 合 Ma w rs 司 的 MA . P C r, t ok 公 h T

数字低通滤波器是对高速采样 的数据进行滤

波, 滤除掉 机抖 陀螺 输 出信 号 中随机 抖 动 和其 他 因素 造成 的高频 噪声 。 由于二 频机抖 陀螺 的抖动 频 率一 般 在 30 z~ 0 H 左 右 , 速 采 样 频 率 0H 40 z 高 选 为 1H , 以满 足 采 样定 理 要 求 。1H k z可 k z的定 时采样信 号可 以在 F G 内对 时钟使 能 得到 。数 PA 字低通滤 波器 采用 FR中的等波纹 逼近法 进行设 I 计, 设计 指标 : 采样 频率 为 1H , k z通带下 限截止频 率为 10 z阻带 上 限截 止频 率 为 30 z且 通 带 0H, 0H , 内波 纹 小 于 0 00d 阻 带 内 幅 度 衰 减 大 于 . 0 1B,

FPGA DDS IP核实现_单频 线性调频

FPGA DDS IP 核实现DDS (Direct Digital Synthesizer ),即直接数字频率合成器,本文主要介绍如何调用Xilinx 的DDS IP 核生成某一频率的Sin 和Cos 信号,以及LFM 信号。

1.相关参数的介绍及求解(1)DDS 输出频率输出频率out f 是系统时钟频率clk f 、相位累加器中相位数据位宽)(n B θ和相位增量θ∆的函数。

)(2n B clk out f f θθ∆=因此,要得到输出频率out f ,要求相位增量θ∆为clk Bout f f n )(2θθ=∆如果要采用时分复用的多个通道,则降低每个通道的有效时钟效率。

对于C 个通道,要求相位增量为clk Bout f Cf n )(2θθ=∆(2)频率分辨率频率分辨率f ∆是系统时钟频率clk f 和相位累加器数据位宽)(n B θ的函数。

)(2n B clk f f θ=∆对于时分复用的多通道,频率分辨率随通道数的增加而提高,对于C 个通道:Cf f n B clk )(2θ=∆(3)相位增量相位增量值是无符号的,当相位增量值与相位位宽匹配时,也可以将其看作有符号数。

假设相位增量和相位数据位宽均为N ,如果看成无符号数,范围由0到N 2表示的是(] 3600,的角度范围;如果看成有符号数,则范围变成)1(2--N 到)1(2-N ,相位表示的是[) 180180,-的角度范围。

根据正弦信号的周期性和对称性,两种表示范围内的信号采样是一致的。

相位增量定义了综合其的输出频率。

相位增量是系统时钟频率clk f 、输出频率out f 和相位数据位宽)(n B θ的函数。

clk B out f f n )(2θθ=∆2.线性调频信号线性调频信号的时间函数表达式可表示为2,2[)],2(exp[)(20T T t Kt t f j t s -∈+=ππ其瞬时频率为]2,2[,)(21)(0T T t Kt f t dt d t f -∈+==ϕπ其中,TB K =,B 为信号调频宽度,T 为信号脉宽。

基于FPGA的工业以太网的实现

基于FPGA的工业以太网的实现作者:张孟新来源:《电脑知识与技术》2017年第07期摘要:目前,基于以太网的组网技术在工业市场的发展中处于举足轻重的位置。

因此可以基于IEEE 802.3标准的以太网协议进行以太网的数据传输方式传输标准的网络业务和实时数据。

而基于FPGA高性价比、可随时进行处理器配置的特点,本文通过FPGA的NIOSII核实现嵌入式TCP/IP协议以及以太网MAC协议,并提供标准GMII接口,通过外接PHY实现网络连接。

关键词:FPGANIOS П;TCP/IP协议;以太网MAC中图分类号:TP311 文献标识码:A 文章编号:1009-3044(2017)07-0069-021概述在Altera FPGA处理器上进行的解决方案和硬件配置的同时,软件设计工具也能够提供工程师设计并集成所需要的一切功能。

NiosП软核处理器可以进行以太网堆栈驱动程序的编写与集成以及实现其他功能。

还可以在需要的情况下继续配置第二个处理器进行搭配工作,这样就可以支持更多开发应用层上面的软件。

这种方案可以提供了在单—硬件上面就能很容易满足需求的变化。

不必花费大量开发时间与开发费用来实现当以太网协议导入软件堆栈后,在处理器上运行加载,而是利用现成的编程与编译工具和软件进行堆栈的处理,几乎可以支持所有的以太网标准协议。

而且,仅在FPGA的硬件平台上改动设计时或者进行协议升级时,就不需要进行对每—新协议设计新的PCB板了。

一块PCB板能够集成并支持多种工业以太网的协议,从而不但减轻了企业在开发时期投入的研发经费了,而且降低了持久拥有成本。

NIOS II中实现的工业以太网协议能够在不同的协议标准的设计中与FPGA其他系列的器件之间进行移植,所以可以在下一代产品更新使用相同的IP。

2系统实现方案在本文提到的设计中,NiosП软核处理器不仅可以支持工业以太网控制器的网络协议的配置和管理,还能运行应用层上面的数据报协议(UDP)栈、提供高效精确的时序同步功能,并支持传输层上的双路10/100 PHY收发器的PHY管理和线路诊断功能。

FPGA_ASIC-基于FPGA的工业以太网灵活解决方案

基于FPGA的工业以太网灵活解决方案(基金颁发部门:江苏省自然科学基金委;项目名称:嵌入式无线传感网络在矿区数据采集中的应用研究;编号:BK2006039;基金申请人:王潜平)崔衍 王潜平 马海波(中国矿业大学 计算机科学与技术学院,江苏徐州 221008)摘要:随着工业以太网的发展,工业设备制造商们为使自己的产品更具有市场竞争力,都在寻找一种具有高性价比的解决方案。

本文提出了使用FPGA传送工业以太网协议的设计方法,这种解决方案的灵活性在于只需用一个电路板就能实现传送不同的工业以太网协议,并且具有开发成本低、使用周期长的特点。

本文还介绍了基于FPGA的工业以太网的硬件IP开发的流程以及使用LwIP协议实现其软件IP功能。

关键字:工业以太网;FPGA; LwIP中图法分类号:TP311文献标识码:BA Flexible Solution With FPGA for Industrial EthernetCUI YAN,WANG QIANPING,MA HAIBO(China University of Mining and Technology, Xuzhou, 221008, China)Abstract: With the development of Industrial Ethernet, many industrial equipment manufacturers must find a cost-effective way to support as many Industrial Ethernet protocols as possible in order to compete. This paper puts forward the design of FPGA based on Industrial Ethernet. The flexible solution is that FPGA devices to deliver a multi-standard Industrial Ethernet capability from a single printed circuit board implementation. The benefits of the FPGA-based solution are cost-effective and long lifetime. The hardware IP development flow of FPGA based on Industrial Ethernet and LwIP protocols used to implement software IP are given.Key words: FPGA; Industrial Ethernet; LwIP1 引言现在有很多以以太网为基础的工业通信协议,并都有自己的优缺点,其中有些协议是开源的,这让开发者可以设计出自己的协议。

FPGA中IP核的生成

软核(Soft Core)

| 软核只完成RTL级的行为设计,以HDL的方式提交 使用。该HDL描述在逻辑设计上做了一定优化,必 须经过仿真验证,使用者可以用它综合出正确的门 级网表。

z 按照设计层次的不同,IP核可以分为三种: 软核(Soft Core)、固核(Firm Core) 和硬核(Hard Core)。

IP设计技术概述

| IP技术是针对可复用的设计而言的,其本 质特征是功能模块的可复用性。

| IP通常满足以下基本特征:

z 通用性好 z 正确性有100%的保证 z 可移植性好。

z IP 可复用接口设计标准; z IP 可交付使用文档规范/ 标准; z IP 保护文件/ 标准。这三方面的规范/

标准不是孤立的,而是有机地联系在一 起,共同构成IP 标准体系。

思考题

| IP核概念和种类 | Xilinx中Core的调用方法 | IP核设计流程

z 具有可配置性,以满足不同设计的需要; z 标准接口; z 遵守设计规则,可确保IP 核时序收敛,功

能正确; z 交付的数据、资料完整,便于芯片集成。

IP设计与复用(续)

| IP设计与复用对基于FPGA的嵌入式系统 设计,具有举足轻重的地位。

| 随着FPGA逻辑门密度的不断提高和设计 工具软件的不断加强与优化,FPGA能够 实现越来越多的功能。

固核(Firm Core)

| 固核比软核有更大的设计深度,己完成 了门级综合、时序仿真并经过硬件验 证,以门级网表的形式提交使用。

| 只要用户提供相同的单元库时序参数, 一般就可以正确完成物理设计。

基于FPGA的TCP IP协议设计与实现

基于FPGA的TCP/IP协议设计与实现摘要:以FPGA(现场可编程逻辑门阵列)为控制中心,实现了网络接口芯片的时序控制,进而搭建一种百兆以太网的高速数据传输平台。

实践证明,此平台具有良好的接口扩展性,更便于同计算机进行连接。

此外,此平台拥有较高的数据吞吐率,能够达到接近100Mb/s 的以太网极限吞吐率。

关键词:FPGA;以太网;TCP/IP协议;DM90000、引言随着网络通信技术的飞速发展,越来越多的测试仪器需要将大量数据传送给终端计算机进行解析处理,抑或从PC机传送大量数据给相应设备。

现在常用的数据传输方式(usb、总线)中,虽说数据传输的速率较快(可达400Mb/s),但是传输距离过短成为其不可避免的缺点。

而百兆以太网中点对点间的数据传送距离可达100m,如果借助交换机或者路由器等设备可以实现更远距离传输。

本文以FPGA 为基础,在硬件上完成简化的TCP/IP协议栈,用来获取必须的协议处理机能,实现三态以太网嵌入式系统设计。

1、系统硬件设计该系统以Altera公司的EPIC12型FPGA芯片作为中心控制单元,另外还需两片作为缓存数据用的SRAM,以太网接口芯片采用DM9000。

系统具体硬件框图如图1所示。

DM9000是一款全集成、功能强大、性价比高的快速以太网MAC控制器。

该芯片拥有一个通用处理器接口、10/1()()PHY、EEPROM 和16kB的SRAM。

DM9000支持8位、16位以及32位的接口访问内部存储器,可以支持不同型号的处理器。

该芯片的PHY协议层接口完全可以使用10MBps下的3/4/5类非屏蔽双绞线和100MBps下的5类非屏蔽双绞线,很好地对应IEEE 802.3u规范。

DM9000实现以太网媒体介质访问层(MAC)和物理层(PHY)的功能,其中包含MAC数据帧的组装/拆分与发送接收、地址的识别、CRC编码/校验、MLT-3编码器、接收噪声抑制、输出脉冲形成、超时重传、链路完整性测试、信号极性检测与纠正等。

Ethernet-IP核的设计和FPGA实现

Ethernet IP核的设计和FPGA实现随着网络通信技术和微电子技术的发展,日常生活中所遇到的设备的信息化和智能化不断加强。

而且,结构单一功能简单的设备已经不能满足使用者的需求。

这就使得设备的发展趋势朝着结构复杂化,功能多样化,高度集成化,高度智能化方向发展。

如今随着我国经济社会的发展,soc产品和嵌入式技术得到了广泛的推广和普及。

特别是随着国家提出物联网发展规划以来,Internet和消费电子的智能化迅速发展。

由此产生了嵌入式设备的联网问题。

本文就是基于这样的背景,采用Verilog HDL程序设计语言对Ethernet IP核进行编程设计,并以FPGA实现。

整个IP核的系统设计采用了Top-Down的设计思想。

在每个设计层次之上都可以把系统分为很多个功能模块,该层次的电路的硬件行为可以由这些功能模块来描述,同时下一层次的模块又描述这一层次的模块的行为。

整个设计过程使用Altera的工具软件Quartus II 13.0对Ethernet IP核各模块进行编译和综合,分析各模块的结构以及相互之间的关系,并采用ModelSim 10.1软件对部分模块进行功能仿真和功能分析,验证Ethernet IP核的功能。

在如今科学技术日新月异飞速发展的时代里,发展最快的领域当属电子科学与技术。

而在这一领域飞速发展的背后是以微电子技术为代表的半导体技术的快速发展来作为支撑和推动的。

尤其是随着微电子技术及其制造工艺的发展,使得芯片的集成度更高,设备的功能更加多样化。

这也就推动了各种消费电子,工业设备,环境监测仪器等的快速发展,如智能手机,平板电脑,车载导航仪,网络仪表,污染检测器等等。

这些设备都需要联网,也就都提出了连入网络的要求。

相对于嵌入式系统的RS232,RS485等串口通信接口相比,Ethernet技术更加普及通用,还能够连入Internet,具有明显的优势。

Ethernet极大的方便了人们的生活和生产。

以太网IP核的FPGA验证

1引言随着网络技术的高速发展,以太网已在通信、控制、传输领域得到了普遍的应用。

目前对集成网络功能的SoC (System on a Chip )芯片的应用需求量也在快速增长。

在实际的科研与应用中,FPGA 验证被广为采用,因其可以快速定位SoC 芯片的设计缺陷,同时兼能进行软件程序开发,进而缩短整个项目的开发周期[1-2]。

在此,首先介绍基于FPGA 的以太网验证平台的软硬件架构,然后详细阐述基于该平台的以太网IP 核的验证工作过程。

2以太网IP 核验证平台系统架构以太网基于TCP/IP 协议[3],其参考模型如图1所示。

其中数据链路层和物理层由硬件实现;应用层、传输层、IP 层则由软件实现。

数据链路层分为逻辑链路控制层LLC 和媒体访问控制层MAC 。

此处需要验证的IP 核为MAC 层的功能。

对MAC 控制器的功能验证采用软硬件协调验证的方法[4]。

该验证系统的硬件平台及软件平台架构简介如下:以太网IP 核的FPGA 验证蔡玉辉(中国电子科技集团公司第四十七研究所,沈阳110032)摘要:随着智能互联设备的多元化,具有以太网功能的SoC 芯片得到广泛应用。

片上系统开发验证技术中,FPGA 原型验证是SoC 芯片功能验证的有效途径,可以在设计前期及时发现设计中存在的问题。

从硬件平台和软件平台两方面对基于FPGA 的以太网IP 核验证系统展开研究。

硬件平台采用母板与子板相结合的方式,通过FMC-HPC 连接,将以太网PHY 、JTAG 调试接口等功能集成于子板,增加硬件平台设计的灵活性。

软件平台主要采用基于轻量级的LWIP 协议,以有效减少代码尺寸。

以此设计出的软硬件协同验证平台,可以有效缩短以太网IP 核开发验证周期,降低SoC 芯片的开发成本,提高产品的竞争力。

关键词:以太网IP 核;SoC 验证;软硬件协同验证;FPGA 验证DOI :10.3969/j.issn.1002-2279.2020.04.008中图分类号:TN492文献标识码:B 文章编号:1002-2279(2020)04-0030-03FPGA Verification of Ethernet IP CoreCAI Yuhui(The 47th Institute of China Electronics Technology Group Corporation,Shenyang 110032,China )Abstract:With the diversification of intelligent interconnected devices,SoC with Ethernet function has been widely used.In SoC verification technology,FPGA prototyping verification is an effective way,which can timely find the problems existing in the design at the early stage.The verification system of Ethernet IP core based on FPGA is studied from hardware and software platform.The hardware platform combines motherboard with daughter board,and integrates Ethernet PHY,JTAG debugging interface and other functions on the daughter board through FMC-HPC connection,which increases the flexibility of hardware platform design.The software platform mainly adopts LWIP protocol based on lightweight to effectively reduce the code size.The software and hardware co-verification platform designed in this way can effectively shorten the development verification cycle of Ethernet IP core,reduce the development cost of SoC chip and improve the competitiveness of products.Key words:Ethernet IP core;SoC verification;Co -verification of software and hardware;FPGA verification作者简介:蔡玉辉(1984—),男,辽宁省营口市人,助理工程师,主研方向:集成电路设计。

数据采集系统中TCP_IP硬件协议栈的研究与FPGA实现

摘要数据采集系统广泛地应用于工业控制等诸多领域,随着精细化、智能化、多路采集的待测设备和场景越来越多,对采集传输系统的能力提出了越来越高的要求。

传统的货架数据采集系统很难满足特定的需求,而非标准产品的采集系统有很强的针对性,且价格昂贵、结构复杂,难以适用于普遍的采集应用场景。

因此,实现一个具备高性能、高灵活性和低成本的数据采集系统,是当前社会、工业发展的迫切需求。

随着集成电路与信息科学技术的快速发展,为数据采集系统的高性能、集成化设计提供了新思路。

借助网络卸载引擎思想,基于FPGA实现TCP/IP协议栈的逻辑设计,实现一种具备高传输速率、高可靠性、灵活性和低成本的以太网传输链路。

旨在研究基于硬件可编程器件实现软件协议硬件化的实施方案,为分布式数据采集领域的高速数据卸载和传输链路加速提供一种可行性方案。

本文首先结合数据采集系统和TCP/IP协议的功能特点,提出TCP/IP协议族裁剪方案,只保留保证数据高速传输和可靠性的必要协议。

采用分层处理、模块化的设计方法,按照“接收解析-数据处理-组帧发送”的顺序,实现了以太网TCP/IP协议通信的基本功能。

在此基础上,深入研究TCP关键技术,在FPGA中采用标准算法实现超时与重传;基于RAM设计TCP发送窗口;基于拥塞窗口包计数改进拥塞控制算法,让其在硬件逻辑处理和批量数据高速传输的过程中具备更高的调控效率。

除此之外,提出请求应答队列管理机制、校验和预计算算法、CRC32超前计算算法,提高网络数据的卸载和封装速率。

其次,基于真实的以太网通信数据编写测试激励源,建立全面的仿真。

结合仿真波形详细分析了TCP/IP协议栈的设计细节和功能实现,保证设计在逻辑上的正确性,为实际的测试和应用提供了大量的实例。

最后,搭建千兆以太网实物平台,测试结果表明,TCP/IP硬件协议栈的ARP 应答,ICMP回显应答,UDP数据接收与发送,TCP服务器的连接建立、数据通信、连接终止、超时重传与恢复等功能均正确实现。

基于FPGA的浮点运算器IP核的设计与实现

基于FPGA的浮点运算器IP核的设计与实现摘要浮点运算作为数字信号处理的最基本的运算,具备动态范围大的特点,不仅成为衡量微处理器性能的主要指标之一,而且广泛适用于复杂的数学计算、科学应用和工程设计中,随着多媒体技术的蓬勃发展,浮点运算单元的应用范围越来越广泛,它已经走入了千家万户,用来解决复杂的数字图像处理,移动物体模型的建立,三维动画设计与演示等等。

随着FPGA的出现以及EDA技术的成熟,采用FPGA实现数字信号处理的方法已经显示出巨大的潜力,利用FPGA技术设计浮点乘法器可以缩短产品的开发周期。

本设计提出了一种基于VHDL语言的浮点乘法器的硬件实现方法,就是用VHDL 语言描述设计文件和原理图方式设计,以Altera公司的Cyclone系列产品为硬件平台,以Quartus为软件工具进行模拟仿真,实现了任意以IEEE754标准表示的23位单精度浮点数的乘法运算。

设计中对阶码的溢出进行了研究并进行了处理,同时对结果进行了规格化处理,通过利用FPGA在线可编程的技术,设计出的浮点乘法器更加方便灵活,克服了专用乘法器的不足,更能广泛的应用到各个领域。

关键词:IEEE754,单精度浮点数,乘法器,硬件描述语言,FPGA,QuartusTHE DESIGN AND IMPLEMENTATION OF FLOATING-POINT UNIT IP CORE BASED ON FPGAABSTRACTAs the most basic operation of digital signal processing, floating-point calculation is equipped with the characteristic of dynamic range, it is not only the main measure of microprocessor performance indexes, but also is widely used in complex mathematical calculation, science applications and engineering design. with the vigorous development of multimedia technology, floating point arithmetic unit has been widely used, and it has come home, been used to solve complex problems, such as digital image processing, the establishment of the moving object model, 3-d animation design and demonstrate, etc. With the maturity of FPGA presence and EDA technology, it has shown great potential to realize digital signal processing by the method of using FPGA, it can cut short the development cycle by using the FPGA technology design floating-point on time-multiplier. The design is proposed based on VHDL language of floating on time-multiplier, the hardware realization method is described with VHDL language schematic design documents and Altera design, by the way the Cyclone series products for hardware platform, with Quartus for software tools for simulation,it realized any twenty-three single precision floating-point multiplication which is in the IEEE754 standard. Design of order yards was studied and spill the processing, and the results are the normalized processing, by using the on-line programmable FPGA technology, design the floating-point greater flexibility on time-multiplier, overcome the deficiency of special on time-multiplier, more can widely used in various fields.KEY WORDS:IEEE754,float,multiplier unit,VHDL,FPGA,Quartus目录前言 (1)第1章绪论 (3)§1.1 引言 (3)§1.2 浮点数的格式 (3)§1.2.1 一般浮点数表示方法 (3)§1.2.2 IEEE754标准表示的浮点数 (4)§1.2.3 浮点数的规格化 (5)§1.2.4 特殊浮点数 (5)§1.3 浮点乘法器的原理 (6)第2章EDA工具介绍 (8)§2.1 EDA技术及其发展 (8)§2.2 EDA设计流程及其工具 (8)§2.2.1 设计流程 (8)§2.2.2 HDL简介 (10)§2.2.3 Quartus II简介 (10)第3章整体框架设计及功能模块介绍 (11)§3.1 设计思路 (11)§3.2 预处理模块 (11)§3.3 定点乘法器 (12)§3.3.1 IEEE754舍入模式 (12)§3.3.2 定点乘法器原理 (13)§3.3.3 定点乘法器模块 (13)§3.4 计算尾数模块 (15)§3.5 计算阶码及溢出处理 (16)§3.5.1 定点加减法原理 (16)§3.5.2 溢出概念与检测方法 (17)§3.5.3 阶码运算原理 (18)§3.5.4 补码模块 (18)§3.5.5 阶码相加模块 (19)§3.5.6 溢出模块 (20)§3.6 数据显示模块 (21)§3.6.1 数据模块 (21)§3.6.2 显示模块 (22)第4章仿真结果及实验验证 (24)§4.1 顶层原理图 (24)§4.2 顶层仿真 (25)§4.2.1 一般情况 (25)§4.2.2 特殊情况 (25)§4.2.3 显示情况 (26)§4.3 引脚锁定 (26)§4.4 硬件平台 (27)§4.4.1 FPGA简介 (27)§4.4.2 芯片选择 (28)§4.5 下载验证 (28)结论 (30)参考文献 (31)致谢 (33)附录 (34)前言21世纪是信息化的时代,信息产业已经成为衡量一个国家经济科技实力的重要标志,集成电路则是信息技术与信息产业的基础,是电子信息产业的命脉。

万兆以太网UDP-IP协议栈在FPGA上实现的研究

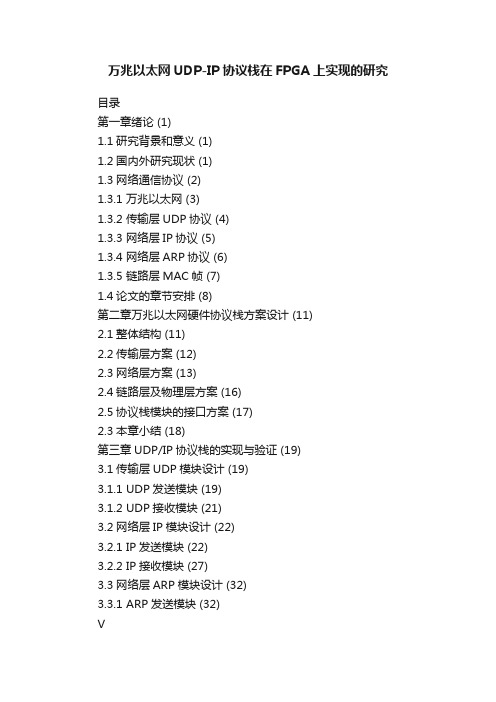

万兆以太网UDP-IP协议栈在FPGA上实现的研究目录第一章绪论 (1)1.1研究背景和意义 (1)1.2国内外研究现状 (1)1.3网络通信协议 (2)1.3.1 万兆以太网 (3)1.3.2 传输层UDP协议 (4)1.3.3 网络层IP协议 (5)1.3.4 网络层ARP协议 (6)1.3.5 链路层MAC帧 (7)1.4论文的章节安排 (8)第二章万兆以太网硬件协议栈方案设计 (11)2.1整体结构 (11)2.2传输层方案 (12)2.3网络层方案 (13)2.4链路层及物理层方案 (16)2.5协议栈模块的接口方案 (17)2.3本章小结 (18)第三章UDP/IP协议栈的实现与验证 (19)3.1传输层UDP模块设计 (19)3.1.1 UDP发送模块 (19)3.1.2 UDP接收模块 (21)3.2网络层IP模块设计 (22)3.2.1 IP发送模块 (22)3.2.2 IP接收模块 (27)3.3网络层ARP模块设计 (32)3.3.1 ARP发送模块 (32)V3.3.2 ARP接收模块 (33)3.3.3 ARP缓存表 (34)3.4链路层MAC控制器及物理子层设计 (37) 3.4.1 FIFO模块 (38)3.4.2 10G-MAC控制器 (39)3.4.3 XGMII接口模块 (40)3.4.4 物理子层PCS/PMA模块 (40)3.5验证方案 (40)3.6仿真测试 (43)3.7本章小结 (46)第四章一个应用系统的案例设计 (47)4.1电源模块设计 (47)4.2时钟模块设计 (48)4.3外围电路设计 (49)4.3.1 SFP+接口设计 (49)4.3.2 DDR3模块设计 (51)4.3.3 88SM9705设计 (51)4.3.4 PCIe接口设计 (52)4.3.5 SA TA接口设计 (54)4.3.6 SAS接口设计 (55)4.3.7 SPI Flash设计 (55)4.3.8 USB转UART设计 (56)4.3.9 JTAG接口设计 (56)4.4本章小结 (57)第五章总结与展望 (59)5.1总结 (59)5.2展望 (59)参考文献 (61)致谢 (65)VI攻读学位期间发表的学术论文及成果 (67) VIIVIII。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

冉冉红日的博客工业以太网协议栈FPGA IP核的实现随着物联网的广泛应用,在嵌入式系统中,越来越多的设备、传感器使用工业以太网作为通信媒介,因为工业以太网有着速度与安全可靠双重优势。

在较高端设备中,由于存在如DSP、ARM之类的处理器,指令代码运行处理速度很快,再有OS进行管理,此时将以太网网卡芯片驱动程序和协议栈加入进来,比较简单方便,易于设备管理和功能更改,这种方案已经应用的非常成熟了。

在某些低端设备中,只有单片机作为处理器,如果还是像上述那样实现以太网的话,单片机的负荷势必会大大增加,对于与单片机相连的设备的实时性控制就会大大降低。

因此,在要加入以太网通信的设备中选用单片机作为处理器不是一种好方案。

除了单片机、DSP、ARM外,还有一种处理器也被广泛应用,那就是FPGA。

现在FPGA的功能越来越多,片内资源也越来越多。

像新出的ALTERA FPGA内部就已有ARM硬核,在ALTERA的所有系列中都能实现软核CPU,此CPU的运行速度相比一般的单片机来说还要更快些。

但如果用它来管理TCP/IP协议栈,我觉得也就会像单片机一样,负载过重,就像让一个10岁的小孩挑50斤的担子一样。

此外,我个人觉得,软核CPU毕竟没有单片机稳定,在FPGA系统中,让软核CPU只做管理就好了,而像以太网协议栈的这样独立性强,又比较复杂的工作就由一个IP 核来实现。

虽然这样的IP核实现起来不容易,但对于实时性要求高、数据传输速度要求高、稳定性要求高的设备,采用这种方案是非常好的。

因此,我想根据嵌入式设备的特点,简化TCP/IP协议栈的内容,实现嵌入式设备需要的功能,而不需要的就剔除掉。

比如,不需要那么复杂的ARP管理,只需将缓存上一次有效的IP-MAC地址;如果只用UDP协议,那么就只需实现简易ARP、IP和UDP就可以了。

这样不仅能节约硬件资源,同时简化了程序,简化了逻辑,提高了系统的稳定性,越简单的事物,稳定性越好。

1 NET_STACK IP核概述1.1 IP核功能简介1)此IP核支持TCP/IP协议栈中的ARP(简化)、IP、UDP、TCP(简化)、ICMP-Ping协议,覆盖协议栈中的网络接口层、网际层和传输层,能应用于10/100/1000Mbps网络系统中。

2)此IP核中只处理ARP应答,不发送ARP请求;只有一个MAC-IP对缓冲区,即只保存上次接收到的来自主机的ARP请求中的MAC-IP对。

3) IP协议支持IP首部长度为20,协议类型为IPV4,不支持分片、选项等功能,发送IP包中的TTL值固定为64。

4) TCP协议支持TCP首部长度为20,不支持SACK、窗等选项功能,单次传输最大净负荷数据为1460字节。

5)此IP核支持完整的UDP协议,单次传输最大净负荷数据为1472字节。

6)在IP核配置时UDP和TCP不能同时被包含,ICMP可以和他们组合包含,只需在配置文件中通过宏定义来加载、卸除组件,操作非常简单。

7) IP核中用于缓冲接收和发送的数据的缓存区大小可以独立配置。

8)应用于IP核的网络参数可以动态在线调整。

9)此IP核能应用于交换机组成的局域网络中。

1.2 IP核接口此IP核在UDP模式和在TCP模式下的顶层接口分别如下图1.1和图1.2所示,前缀为nat_的信号为需要设置的网络参数;前缀为L3的信号为与应用层逻辑接口的信号,它遵循Avalon Stream接口协议,其中ready信号对应的readyLatency等于0,data信号的数据模式是大端模式,此接口在SignalTapII中捕获传输奇数字节的时序图如下图1.3所示;前缀为L1的信号为与网络芯片控制器逻辑接口的信号,它也遵循Avalon Stream 接口协议。

图1.1 NET_STACK IP核UDP模式顶层接口图1.2 NET_STACK IP核TCP模式顶层接口图1.3 接口时序图1.3 IP核使用NET_STACK IP核使用非常简单,在应用时可以采用三种方式将此IP核集成到您的系统中:1)采用Verilog源码方式,将此IP核看做一个模块集成到您的系统中;2)采用原理图方式,将此IP的顶层模块转化为原理图符号,进而集成到您的系统中;3)采用组件方式,在SOPC Builder或Qsys中将此IP核转化为一个组件,进而集成到您的系统中。

无论采用哪种方式,在系统工程编译之前,需要做如下工作:1)设置IP核的工作模式,UDP或TCP模式,加载/卸除Ping功能组件;2)设置IP核内接收缓冲区和发送缓冲区RAM的大小;3)设置网络参数:本地物理地址nat_mac_addr、本地IP地址nat_ip_addr和本地端口号nat_port。

2 NET_STACK IP核性能评估2.1资源占用此IP核占用的资源类型只有逻辑资源和片内RAM两种,下图2.1和图2.2分别为IP核在UDP模式和TCP模式下在测试工程中占有的资源情况,目标器件为ALTERA公司的CycloneII系列EP2C35F484C7,开发环境为QuartusII 11.0。

图2.1 NET_STACK IP核UDP模式占用资源情况图2.2 NET_STACK IP核TCP模式占用资源情况2.2 Ping功能Ping功能属于ICMP协议,它是一个非常好用且有用的TCP/IP工具,是网络维护中最重要的一个命令,它主要的功能是检测网络的连通状况和分析网络速度。

此IP核能非常方便地加载和卸除Ping功能组件,只要在net_define.v文档中通过宏ICMP_INCLUDED的定义或取消来控制即可。

在ALTERA公司器件EP2C35F484中编译,综合分析优化参数设置为“Balance”,如下图2.3所示,只占用229个逻辑单元,具体消耗的资源如下图2.4所示。

图2.3 QuartusII中分析综合优化参数图2.3 DOS界面下Ping测试图2.4 局域网络通信测试2.6最高时钟频率在ALTERA公司的CycloneII系列EP2C35F484C7器件,QuartusII 11.0开发环境中的TimeQuest Timing Analyzer组件下测试得到的IP核系统时钟clk最高为122.05MHz。

注:如果需要更高的时钟频率,可以在牺牲资源面积的前提下将系统时钟clk进一步提高。

3参数更改此IP核在应用过程中有如下参数需要修改:1)工作模式,默认值:UDP模式;2)接收和发送缓冲区RAM的大小,默认值:接收和发送RAM大小都为512×2字节;3)网络参数,默认值:MAC=01-02-03-04-05-06,IP=192.168.0.1,PORT=1024。

3.1更改工作模式IP核中包含三个组件:ICMP-Ping组件、UDP组件、TCP组件,在实际应用中需要使用哪些功能,则在net_define.v文件中包含这个组件的宏,其中UDP组件和TCP组件不能同时使用。

例如:要使用Ping功能和UDP通信,则在net_define.v文件将代码修改为://== Protocol Included ==//`define ICMP_INCLUDED 1`define UDP_INCLUDED 1 // UDP和TCP只能选择一个//`define TCP_INCLUDED 13.2更改RAM大小此IP核中的发送通道和接收通道具有独立的数据缓冲区RAM,可以分别进行更改其大小,更改的步骤如下:步骤一:使用QuartusII中的MegaWizard Plug-in Manager进行RAM参数设置,设置细节请参看《工业以太网协议栈NET_STACK IP核技术设计文档》中的章节2.2的内容。

步骤二:更改net_define.v中的RBW和/或TBW的值,此值须和步骤一中设置的参数值一致。

3.3更改网络参数此IP核中的网络参数有本地MAC地址、本地IP地址、本地端口号,当需要更改其中任意一个或多个时,只需在net_stack_top实例化的时候,在接口中赋值即可。

例如,想要将网络参数设置为:MAC地址为01-60-6E-11-02-0F,IP地址为192.168.0.31,本地端口号为6800,则接口参数设置为:.nat_ip_addr (32'hC0A8001F ),.nat_port (16'h1A90 ),.nat_mac_addr (48'h01606E11020F ),在上一篇博文中,介绍了如何在FPGA中实现UDP、ARP、IP子协议及其使用,经过调试、应用后,发现有些地方是可以改进的,比如在接收通道上,对于IP、UDP子协议的分析,首部的分析可以在网络接口层中就解析出来,然后再在IP、UDP模块中检测判断,这样不仅可以加快分析处理的速度,而且可以简化结构、逻辑编写。

在实际应用中,除了UDP被广泛使用外,TCP也常常被应用在嵌入式系统中。

开始一想到TCP的管理,就感觉很复杂,如果在FPGA中实现,肯定不容易,也就没有再细想下去。

后来静下心来,仔细阅读了TCP协议,对TCP状态跳转图进行分析,发现其实不是那么复杂,可以简化,去掉一些复杂功能,只保留最基本的结构,就可以用于一些网络结构简单的嵌入式系统中。

TCP协议之所以复杂,是因为它考虑的很全面,像分片、滑动窗、流量监控等等,它覆盖面很宽,可以满足很多情况的应用,但其最基本的也就是管理连接、发送应答、出错超时重发,重点是看重其是面向连接的,应用层不需要对数据传输进行维护,同时它分为客户端和服务器两种情况。

而对于一些网络结构简单的系统,比如PC机与单板是直连,或中间只有一个路由器,网络上的数据很“规整”,没有无用的数据传输,单板侧作为一个服务器端,接收PC机客户端的访问,然后应答相应的数据,以实现PC机对单板的监控和数据传输。

经过分析,我将TCP协议简化为:首部长度固定,只支持FIN、SYN、ACK功能选项,只作为服务器,一次只负责一个数据包的管理(即缓冲区中只保存一个数据包,只有待此包发送正确后才能接收新的数据包)。

然后,按照上述第一段中提到的结构,采用Verilog HDL语言,在FPGA 中实现了作为服务器功能的TCP传输功能。

经过对时序的分析、修改,再调试,终于在原有TCP/IP协议栈IP核中添加了TCP传输功能,不过出错自恢复功能还不完善,如果出现网络错误,需要从复位开始,重新连接才可以恢复正常。

TCP传输功能还需要在实际应用中锤炼,得到进一步完善。