小数合成器HMC838

可调小数分频合成器曲-最新资料

可调小数分频合成器曲小数分频频率合成技术是20世纪70年代后期发展起来的一种新型合成技术。

它能够协调高工作频率和小频率间隔之间的矛盾,并且具有输出噪声低,抑制寄生边带干扰能力强等优点,因而应用范围很广。

例如在数字移动通信系统的设计过程中,经常采用跳频方法来提高通信系统的抗干扰、抗多径衰落能力。

因而要求快速跳频系统中的超快速跳频PLL能够在几十微秒(?%es)内稳定到所要求的相位和频率。

为达到此要求可采用由两个小数分频频率合成器构成的"乒乓"体系结构。

在这种系统中,当一个频率合成器作为本地振荡器工作时.另一个频率合成器的作用是锁定下一步要求的频率。

锁相频率合成器的工作原理是,当可编程分频器的分频比变化1时,得到输出频率增量为参考频率fr。

当需要提高频率分辨力时,需要减小参考频率fr,而锁相环内的环路滤波器的带宽必须小于参考频率fr,因而环路滤波器的带宽也要压缩。

环路的捕捉时间或跟踪时间就要增长,即频率合成器的频率转换时间加大。

若可编程分频器能够提供小数分频比,则每次改变某位或某几位小数,就能在不降低参考频率的情况下提高频率分辨力了。

虽然数字分频器本身无法实现小数分频,但依然可采用如下方法实现小数分频。

例如,N=7.5的小数分频,若能控制数字分频器先除一次7,再除一次8,这样交替进行,从输出的平均频率观测,即是实现了7.5的小数分频。

因此只要控制整数分频器的分频比按照某特定规律工作,即能实现小数分频。

若能将该特定规律用变量间的关系式表达出来,即是实现了可调小数分频功能了。

现举两个例子用来引导关系式的推出。

若要完成N.F=2.6的小数分频,其中N表示整数部分,F表示小数部分,则只要在每10次分频中,作4次除2,再作6次除3,就可以得到N.F=??2??+3??)=2.6若要完成N.F=62.45的小数分频,则只要在每100次分频中,作55次除62,再作45次除63,即可得到N.F=??6255+6345)=62.45则现总结关系式,若要完成N.F小数分频,N表示整数部分,F 表示小数部分,P表示小数部分F的位数,则:N.F={N??1-F)+(N+1)F}按照此思路,实现小数分频器的电路可由一个基本单环频率合成器和累加器、存储器构成。

基于ADF4157的Σ-△小数分频锁相环频率合成器设计

图 3 示 为 芯 片原 理 框 图 ,L D T 、E为 串行 输 入 时 所 C K、 A E L

相对较差 , 成度低 , 集 越来 越不能满足现代低成本 、 高一致性 、

钟数据和使能控制 ; X U MU O T为输 出信号锁定检测脚 ; P为电 C 荷泵输出。 中, S 其 C R为快锁功能控制 , 它可 以在小频率范围内 信号变换时 陕速锁定 ,它的原理是通过控制 C P输出电流来降

为 (R C2% v。 F A /2XFm

∞ m RⅡ s

式 ( 中第 一 项 为 所需 频 率 , 二 项 为 由小数 分频 形 成 的 1 ) 第

阶调 制 的量 化误 差 。

它将 前 一 级 的 量 化误 差作 为下 一 级 调制 器 的输 入 , 而把 从

噪声推 向远端 , 噪声在信号近端受到很大抑制 , 以被环路 使 可 滤波器滤除 , 从而达到更好的噪声整形效果 。因此 , 采用多阶调

快 速 发 展 , 高 频 率 、 定 度 的要 求 就 越 高 。 对 高稳

荡器输 出信号相位 , 出 两个信号相 位差成正 比的电压作为 取

误 差 电压 来 控 制 V O输 出频 率 , C 实现 稳 定 信 号 输 出 。

整数 分频锁相环频率 合成器存在 高分 辨率 低 噪声 之间

锁 相 式 、 锁 相 式 和 数字 分频 锁 相 式 三 种 。数 字 分 频 锁 相 环 取样

∑一 △小数分频锁相环频率合成器具有很高 的开关速度以 及通过 F G P A控制可以迅速 变频 ,有效地 抑制 了输 出杂散 , 有 效地解决了高鉴相频率和高分辨率的矛盾 , 降低 了输出信号的 相位噪声。 三阶 ∑一 b Al 数分频锁相环的结构 如图 l 所示 。

MAX830中文资料

STEP-DOWN CONVERTER

* CoilCraft DO3316-104

________________________________________________________________ Maxim Integrated Products

1

Call toll free 1-800-998-8800 for free samples or literature.

* THIS THERMAL RESISTANCE NUMBER IS WITH THE DEVICE WELL MOUNTED ON 1 oz. COPPER WITH THERMAL PASTE BETWEEN THE IC AND THE UNDERLYING GROUND PLANE. LOWER THERMAL RESISTANCE IS POSSIBLE (SEE APPLICATIONS SECTION).

NUAL KIT MA ATION U EET L H A S V A E T WS DA FOLLO

___________________________Features

o Input Range: Up to 30V o 1A On-Chip Power Switch o Adjustable Output (MAX830) Fixed Outputs: 5V (MAX831) 3.3V (MAX832) 3V (MAX833) o 100kHz Switching Frequency o Excellent Dynamic Characteristics o Few External Components o 8mA Quiescent Current o 16-Pin SO Package o Evaluation Kit Available

一种高分辨率_小数分频频率合成器

N div = Y 1( Z) + Y 2( Z) ( 1 - Z- 1) + Y 3 ( 1 - Z- 1 ) ( 1

- Z- 1) = N . F ( Z) + ( 1 - Z- 1) 3 E3 ( Z)

( 1)

F er r( Z) = [ N div( Z) - N . F( Z) ] Fref=

4 期

郭桂良等: 一种高分辨率 小数分频频率合成器

5 17

通过比较简单的控制电路来实现大范围的整数/ 小 数分频的变化。经流片验证这种方法分频准确有效。

表 1 MASH 输出译码表 Tab. 1 Coding table for the MASH output

b2

b1

b0

0

0

0

0

0

1

Output level 0 1

1 小数分频频率合成器结构

传统的锁相环频率合成器由压控振荡器、鉴频 鉴相器、环路滤波器、分频器和参考频率源组成。频 率合成器的输出为f VCO = N ×f ref , 其中N 是整数, 用 于改变锁相环的输出频率。而传统的小数分频频率 合成器只有 N 和 N + 1 两种模式, 存在相差的连续 累加, 相位杂散较严重。为了消除杂散用sigm a-delt a 调制器来控制多模分频器的方案被提出[ 4-5] , 这种方 案在 N 不变的情况下, 实现 N . F 时( N 为自然数, . F 为小数) , 可直接利用多模分频器多个周期内平 均得到, 但如果N 和F 都需要大范围内变化, 控制比 较复杂, 对于硬件要求也比较高[ 4-7] 。有些方案芯片 中集成了R A M , 浪费了大量的面积[ 4] ; 而采用DA C/ PF D 的方法, 更是增加了设计的难度和复杂 度[ 7] ; 还有采用复杂的控制逻辑方案, 也增加了电路的开 销和设计复杂度[ 5-6] 。基于此, 文中提出了一种通过 简单控制即可在大范围内实现N 和F 的变化的小数 / 整数分频器, 如图1 所示。实现整数变化时, 不同于 传统小数分频器通过复杂的编程和控制实现, 通过 先设计一个[ - 3, 4] 宽度为 8 的不变窗口, 变化整数 时, 只需将窗口的中心位置进行移动, 窗口中心位置 即为分频的整数部分。小范围内窗口中心位置的移 动通过 c2、c1、c0 来实现, 大范围移动则还需要改变 计数器 B 计数值。控制简单, 电路复杂度低。

基于HMC833的小数分频频率源设计

1基本原理

小数分频锁相环 由鉴 相器 、低通滤波器 、

到 1 0 0 MHz ,归一化相 位噪底有一 2 2 7 d B c / 3 2 . 4 MHz ,二阶整 数边界杂散 出现在 8 5 8 . 8 MH z

Hz ,分辨 率为鉴相 频率 的 1 / 2 2 4 ,芯片封装 是 和 9 2 3 . 6处 ; 这 些 杂 散 都 落 在 环 路 带 宽 外 ,可 L P 6 ,尺 寸仅 为 6 x 6 mm。芯片 其 内部集 成 了 以通过环 路滤波 器加 以衰减 。以前 的小数分频 锁相环芯 片要求 设置模 数,这个模数会产生通

2 . 1 芯 片 介 绍

引言

频 率综合器 作为系 统收发组件 的本振源 广泛应用于在雷 达、通讯、导航 、遥感遥测等 诸多领域 。相较 于整数分频模式 的锁相环 ,小

关 系时 ,杂散边带将 以一定 的偏移频率 出现在

HMC8 3 3是 Hi t i t e公 司 推 出 的 一 款 V CO输 出频 谱上 ,该 偏移频 率 与整数 倍数 的

ห้องสมุดไป่ตู้

带宽,才能达到最佳 相位噪声。 ( 3 )设置 芯片的寄存器 值。调整 电荷 泵 寄存器的增益和偏移幅度对频率综合器的相位 噪声和杂散都有影响。

输 出频率 :8 9 1 . 2 MHz ; 输 出相 位 噪 声: 一 1 2 0 d Bc/Hz @1

k Hz ;

率源的低相噪低杂散设计方 法。

d B 的恶 化 。 输入晶振、鉴相器和分频器 的相位 噪声起主 导 相 位 噪 声 会 受到 大 约 3

+ 曰

3结论

本 文 利 用 小 数 分 频 锁 相 环 芯 片 来 设 计 点

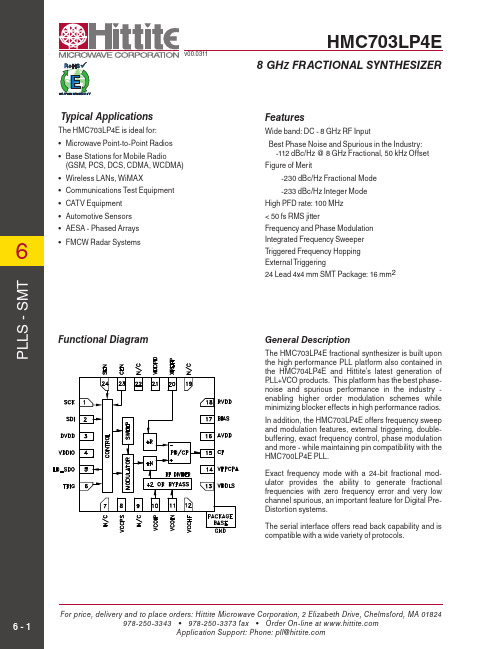

小数合成器HMC703

3.3 5.0

3.5 5.2

V V

3.3V - Current consumption

34 54 74 3 7 13

45 70 95 5 12 16 100

mA mA mA mA mA mA uA V

5V - Current consumption

Power Down Current BIAS Reference Voltage

v00.0311

HMC703LP4E

8 GHZ FRACTIONAL SYNTHESIZER

Typical Applications

The HMC703LP4E is ideal for:

Features

Wide band: DC - 8 GHz RF Input Best Phase Noise and Spurious in the Industry: -112 dBc/Hz @ 8 GHz Fractional, 50 kHz Offset Figure of Merit -230 dBc/Hz Fractional Mode -233 dBc/Hz Integer Mode High PFD rate: 100 MHz < 50 fs RMS jitter Frequency and Phase Modulation Integrated Frequency Sweeper Triggered Frequency Hopping External Triggering 24 Lead 4x4 mm SMT Package: 16 mm2

dBc

VIH/VIL within 50 mV of Vsw

38

47

54

% VDDIO

VDDIO 0 VDDIO=3.3 V VDDIO=3.3 V 115 130 150 135 180 210 1.5 1.7nsec with a 3 pF load 0.5ns+0.2ns/pF 8.2ns+0.2ns/pF

hmc830手册

hmc830手册一、概述HMC830是一款高性能、低功耗的混合信号控制器,专为高性能嵌入式系统设计。

手册提供了关于HMC830控制器的基本信息、技术规格、使用方法、编程指南以及常见问题解答等内容。

通过阅读本手册,您可以了解如何充分发挥HMC830控制器的性能,并确保其在您的应用中稳定运行。

二、产品规格HMC830控制器的主要规格如下:1. 电源电压:1.7V至3.6V2. 工作温度范围:-40℃至+85℃3. 封装:QFN-64封装4. 引脚数目:64个引脚5. 工作频率:150MHz6. 闪存容量:1MB(可配置为2MB)7. RAM容量:512KB(可配置为1MB)8. 串行通信接口:I2C、SPI、UART9. 模拟输入输出:10位ADC和DAC10. 时钟和定时器:4个定时器,1个实时时钟11. 中断控制器:24个外部中断输入12. 调试接口:JTAG和SWD编程接口13. 安全特性:AES加密和安全启动14. 开发工具支持:KeilMDK-ARM、IAR Embedded Workbench等三、使用方法在使用HMC830控制器时,您需要完成以下步骤:1. 硬件设计:根据您的应用需求,设计合适的硬件电路,包括电源、时钟、存储器和外设接口等。

请参考HMC830的引脚图和电路图进行设计。

2. 编程环境设置:选择适合您的开发工具,例如KeilMDK-ARM 或IAR Embedded Workbench。

根据您的偏好和项目需求,设置编程环境。

3. 编程语言:使用C语言进行编程。

HMC830控制器支持使用C 语言进行开发,使您能够充分利用控制器的性能。

4. 程序编写:根据您的应用需求,编写合适的程序。

请参考HMC830的手册和示例代码进行编程。

鉴频鉴相器HMC440的在C波段频率合成中的应用

鉴频鉴相器HMC440的在C波段频率合成中的应用乔通;周迁【摘要】介绍了HITTITE公司一款具有超低相位噪声基底的鉴频鉴相器HMC440在C波段锁相频率合成器中的应用.其特点是鉴相频率高,噪声基底非常低,他集成数控程序分频器,是低相位噪声锁相频率合成器的关键部件.该器件在要求超低相位噪声的载波或本振的地方,如:卫星通信系统、军事通讯系统、Sonet时钟发生系统等,有着很好的应用前景.【期刊名称】《现代电子技术》【年(卷),期】2007(030)013【总页数】3页(P38-39,42)【关键词】鉴频鉴相器;低相位噪声;锁相频率合成器;杂散抑制【作者】乔通;周迁【作者单位】电子科技大学,电子工程学院,电子系统工程研究所,四川,成都,610054;电子科技大学,电子工程学院,电子系统工程研究所,四川,成都,610054【正文语种】中文【中图分类】TN74现代无线电通信和雷达技术的飞速发展,64QAM甚至256QAM等调制的应用,对系统的相位噪声性能提出了更高更严格的要求。

这就要求系统的载波、本振具有更好的相位噪声指标,这便是超低相位噪声的频率合成器的应用背景。

本文介绍了一套应用HITTITE公司的低相噪鉴频鉴相器HMC440设计的低相位噪声C波段锁相跳频源。

1 系统方案介绍输出频率范围:4 428~5 220 MHz;频率步进:36 MHz (23个频点);相位噪声:Δf /kHz0.11.010100£(f) /dBc/Hz-80-90-100-100其系统框图如图1所示。

系统采用了混频锁相的方案。

主要是因为HMC440鉴相频率范围为10~2 800 MHz,所以不能直接由VCO返回鉴相器,而加固定前置分频器又不能满足跳频的要求。

于是,混频锁相成了惟一可行的办法。

另外根据带内相噪估算公式(不考虑晶振的相噪):PN= PDnoisefloor+10 logfPD+20 log(fo/fPD)(dBc/Hz)(1)PN =-233+10 log(36×106)+20 log(4 140/36)=-116 dBc/HzPN =-233+10 log(36×106)+20 log((5 220-4 140)/36)=-128 dBc/Hz图1 系统框图注:HMC440技术资料上给出的-153 dBc/Hz@10 kHz offset @100 MHz,换算到1Hz即为-233 dBc/Hz可见,理论上,要实现上述相噪指标,完全由晶振相噪决定。

一种简单易行的频率合成器

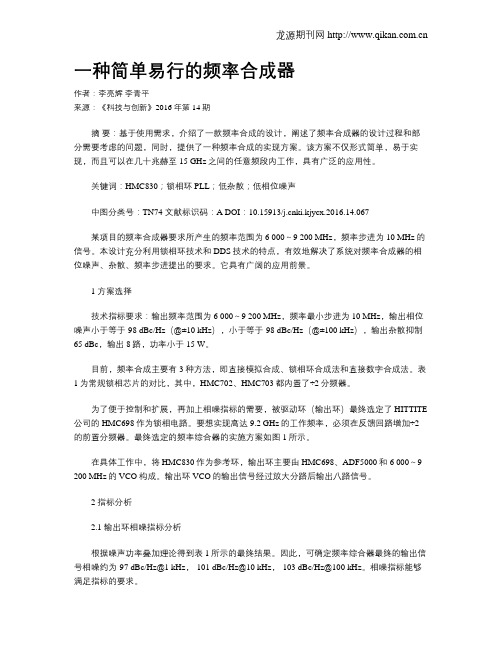

一种简单易行的频率合成器作者:李亮辉李青平来源:《科技与创新》2016年第14期摘要:基于使用需求,介绍了一款频率合成的设计,阐述了频率合成器的设计过程和部分需要考虑的问题,同时,提供了一种频率合成的实现方案。

该方案不仅形式简单,易于实现,而且可以在几十兆赫至15 GHz之间的任意频段内工作,具有广泛的应用性。

关键词:HMC830;锁相环PLL;低杂散;低相位噪声中图分类号:TN74 文献标识码:A DOI:10.15913/ki.kjycx.2016.14.067某项目的频率合成器要求所产生的频率范围为6 000~9 200 MHz,频率步进为10 MHz的信号。

本设计充分利用锁相环技术和DDS技术的特点,有效地解决了系统对频率合成器的相位噪声、杂散、频率步进提出的要求。

它具有广阔的应用前景。

1 方案选择技术指标要求:输出频率范围为6 000~9 200 MHz,频率最小步进为10 MHz,输出相位噪声小于等于-98 dBc/Hz(@±10 kHz),小于等于-98 dBc/Hz(@±100 kHz),输出杂散抑制65 dBc,输出8路,功率小于15 W。

目前,频率合成主要有3种方法,即直接模拟合成、锁相环合成法和直接数字合成法。

表1为常规锁相芯片的对比,其中,HMC702、HMC703都内置了÷2分频器。

为了便于控制和扩展,再加上相噪指标的需要,被驱动环(输出环)最终选定了HITTITE 公司的HMC698作为锁相电路。

要想实现高达9.2 GHz的工作频率,必须在反馈回路增加÷2的前置分频器。

最终选定的频率综合器的实施方案如图1所示。

在具体工作中,将HMC830作为参考环,输出环主要由HMC698、ADF5000和6 000~9 200 MHz的VCO构成。

输出环VCO的输出信号经过放大分路后输出八路信号。

2 指标分析2.1 输出环相噪指标分析根据噪声功率叠加理论得到表1所示的最终结果。

HMC830调试说明引导

HM Band PLLVCO Application Note

Rev: 1.6 目录

Hittite 频综 PLLVCO 芯片性能介绍 ................................................................................................................................................................ 3 Hittite 频综 PLLVCO 一览表(不含微波频段) ............................................................................................................................................ 4 硬件部分 .............................................................................................................................................................................................................. 5 Hittite 的参考设计 ..................................................................................................................................................................................... 5 Reference Input Stage 电路设计 ........................................................................................................................................................... 5 Operating Guide 里面 Ref Input 折算为 Vpp 电压的要求 ........................................................................................................ 7 发射机/接收机的谐波抑制处理................................................................................................................................................................. 8 简单谐波滤波器设计 .................................................................................................................................................................................. 8 Loop Filter 设计和优化 ........................................................................................................................................................................... 10 PLLVCO Regulator 的使用建议 ............................................................................................................................................................ 10 电路设计 Layout 以及调试请注意 ................................................................................................................................................................. 10 Layout 示范 ...................................................................................................................................................................................................... 11 软件部分 ............................................................................................................................................................................................................ 11 HMC Mode & OPEN Mode 设定(仅在上电的过程中有效设置) ................................................................................................ 11 SPI 总线的 Open / HMC Mode 的潜在误操作及控制方法 ............................................................................................................... 14 1 / 24 Hittite Microwave Corporation Confidential

锁相环HMC832的设计与实现

0 引言HMC832是Hittite 公司继HMC830之后推出的又一款25MHz 到3GHz 的频率合成芯片。

该芯片拥有单电源供电、宽带、超低噪声、超低杂散的特性[1]。

具备小数N 分频,内部集成1500 MHz ~3000 MHz 的压控振荡器(VCO),输出分频比1/2/4/6.../60/62,输出频率范围为25 MHz 至3000 MHz。

内部集成相位检波器(PD)和Δ-Σ型调制器能以高达100 MHz 的频率工作,实现更宽的环路带宽和更快的频率调谐,并具备出色的频谱性能。

该器件以其优异的低相位噪声和低杂散性能,广泛应用于无线通信系统中。

1 硬件设计HMC832 的内部功能结构主要包括以下几个部分:参考信号从XREFP 输入到参考支路R 分频器、PFD 鉴频鉴相器、CP 电荷泵,再通过外部环路滤波器,从VTUNE 引脚输入到VCO,通过N 分频器反馈到PFD 鉴频鉴相器形成锁相环路。

其中N 分频器上的Δ-Σ 调制器可以提供小数分频的功能。

VCO 通过CAL 模块获得校准的能力,最后VCO 通过可编程的末级分频器将需要的频率输出到RF 引脚。

其内部系统功能框图如图1。

外围硬件电路主要有参考时钟、环路滤波电路、电源供电三部分。

1.1 晶振的选择为保证频率稳定度和低相噪,本设计采用恒温晶振,在全温度范围内稳定度为±50ppb,频率调整范围为±2ppm ;且具有极好相噪指标。

HMC832时钟参考Reference 输入管脚对时钟输入幅度要求见表1所示。

purity� The paper introduces the basic working principle of HMC832, and provides the software and hardware design in practical application� The experimental results show that the device has excellent performance and good application value�Key words : HMC832; PLL; Phase Noise ; Spurious ; VCO图1 系统功能框图图2 参考输入内部等效电路图1.2 环路滤波环路滤波器件设计主要考虑相位裕度和环路带带宽。

高精度宽带锁相环HMC830LP6GE

环 路 带 宽 ( kHz) 74 90

C1 (pF) 150 270

C2 (nF) 27 3.9

C3 (pF) 220 56

C4 (pF) 220 56

R2 (k ) 0. (k ) 1 1

与市场上流行产品的对比 下图是 HMC830LP6GE 与市场某流行的宽带 PLL 的一些指标比较 XXXX Typical rms jitter 可编程输出电平 FoM 0.5ps -4 to 5 dBm -213dBc/Hz HMC830LP6GE 0.18ps -3 to 6 dBm -227dBc/Hz

FoM 也就是优质因素,这个表示的是归一化到每 Hz 的相位噪声。锁相环芯片该指标的好坏决定了其在所 有频率的相位噪声性能,可以看出,HMC830LP6GE 在该指标上超出很多。 XXXX 产品的杂散约是 -70dBc ,而此项指标 HMC830LP6GE 也有很大的优势,下图是 HMC830LP6GE 在 2113.5MHz 的测量所得。

产品简介 HMC830LP6GE 是内部集成了 VCO 的小数分频锁相环芯片,以及可工作在 100MHz 的相位检测器和 delta-sigma 调制器,这使的其在较宽的环路带宽内有着极好的频谱特性。

性能特征与使用 HMC830LP6GE 的优质因数在整数和小数状态下分别是 -230/-227。双边带 RMS 抖动小于 180fs。精确频率 模式使得输出频率的可以非常小的步进,做到 0Hz 频率误差。HMC830LP6GE 已经在宽带范围内匹配到 50 欧 姆,输出功率动态范围是 9dB (3dB step) ,其唤醒时间只有 250 微秒。 HMC830LP6GE 采用 6*6 塑封表贴封装。在 -40 度到 85 度的温度范围内有优秀的稳定性。 由于该芯片集成了 VCO,PFD ,及分频器,因此使用者只需要设计环路滤波器。由于该芯片还集成了放大 器,环路滤波器的设计也较为简单,只要采用电容加电阻构成的无源滤波器就可以了。 滤波器的拓扑结构及部分参考数值如下。

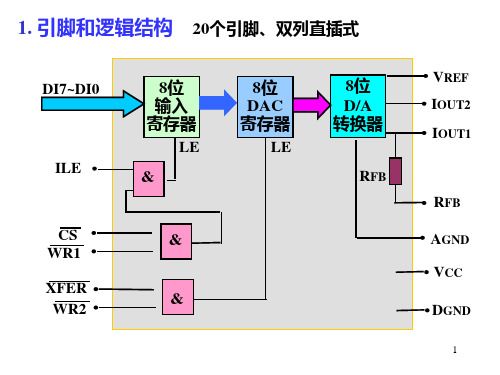

典型DA转换DAC0832芯片4580

XFER

DGND AGND

13

PC总线

D7~D0

+5V

A9~A0

IOW

DI7~DI0

输入 寄存

ILE

LE

WR1 &

地 port1 CS

址

译 码

port2

XFER &

WR2

DAC 寄存

LE

D/A IOUT2 转换

+

Vo

IOUT1

-

RFB

转换一个数据的程序段:

MOV AL, data ;取数字量 MOV DX,port1 OUT DX, AL ;打开第一级锁存 MOV DX, port2 OUT DX, AL ;打开第二级锁存

• 双积分式A/D转换器组成: 积分器A1; 零电压比较器A2; 计数器; 控制逻辑; 标准电压等。

29

双积分式A/D转换

S2

V01

模拟输入

C

VX

S1

VN

标准电压

+ A1

V01 - 比较器 + A2

A/D启动 A/D结束

控制逻辑 ......

控制逻辑 ......

溢

清0

出 进

位

t0

t1

A/D启动 A/D结束

D0 ~ D7 +5V IOW

数据线

地 port1

A0

址

~

译 port2

A9

码

PC总线

DI0

RFB

~ DI7

IOUT1

-

ILE

IOUT2

+

Vo

WR1 WR2

转换一个数据的程序段:

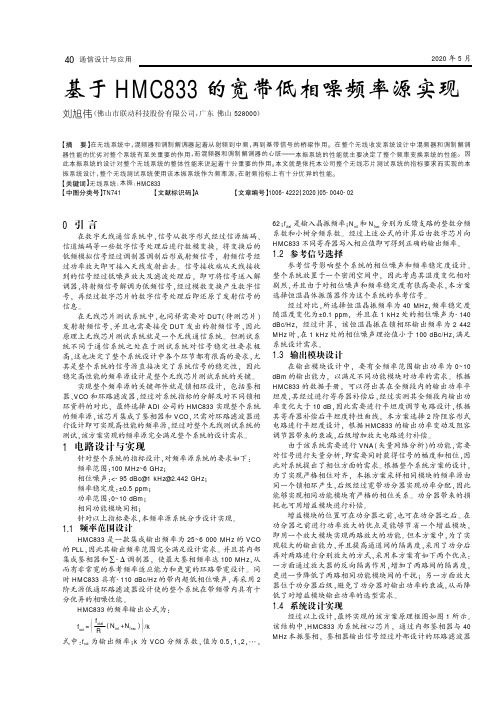

基于HMC833的宽带低相噪频率源实现

2020年5月基于HMC833的宽带低相噪频率源实现刘旭伟(佛山市联动科技股份有限公司,广东佛山528000)【摘要】在无线系统中,混频器和调制解调器起着从射频到中频,再到基带信号的桥梁作用。

在整个无线收发系统设计中混频器和调制解调器性能的优劣对整个系统有至关重要的作用,而混频器和调制解调器的心脏———本振系统的性能就主要决定了整个频率变换系统的性能。

因此本振系统的设计对整个无线系统的整体性能来说起着十分重要的作用。

本文就是依托本公司整个无线芯片测试系统的指标要求而实现的本振系统设计,整个无线测试系统使用该本振系统作为频率源,在射频指标上有十分优异的性能。

【关键词】无线系统;本振;HMC833【中图分类号】TN741【文献标识码】A【文章编号】1006-4222(2020)05-0040-020引言在数字无线通信系统中,信号从数字形式经过信源编码、信道编码等一些数字信号处理后进行数模变换,将变换后的低频模拟信号经过调制器调制后形成射频信号,射频信号经过功率放大即可接入天线发射出去。

信号接收端从天线接收到的信号经过低噪声放大及滤波处理后,即可将信号送入解调器,将射频信号解调为低频信号,经过模数变换产生数字信号,再经过数字芯片的数字信号处理后即还原了发射信号的信息。

在无线芯片测试系统中,也同样需要对DUT(待测芯片)发射射频信号,并且也需要接受DUT发出的射频信号,因此原理上无线芯片测试系统就是一个无线通信系统。

但测试系统不同于通信系统之处在于测试系统对信号稳定性要求极高,这也决定了整个系统设计中各个环节都有很高的要求,尤其是整个系统的信号源直接决定了系统信号的稳定性,因此稳定高性能的频率源设计是整个无线芯片测试系统的关键。

实现整个频率源的关键部件就是锁相环设计,包括鉴相器、VCO和环路滤波器,经过对系统指标的分解及对不同锁相环资料的对比,最终选择ADI公司的HMC833实现整个系统的频率源,该芯片集成了鉴相器和VCO,只需对环路滤波器进行设计即可实现高性能的频率源,经过对整个无线测试系统的测试,该方案实现的频率源完全满足整个系统的设计需求。

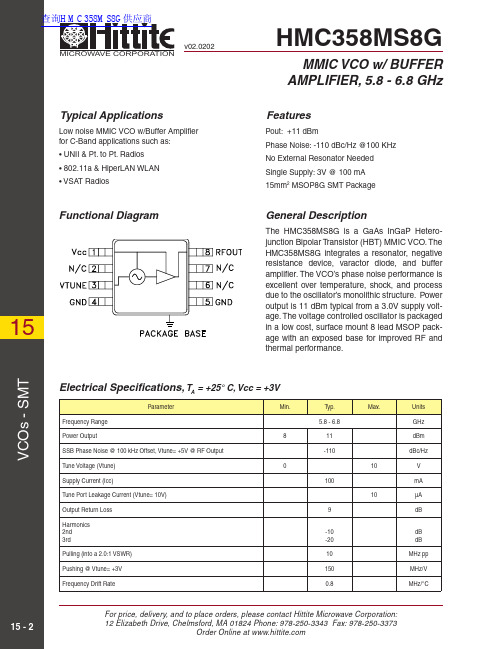

Hittite HMC358MS8G 数据手册

MICROWAVE CORPORATIONV C O s - S M T15HMC358MS8GMMIC VCO w/ BUFFER AMPLIFIER, 5.8 - 6.8 GHzv02.0202General DescriptionFeaturesFunctional Diagram The H MC358MS8G is a GaAs InGaP H etero-junction Bipolar Transistor (HBT) MMIC VCO. The H MC358MS8G integrates a resonator, negative resistance device, varactor diode, and buffer amplifi er. The VCO’s phase noise performance is excellent over temperature, shock, and process due to the oscillator’s monolithic structure. Power output is 11 dBm typical from a 3.0V supply volt-age. The voltage controlled oscillator is packaged in a low cost, surface mount 8 lead MSOP pack-age with an exposed base for improved RF and thermal performance.Pout: +11 dBmPhase Noise: -110 dBc/Hz @100 KHz No External Resonator Needed Single Supply: 3V @ 100 mA 15mm 2 MSOP8G SMT PackageTypical ApplicationsLow noise MMIC VCO w/Buffer Amplifi erfor C-Band applications such as:• UNII & Pt. to Pt. Radios • 802.11a & HiperLAN WLAN • VSA T RadiosElectrical Specifi cations, T A = +25° C, Vcc = +3VParameterMin.Typ.Max.Units Frequency Range 5.8 - 6.8GHz Power Output811dBm SSB Phase Noise @ 100 kHz Offset, Vtune= +5V @ RF Output -110dBc/Hz T une Voltage (Vtune)010V Supply Current (Icc)100mA T une Port Leakage Current (Vtune= 10V)10µA Output Return Loss 9dBHarmonics 2nd 3rd-10-20dB dB Pulling (into a 2.0:1 VSWR)10MHz pp Pushing @ Vtune= +3V 150MHz/V Frequency Drift Rate0.8MHz/°C查询HMC358MS8G供应商15V C O s - S M T5.65.866.26.46.66.877.212345678910O U T P U T F R E Q U E N C Y (G H z )TUNING VOLTAGE (VOLTS)050100150200250300012345678910S E N S I T I V I T Y (M H z /V O L T )TUNING VOLTAGE (VOLTS)02468101214161820012345678910O U T P U T P O W E R (d B m )TUNING VOLTAGE (VOLTS)-120-110-100-90-80-70-6012345678910S S B P H A S E N O I S E (d B c /H z )TUNING VOLTAGE (VOLTS)Frequency vs. Tuning Voltage, T= 25°C AMPLIFIER, 5.8 - 6.8 GHz-150-140-130-120-110-100-90-80-70-60-50-40-30-20-100103104105106107S S B P H A S E N O I S E (d B c /H z )OFFSET FREQUENCY (Hz)Sensitivity vs. Tuning Voltage, Vcc= +3VTypical SSB Phase Noise @ Vtune= +5VPhase Noise vs. Tuning Voltage5.65.866.26.46.66.877.212345678910O U T P U T F R E Q U E N C Y (G H z )TUNING VOLTAGE (VOLTS)Frequency vs. Tuning Voltage, Vcc= +3VOutput Power vs.Tuning Voltage, Vcc= +3V15Absolute Maximum RatingsOutline DrawingAMPLIFIER, 5.8 - 6.8 GHz4. DIMENSIONS ARE IN INCHES [MILLIMETERS].5. DIMENSION DOES NOT INCLUDE MOLDFLASH OF 0.15 mm PER SIDE.6. DIMENSION DOES NOT INCLUDE MOLDFLASH OF 0.25 mm PER SIDE.Typical Supply Current vs. VccNote: VCO will operate over full voltage range shown above.15V C O s - S M TAMPLIFIER, 5.8 - 6.8 GHzPin Descriptions15AMPLIFIER, 5.8 - 6.8 GHzThe circuit board used in the fi nal application shoulduse RF circuit design techniques. Signal lines should have 50 ohm impedance while the package ground leads and backside ground slug should be connected directly to the ground plane similar to that shown. A suffi cient number of via holes should be used to con-nect the top and bottom ground planes. The evalua-tion circuit board shown is available from Hittite upon request.Evaluation PCBList of Materials15V C O s - S M TAMPLIFIER, 5.8 - 6.8 GHzNotes:。

宽频带频率合成器的编程与分析

宽频带频率合成器的编程与分析田佳可;颜锦奎;储甜;陈豪赞【期刊名称】《电子测量技术》【年(卷),期】2014()5【摘要】编写了P89LPC938单片机程序和MATLAB程序,来控制Hittite公司宽带频率合成芯片HMC833LP6GE.MATLAB程序通过RS232接口和单片机对HMC833LP6GE寄存器进行读写.用Agilent频谱仪观测HMC833LP6GE输出信号的频谱特性.改变HMC833LP6GE内部众多寄存器的内容,分析HMC833LP6GE 锁相环的锁存状态、频率的杂散特性以及增益与输出功率的关系.实验表明,HMC833LP6GE数据手册推荐的自动校准方式在实际使用时并不理想,锁相环不易锁存.本文的方法是,在整个VCO频率范围(1 500~3 000 MHz)内逐点改变频率,找到保证锁相环锁存的最佳寄存器数据并保存起来,建立寄存器内容和VCO频率的函数关系,实现手动校准方式.这种方法不但能够保证任何频率下锁存,而且提高了锁存速度,在随机频率跳变下也能完全锁存.HMC833LP6GE的内部寄存器可以控制输出,通过实验找出了最佳的功率频率关系.另外,关于电荷泵电流对杂散的影响也做了讨论.【总页数】5页(P47-51)【关键词】锁相环;HMC833LP6GE;MATLAB;VCO;电荷泵【作者】田佳可;颜锦奎;储甜;陈豪赞【作者单位】上海大学特种光纤与光接入网省部共建重点实验室;爱立信(中国)通信技术有限公司【正文语种】中文【中图分类】TN742【相关文献】1.应用于频率合成器的宽分频比CMOS可编程分频器设计 [J], 鞠英;文光俊;杨拥军2.宽频带数控频率合成器 [J], 庄锡荣;吴周桥3.基于ADF4360-7的宽频带频率合成器设计 [J], 刘晗超4.无线电话锁相环频率合成器原理及其频率编程技术探析与应用 [J], 王天佑5.一种补偿宽频带小数N频率合成器中Sigma-Delta整形噪声的新方法(英文) [J], 石浩;刘军华;张国艳;廖怀林;黄如;王阳元因版权原因,仅展示原文概要,查看原文内容请购买。

华联电子光敏晶体管输出型光耦合器规格书 hpc357x说明书

参数名称 Characteristic

正向电流 Forward Current 正向脉冲电流 Forward Current (Pulsed ) Pulse width ≤ 100μs, frequency 100 Hz

符号 Symbol

IFM

IFP

额定值 Rating

50

1

单位 Unit mA

A

反向电压 Reverse Voltage

Downloaded From

Only after the signature or seal, the product specifications have the force of law.

Downloaded From

华联电子 Xiamen Hualian

规格书 SPECIFICATION

HPC357×

工作温度 Operating Temperature Range

TOPR

-55~110

C

贮存温度 Storage Temperature Range

TSTG

-55~125

C

回流焊接温度 Reflow Soldering (10 seconds )

Th

260

C

总耗散功率 Total Power Dissipation

VF

IF=10mA

反向电流 Reverse Current

IR

输入端子电容 Input Capacitance

CIN

VR =6V V=0V F=1MHz

集电极-发射极反向击穿电压 Collector-Emitter Reverse Breakdown Voltage

V(BR)CEO

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

7HMC838LP6CEv02.1010Functional DiagramFeatures• RF Bandwidth:795 - 945, 1590 - 1890, 3180 - 3780 MHz• Ultra Low Phase Noise-111 dBc/Hz in Band Typ.• Figure of Merit (FOM) -227 dBc/Hz• < 180 fs RMS Jitter• 24-bit Step Size, Resolution 3 Hz typ• Exact Frequency Mode• Built-in Digital Self Test• 40 Lead 6x6 mm SMT Package: 36 mm2Typical Applications• Cellular/4G Infrastructure• Repeaters and Femtocells• Communications Test Equipment• CATV Equipment• Phased Array Applications• DDS Replacement• Very High Data Rate RadiosFRACTIONAL-N SYNTHESIZER WITH INTEGRATED VCO795 - 945, 1590 - 1890, 3180 - 3780 MHzP L L S w / I N T E G R A T E D V C O - S M T7General DescriptionThe HMC838LP6CE is a fully functioned Fractional-N Phase-Locked-Loop (PLL) Frequency Synthesizer with an Integrated Voltage Controlled Oscillator (VCO). The synthesizer consists of an integrated low noise VCO with a tri-band output, an autocalibration subsystem for low voltage VCO tuning, a very low noise digital Phase Detector (PD), a precision controlled charge pump, a low noise reference path divider and a fractional divider.The fractional synthesizer features an advanced delta-sigma modulator design that allows both ultra-fine step sizes and low spurious products. The phase detector (PD) features cycle slip prevention (CSP) technology to allow fas- ter frequency hopping times. Ultra low in-close phase noise and low spurious also allows wider loop bandwidths for faster frequency hopping and low micro-phonics.For theory of operation and register map refer to the “PLLs w/ Integrated VCOs - RF VCOs Operating Guide ”. To view the Operating Guide, please visit and choose HMC838LP6CE from the “Search by Part Number” pull down menu.795 - 945, 1590 - 1890, 3180 - 3780 MHzElectrical Specifications, T A = +25° C, VPPCP, VDDCP, VCC1, VCC2 = 5V ±4%;RVDD, AVDD, DVDD3V, VCCPD, VCCHF, VCCPS = 3.3V ±6% GNDCP = GNDLS = Ground Paddle = 0V, 50 MHz Reference Unless Otherwise Noted7795 - 945, 1590 - 1890, 3180 - 3780 MHz Electrical Specifications (Continued)Note 1: This maximum phase detector frequency can only be achieved if the minimum N value is respected. eg. In the case of fractional feedback mode, the maximum PFD rate = fvco/20 or 100 MHz, whichever is less.P L L S w / I N T E G R A T E D V C O - S M T7Electrical Specifications (Continued)795 - 945, 1590 - 1890, 3180 - 3780 MHz7795 - 945, 1590 - 1890, 3180 - 3780 MHz[1] Fractional Mode, 50 MHz Crystal, R=1Typical Closed Loop Fractional Phase Noise [1]Free Running Phase Noise Typical Tuning Curves vs. Switch PositionTypical VCO Tuning Voltage After CalibrationFree Running VCO Phase Noise Over TemperatureClosed Loop Integer Phase NoiseFREQUENCY OFFSET(Hz)P H A S E N O I S E (d B c /H z )-170-150-130-110-90-701000104105106107108FREQUENCY OFFSET (Hz)P H A S E N O I S E (d B c /H z )835MHz1671MHz3377MHz -180-160-140-120-100-80-60-40-200103104105106107108OFFSET FREQUENCY (Hz)P H A S E N O I S E (d B c /H z )835MHz3378MHz1670MHz900950100010501100012345TUNING VOLTAGE (V)K V C O (M H z /V )n0n2n4n6n8n10n12n14n16n18n20n22n24n26n31fmax fmin fmaxn3001234515001600170018001900VCO FREQUENCYT U N E V O L T A G E A F T E R C A L I B R A T I O N (V )1531fmin fmax -170-160-150-140-130-120-110+27C +85C -40C130013501400145015001550160016501700P H A S E N O I S E (d B c /H z )FREQUENCY (MHz)1 MHz Offset100 kHz Offset10 MHz OffsetP L L S w / I N T E G R A T E D V C O - S M T7Typical VCO Sensitivity vs. Cap @ Fo VoltageFigure of Merit795 - 945, 1590 - 1890, 3180 - 3780 MHzTypical Output Power - Narrow Band MatchTypical Spurious @ 200 kHz from Integer Boundary0102030405060012345TUNING VOLTAGE (V)K V C O (M H z /V )+25C Typ Operating RangeTuning Cap 0, 1929MHz at 2VTuning Cap 15, 1708MHz at 2V Tuning Cap 31, 1540MHz at 2V-160-140-120-100-80-60-40-2001000104105106107108FREQUENCY OFFSET (Hz)P H A S E N O I S E (d B c /H z )400kHz, -80Bc200kHz, -75dBc 1700.200MHz50MHz PFD Fractional Mode200kHz Offset from Integer Boundary 40kHz Loop Bandwidth50MHz, -98dBc-240-230-220-210-2001001000104105106N O R M A L I Z E D P H A S E N O I S E (d B c /H z )FREQUENCY OFFSET (Hz)FOM FloorFOM 1/f NoiseTyp FOM vs Offset-10-5051015208001000200030004000OUTPUT FREQUENCY(MHz)O U T P U T P O W E R (d B m )7795 - 945, 1590 - 1890, 3180 - 3780 MHzPin Descriptions[1] For doubler mode of operation, pin 28 (RF_N) and pin 29 (RF_P) outputs must be shorted together.P L L S w / I N T E G R A T E D V C O - S M T7Outline DrawingPackage InformationNOTES:1. LEADFRAME MATERIAL: COPPER ALLOY2. DIMENSIONS ARE IN INCHES [MILLIMETERS].3. LEAD SPACING TOLERANCE IS NON-CUMULATIVE4. PAD BURR LENGTH SHALL BE 0.15mm MAXIMUM. PAD BURR HEIGHT SHALL BE 0.05mm MAXIMUM.5. PACKAGE WARP SHALL NOT EXCEED 0.05mm.6. ALL GROUND LEADS AND GROUND PADDLE MUST BE SOLDERED TO PCB RF GROUND.7. REFER TO HITTITE APPLICATION NOTE FORSUGGESTED PCB LAND PATTERN.Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.795 - 945, 1590 - 1890, 3180 - 3780 MHz7795 - 945, 1590 - 1890, 3180 - 3780 MHz Evaluation PCB, fo & fo/2 ModesThe circuit board used in the application should use RF circuit design techniques. Signal lines should have50 Ohm impedance while the package ground leads and exposed paddle should be connected directlyto the ground plane similar to that shown. A sufficient number of via holes should be used to connect thetop and bottom ground planes. The evaluation circuit board shown is available from Hittite upon request.Evaluation PCB SchematicTo view this Evaluation PCB Schematic please visit and choose HMC838LP6CE from the “Search by Part Number” pull down menu to view the product splash page.P L L S w / I N T E G R A T E D V C O - S M T7[1] Reference this number when ordering complete evaluation PCB [2] Circuit Board Material: Rogers 4350 or Arlon 25FR and FR4List of Materials for[1]795 - 945, 1590 - 1890, 3180 - 3780 MHz7795 - 945, 1590 - 1890, 3180 - 3780 MHz Evaluation PCB, 2xfo ModeThe circuit board used in the application should use RF circuit design techniques. Signal lines should have50 Ohm impedance while the package ground leads and exposed paddle should be connected directlyto the ground plane similar to that shown. A sufficient number of via holes should be used to connect thetop and bottom ground planes. The evaluation circuit board shown is available from Hittite upon request.Evaluation PCB SchematicTo view this Evaluation PCB Schematic please visit and choose HMC838LP6CE from the “Search by Part Number” pull down menu to view the product splash page.P L L S w / I N T E G R A T E D V C O - S M T7List of Materials for[1]795 - 945, 1590 - 1890, 3180 - 3780 MHz[1] Reference this number when ordering complete evaluation PCB [2] Circuit Board Material: Rogers 4350 or Arlon 25FR and FR4。