半导体能带弯曲上下弯曲的原因

能带弯曲

望各位版友能讨论一下半导体异质结能带弯曲的问题,能带在什么情况下会发生弯曲?会出现何种弯曲?弯曲的幅度有没有定量的标准或测量方法?2007-5-20 21:48 #1zajylf助理工程师精华 0积分 1887 帖子 942 水位 1884 技术分 0这个问题相当有意思!!因为这是做太阳能电池的基础.刚学了些硅太阳能的知识,交流一下我知道的,请高手提些意见!能带弯曲产生主要原因是半导体的载流子的热运动造成空间电偶层,形成内电场.同质结可用一块半导体经掺杂形成P区和N区。

由于杂质的激活能量ΔE 很小,在室温下杂质差不多都电离成受主离子和施主离子.在PN区交界面处因存在载流子的浓度差,故彼此要向对方扩散。

设想在结形成的一瞬间,在N区的电子为多子,在P区的电子为少子,使电子由N区流入P区,电子与空穴相遇又要发生复合,这样在原来是N区的结面附近电子变得很少,剩下未经中和的施主离子ND+形成正的空间电荷。

同样,空穴由P区扩散到N区后,由不能运动的受主离子NA-形成负的空间电荷。

在P区与N区界面两侧产生不能移动的离子区,于是出现空间电偶层,形成内电场,此电场对两区多子的扩散有抵制作用,而对少子的漂移有帮助作用,直到扩散流等于漂移流时达到平衡,在界面两侧建立起稳定的内建电场。

在热平衡条件下,结区有统一的EF;在远离结区的部位,EC、EF、Eν之间的关系与结形成前状态相同。

一般情况下,N型、P型半导体单独存在时,EFN与EFP有一定差值。

当N型与P型两者紧密接触时,电子要从费米能级高的一方向费米能级低的一方流动,空穴流动的方向相反。

同时产生内建电场,内建电场方向为从N区指向P区。

在内建电场作用下,EFN将连同整个N区能带一起下移,EFP将连同整个P区能带一起上移,直至将费米能级拉平为EFN=EFP,载流子停止流动为止。

在结区这时导带与价带则发生相应的弯曲,形成势垒。

势垒高度等于N型、P型半导体单独存在时费米能级之差.这样能带就弯曲了,这是无法避免的,其实从某种角度来说,太阳能电池正是得益于这种弯曲呢#2费米能级就是绝对零度下电子可以占据的最高能级,p-n结接触后,如果费米能级不相等,电子就会从费米能级高的向费米能级低的一方扩散,从而使费米能级发生变化,最终达到平衡时,费米能级相等。

半导体物理学第八章知识点

第8章 半导体表面与MIS 结构许多半导体器件的特性都和半导体的表面性质有着密切关系,例如,晶体管和集成电路的工作参数及其稳定性在很大程度上受半导体表面状态的影响;而MOS 器件、电荷耦合器件和表面发光器件等,本就是利用半导体表面效应制成的。

因此.研究半导体表面现象,发展相关理论,对于改善器件性能,提高器件稳定性,以及开发新型器件等都有着十分重要的意义。

§8.1 半导体表面与表面态在第2章中曾指出,由于晶格不完整而使势场的周期性受到破坏时,禁带中将产生附加能级。

达姆在1932年首先提出:晶体自由表面的存在使其周期场中断,也会在禁带中引入附加能级。

实际晶体的表面原子排列往往与体内不同,而且还存在微氧化膜或附着有其他分子和原子,这使表面情况变得更加复杂。

因此这里先就理想情形,即晶体表面无缺陷和附着物的情形进行讨论。

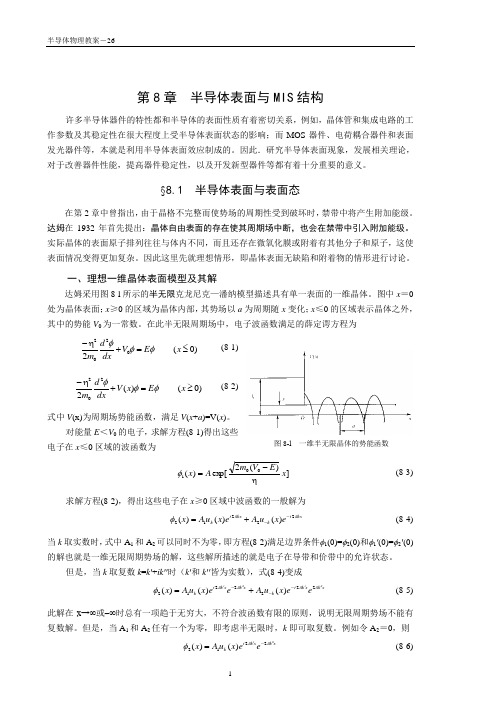

一、理想一维晶体表面模型及其解达姆采用图8-l 所示的半无限克龙尼克—潘纳模型描述具有单一表面的一维晶体。

图中x =0处为晶体表面;x ≥0的区域为晶体内部,其势场以a 为周期随x 变化;x ≤0的区域表示晶体之外,其中的势能V 0为一常数。

在此半无限周期场中,电子波函数满足的薛定谔方程为)0(20202≤=+-x E V dx d m φφφη (8-1))0()(2202≥=+-x E x V dx d m φφφη (8-2)式中V (x)为周期场势能函数,满足V (x +a )=V(x )。

对能量E <V 0的电子,求解方程(8-1)得出这些电子在x ≤0区域的波函数为 ])(2ex p[)(001x E V m A x η-=φ (8-3) 求解方程(8-2),得出这些电子在x ≥0区域中波函数的一般解为kx i k kx i k e x u A e x u A x ππφ22212)()()(--+= (8-4)当k 取实数时,式中A 1和A 2可以同时不为零,即方程(8-2)满足边界条件φ1(0)=φ2(0)和φ1'(0)=φ2'(0)的解也就是一维无限周期势场的解,这些解所描述的就是电子在导带和价带中的允许状态。

半导体物理参考答案第六章

= − qNd 2ε n

(x

+

xn )2

+ ϕin (−xn )

ϕip (x)=

qNa εp

(x

−

xp )2

+ ϕin (xp )

则:

ϕin =

ϕin (−xn ) − ϕin (0) =

qNd 2ε n

xn 2

ϕip

=ϕin (0) − ϕin (xp )

=qNa 2ε p

xp2

(−xn ≤ x ≤ 0) (0 < x ≤ xp )

xp2

Байду номын сангаас

则耗尽层厚度为:

xp

=

( 2φsε Si qNa

1

)2

7.试求出肖特基二极管的接触电阻表达式,并讨论和降低接触电阻、形成欧姆接 触的有效途径。

解:通过肖特基二极管的电流为 I ≈ I0 eqVA kT −1

其中 I0

=

Aq2Dn NC kT

[ 2qNd (φi ε Si

−

VA

)

1

]2

d

ϕ2 ip

dx2

=

qNa εp

(−xn ≤ x ≤ 0) (0 < x ≤ xp )

在 x= −xn 和 x= xp 处电场为零,即:

− dϕin

= − dϕip = 0

dx x= − xn

dx x=xp

电中性条件:

qNd xn

=

qNa xp ,得

xn xp

=

Na Nd

解泊松方程得:

ϕin (x)

(−xn ≤ x ≤ 0) (0 < x ≤ xp )

芯片翘曲原因

在微观的电子世界里,每一颗芯片都是一个精密复杂的宇宙。

然而,即便是最尖端的科技产物,也可能会遇到质量问题,芯片翘曲就是其中一种常见但又复杂的问题。

这种现象就好比一张平整的纸张因为湿度变化而卷曲起来,虽然原理相似,但芯片翘曲的原因却更加多样。

芯片翘曲,顾名思义,是指芯片在制造过程中或之后出现了形变,一边或几个角落向上或向下翘起。

翘曲的芯片就如同一个扭曲的地砖,不仅影响美观,更重要的是会引发一系列功能性问题。

那么,究竟是什么导致了芯片翘曲呢?首先,材料特性是导致芯片翘曲的内在因素。

芯片中的硅和其他半导体材料在不同温度下会有热膨胀和收缩的物理特性。

如果温度控制不均匀,就可能导致材料某部分膨胀另一部分收缩,从而引起翘曲。

这就好比在炎热的夏日,地面因阳光照射不均而产生局部膨胀,造成路面不平。

其次,制程技术也是影响芯片翘曲的重要因素。

在芯片的制造过程中,需要经历多次的光刻、蚀刻、沉积、抛光等步骤。

如果这些步骤中操作不当或者设备精度不够,就可能造成材料堆积不均或者应力分布不均,进而导致翘曲。

这就像是搭建积木时,若底部积木摆放不稳或上面的积木堆叠不均匀,最终很可能导致整个结构倾斜。

再者,设计缺陷有时候也会引起芯片翘曲。

例如,如果芯片设计时没有充分考虑热力学和力学的原则,那么在实际使用中就可能因为热量分布不均或者受力不均而导致变形。

这就像设计一座桥梁时没有计算好各部分的受力情况,最终可能导致桥梁在使用过程中出现弯曲或断裂。

最后,外部环境因素也不能忽视。

湿度、温度波动以及机械应力都可能对芯片的稳定性产生影响。

芯片在封装、测试或者运输过程中如果遭遇极端环境,也可能发生翘曲。

这就好比一本书长时间放在潮湿的环境中,书页会因为吸水膨胀而造成整本书的变形。

综上所述,芯片翘曲是一个多因素综合作用的结果。

它可能源于材料特性、制程技术、设计缺陷以及外部环境的影响。

要解决这一问题,就需要从材料选择、工艺优化、设计改进以及环境控制等多个方面入手,通过不断的技术创新和质量管理,确保每一颗芯片都能完美呈现其应有的性能与价值。

半导体物理学第九章知识点

半导体物理学第九章知识点第9章半导体异质结构第6章讨论的是由同⼀种半导体材料构成的p-n结,结两侧禁带宽度相同,通常称之为同质结。

本章介绍异质结,即两种不同半导体单晶材料的结合。

虽然早在1951年就已经提出了异质结的概念,并进⾏了⼀定的理论分析⼯作,但是由于⼯艺⽔平的限制,⼀直没有实际制成。

直到⽓相外延⽣长技术开发成功,异质结才在1960年得以实现。

1969年发表了第⼀个⽤异质结制成激光⼆极管的报告之后,半导体异质结的研究和应⽤才⽇益⼴泛起来。

§9.1 异质结及其能带图⼀、半导体异质结异质结是由两种不同的半导体单晶材料结合⽽成的,在结合部保持晶格的连续性,因⽽这两种材料⾄少要在结合⾯上具有相近的晶格结构。

根据这两种半导体单晶材料的导电类型,异质结分为以下两类:(1)反型异质结反型异质结是指由导电类型相反的两种不同的半导体单晶材料所形成的异质结。

例如由p型Ge与n型Si构成的结即为反型异质结,并记为pn-Ge/Si或记为p-Ge/n-Si。

如果异质结由n型Ge 与p型Si形成,则记为np-Ge/Si或记为n-Ge/p-Si。

已经研究过许多反型异质结,如pn-Ge/Si;pn-Si/GaAs;pn-Si/ZnS;pn-GaAs/GaP;np-Ge/GaAs;np-Si/GaP等等。

(2)同型异质结同型异质结是指由导电类型相同的两种不同的半导体单晶材料所形成的异质结。

例如。

在以上所⽤的符号中,⼀般都是把禁带宽度较⼩的材料名称写在前⾯。

⼆、异质结的能带结构异质结的能带结构取决于形成异质结的两种半导体的电⼦亲和能、禁带宽度、导电类型、掺杂浓度和界⾯态等多种因素,因此不能像同质结那样直接从费⽶能级推断其能带结构的特征。

1、理想异质结的能带图界⾯态使异质结的能带结构有⼀定的不确定性,但⼀个良好的异质结应有较低的界⾯态密度,因此在讨论异质结的能带图时先不考虑界⾯态的影响。

(1)突变反型异质结能带图图9-1(a)表⽰禁带宽度分别为E g1和E g2的p型半导体和n型半导体在形成异质pn结前的热平衡能带图,E g1 E g2。

半导体物理pn结的形成与能带弯曲

x

)

q(VD-U) EFn

qU

-

5)肖克莱方程式

将以上结果代入

J

jp (xn )

jn (xp )

qDp Lp

p(xn )

qDn Ln

n(xp )

得

J

( qDp pn0 Lp

qDnnp0 Ln

)[exp(qU kT

)

1]

qU JS [exp( kT

)

1]

JS

( qDp pn0 Lp

qDnnp0 ) Ln

设两边的杂质都已完全电离,即pn0=ni2/ND,np0=ni2/NA,于是得注入比

J p (xn ) Dp Ln pn0 p Ln N A Jn (xp ) DnLpnp0 nLp ND

若忽略电子和空穴之间的迁移率之差和扩散长度之差,

则近似有

J p (xn ) NA Jn(xp ) ND

pn结的注入比主要取决于p区与n区的掺杂浓度之比,浓度

pn结正向偏置时的载流子运动

2)正偏置pn结的能带结构

EC XD

qVD

EF

EV

EFp

+

p

n

零偏置

XD

Ln

q(VD-U)

EFn qU

LP

-

正向偏置

3)正偏置pn结的扩散电流

总电流是通过pn结同一截面的 电子电流与空穴电流之和:

j jp (xn ) jn (xn ) 或

EFp

j jp (xp ) jn (xp )

4)注入载流子的密度

XD

• p 侧边界 xp 处的电子密度可用 EFn求解,因为EFn比零偏状态 升高了qU,即xp处的电子密度 在正偏压下是零偏压下平衡密 EFp

2019年宁波大学考博试题2604半导体器件(B卷)

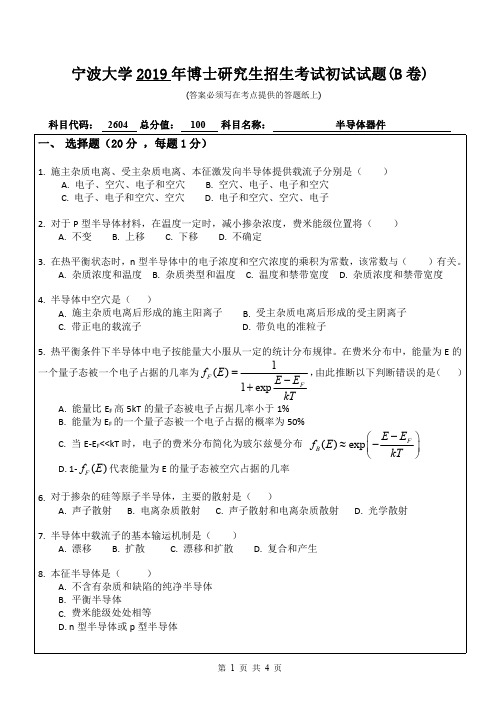

(答案必须写在考点提供的答题纸上)科目代码:2604总分值:100科目名称:半导体器件一、选择题(20分,每题1分)1.施主杂质电离、受主杂质电离、本征激发向半导体提供载流子分别是()A.电子、空穴、电子和空穴B.空穴、电子、电子和空穴C.电子、电子和空穴、空穴D.电子和空穴、空穴、电子2.对于P 型半导体材料,在温度一定时,减小掺杂浓度,费米能级位置将()A.不变B.上移C.下移D.不确定3.在热平衡状态时,n 型半导体中的电子浓度和空穴浓度的乘积为常数,该常数与()有关。

A.杂质浓度和温度 B.杂质类型和温度 C.温度和禁带宽度 D.杂质浓度和禁带宽度4.半导体中空穴是()A.施主杂质电离后形成的施主阳离子 B.受主杂质电离后形成的受主阴离子C.带正电的载流子D.带负电的准粒子5.热平衡条件下半导体中电子按能量大小服从一定的统计分布规律。

在费米分布中,能量为E 的一个量子态被一个电子占据的几率为1()1expF Ff E E E kT=-+,由此推断以下判断错误的是()A.能量比E F 高5kT 的量子态被电子占据几率小于1%B.能量为E F 的一个量子态被一个电子占据的概率为50%C.当E-E F <<kT 时,电子的费米分布简化为玻尔兹曼分布()exp F B E E f E kT -⎛⎫≈- ⎪⎝⎭D.1-()F f E 代表能量为E 的量子态被空穴占据的几率6.对于掺杂的硅等原子半导体,主要的散射是()A.声子散射 B.电离杂质散射 C.声子散射和电离杂质散射 D.光学散射7.半导体中载流子的基本输运机制是()A.漂移 B.扩散 C.漂移和扩散 D.复合和产生8.本征半导体是()A.不含有杂质和缺陷的纯净半导体B.平衡半导体C.费米能级处处相等D.n 型半导体或p 型半导体(答案必须写在考点提供的答题纸上)科目代码:2604总分值:100科目名称:半导体器件9.零偏pn结的内建电场()A.为0B.由n指向p方向C.由p指向n方向D.强度处处相等10.双极晶体管四种工作模式分别是正向有源、截止、反向有源和饱和。

半导体器件基础习题答案(完美版)

半导体器件习题答案

片的电阻率较大?说明理由。 A:

1 , n型半导体 q n N D 1 , p型半导体 q p N A

两片晶片的掺杂浓度相同,而电子的迁移率大于空穴的迁移率,因此 p 型半导体即晶片 2 的电阻率较大。 Q: (e) 在室温下硅样品中测得电子的迁移率 cm2/V .s 。求电子的扩散系数。 A:

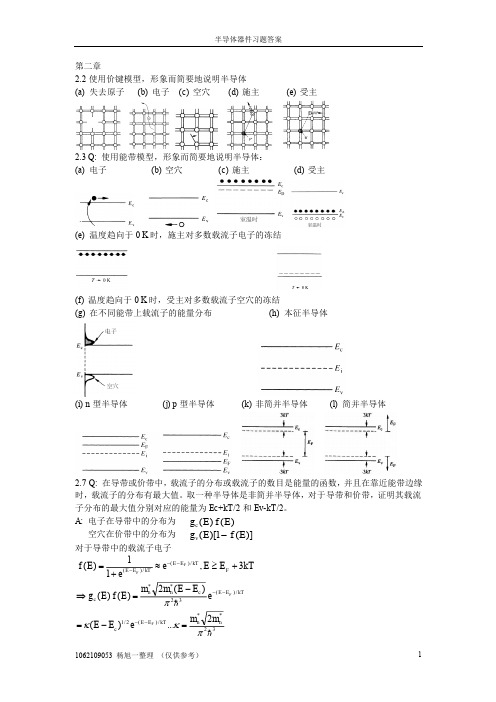

第二章 2.2 使用价键模型,形象而简要地说明半导体 (a) 失去原子 (b) 电子 (c) 空穴 (d) 施主 (e) 受主

2.3 Q: 使用能带模型,形象而简要地说明半导体: (a) 电子 (b) 空穴 (c) 施主

(d) 受主

(e) 温度趋向于 0 K 时,施主对多数载流子电子的冻结

(f) 温度趋向于 0 K 时,受主对多数载流子空穴的冻结 (g) 在不同能带上载流子的能量分布 (h) 本征半导体

说明:当材料内存在电场时,能带能量变成位置的函数,称为“能带弯曲” Q: (b) 电子的动能为零,即 K.E.=0 A: 说明:

Q: (c) 空穴的动能 K.E.=EG/4 A: 说明:

Q: (d) 光产生 A:

说明:从外部输入的光被吸收,电子被激发后,直接从价带进入导带 Q: (e) 直接热产生

1062109053 杨旭一整理 (仅供参考)

* m* p 2 m p ( Ev E )

g v ( E )[1 f ( E )] ( Ev E ) e

1/ 2

2

3

e ( E EF ) / kT

( E E F ) / kT

...

* m* p 2m p

d g c ( E ) f ( E ) dE e ( E EF ) / kT ( Ev E )1/ 2 e ( E EF ) / kT 1/ 2 2( Ev E ) kT 0 EE

光催化半导体能带弯曲上下弯曲的原因

光催化半导体能带弯曲上下弯曲的原因

光催化半导体的能带弯曲是由于其表面发生了光催化反应而形成的。

当光照射到半导体表面时,光子的能量可以被半导体吸收,激发了表面的电子跃迁到半导体的导带中。

这些被激发的电子在导带中具有较高的动能,可以与表面的氧分子或其他物质发生反应。

在光催化反应中,电子在导带中的跃迁会导致能带的弯曲。

当光子被吸收并激发电子到导带中时,导带的能量会上升。

同时,由于电子的跃迁,原来处于平衡状态的能带发生偏移,形成了能带弯曲。

这种能带弯曲可以提供更多的激发态能量,使得电子能够更容易地参与化学反应。

此外,光照还可以引起半导体表面的电子-空穴对的生成和分离,从而增加了光催化反应的效率。

当光子被吸收后,产生的电子和空穴可以在半导体中自由移动,与表面的反应物接触并参与反应。

这种电子-空穴对的生成和分离也会导致能带的弯曲。

总之,光催化半导体能带的弯曲是由于光子被吸收并激发了电子跃迁到导带中,以及电子-空穴对的生成和分离。

这些过程

提供了更多的激发态能量和活跃的反应位点,促进了光催化反应的发生。

两个n型半导体接触 能带弯曲

两个n型半导体接触能带弯曲1. 引言在半导体物理学领域,半导体接触以及能带结构一直是研究的热点。

而在实际应用中,对于两个n型半导体接触的能带弯曲问题,更是具有重要意义。

本文将从深度和广度兼具的角度,对两个n型半导体接触的能带弯曲进行全面评估,并撰写一篇有价值的文章,以帮助读者更深入地理解这一主题。

2. 什么是n型半导体在探讨两个n型半导体接触的能带弯曲问题之前,我们需要先了解什么是n型半导体。

简而言之,n型半导体是指杂质浓度较高,电子迁移率较大的半导体材料。

在n型半导体中,由于杂质原子的掺杂,使得半导体中出现了大量的自由电子,带负电荷。

3. 能带结构及能带弯曲的概念能带结构是半导体材料中电子运动的基础,其能级分布对材料的导电性质有着重要影响。

在两个n型半导体接触的情况下,由于能带结构可能存在差异,因此会形成能带弯曲的现象。

能带弯曲是指两个不同类型半导体接触形成的能带在接触区域出现的弯曲现象,其形成原因主要是由于两者之间的能带差异造成的。

4. 两个n型半导体接触的能带弯曲机制接下来,我们将深入探讨两个n型半导体接触的能带弯曲机制。

当两个n型半导体接触时,由于其能带结构的不同,会导致在接触位置处出现能级差异,从而形成能带弯曲。

这种能带弯曲的现象,在半导体器件的工作中可能会对电子运动和载流子注入产生影响。

5. 应用与展望我们将对两个n型半导体接触的能带弯曲问题进行应用与展望。

在半导体器件中,深刻理解两个n型半导体接触的能带弯曲机制,对于提高器件的性能以及优化器件结构都具有重要意义。

随着材料科学和半导体技术的发展,相信对于这一问题的研究会为未来的半导体器件设计和制造提供更多的可能性。

结语通过本文对两个n型半导体接触的能带弯曲问题进行全面评估和探讨,相信读者对这一主题已经有了更深入的理解。

能带结构及其弯曲的问题不仅在半导体物理学中具有重要意义,在实际应用中也有着重要的作用。

希望本文的内容能够为相关领域的研究者提供一些启发,推动半导体物理学理论研究和实际应用的发展。

pn结能带弯曲原理

pn结能带弯曲原理

PN结能带弯曲原理是指在半导体材料中,当P型和N型半导体材料通过结合形成PN结时,由于材料的能带结构不同,在PN结附近的能带出现弯曲现象。

这种能带弯曲现象是由于PN结区域中的电子和空穴浓度不一致造成的。

在PN结的P区域,由于掺杂有较高浓度的施主掺杂剂,使得该区域的电子浓度较高,而空穴

浓度较低。

在N区域中,由于掺杂有较高浓度的受主掺杂剂,使得该区域的空穴浓度较高,

而电子浓度较低。

因此,在PN结的P-N交界处,电子和空穴的浓度变化非常剧烈,形成能带

的弯曲。

具体地说,PN结的能带弯曲表现为P区的导带下降和价带上升,N区的导带上升和价带下降。

在PN结附近,导带下降和价带上升导致了形成一个势垒,阻止了电子和空穴的自由移动。

只

有在外加正向偏置时,势垒被克服,电子和空穴才能通过PN结进行注入和复合,形成电流。

能带弯曲现象对PN结的电子行为和电流特性产生了重要影响。

例如,能带弯曲导致了PN结

的正向偏置产生更小的电势差,相较于理想情况下的PN结,需要更低的正向偏置电压才能使

电流通过PN结。

此外,能带弯曲也对PN结的势垒高度和扩散电流起到调节作用。

功函数差与能带弯曲

功函数差与能带弯曲1.引言1.1 概述概述部分的内容可以如下所示:引言是一篇文章的开篇部分,通过对研究主题的概述,向读者介绍文章的背景和重要性。

本文将探讨功函数差与能带弯曲之间的关系。

功函数差是指两种不同材料接触时形成的电势差,而能带弯曲是指材料中电子能带的形状变化。

这两个概念在材料科学和物理学领域具有重要意义。

在材料科学中,功函数差是金属与半导体、金属与绝缘体等不同材料接触时产生的重要现象。

功函数差的大小直接影响到材料之间的电子转移和能级对齐情况。

这一现象在光电子器件、太阳能电池和传感器等领域具有广泛应用。

与此同时,能带弯曲这一概念也是材料科学中研究的重点之一。

能带弯曲是由于杂质、缺陷或外界电场等因素导致电子能带形状发生变化的现象。

能带弯曲对于材料的导电性质、光学性质以及载流子输运等方面都有着重要影响。

因此,深入了解功函数差与能带弯曲之间的关系,不仅可以为材料设计和性能优化提供理论指导,还有助于解决现实生产和应用中面临的问题。

本文的目的是探讨功函数差与能带弯曲之间的关系,并分析其对材料性能和应用的影响。

在正文部分,将分别详细介绍功函数差和能带弯曲的概念、定义以及形成原因。

结论部分将总结这两个概念之间的关系以及其在实际应用中的意义和价值。

通过本文的研究,我们可以更好地理解功函数差与能带弯曲之间的联系,为材料科学领域的研究和应用提供新的思路和方法。

希望本文能够激发读者的兴趣,为相关领域的学者和工程师提供参考和借鉴。

1.2 文章结构本文将分为三个主要部分进行阐述,即"引言"、"正文"和"结论"。

下面将对每个部分的内容进行详细描述。

1. 引言部分将对本文所要讨论的主题进行一个概述。

首先介绍功函数差和能带弯曲的基本概念,并阐述它们在材料科学中的重要性和应用价值。

然后,给出本文的目的,即通过探讨功函数差与能带弯曲之间的关系,来深入理解材料的电子结构及其对材料性能的影响。

金属半导体接触 能带弯曲

金属-半导体接触是电子器件中的一个重要概念,通常用于制造二极管、晶体管等半导体元件。

在金属和半导体之间形成的界面处,由于它们的能带结构不同,会发生能带弯曲现象。

1. 金属的能带结构:金属的价带和导带重叠,形成了连续的能带,因此金属内部有大量的自由电子可以移动,表现出良好的导电性。

2. 半导体的能带结构:半导体的价带和导带之间存在禁带,没有自由电子,但在外部激励(如加热或光照)下,部分价带电子可以跃迁到导带,形成电子-空穴对,从而具有导电能力。

3. 金属-半导体接触能带弯曲:当金属与半导体接触时,金属中的自由电子会扩散到半导体中,使半导体靠近金属一侧的费米能级升高,导致能带发生弯曲。

这种弯曲使得半导体中的载流子浓度增加,增强了半导体的导电性。

4. 肖特基势垒:在金属-半导体接触区域形成的这种能带弯曲也被称为肖特基势垒。

它阻碍了电子从半导体向金属的进一步扩散,同时允许电子从金属向半导体扩散,因此金属-半导体结呈现出单向导通特性。

5. 应用:金属-半导体接触的能带弯曲原理被广泛应用于半导体器件的设计和制造中,例如硅太阳能电池、场效应晶体管等。

总之,金属-半导体接触能带弯曲是一个重要的物理现象,对于理解半导体器件的工作原理以及设计新型半导体器件具有重要意义。

电压和能带弯曲的关系

电压和能带弯曲的关系

电压和能带弯曲之间存在密切的关系。

在半导体中,当加电压时,即形成电场。

电场作用下,半导体表面一定深度下的电子能级发生改变,导致材料表面的导电性发生改变,使得材料表面区域的电子能占有的能级发生变化。

这种效应具有代表性的表征方式就是“能带弯曲图”。

能带弯曲图反映了材料表面的能带边界ef、ec、ev与进入材料深度x之间的关系。

在典型的能带弯曲图中,为了简化,能带中的能量单位是ev,电压的单位是v,避免了引入参数q作为单位电荷。

在图中,导带的最低能级(conduction edge)和价带的最高能级(valence edge)在外加电压v的作用下发生弯曲。

依照习惯,图中显示的是电子的拥有能量,所以一个正电压作用于半导体材料会使材料表面的能带向下弯曲。

【高中物理】优质课件:表面能带弯曲与反型

School of Microelectronics

• 对于图5.4(b)所示的表面能级带正电、能带下弯的情况, 那么p型样品在近表面区域其EF距价带顶Ev的距离就有可能比 距导带底Ec的距离更远,这样该区域电子浓度大于空穴浓度, 呈现n型反型层。

• 由于固定电荷起因于Si-SiO2界面附近存在的过剩硅离子, 采用退火工艺可进一步降低SiO2中已经形成的固定电荷。

School of Microelectronics

(3) 影响Si半导体器件性能最重要的因素是Si-SiO2系统中 SiO2层内可动离子的漂移。 降低SiO2层中可动离子的影响可以从几个方面着手:

School of Microelectronics

表面处理

(1) Si-SiO2界面处的界面态密度和Si的晶向(晶面)有关,一 般(111)面的态密度比(110)面大,而(110)面的态密度又 比(100)大,也就是说(100)面的界面态密度最小。

• 为减少界面态影响,在MOS器件和集成电路生产中常选 用(100)晶面。

1 1 1 τ τv τs

1/τv 是体内复合几率,1/τs 是表面复合几率,而τ称为有效 寿命。

School of Microelectronics

感 谢 观 看

School of Microelectronics

• 首先是要设法控制并减少器件制造工艺过程中的Na+沾污; • 其次,由于要根本避免Na+沾污几乎不可能,那么对于已经

存在于SiO2中的Na+应该设法使其固定在空气- SiO2或金属SiO2界面附近,以减弱它们的不良影响; • 还有就是芯片完成后,再采取制备钝化膜来保护管芯的措 施,以阻挡Na+的重新沾污。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

半导体能带弯曲上下弯曲的原因

引言

半导体是一种特殊的材料,具有介于导体和绝缘体之间的电导特性。

在半导体中,能带理论被广泛应用于解释其电子结构和电学性质。

能带理论认为,半导体中的电子分布在离散的能级上,称为能带。

然而,在某些情况下,半导体能带会出现弯曲,即上下弯曲的现象。

本文将探讨半导体能带弯曲上下弯曲的原因。

能带理论简介

在了解半导体能带弯曲的原因之前,我们先来回顾一下能带理论。

根据量子力学原理,一个电子在晶格势场中运动时会形成一系列离散的能级。

这些电子所处的不同能级被分为两个区域:价带和导带。

价带是最高填充态的集合,而导带是最低未填充态的集合。

两者之间存在一个禁止带隙(band gap),其中没有允许态存在。

对于绝缘体来说,禁止带隙很大,电子无法跃迁到导带,因此绝缘体不导电。

对于导体来说,禁止带隙趋近于零,电子可以自由地跃迁到导带,因此导体具有良好的导电性。

而半导体则处于介于两者之间的状态,禁止带隙较小,温度升高或施加外加电场时可以激发部分电子进入导带。

半导体能带弯曲的原因

半导体能带弯曲上下弯曲的原因主要包括杂质、应力和温度三个方面。

1. 杂质

杂质是指在半导体晶格中掺入的其他元素或杂质。

这些杂质会改变晶格结构和原子排列方式,从而影响半导体的能带结构。

当杂质与半导体原子结合时,会形成能级位于价带或导带中的能级。

这些能级被称为杂质态(impurity states)。

由于杂质态在禁止带隙内存在,它们会与价带和

导带之间的允许态发生相互作用,并引起能带弯曲。

2. 应力

应力是指在半导体材料中施加的外力或外界环境对晶格结构的影响。

应力可以来自于机械变形、热膨胀或其他因素。

当半导体材料受到应力作用时,晶格结构会发生畸变。

这种畸变会导致能带结构发生改变,从而引起能带弯曲。

3. 温度

温度是影响半导体能带弯曲的另一个重要因素。

根据固体物理学原理,随着温度的升高,原子和分子的热运动会增强,电子跃迁的概率也会增加。

在半导体中,温度升高会激发更多的电子进入导带,从而改变能带结构。

这种温度效应被称为热激发(thermal excitation),它可以导致能带上下弯曲。

结论

半导体能带弯曲上下弯曲是由于杂质、应力和温度等因素引起的。

杂质造成了禁止带隙内的杂质态形成,与允许态相互作用;应力导致晶格结构发生畸变,从而改变能带结构;温度升高使得更多的电子进入导带,引起能带上下弯曲。

了解半导体能带弯曲的原因对于理解半导体材料的电学性质和应用具有重要意义。

通过控制和调节这些因素,可以优化半导体材料的性能,并开发出更高效、可靠的电子器件。

参考文献: 1. Sze, S. M., & Ng, K. K. (2006). Physics of semiconductor devices (3rd ed.). Wiley-Interscience. 2. Streetman, B. G., & Banerjee, S. K. (2005). Solid state electronic devices (6th ed.). Pearson Education.

Markdown格式输出

# 半导体能带弯曲上下弯曲的原因

## 引言

半导体是一种特殊的材料,具有介于导体和绝缘体之间的电导特性。

在半导体中,能带理

论被广泛应用于解释其电子结构和电学性质。

能带理论认为,半导体中的电子分布在离散

的能级上,称为能带。

然而,在某些情况下,半导体能带会出现弯曲,即上下弯曲的现象。

本文将探讨半导体能带弯曲上下弯曲的原因。

## 能带理论简介

在了解半导体能带弯曲的原因之前,我们先来回顾一下能带理论。

根据量子力学原理,一个电子在晶格势场中运动时会形成一系列离散的能级。

这些电子所

处的不同能级被分为两个区域:价带和导带。

价带是最高填充态的集合,而导带是最低未

填充态的集合。

两者之间存在一个禁止带隙(band gap),其中没有允许态存在。

对于绝缘体来说,禁止带隙很大,电子无法跃迁到导带,因此绝缘体不导电。

对于导体来说,禁止带隙趋近于零,电子可以自由地跃迁到导带,因此导体具有良好的导电性。

而半

导体则处于介于两者之间的状态,禁止带隙较小,温度升高或施加外加电场时可以激发部

分电子进入导带。

## 半导体能带弯曲的原因

半导体能带弯曲上下弯曲的原因主要包括杂质、应力和温度三个方面。

### 1. 杂质

杂质是指在半导体晶格中掺入的其他元素或杂质。

这些杂质会改变晶格结构和原子排列方式,从而影响半导体的能带结构。

当杂质与半导体原子结合时,会形成能级位于价带或导带中的能级。

这些能级被称为杂质

态(impurity states)。

由于杂质态在禁止带隙内存在,它们会与价带和导带之间的允

许态发生相互作用,并引起能带弯曲。

### 2. 应力

应力是指在半导体材料中施加的外力或外界环境对晶格结构的影响。

应力可以来自于机械

变形、热膨胀或其他因素。

当半导体材料受到应力作用时,晶格结构会发生畸变。

这种畸变会导致能带结构发生改变,从而引起能带弯曲。

### 3. 温度

温度是影响半导体能带弯曲的另一个重要因素。

根据固体物理学原理,随着温度的升高,

原子和分子的热运动会增强,电子跃迁的概率也会增加。

在半导体中,温度升高会激发更多的电子进入导带,从而改变能带结构。

这种温度效应被

称为热激发(thermal excitation),它可以导致能带上下弯曲。

## 结论

半导体能带弯曲上下弯曲是由于杂质、应力和温度等因素引起的。

杂质造成了禁止带隙内

的杂质态形成,与允许态相互作用;应力导致晶格结构发生畸变,从而改变能带结构;温

度升高使得更多的电子进入导带,引起能带上下弯曲。

了解半导体能带弯曲的原因对于理解半导体材料的电学性质和应用具有重要意义。

通过控

制和调节这些因素,可以优化半导体材料的性能,并开发出更高效、可靠的电子器件。

参考文献:

1. Sze, S. M., & Ng, K. K. (2006). Physics of semiconductor devices (3rd ed.).

Wiley-Interscience.

2. Streetman, B. G., & Banerjee, S. K. (2005). Solid state electronic devices (6th ed.). Pearson Education.。