PolyMax Enhanced Thin Wafers _LT

离子束增强沉积TiN薄膜的耐蚀性

通

大

学

学 报

Vo 1 . 3 4 No . 6 De c . 2 01 3

2 0 1 3年 1 2月

J OURN AL OF D AL I AN J I AOT ONG UNI VER S I T Y

文章编号 : 1 6 7 3 — 9 5 9 0 ( 2 0 1 3 ) 0 6 — 0 0 7 9 — 0 4

离 子束 增 强 沉 积 T i N薄 膜 的耐 蚀 性

朱雪梅 , 马永 乐, 张琳

( 大连交通大 学 材料科 学- 9工程 学院 , 辽 宁 大连 1 1 6 0 2 8 ) 米

摘

要: 采用不 同离子束入射方 向的离子束增强沉 积技术 ( I B E D)在 W1 8 C r 4 V高速钢 表面沉 积 T i N薄

E- ma i l : x m z h u @d j t u . e d u . e n .

8 0

大 连 交 通 大 学 学 报

第3 4卷

电化 学 腐 蚀 实 验 采 用 E G &G P A R 2 2 7 3电化 学工 作站 , 在0 . 5 m o l / L H 2 S O 4和 3 % N a C 1 溶 液 中室 温下 进行 , 采用 典型 的三 电极 体系 , 参 比 电极

采用 X R D一 6 0 0 0型 x射 线衍 射 分 析 仪 分 析 改性 前后 合金 的相 结 构 . x射 线 种类 为 c u K , 波

长为 1 . 5 4 0 6 o 3 , , 电压 为 4 0 . 0 k V, 电流为 3 0 . 0

1 实 验 方 法

领 域 中具 有 重 要 的 应 用 价 值 和 广 阔 的应 用 前 景 。 ] . 但T i N薄膜的耐蚀性受到薄膜显微结构 的 显著 影响 , 不 同 金 属 材 料 表 面 上 物 理 气 相 沉 积

半导体制造技术

Semiconductor Manufacturing Technology半导体制造技术Instructor’s ManualMichael QuirkJulian SerdaCopyright Prentice HallTable of Contents目录OverviewI. Chapter1. Semiconductor industry overview2. Semiconductor materials3. Device technologies—IC families4. Silicon and wafer preparation5. Chemicals in the industry6. Contamination control7. Process metrology8. Process gas controls9. IC fabrication overview10. Oxidation11. Deposition12. Metallization13. Photoresist14. Exposure15. Develop16. Etch17. Ion implant18. Polish19. Test20. Assembly and packagingII. Answers to End-of-Chapter Review QuestionsIII. Test Bank (supplied on diskette)IV. Chapter illustrations, tables, bulleted lists and major topics (supplied on CD-ROM)Notes to Instructors:1)The chapter overview provides a concise summary of the main topics in each chapter.2)The correct answer for each test bank question is highlighted in bold. Test bankquestions are based on the end-of-chapter questions. If a student studies the end-of-chapter questions (which are linked to the italicized words in each chapter), then they will be successful on the test bank questions.2Chapter 1Introduction to the Semiconductor Industry Die:管芯 defective:有缺陷的Development of an Industry•The roots of the electronic industry are based on the vacuum tube and early use of silicon for signal transmission prior to World War II. The first electronic computer, the ENIAC, wasdeveloped at the University of Pennsylvania during World War II.•William Shockley, John Bardeen and Walter Brattain invented the solid-state transistor at Bell Telephone Laboratories on December 16, 1947. The semiconductor industry grew rapidly in the 1950s to commercialize the new transistor technology, with many early pioneers working inSilicon Valley in Northern California.Circuit Integration•The first integrated circuit, or IC, was independently co-invented by Jack Kilby at Texas Instruments and Robert Noyce at Fairchild Semiconductor in 1959. An IC integrates multiple electronic components on one substrate of silicon.•Circuit integration eras are: small scale integration (SSI) with 2 - 50 components, medium scale integration (MSI) with 50 – 5k components, large scale integration (LSI) with 5k to 100kcomponents, very large scale integration (VLSI) with 100k to 1M components, and ultra large scale integration (ULSI) with > 1M components.1IC Fabrication•Chips (or die) are fabricated on a thin slice of silicon, known as a wafer (or substrate). Wafers are fabricated in a facility known as a wafer fab, or simply fab.•The five stages of IC fabrication are:Wafer preparation: silicon is purified and prepared into wafers.Wafer fabrication: microchips are fabricated in a wafer fab by either a merchant chip supplier, captive chip producer, fabless company or foundry.Wafer test: Each individual die is probed and electrically tested to sort for good or bad chips.Assembly and packaging: Each individual die is assembled into its electronic package.Final test: Each packaged IC undergoes final electrical test.•Key semiconductor trends are:Increase in chip performance through reduced critical dimensions (CD), more components per chip (Moore’s law, which predicts the doubling of components every 18-24 months) andreduced power consumption.Increase in chip reliability during usage.Reduction in chip price, with an estimated price reduction of 100 million times for the 50 years prior to 1996.The Electronic Era•The 1950s saw the development of many different types of transistor technology, and lead to the development of the silicon age.•The 1960s were an era of process development to begin the integration of ICs, with many new chip-manufacturing companies.•The 1970s were the era of medium-scale integration and saw increased competition in the industry, the development of the microprocessor and the development of equipment technology. •The 1980s introduced automation into the wafer fab and improvements in manufacturing efficiency and product quality.•The 1990s were the ULSI integration era with the volume production of a wide range of ICs with sub-micron geometries.Career paths•There are a wide range of career paths in semiconductor manufacturing, including technician, engineer and management.2Chapter 2 Characteristics of Semiconductor MaterialsAtomic Structure•The atomic model has three types of particles: neutral neutrons(不带电的中子), positively charged protons(带正电的质子)in the nucleus and negatively charged electrons(带负电的核外电子) that orbit the nucleus. Outermost electrons are in the valence shell, and influence the chemical and physical properties of the atom. Ions form when an atom gains or loses one or more electrons.The Periodic Table•The periodic table lists all known elements. The group number of the periodic table represents the number of valence shell electrons of the element. We are primarily concerned with group numbers IA through VIIIA.•Ionic bonds are formed when valence shell electrons are transferred from the atoms of one element to another. Unstable atoms (e.g., group VIIIA atoms because they lack one electron) easily form ionic bonds.•Covalent bonds have atoms of different elements that share valence shell electrons.3Classifying Materials•There are three difference classes of materials:ConductorsInsulatorsSemiconductors•Conductor materials have low resistance to current flow, such as copper. Insulators have high resistance to current flow. Capacitance is the storage of electrical charge on two conductive plates separated by a dielectric material. The quality of the insulation material between the plates is the dielectric constant. Semiconductor materials can function as either a conductor or insulator.Silicon•Silicon is an elemental semiconductor material because of four valence shell electrons. It occurs in nature as silica and is refined and purified to make wafers.•Pure silicon is intrinsic silicon. The silicon atoms bond together in covalent bonds, which defines many of silicon’s properties. Silicon atoms bond together in set, repeatable patterns, referred to asa crystal.•Germanium was the first semiconductor material used to make chips, but it was soon replaced by silicon. The reasons for this change are:Abundance of siliconHigher melting temperature for wider processing rangeWide temperature range during semiconductor usageNatural growth of silicon dioxide•Silicon dioxide (SiO2) is a high quality, stable electrical insulator material that also serves as a good chemical barrier to protect silicon from external contaminants. The ability to grow stable, thin SiO2 is fundamental to the fabrication of Metal-Oxide-Semiconductor (MOS) devices. •Doping increases silicon conductivity by adding small amounts of other elements. Common dopant elements are from trivalent, p-type Group IIIA (boron) and pentavalent, n-type Group VA (phosphorus, arsenic and antimony).•It is the junction between the n-type and p-type doped regions (referred to as a pn junction) that permit silicon to function as a semiconductor.4Alternative Semiconductor Materials•The alternative semiconductor materials are primarily the compound semiconductors. They are formed from Group IIIA and Group VA (referred to as III-V compounds). An example is gallium arsenide (GaAs).•Some alternative semiconductors come from Group IIA and VIA, referred to as II-VI compounds. •GaAs is the most common III-V compound semiconductor material. GaAs ICs have greater electron mobility, and therefore are faster than ICs made with silicon. GaAs ICs also have higher radiation hardness than silicon, which is better for space and military applications. The primary disadvantage of GaAs is the lack of a natural oxide.5Chapter 3Device TechnologiesCircuit Types•There are two basic types of circuits: analog and digital. Analog circuits have electrical data that varies continuously over a range of voltage, current and power values. Digital circuits have operating signals that vary about two distinct voltage levels – a high and a low.Passive Component Structures•Passive components such as resistors and capacitors conduct electrical current regardless of how the component is connected. IC resistors are a passive component. They can have unwanted resistance known as parasitic resistance. IC capacitor structures can also have unintentional capacitanceActive Component Structures•Active components, such as diodes and transistors can be used to control the direction of current flow. PN junction diodes are formed when there is a region of n-type semiconductor adjacent to a region of p-type semiconductor. A difference in charge at the pn junction creates a depletion region that results in a barrier voltage that must be overcome before a diode can be operated. A bias voltage can be configured to have a reverse bias, with little or no conduction through the diode, or with a forward bias, which permits current flow.•The bipolar junction transistor (BJT) has three electrodes and two pn junctions. A BJT is configured as an npn or pnp transistor and biased for conduction mode. It is a current-amplifying device.6• A schottky diode is formed when metal is brought in contact with a lightly doped n-type semiconductor material. This diode is used in faster and more power efficient BJT circuits.•The field-effect transistor (FET), a voltage-amplifying device, is more compact and power efficient than BJT devices. A thin gate oxide located between the other two electrodes of the transistor insulates the gate on the MOSFET. There are two categories of MOSFETs, nMOS (n-channel) and pMOS (p-channel), each which is defined by its majority current carriers. There is a biasing scheme for operating each type of MOSFET in conduction mode.•For many years, nMOS transistors have been the choice of most IC manufacturers. CMOS, with both nMOS and pMOS transistors in the same IC, has been the most popular device technology since the early 1980s.•BiCMOS technology makes use of the best features of both CMOS and bipolar technology in the same IC device.•Another way to categorize FETs is in terms of enhancement mode and depletion mode. The major different is in the way the channels are doped: enhancement-mode channels are doped opposite in polarity to the source and drain regions, whereas depletion mode channels are doped the same as their respective source and drain regions.Latchup in CMOS Devices•Parasitic transistors can create a latchup condition(???????) in CMOS ICs that causes transistors to unintentionally(无心的) turn on. To control latchup, an epitaxial layer is grown on the wafer surface and an isolation barrier(隔离阻障)is placed between the transistors. An isolation layer can also be buried deep below the transistors.Integrated Circuit Productsz There are a wide range of semiconductor ICs found in electrical and electronic products. This includes the linear IC family, which operates primarily with anal3og circuit applications, and the digital IC family, which includes devices that operate with binary bits of data signals.7Chapter 4Silicon and Wafer Preparation8z Semiconductor-Grade Silicon•The highly refined silicon used for wafer fabrication is termed semiconductor-grade silicon (SGS), and sometimes referred to as electronic-grade silicon. The ultra-high purity of semiconductor-grade silicon is obtained from a multi-step process referred to as the Siemens process.Crystal Structure• A crystal is a solid material with an ordered, 3-dimensional pattern over a long range. This is different from an amorphous material that lacks a repetitive structure.•The unit cell is the most fundamental entity for the long-range order found in crystals. The silicon unit cell is a face-centered cubic diamond structure. Unit cells can be organized in a non-regular arrangement, known as a polycrystal. A monocrystal are neatly arranged unit cells.Crystal Orientation•The orientation of unit cells in a crystal is described by a set of numbers known as Miller indices.The most common crystal planes on a wafer are (100), (110), and (111). Wafers with a (100) crystal plane orientation are most common for MOS devices, whereas (111) is most common for bipolar devices.Monocrystal Silicon Growth•Silicon monocrystal ingots are grown with the Czochralski (CZ) method to achieve the correct crystal orientation and doping. A CZ crystal puller is used to grow the silicon ingots. Chunks of silicon are heated in a crucible in the furnace of the puller, while a perfect silicon crystal seed is used to start the new crystal structure.• A pull process serves to precisely replicate the seed structure. The main parameters during the ingot growth are pull rate and crystal rotation. More homogeneous crystals are achieved with a magnetic field around the silicon melt, known as magnetic CZ.•Dopant material is added to the melt to dope the silicon ingot to the desired electrical resistivity.Impurities are controlled during ingot growth. A float-zone crystal growth method is used toachieve high-purity silicon with lower oxygen content.•Large-diameter ingots are grown today, with a transition underway to produce 300-mm ingot diameters. There are cost benefits for larger diameter wafers, including more die produced on a single wafer.Crystal Defects in Silicon•Crystal defects are interruptions in the repetitive nature of the unit cell. Defect density is the number of defects per square centimeter of wafer surface.•Three general types of crystal defects are: 1) point defects, 2) dislocations, and 3) gross defects.Point defects are vacancies (or voids), interstitial (an atom located in a void) and Frenkel defects, where an atom leaves its lattice site and positions itself in a void. A form of dislocation is astacking fault, which is due to layer stacking errors. Oxygen-induced stacking faults are induced following thermal oxidation. Gross defects are related to the crystal structure (often occurring during crystal growth).Wafer Preparation•The cylindrical, single-crystal ingot undergoes a series of process steps to create wafers, including machining operations, chemical operations, surface polishing and quality checks.•The first wafer preparation steps are the shaping operations: end removal, diameter grinding, and wafer flat or notch. Once these are complete, the ingot undergoes wafer slicing, followed by wafer lapping to remove mechanical damage and an edge contour. Wafer etching is done to chemically remove damage and contamination, followed by polishing. The final steps are cleaning, wafer evaluation and packaging.Quality Measures•Wafer suppliers must produce wafers to stringent quality requirements, including: Physical dimensions: actual dimensions of the wafer (e.g., thickness, etc.).Flatness: linear thickness variation across the wafer.Microroughness: peaks and valleys found on the wafer surface.Oxygen content: excessive oxygen can affect mechanical and electrical properties.Crystal defects: must be minimized for optimum wafer quality.Particles: controlled to minimize yield loss during wafer fabrication.Bulk resistivity(电阻系数): uniform resistivity from doping during crystal growth is critical. Epitaxial Layer•An epitaxial layer (or epi layer) is grown on the wafer surface to achieve the same single crystal structure of the wafer with control over doping type of the epi layer. Epitaxy minimizes latch-up problems as device geometries continue to shrink.Chapter 5Chemicals in Semiconductor FabricationEquipment Service Chase Production BayChemical Supply Room Chemical Distribution Center Holding tank Chemical drumsProcess equipmentControl unit Pump Filter Raised and perforated floorElectronic control cablesSupply air ductDual-wall piping for leak confinement PumpFilterChemical control and leak detection Valve boxes for leak containment Exhaust air ductStates of Matter• Matter in the universe exists in 3 basic states (宇宙万物存在着三种基本形态): solid, liquid andgas. A fourth state is plasma.Properties of Materials• Material properties are the physical and chemical characteristics that describe its unique identity.• Different properties for chemicals in semiconductor manufacturing are: temperature, pressure andvacuum, condensation, vapor pressure, sublimation and deposition, density, surface tension, thermal expansion and stress.Temperature is a measure of how hot or cold a substance is relative to another substance. Pressure is the force exerted per unit area. Vacuum is the removal of gas molecules.Condensation is the process of changing a gas into a liquid. Vaporization is changing a liquidinto a gas.Vapor pressure is the pressure exerted by a vapor in a closed container at equilibrium.Sublimation is the process of changing a solid directly into a gas. Deposition is changing a gas into a solid.Density is the mass of a substance divided by its volume.Surface tension of a liquid is the energy required to increase the surface area of contact.Thermal expansion is the increase in an object’s dimension due to heating.Stress occurs when an object is exposed to a force.Process Chemicals•Semiconductor manufacturing requires extensive chemicals.• A chemical solution is a chemical mixture. The solvent is the component of the solution present in larger amount. The dissolved substances are the solutes.•Acids are solutions that contain hydrogen and dissociate in water to yield hydronium ions. A base is a substance that contains the OH chemical group and dissociates in water to yield the hydroxide ion, OH-.•The pH scale is used to assess the strength of a solution as an acid or base. The pH scale varies from 0 to 14, with 7 being the neutral point. Acids have pH below 7 and bases have pH values above 7.• A solvent is a substance capable of dissolving another substance to form a solution.• A bulk chemical distribution (BCD) system is often used to deliver liquid chemicals to the process tools. Some chemicals are not suitable for BCD and instead use point-of-use (POU) delivery, which means they are stored and used at the process station.•Gases are generally categorized as bulk gases or specialty gases. Bulk gases are the relatively simple gases to manufacture and are traditionally oxygen, nitrogen, hydrogen, helium and argon.The specialty gases, or process gases, are other important gases used in a wafer fab, and usually supplied in low volume.•Specialty gases are usually transported to the fab in metal cylinders.•The local gas distribution system requires a gas purge to flush out undesirable residual gas. Gas delivery systems have special piping and connections systems. A gas stick controls the incoming gas at the process tool.•Specialty gases may be classified as hydrides, fluorinated compounds or acid gases.Chapter 6Contamination Control in Wafer FabsIntroduction•Modern semiconductor manufacturing is performed in a cleanroom, isolated from the outside environment and contaminants.Types of contamination•Cleanroom contamination has five categories: particles, metallic impurities, organic contamination, native oxides and electrostatic discharge. Killer defects are those causes of failure where the chip fails during electrical test.Particles: objects that adhere to a wafer surface and cause yield loss. A particle is a killer defect if it is greater than one-half the minimum device feature size.Metallic impurities: the alkali metals found in common chemicals. Metallic ions are highly mobile and referred to as mobile ionic contaminants (MICs).Organic contamination: contains carbon, such as lubricants and bacteria.Native oxides: thin layer of oxide growth on the wafer surface due to exposure to air.Electrostatic discharge (ESD): uncontrolled transfer of static charge that can damage the microchip.Sources and Control of Contamination•The sources of contamination in a wafer fab are: air, humans, facility, water, process chemicals, process gases and production equipment.Air: class number designates the air quality inside a cleanroom by defining the particle size and density.Humans: a human is a particle generator. Humans wear a cleanroom garment and follow cleanroom protocol to minimize contamination.Facility: the layout is generally done as a ballroom (open space) or bay and chase design.Laminar airflow with air filtering is used to minimize particles. Electrostatic discharge iscontrolled by static-dissipative materials, grounding and air ionization.Ultrapure deiniozed (DI) water: Unacceptable contaminants are removed from DI water through filtration to maintain a resistivity of 18 megohm-cm. The zeta potential represents a charge on fine particles in water, which are trapped by a special filter. UV lamps are used for bacterial sterilization.Process chemicals: filtered to be free of contamination, either by particle filtration, microfiltration (membrane filter), ultrafiltration and reverse osmosis (or hyperfiltration).Process gases: filtered to achieve ultraclean gas.Production equipment: a significant source of particles in a fab.Workstation design: a common layout is bulkhead equipment, where the major equipment is located behind the production bay in the service chase. Wafer handling is done with robotic wafer handlers. A minienvironment is a localized environment where wafers are transferred on a pod and isolated from contamination.Wafer Wet Cleaning•The predominant wafer surface cleaning process is with wet chemistry. The industry standard wet-clean process is the RCA clean, consisting of standard clean 1 (SC-1) and standard clean 2 (SC-2).•SC-1 is a mixture of ammonium hydroxide, hydrogen peroxide and DI water and capable of removing particles and organic materials. For particles, removal is primarily through oxidation of the particle or electric repulsion.•SC-2 is a mixture of hydrochloric acid, hydrogen peroxide and DI water and used to remove metals from the wafer surface.•RCA clean has been modified with diluted cleaning chemistries. The piranha cleaning mixture combines sulfuric acid and hydrogen peroxide to remove organic and metallic impurities. Many cleaning steps include an HF last step to remove native oxide.•Megasonics(兆声清洗) is widely used for wet cleaning. It has ultrasonic energy with frequencies near 1 MHz. Spray cleaning will spray wet-cleaning chemicals onto the wafer. Scrubbing is an effective method for removing particles from the wafer surface.•Wafer rinse is done with overflow rinse, dump rinse and spray rinse. Wafer drying is done with spin dryer or IPA(异丙醇) vapor dry (isopropyl alcohol).•Some alternatives to RCA clean are dry cleaning, such as with plasma-based cleaning, ozone and cryogenic aerosol cleaning.Chapter 7Metrology and Defect InspectionIC Metrology•In a wafer fab, metrology refers to the techniques and procedures for determining physical and electrical properties of the wafer.•In-process data has traditionally been collected on monitor wafers. Measurement equipment is either stand-alone or integrated.•Yield is the percent of good parts produced out of the total group of parts started. It is an indicator of the health of the fabrication process.Quality Measures•Semiconductor quality measures define the requirements for specific aspects of wafer fabrication to ensure acceptable device performance.•Film thickness is generally divided into the measurement of opaque film or transparent film. Sheet resistance measured with a four-point probe is a common method of measuring opaque films (e.g., metal film). A contour map shows sheet resistance deviations across the wafer surface.•Ellipsometry is a nondestructive, noncontact measurement technique for transparent films. It works based on linearly polarized light that reflects off the sample and is elliptically polarized.•Reflectometry is used to measure a film thickness based on how light reflects off the top and bottom surface of the film layer. X-ray and photoacoustic technology are also used to measure film thickness.•Film stress is measured by analyzing changes in the radius of curvature of the wafer. Variations in the refractive index are used to highlight contamination in the film.•Dopant concentration is traditionally measured with a four-point probe. The latest technology is the thermal-wave system, which measures the lattice damage in the implanted wafer after ion implantation. Another method for measuring dopant concentration is spreading resistance probe. •Brightfield detection is the traditional light source for microscope equipment. An optical microscope uses light reflection to detect surface defects. Darkfield detection examines light scattered off defects on the wafer surface. Light scattering uses darkfield detection to detectsurface particles by illuminating the surface with laser light and then using optical imaging.•Critical dimensions (CDs) are measured to achieve precise control over feature size dimensions.The scanning electron microscope is often used to measure CDs.•Conformal step coverage is measured with a surface profiler that has a stylus tip.•Overlay registration measures the ability to accurately print photoresist patterns over a previously etched pattern.•Capacitance-voltage (C-V) test is used to verify acceptable charge conditions and cleanliness at the gate structure in a MOS device.Analytical Equipment•The secondary-ion mass spectrometry (SIMS) is a method of eroding a wafer surface with accelerated ions in a magnetic field to analyze the surface material composition.•The atomic force microscope (AFM) is a surface profiler that scans a small, counterbalanced tip probe over the wafer to create a 3-D surface map.•Auger electron spectroscopy (AES) measures composition on the wafer surface by measuring the energy of the auger electrons. It identifies elements to a depth of about 2 nm. Another instrument used to identify surface chemical species is X-ray photoelectron spectroscopy (XPS).•Transmission electron microscopy (TEM) uses a beam of electrons that is transmitted through a thin slice of the wafer. It is capable of quantifying very small features on a wafer, such as silicon crystal point defects.•Energy-dispersive spectrometer (EDX) is a widely used X-ray detection method for identifying elements. It is often used in conjunction with the SEM.• A focused ion beam (FIB) system is a destructive technique that focuses a beam of ions on the wafer to carve a thin cross section from any wafer area. This permits analysis of the wafermaterial.Chapter 8Gas Control in Process ChambersEtch process chambers••The process chamber is a controlled vacuum environment where intended chemical reactions take place under controlled conditions. Process chambers are often configured as a cluster tool. Vacuum•Vacuum ranges are low (rough) vacuum, medium vacuum, high vacuum and ultrahigh vacuum (UHV). When pressure is lowered in a vacuum, the mean free path(平均自由行程) increases, which is important for how gases flow through the system and for creating a plasma.Vacuum Pumps•Roughing pumps are used to achieve a low to medium vacuum and to exhaust a high vacuum pump. High vacuum pumps achieve a high to ultrahigh vacuum.•Roughing pumps are dry mechanical pumps or a blower pump (also referred to as a booster). Two common high vacuum pumps are a turbomolecular (turbo) pump and cryopump. The turbo pump is a reliable, clean pump that works on the principle of mechanical compression. The cryopump isa capture pump that removes gases from the process chamber by freezing them.。

拉曼晶圆lt衬底材料界面

拉曼晶圆lt衬底材料界面

拉曼晶圆LT衬底材料界面通常指的是衬底的表面和材料之间

的界面。

由于拉曼晶圆LT衬底材料通常是通过化学气相沉积

或分子束外延等方式生长在衬底上的,因此衬底材料界面对于拉曼晶圆的性能和质量起着至关重要的作用。

在拉曼晶圆LT衬底材料界面上,常常存在着应力、晶格失配、缺陷等问题。

这些问题会导致材料的晶格畸变和结构杂质的形成,影响拉曼晶圆的光电性能。

为了解决这些问题,可以通过界面控制和应力调控技术来优化拉曼晶圆的界面结构和性能。

界面控制技术包括衬底前处理、表面清洁和预测等方法,用于改善拉曼晶圆LT衬底材料的表面质量和界面结构。

应力调控

技术则是通过在衬底生长过程中控制材料的应力分布和缓解晶格失配,来减少界面应力和缺陷的形成。

通过界面控制和应力调控技术,可以改善拉曼晶圆LT衬底材

料的界面结构和质量,提高拉曼晶圆的光电性能和稳定性。

这对于应用于光电子器件和半导体器件等领域具有重要的意义。

最新纳米薄膜与粉体

做出了黑色氮化钛,但这一结果还有赖于进一步分析。

2 纳米晶体金刚石薄膜材料

我们用磁过滤等离子体技术在室温下沉积的不含H的纳米金

刚石薄膜中的sp3含量达到90%以上,硬度可高达80GPa, 远

华新电阻规格书

Functional code X : Thick film low ohm M : Metal low ohm N : Metal low ohm, high power W : Thick film low TCR P : Thick film low TCR high power ( 2512 size=2 watt, 2010 size=1 watt, 1210 size=0.5 watt, 1206 size=0.5 watt,

R002

Tolerance F : +/- 1% J : +/- 5% P : Jumper

Packaging code P : 4” reel taping T : 7” reel taping A : 7” reel taping 15Kpcs Q : 10” reel taping G : 13” reel taping R : 0603 2mm pitch taping B : Bulk K : Bulkcase

Termination code L = Sn base (Lead free) 5 3E SSP (total)

WW

25

M

F

T

L

Type code WW: R< 1ohm MW: R< 1ohm Automotive SW: R< 1ohm Anti-sulfuration

Size code 25 : 2512 (6432) 20 : 2010 (5025) 18 : 1218 (3248) 12 : 1206 (3216) 10 : 1210 (3225) 08 : 0805 (2012) 06 : 0603 (1608) 04 : 0402 (1005)

表面等离子体无掩膜干涉光刻系统的数值分析(英文)

表面等离子体无掩膜干涉光刻系统的数值分析(英文)

董启明;郭小伟

【期刊名称】《光子学报》

【年(卷),期】2012()5

【摘要】表面等离子体激元具有近场增强效应,可以代替光子作为曝光源形成纳米级特征尺寸的图像.本文数值分析了棱镜辅助表面等离子体干涉系统的参量空间,并给出了计算原理和方法.结果表明,适当地选择高折射率棱镜、低银层厚度、入射波长和光刻胶折射率,可以获得高曝光度、高对比度的干涉图像.入射波长为431nm 时,选择40nm厚的银层,曝光深度可达200nm,条纹周期为110nm.数值分析结果为实验的安排提供了理论支持.

【总页数】7页(P558-564)

【关键词】干涉光刻;表面等离子体激元;克莱舒曼结构

【作者】董启明;郭小伟

【作者单位】电子科技大学光电信息学院

【正文语种】中文

【中图分类】TN305.7

【相关文献】

1.光胶做挡光层的紫外光刻掩膜用于高聚物芯片表面选择性光化学改性 [J], 孔泳;陈恒武;云晓;郝振霞;方肇伦

2.表面等离子体干涉光刻理论计算 [J], 王向贤;叶松;余建立;许雪艳;许明坤

3.基于DMD无掩膜光刻快速制作亲疏水图案化表面 [J], 陈鹏;李木军

4.一种提高无掩膜光刻机图形质量的方法 [J], 李备;朴林华;王育新;张严

5.基于数字微镜器件的无掩膜光刻技术进展 [J], 张思琪;周思翰;杨卓俊;许智;兰长勇;李春

因版权原因,仅展示原文概要,查看原文内容请购买。

一种提高高阻衬底电感性能的方法[发明专利]

![一种提高高阻衬底电感性能的方法[发明专利]](https://img.taocdn.com/s3/m/89e49a09f8c75fbfc67db2e5.png)

专利名称:一种提高高阻衬底电感性能的方法专利类型:发明专利

发明人:黎坡

申请号:CN201410465852.8

申请日:20140912

公开号:CN105470105A

公开日:

20160406

专利内容由知识产权出版社提供

摘要:本发明提供了一种提高高阻衬底电感性能的方法,包括:提供高阻硅衬底,并且在高阻硅衬底上的中间层中的电感区域中形成有电感;在中间层上形成钝化层;减薄电感区域上的钝化层的厚度。

在本发明的提高高阻衬底电感性能的方法中,对电感区域的钝化层的厚度减薄,使得电感性能得到显著提高。

申请人:上海华虹宏力半导体制造有限公司

地址:201203 上海市浦东新区张江高科技园区祖冲之路1399号

国籍:CN

代理机构:上海思微知识产权代理事务所(普通合伙)

代理人:郑玮

更多信息请下载全文后查看。

5g滤波器陶瓷类型

5g滤波器陶瓷类型

5G滤波器中常用的陶瓷材料有以下几种:

1. 铝氧化物(Alumina):具有高温稳定性、低介电损耗和良好的机械性能,是一种常用的5G滤波器陶瓷材料。

2. 钛酸钡(Barium Titanate):具有良好的介电性能和较高的介电常数,可以用于制备高频率的5G滤波器。

3. 铈钛矿(Perovskite):具有较高的介电常数,适用于制备高频率的5G滤波器。

4. 铝镧石(Aluminum Lanthanum Silicate):具有较高的介电常数和较低的损耗,可以用于制备高频率的5G滤波器。

5. 氧化锆(Zirconia):具有高介电常数和优异的稳定性,可以用于制备高频率的5G滤波器。

以上是一些常用的5G滤波器陶瓷材料,不同的应用场景和要求可能会选择不同的材料。

高品质金刚石厚膜的微波等离子体cvd沉积技术

高品质金刚石厚膜的微波等离子体cvd沉积技术下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!高品质金刚石厚膜的微波等离子体CVD沉积技术1. 引言在现代科技领域中,金刚石薄膜因其优异的物理和化学性质,在各种应用中展现出巨大的潜力。

微米纳米熔融石英基滤波器芯片加工

微米纳米熔融石英基滤波器芯片加工微米纳米熔融石英基滤波器芯片加工技术是一项新型精密微型加工技术,它可以制造出尺寸在几微米到几百微米,精度达到几微米以内的微芯片滤波器,并且可以采用内置的精密再现度。

该技术的基本原理是通过熔融石英精密加工芯片,使滤波器芯片表面粗糙度和尺寸精度满足特定的要求。

熔融石英可以保持着非常高的温度,使得熔融石英能够通过精确地控制高温来完成需要的精密加工。

首先,将芯片放置在熔融石英的外壳中,然后将外壳加热,利用熔融石英的外壳将芯片加热,使得芯片表面熔融,并形成一个滤波芯片,滤波器芯片的尺寸精度和粗糙度都可以得到保证。

微米纳米熔融石英滤波器芯片加工技术的应用非常广泛,可以应用于通信设备、医疗设备以及电子设备等方面,比如FET滤波器、低通滤波器、带通滤波器、高通滤波器、带阻滤波器、多沟道滤波器和各种复杂的滤波器等等,都可以通过微米纳米熔融石英滤波器芯片加工技术来制造。

在微米纳米熔融石英滤波器芯片加工技术的应用过程中,大多数都需要自动化加工,这样才能保证滤波器芯片的加工精度,才能达到设计的功能要求。

微米纳米熔融石英滤波器芯片加工技术在微米纳米加工技术的发展中,已经形成了良好的发展格局,它的应用及其重要性,也受到了广泛的关注。

因此,微米纳米熔融石英滤波器芯片加工技术在精密加工领域中具有十分重要的意义,不仅可以满足客户对高精密度和尺寸精度

的要求,而且可以提高器件的节能性能,有利于降低电子设备的功耗,从而为社会的发展和可持续发展做出自己的一份贡献。

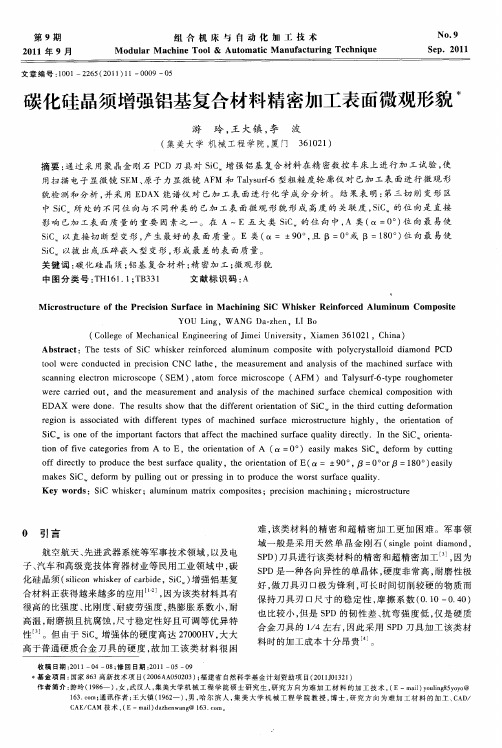

碳化硅晶须增强铝基复合材料精密加工表面微观形貌

sa nn lcr n mir s o e( E ) ao fre mir so e ( M )a d Tay uf6 tp o g o tr c n ig ee t co c p S M , tm o c co c p AF o n ls r一 ・ e ru h mee y

w ee c  ̄i d o t n he m e s r m e ta nay i f t a h ne u f c h m ia o p ii n wih r a e u ,a d t a u e n nd a l ss o he m c i d s ra e c e c lc m osto t ED AX e e d n w r o e. Th e u t ho t tt e dif r n re t t n o C i h hid c ti g deo m ai n e r s ls s w ha h fe e to in a i fSi o n t e t r u tn f r to r g o s s o it d e i n i a s c ae wi d fe e t t p s f m a h n d ura e t h if r n y e o c i e s f c m ir sr c u e i h y, t e re ai n f c o tu t r h g l h o intto o

Si i n ft m po tntf co st ta f c h a h n d s r a e q aiy dr c l I h C o in a C so e o he i ra a t r ha fe tt e m c i e u f c u lt ie t y. n t e Si re t —

用扫描 电子 显微 镜 S M、 子 力显微镜 A M 和 T lsr6型粗糙 度轮 廓仪 对 已加 工 表 面进行 微 观 形 E 原 F ayuf 一

韩国通过研究量子效率与外延层厚度之间关系提高HgCdTe焦平面阵列响应均匀性

0 l l

f

个 用 生 长 在 C Z T 衬 底 上 的 d ne x0 -. 3的液 相 外 延 H C T g d e制 备 的 间距 为 3 1 的 3 0 26元 焦 0m z 2 ̄ 5 平 面 阵 列 。他 们 用 傅 里 叶 变 换 红 外 光谱 仪测 量 了 H C T g d e外 延 层 的厚 度 。测 量 时所 用 的狭 缝 尺 寸 为 5 × 0 i 。每 2ll 0 5g n Il I l 测 量 一 次 傅 里 叶 变 换 红 外 透 射 光谱 。 所 周 知 ,由于 外 延 层 边 众 界 处 的 多次 反 射 ,Hg d e外延 CT 层 会 有 干 涉 条 纹 。 由这 些 条 纹 的 频 率 可 以计 算 出外 延 层 的厚 度 ,即 d / n, 里 的 n为 折 射 =f2 这 指 数 , f 条 纹 频 率。图 1所 示 为 为典 型 的液 相 外 延 生长 H C T g de 晶片 的厚 度 绘 图。 中一 般 可 以 从 发 现, 1mm ̄ 4 面 积 内外 在 0 1mm 延 层 厚度 存 在 1p 的 变 化 。 0. m

韩 国 isse 公 司 是 韩 国 3y tm 焦 平 面 阵 列 。但 红 外 成 像 系 统 电二极 管像 元 组成 。其每 个 像 研 究 开 发 红 外 传 感 器 和 红 的 性 能 依 然 受 到 空 间 噪 声 和 时 元 的 非 均 匀 量 子 效 率 会 在 输 出 响 应 中 以 非 均 匀 性 表 现 出来 。 间 噪 声 的影 响 ,因此 ,响 应 均 匀 影 像 关 联 系 统 的风 险 企 业 。 公 司 自 20 年 起 开 始 研 制 性 是 现 代 焦 平 面 最 重 要 的 参 数 为 了 提 高 红 外 焦 平 面 的响 应 均 03 之 一 , 同 时 也 是 像 元 可 操 作 性 匀 性 ,韩 国研 究 人 员 对 量 子 效 :d e二 维 红 外焦 平 面 阵列 , CT 和 成 品 率 的 一 个 关 键 因 素 。红 率 与 外 延 层 厚 度 之 间 的关 系 进 已经 研 制 出 了 适 合 在 野 外 使 他 的 3 0 2 6元 H C T 红 外 外 焦 平 面 阵 列 由 大 量 单 个 的 光 行 了研 究。研 究 时, 们 采 用 了 2× 5 g de

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PolyMax™ Enhanced Thin PV Wafers Technology

© 2009 Silicon Genesis Corporation. All rights reserved.

Thin Wafers Technical Considerations

PolyMax™ Wafer Manufacturing Flow

Mono Si

1 2 3 4

Growing/Casting

Cropping

Squaring/Bricking

Edge Grinding

5

6

c-Si Ingot Preparation

Detach and Singulate

Cut to Tiles

1 2 3 4 5 6

~50% Poly Loss ~100-120µm Limit

Edge Grinding Gluing Wafer Cutting Wafer Separating Wafer Cleaning Wafer Measuring

© 2009 Silicon Genesis Corporation. All rights reserved.

SiGen PolyMax™ Wire Saw

Slurry

Enhanced c-Si wafers 2x to 4x more wafers Reduction: ~$1/wafer No Kerf-loss

© 2009 Silicon Genesis Corporation. All rights reserved.

Silicon Boule

© 2009 Silicon Genesis Corporation. All rights reserved.

Cleaved Wafers

SiGen PolyMax™ is the Solution

Enhanced c-Si wafers 2x – 4x more wafers Reduction: ~$1/wafer No kerf loss

Thin wafer value

Theoretical improvements in CE to 70um thick wafers Poly savings below 100µm is primary aspect

Thin wafer processing

Must have reduced breakage Micro-crack control will be critical: especially if hidden*

Need to reduce breakage and improve TTV and micro-cracks for: yield and reliability

PolyMax™ Value

Greater wafer capacity from a given plant No kerf loss No consumables No hidden micro-cracks Superior mechanical strength Better TTV No hidden micro-cracks and superior mechanical strength Lower breakage Higher yield Better TTV Higher yield Enables improved cell design

Poor TTV, micro-cracks No roadmap to <100μm High cost of consumables

PolyMax™ Enhanced Silicon

Unique Characteristics:

Thickness uniformity – TTV at 5% Superior mechanical strength – 10X stronger No hidden micro-cracks for downstream failures Scalable thickness - 20μm - 150μm

© 2009 Silicon Genesis Corporation. All rights reserved.

Traditional PV Wafer Fabrication

Mono Si

Growing/Casting

Poly Si

Cropping

Squaring/Bricking

WireSaw

mc-Si “Thick” Solar Cells

PolyMax process 20 - 150µm 150µ

Active Cell Thickness (um)

© 2009 Silicon Genesis Corporation. All rights reserved.

SiGen PolyMax™ vs. Wire Saw Process

© 2009 Silicon Genesis Corporation. All rights reserved.

New processing conditions are already under development

Improved bowing, texturization, metallization, design - reported*

Tighter product distribution

Wafer parameter control gives better process control Tighter distribution allows for better matching lower cost

*See IEEE 33rd PV conference session: Enabling Thin Crystalline Silicon Solar Cells

© 2009 Silicon Genesis Corporation. All rights reserved.

May 15th, 2008

Market Context

Market driver – lower production $/W

Lower cost Higher efficiency Better yield

SiGen PolymaxTM approach to wafering

Lower production cost: ~1$/wafer less vs. wire-saw Improved utilization of Si: about 2-4x less gm/W vs. wire-saw Potentially higher cell conversion efficiency Improved wafer characteristics for better yield Better TTV, strength, micro-crack control

PolyMax™ benefits cascade to all links in the PV production chain

Poly Silicon Ingot Wafer Cell Module

© 2009 Silicon Genesis Corporation. All rights reserved.

© 2009 Silicon Genesis Corporation. All rights reserved.

PolyMax™ Bridges the Gap Between Thick & Thin

Cell Power Conversion Efficiency (%)

C-Si “Thick”throughout the PV Chain

Adds value to the full chain

Poly Silicon Ingot Wafer

Lower $/W

Cell Module

Context

Ingots and wafers represent the biggest portion of the value chain with respect to capital and materials costs

Planarization & Polish

© 2009 Silicon Genesis Corporation. All rights reserved.

SiGen PolyMax™ Process

Two-Step Process: Implant & Cleave Eliminates kerf loss Direct Cleave Process Eliminates consumables SiC, Slurry, Wire Eliminates other systems Gluing Singulation Cleaning Less damage Etch