低功耗物理设计

一种安全SoC芯片的物理设计

护敏感信息 的集成电路芯片。安全芯片的安全包括

N F I 1 . x与 3 . 0标 准 的 N a n d F l a s h控 制 器 ;含嵌 入 两层含义 ,一是安全芯片提供 的安全所能达到 的程 全 能力 , 二是 考 虑 到人 为 破 坏 和 恶 意攻 击 , 式 非易 失性 与静态存储 器 ;具 有 7

d e s i n g i s a l s o d i s c u s s e d . T h e c h i p me e t s t h e t a r g e t s a f t e r s i g n o f a n a l y s i s . T h e c h i p c o n t a i n s 3 6 c l o c k s d o ma i n s , 4

1 引言

安全 芯片是 一种 直 接或 间接使 用 密码 技术 来保

安全芯片应该具备的自身安全性。该安全 S o C芯片

soc技术论文

soc技术论文随着集成电路按照摩尔定律的发展,芯片设计已经进入了系统级芯片(SOC)阶段,下面是由店铺整理的soc技术论文,谢谢你的阅读。

soc技术论文篇一SOC设计中的低功耗技术【摘要】随着以IP(Intellectual Property)核复用为核心的设计技术的出现,集成电路(Integrated Circuit,IC)应用设计已经进入SoC(System on a Chip)时代,SoC是一种高度集成的嵌入式片上系统.,而低功耗也已成为其重要的设计目标。

【关键词】SoC;低功耗技术;功耗评估1.电路中功耗的组成要想实现低功耗,就必须了解电路中功耗的来源,对于CMOS电路功耗主要分为三部分,分别是电路在对负载电容充电放电引起的跳变功耗;由CMOS晶体管在跳变过程中,短暂的电源和地导通带来的短路功耗和由漏电流引起的漏电功耗。

其中跳变功耗和短路功耗为动态功耗,漏电功耗为静态功耗。

以下是SoC功耗分析的经典公式:P=Pswitching + Pshortcircut + Pleakage=ACV2f+τAVIshort+VIleak (1)其中是f系统的频率;A是跳变因子,即整个电路的平均反转比例;是C门电路的总电容;V是供电电压;τ是电平信号从开始变化到稳定的时间。

1.1跳变功耗跳变功耗,又称为交流开关功耗或负载电容功耗,是由于每个门在电平跳变时,输出端对负载电容充放电形成的。

当输出端电平有高到低或由低到高时,电源会对负载电容进行充放电,形成跳变功耗。

有公式(1)第一项可以看出,要想降低跳变功耗就需要降低器件的工作电压,减小负载电容,降低器件的工作频率以及减小电路的活动因子。

1.2短路功耗短路功耗又称为直流开关功耗。

由于在实际电路中,输入信号的跳变需要经过一定的时间。

所以当电压落到VTN和Vdd-VTP之间时(其中VTN和VTP分别为NMOS管和PMOS管的阈值电压,Vdd为电源电压),这样开关上的两个MOS管会同时处于导通状态,这是会形成一个电源与地之间的电流通道,由此而产生的功耗便成为短路功耗。

蓝牙多少功耗算低功耗?低功耗蓝牙是如何实现低功耗的?

蓝牙多少功耗算低功耗?低功耗蓝牙是如何实现低功耗的?目前市场上比较常见的连接技术包括wifi、蓝牙和NFC等等。

WiFi是热点最多的无线连接,但功耗较高;NFC可以说是“最私密”的无线连接,即是近距离连接;那相比wifi高功耗、NFC 近距离,蓝牙的低功耗无缝、快速连接显然是物联网市场中最有力的竞争者。

一、多低的功耗才算是低功耗蓝牙呢?如何界定低功耗蓝牙?平均工作电流为uA级峰值电流不超过15mA采用纽扣电池供电,电池寿命可达数年在很多低功耗应用场景中,是采用纽扣电池来供电的,采用纽扣电池来供电是低功耗蓝牙设计的主要目标,而纽扣电池的使用通常有较为严苛的限制条件。

不过需要注意的是,纽扣电池的能量并不能完全的转化,因为会受到温度的影响。

通常情况下,在零度时仅能提供室温下能量的约80%。

此外电池自身的自放电特性也需要予以考虑,常温下储存,每年容量损失小于2%。

这些因素在计算工作时间时也需要予以考虑。

二、低功耗蓝牙如何实现低功耗?和传统蓝牙技术相比,低功耗蓝牙技术功耗方面的降低主要得益于以下几个方面的改变:1、低功耗蓝牙实现快速连接低功耗蓝牙的机制在于可以实现快速连接,在需要发送命令或传送状态时,可以快速的建立连接,完成后迅速断开连接。

快速连接对于许多低功耗设备而言是一个极大的福音,大大降低了低功耗产品的开发门槛。

重点提一下,按照传统蓝牙协议规范,若某一蓝牙设备正在进行广播,则它不会响应当前正在进行的设备扫描,而低功耗蓝牙协议规范允许正在进行广播的设备连接到正在扫描的设备上,这就有效避免了重复扫描,可以大幅度地降低功耗。

2、低功耗蓝牙减少了待机功耗传统蓝牙设备的待机耗电量大是公认的缺点之一,这与传统蓝牙技术采用16~32个频道进行广播不无关系,而低功耗蓝牙仅使用3个广播通道,这个改变显然大大降低了广播数据导致的功耗。

此外低功耗蓝牙设计了“深度睡眠”状态来替换传统蓝牙的空闲状态,因此这样的设计也节省了最多的能源。

基于SMIC40LL工艺的DDR物理层IP设计

如 图 1所 示 ,DDR接 口电路 按照 功 能分 解 为 控 制器电路和 PHY(物理层 )电路 (包含 10)。物理层

DDR(Double Data Rate)是 JEDEC组 织于 2000 年推出的动态随机存储器接 口规范 ,自DDR规范推 出后 ,该技术迅速得到发展 ,成为绝大部分电子设备 采用的存储器接 口。随着多媒体应用的迅速增加 ,对 数据存取带宽的需求越来越高 ,DDR的规范也进一 步 发 展 到 DDR2、LPDDR2、DDR3、LPDDR3、DDR4

基于 SM_C40LL工艺的 DDR物理层 -P设计

戴颉 ,张浩,杜 丽,王 强,孔 亮 (灿芯半导体 (上 海 )有 限公 司,上海 ,2 01203)

摘要:随着高性能消费电子如智能手机 ,平板 电脑 的迅速普及,对高性能低功耗的 DDR接 口电路 的需求 随之 迅速 增加 。本 文论 述 了在 SMIC40LL工艺上 实现 了高性 能 、低 功耗 、小面积 的 DDR物理 层 IP技 术 , 包括 DDR物理层架构 、DLL设计、10设计和物理 实现。该物理层 IP可以在 ss条件下达到 1 333Mbps的 速率 并在核 心电压稍 稍过 压 下达到 1600Mbps的速率 。 关键词:DDR(双倍速率 );PHY(物理层 );DLL(延迟锁 相环 );SI(信号完整性 );PI(电源完整性 );

Key W ords:DDR (Double Data Rate);PHY (Physical Layergnal Integrity);PI(Power Integrity);CTS (Clock Tree Synthesis)

1 引言

CTS(时钟树 综合 )

Abstract:W ith the rapid growth of high performance consumer electronic devices,such as smart phone,PAD, etc.there are increasing demand for high perform ance,low power DDR interface circuit.This paper addresses the design of high per formance, low power, small area PHY IP on SMIC4OLL process, including DDR PHY architecture design,DLL design,IO design,and physical im plem entation.The PHY IP can run at 1 333M bps under SS corner and can work at 1 600M bps with a little bit overvohage of the core power.

集成电路设计中的关键技术解析

集成电路设计中的关键技术解析一、前言集成电路是当今信息科技崛起的核心技术,它是各种电子设备的掌控中心,为人们的生活提供了便利。

而集成电路的设计是实现其功能的前提,设计的好坏直接关系到芯片的性能和质量。

因此,掌握集成电路设计的核心技术非常重要。

本文针对集成电路设计中的关键技术进行分析和探讨,旨在帮助读者了解和掌握集成电路设计的关键技术,为其在该领域拓展更广阔的发展空间提供技术支持和指导。

二、基础知识在讨论集成电路设计中的关键技术之前,有几个基础概念需要了解。

1、芯片元件设计芯片元件设计在整个集成电路设计中占据着重要的地位,它是实现集成电路功能的最基本要素。

芯片元件设计主要包括三个方面:(1)电路设计,指的是集成电路内部的电路原理图设计。

(2)版图设计,是指对电路布局的设计。

(3)物理设计,包括对电路的物理尺寸、硅片材料等细节设置。

2、库库,是用来存储和组织芯片设计的基础元件(如逻辑门等)和算法的数据库。

在芯片设计过程中,设计工程师可以查找所需元件或算法,从而加快芯片设计进程。

3、封装封装就是将单个芯片先封装成一个元件(例如,芯片上的几个电子器件在消山一般的封装中被组合成一个管),再将这个元件与其他部件组装成完整的设备。

三、关键技术1、低功耗设计技术随着移动设备、物联网等电子设备的不断发展,对于集成电路能够持久、快速运行的实时、高速、高效的需求也在不断增加。

低功耗设计技术应运而生,其重点是降低芯片静态和动态功率,以满足设备的可持续有效运行。

低功耗的关键在于优化电路和设计。

采用节能技术如深度睡眠/待机模式、动态频率调整、静态电压缩等技术,避免无谓的功耗损失。

同时,还要考虑尽可能地缩小电路动态电压的漂移幅度,以减少功耗的损失,提高芯片的稳定性。

2、嵌入式系统设计技术嵌入式系统是指将计算机技术应用于各种电子设备,通过芯片对设备进行控制和处理。

嵌入式系统的应用范围非常广泛,如手机、电视、智能穿戴等。

嵌入式系统设计技术主要包括:架构设计和软件开发。

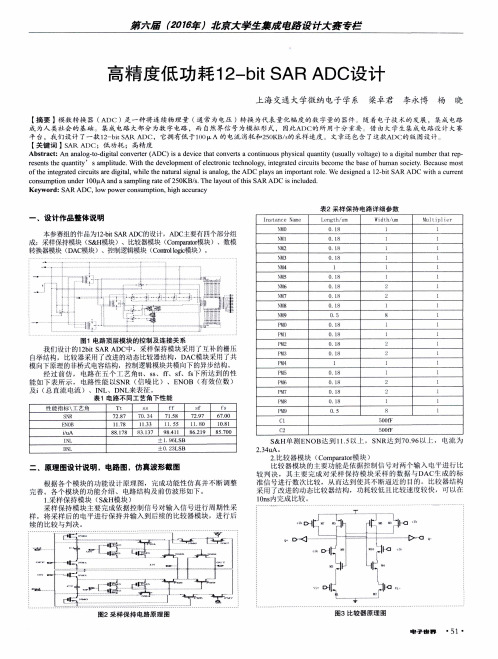

高精度低功耗12-bit SAR ADC设计

.

表 2采 样 保 持 电路 详 细 参 数

一

、

设计作 品整 体说明

I n S t a n c o N { t i l l ( ?

一

1

W i d t f i / u m

1

1

j l t I , r

l

1

N 2

O.1 8

l

l

N M 3

NM 4 N M5 N M6 N M7

O . 1 8

l

1 1

l

I 1 1

O.I 8 0.I 8 O.1 8

,

~ ; of t h e i n t e gr a t e d c i r c u i t s a r e di g i t a l , wh i l e t he n a t ur a l s i g na l i s a na l o g ,t h e ADC pl a ys a n i mp o r t a nt r o l e We de s i g ne d a 1 2一 b i t S AR ADC wi t h a c u r r e nt

NM O

NMl

L e n g t h / u n r

O.1 8

0 l 8

本参 赛组 的作 品为 l 2 一 b i t S A RA D C 的波计,A D C 主要 叫个 部分组 成 :采样保持模块 ( S & H 模块 )、比较 器模块 ( C o mp a r a t o f .  ̄ 块 )、数模 转换器模块 ( D A C 模块 )、控制逻辑模块 ( C o n l r o l l o 舀 c 模块)。

数字集成电路低功耗物理实现技术与UPF

数字集成电路低功耗物理实现技术与UPF孙轶群sun.yiqun@国民技术股份有限公司Nationz Technologies Inc摘要本文从CMOS电路功耗原理入手,针对不同工艺尺寸下数字集成电路的低功耗物理实现方法进行描述,并着重描述了Synopsys UPF(Unified Power Format)对低功耗设计的描述方法。

UPF是Synopsys公司提出的一种对芯片中电源域设计进行约束的文件格式。

通过与UPF 格式匹配的Liberty文件,UPF约束文件可以被整套Galaxy物理实现平台的任何一个环节直接使用,并将设计者的电源设计约束传递给设计工具,由工具完成设计的实现工作,从而实现整套数字集成电路低功耗物理实现的流程。

1.0 概述本文从数字集成电路低功耗设计原理下手,对设计中低功耗的实现技术进行描述,包括完成低功耗设计需要的库资料以及常用EDA工具对低功耗技术实现的方法。

2.0 CMOS电路的低功耗设计原理CMOS电路功耗主要分3种,静态功耗主要与工艺以及电路结构相关,短路电流功耗主要与驱动电压、p-MOS和n-MOS同时打开时产生的最大电流、翻转频率以及上升、下降时间有关,开关电流功耗主要与负载电容、驱动电压、翻转频率有关。

做低功耗设计,就必须从这些影响功耗的因素下手。

3.0 低功耗设计手段及Library需求低功耗的设计手段较为复杂,但对于不同的设计,或者不同的工艺,实现的方法却各不相同。

3.1 0.18um及以上工艺0.18um及以上工艺,在低功耗设计手段上较为有限,主要原因在于,静态功耗很小,基本不用关心。

动态功耗方面,主要的功耗来自于Switching Power,即与负载电容、电压以及工作中的信号翻转频率相关。

减小负载电容,就必须在设计上下功夫,减少电路规模。

减少信号翻转频率,除了降低时钟频率外,只有在设计上考虑,能不翻转的信号就不翻转。

至于电压,由于0.18um及以上工艺的阈值电压有一定的限制,因此,供电电压降低,势必影响工作频率。

SoC物理设计低功耗方法研究

术的发展 符合社 会技术 研究 发 展 的方 向。 由此 可见

C O M S电路动 态功耗 主要 由交流 开关 功耗 和直

流开关 功耗 组成 。

2 2 1 交 流开 关功耗 ..

交流 开关 功 耗 由门 的输 出电容 充放 电形 成 , 是

到 电路 的开关 活 动性信 息 , 进行 反标 , 再 然后 根据工 艺 库 的数 据从 而得 到具 体功耗 。利 用动态仿 真方法 进 行功耗 分析 的关 键 因素 有 两个 : 是 要 能够 提供 一 合 适 的输 人信 号矢 量 ; 是需 要 足够 长 的时 间进行 二

式 中 , 为节点 的 翻转概 率 为电路 时钟频 率 。

动 态仿 真 以确 钟 是 一种应 用较 为广 泛和成熟 的低功耗

设 计技 术 。它通 过减 少 电路 中冗 余 状 态 翻转 , 让一 些 暂 时不工作 的单 元 处 于 非 触 发状 态 , 当需 要 这些 单 元工 作时 , 以用 使 能 信 号 触发 它 们 。借助 门控 可

3 3 操作 数 隔离 .

在 深亚微 米工 艺下 , 过技术 改 善 , 路功耗 和 通 短 泄漏功 耗能被 减小 到 可 以忽 略 的 程 度 , 时开 关 功 此 耗 就成 了主 要 因素 。然 而 当工 艺 技 术 发 展 到 9 n 0m

操作 数隔离 的核 心 思想是 增加额 外 的数 据选择

2 2 2 直流开 关功 耗 ..

在 实 际 电路 中 , 人 信 号从 低 到 高或 者 从 高 到 输 低 的跳 变过程 总是需 要一 定 的时 间 。因此 当输人 电

压 落到 和 。 } 区间 内时 ( 和 分别 一I 的 为 N S管 和 P S管 的 阈值 电 压 ) 两 管 会 同时 MO MO , 处于导通 状态 , 而在 电源 与 地 之 间产 生 了一 条 电 从

asic电路设计 -回复

asic电路设计-回复[aic电路设计] 是指以应用特定集成电路(Application Specific Integrated Circuit,ASIC)技术为基础,设计和开发用于特定应用的定制化集成电路的过程。

ASIC电路设计在当今科技领域起着重要作用,本文将逐步解释ASIC电路设计的关键步骤,并介绍其中的一些关键技术和应用领域。

第一步:需求分析ASIC电路设计的第一步是进行需求分析。

这涉及到理解客户对电路性能、功耗、面积和成本等方面的要求。

只有明确需求,才能确保设计的输出与预期相符。

第二步:架构设计基于需求分析,设计师需要进行架构设计。

这包括确定电路的整体结构和功能模块,以及模块之间的通信方式和数据流。

架构设计决定了电路的整体性能和灵活性。

第三步:电路设计在电路设计阶段,设计师将电路架构转化为具体的逻辑电路和电路原理图。

这包括选择合适的数字或模拟电路组件,进行逻辑门和时序设计,以及电路仿真和验证。

第四步:物理设计物理设计是将电路设计转化为实际的物理芯片版图的过程。

这包括划分电路版图,设计电路布局和布线,以及进行电磁兼容性和功耗优化。

物理设计对最终电路的性能和面积至关重要。

第五步:验证和仿真验证和仿真是确保电路设计符合预期要求的重要步骤。

通过使用专业的EDA工具(如Verilog和VHDL)进行仿真和验证,设计师能够检测和纠正潜在的逻辑和时序错误,以确保电路的正确性和稳定性。

第六步:制造与测试一旦电路设计完成并通过验证,接下来是进入制造和测试阶段。

制造包括使用光刻和蚀刻等工艺将电路版图转化为实际的芯片。

测试则包括芯片的功能、性能和可靠性测试,以确保芯片在实际应用中的可用性。

ASIC电路设计的关键技术:1. 逻辑门设计:逻辑门设计是将数字逻辑电路设计转化为逻辑门电路的过程。

通过选择合适的逻辑门类型和布局,可以实现高速、低功耗和小面积的数字电路设计。

2. 时序设计:时序设计涉及到电路中各个时钟域之间的时序关系与处理。

低功耗设计物理实现方法

低功耗设计物理实现方法

低功耗设计物理实现方法有很多,以下列举了一些常见的方法:

1. 电源管理:通过使用功率管理电路和适当的电源管理策略,可以降低电路的静态功耗。

例如,使用睡眠模式以及动态电压和频率调节技术可以降低电路在闲置状态下的功耗。

2. 时钟管理:减少时钟频率可以降低电路的功耗。

通过优化时钟分配和时钟树设计,可以消除时钟冗余和减小时钟延迟,从而降低功耗。

3. 电路优化:通过使用优化的电路设计技术,如逻辑合成和优化、布局和布线优化,可以减小电路的面积和功耗。

4. 错误容忍设计:使用纠错码、校验位等技术来检测和修复数据传输过程中发生的错误,从而减少重传或重新计算的次数,降低功耗。

5. 采用低功耗器件和技术:选择具有低功耗特性的器件和技术,如低功耗CMOS器件、偏置和传输门技术,可以降低电路的

功耗。

6. 优化电源网络设计:通过设计适当的电源网络和电源噪声滤波器,可以降低功耗和噪声干扰。

7. 动态电压和频率调节:根据电路的工作负载情况,动态调整电压和频率,以降低功耗和延长电池寿命。

8. 优化数据传输:采用更高效的通信协议和数据传输机制,减少数据传输的次数和数据传输的距离,从而降低功耗。

9. 优化功耗分析:使用功耗分析工具和技术,对电路进行功耗建模和分析,找出并优化功耗较高的部分。

以上仅列举了一些常见的低功耗设计物理实现方法,具体的实践中还可以根据具体的需求和应用场景做出更具体的优化和调整。

soc芯片开发方法

soc芯片开发方法随着科技的快速发展,soc(System On Chip)芯片已成为现代电子设备中不可或缺的核心部件。

它集成了多种功能模块,为各类电子产品提供了强大的处理能力。

本文将详细介绍soc芯片的开发方法,帮助读者了解这一领域的相关知识。

一、soc芯片概述soc芯片,即系统级芯片,是将多种功能模块集成在一块芯片上的高度集成化产品。

它具有高性能、低功耗、小尺寸等特点,广泛应用于智能手机、平板电脑、可穿戴设备等领域。

二、soc芯片开发流程1.需求分析在soc芯片开发初期,首先要进行需求分析,明确芯片的应用场景、性能指标、功耗要求等。

需求分析是整个开发过程的基础,对后续设计工作具有指导意义。

2.架构设计根据需求分析,设计soc芯片的架构。

这包括处理器核心、内存、外设接口、电源管理模块等。

架构设计要充分考虑性能、功耗、面积等多方面因素,力求实现最优的平衡。

3.逻辑设计在架构设计的基础上,进行逻辑设计。

逻辑设计主要包括各功能模块的详细设计、接口定义、时序分析等。

这一阶段需要使用硬件描述语言(如Verilog、VHDL等)进行描述。

4.仿真验证在逻辑设计完成后,需要进行仿真验证,确保设计的正确性和可靠性。

仿真验证主要包括功能仿真、时序仿真和功耗仿真等。

5.物理设计物理设计是将逻辑设计转化为实际电路的过程,主要包括布局、布线、版图绘制等。

这一阶段要考虑信号完整性、电源噪声、热效应等因素,确保芯片的性能和可靠性。

6.制造与测试将设计好的soc芯片发送至晶圆代工厂进行制造。

制造完成后,进行封装、测试,确保芯片的质量和性能符合预期。

三、soc芯片开发方法1.模块化设计模块化设计是soc芯片开发的核心方法。

通过将复杂的功能划分为多个独立的模块,降低设计复杂度,提高开发效率。

2.面向复用设计面向复用设计是指在设计过程中,充分考虑已有资源的复用。

这有助于缩短开发周期,降低成本。

3.高级综合高级综合是将高级描述语言(如C、C++等)转化为硬件描述语言的过程。

智能硬件中的低功耗设计策略

智能硬件中的低功耗设计策略智能硬件已经成为了现代社会的重要组成部分,它们的出现与普及带来了许多便利和创新。

然而,由于大多数智能硬件需要长时间的运行和频繁的充电,低功耗设计成为了智能硬件设计中的重要考虑因素。

本文将探讨智能硬件中的低功耗设计策略。

1. 芯片级别的低功耗设计在智能硬件的设计中,芯片是核心组件之一,决定了整个硬件的性能和功耗表现。

为了实现低功耗设计,在芯片级别可以采取以下策略:(1)优化电源电压:通过将电源电压降低到最低限度,可以降低整个芯片的功耗。

例如,采用动态电压调整技术(DVC),能够根据芯片的工作负载自动调整电源电压,以达到节能的效果。

(2)降低时钟频率:将芯片的时钟频率降低到最低限度,能够有效降低功耗。

可以根据实际需求,动态地调整时钟频率,以平衡性能和功耗的要求。

(3)优化器件选择:选择功耗较低的器件,如低功耗微控制器(MCU)、低功耗传感器等。

这些器件在设计中已经经过了功耗优化,可以很好地满足低功耗要求。

2. 系统级别的低功耗设计除了芯片级别的低功耗设计,系统级别的设计也是实现低功耗的重要手段。

(1)优化功耗相关的软件算法:在设计智能硬件时,需要针对具体的应用场景进行功耗相关的软件算法优化。

通过合理利用睡眠模式、任务调度等技术,实现系统在低功耗状态下的工作。

(2)合理配置硬件模块的运行模式:智能硬件通常由多个模块组成,如屏幕、无线模块、感应器等。

在设计中,需要根据实际需求合理配置这些硬件模块的运行模式,避免不必要的功耗消耗。

(3)充电和能量管理:对于需要长时间运行的智能硬件来说,充电和能量管理是至关重要的。

合理设计充电模块和能量管理系统,可以提高电池的使用寿命,并有效降低功耗。

3. 优化用户交互界面用户交互界面是智能硬件与用户之间沟通的重要途径,也是功耗的一大来源。

因此,在设计用户交互界面时,需要采取措施降低功耗。

(1)优化背光和屏幕亮度:背光和屏幕亮度是屏幕功耗的主要来源,可以通过合理控制背光亮度和自动调节屏幕亮度的技术,来减少屏幕功耗。

基于FPGA_的5G_物理层LowPHY_设计

doi:10.20149/ki.issn1008-1739.2024.02.010引用格式:范晓星.基于FPGA 的5G 物理层LowPHY 设计[J].计算机与网络,2024,50(2):150-155.[FAN Xiaoxing.Design of 5G Physical Layer LowPHY Based on FPGA[J].Computer and Network,2024,50(2):150-155.]基于FPGA 的5G 物理层LowPHY 设计范晓星1,2(1.河北远东通信系统工程有限公司,河北石家庄050200;2.专网通信设备与技术河北省工程研究中心,河北石家庄050200)摘㊀要:在对5G O-RAN 架构及物理层功能研究的基础上,设计实现了基于现场可编程门阵列(Field Programmable Gate Array,FPGA)的5G 物理层LowPHY 功能模块㊂通过对5G 物理层LowPHY 的功能进行分析,制定了总体设计方案,将功能模块划分为上行LowPHY 模块㊁下行LowPHY 模块及物理随机接入信道(Physical Random Access Channel,PRACH)LowPHY 模块㊂针对LowPHY 数据处理量大的特点,选用在数据处理方面具备高性能㊁低时延㊁低功耗优势的FPGA 器件来实现㊂将设计的LowPHY 功能模块与其他模块集成为O-RU 单元,在5G NR 系统中进行测试验证,测试结果表明本设计满足了项目需求,实现了设计目标㊂关键词:5G;物理层;现场可编程门阵列;LowPHY;物理随机接入信道;FFT;IFFT;循环前缀;正交频分复用中图分类号:TN929.5文献标志码:A 文章编号:1008-1739(2024)02-0150-06Design of 5G Physical Layer LowPHY Based on FPGAFAN Xiaoxing 1,2(1.Hebei Far-East Communication System Engineering Co.,Ltd.,Shijiazhuang 050200,China ;2.Hebei Engineering Research Center for Private Network Communication Equipment and Technology ,Shijiazhuang 050200,China )Abstract :Based on the research of 5G O-RAN architecture and physical layer function,the 5G physical layer LowPHY function module based on Field Programmable Gate Array (FPGA)is designed and implemented.Based on the analysis of the LowPHY function of 5G physical layer,the overall design scheme is developed,and the functional modules are divided into upstream LowPHY module,downstream LowPHY module and Physical Random Access Channel (PRACH)LowPHY module.Aiming at the characteristics of large data processing capacity of LowPHY,FPGA devices with high performance,low delay and low power consumption in data processing are selected.The designed LowPHY function module is integrated with other modules into O-RU unit,which is tested and verified in 5G NR system.The test results show that the design can meet the project requirements and realize the design objectives.Keywords :5G;physical Layer;FPGA;LowPHY;PRACH;FFT;IFFT;cyclic prefix;OFDM收稿日期:2023-12-210㊀引言随着移动通信技术的发展,第四代移动通信系统(4G)在现代社会获得了广泛应用,人们的生活方式发生了巨大变化㊂在智能终端普及与移动互联网发展的双重因素作用下,移动互联网的多媒体业务获得了长足发展,4G 已经无法满足未来用户更低时延㊁更快速率㊁更大容量的通信需求,因此具有更高性能指标要求的第五代移动通信系统(5G)的研究是通信发展的必然趋势[1-2]㊂5G 在高清视频传输[3]㊁物联网和智能制造[4]等方面已经获得了比较好的效果㊂物理层是5G 新空口(5G New Radio,5G NR)的核心,提供物理介质传输bit 信号流所需要的功能,包括编解码㊁调制解调㊁时频资源映射,并以传输信道的方式为上层提供服务㊂5G 物理层在4G 物理层基础上进行了一些全新的设计[5],采用正交频分复用(Orthogonal Frequency Division Multiplexing,OFDM)技术作为物理层设计基础,引入可扩展的OFDM 子载波间隔参数配置,采用循环前缀OFDM;采用新型信道编码方案低密度奇偶校验码(LDPC),运算量低㊁时延低且硬件实现方便;采用大规模MIMO 技术[6],在多天线处理中实现更高的空间解析度和更高的频谱效率㊂本文结合项目实际需求,设计了基于FPGA 器件实现的5G 物理层LowPHY 功能模块,应用在5G NR 系统中㊂1㊀O-RAN 架构分析O-RAN 是一种开放式无线接入网,允许不同设备商开发的网络设备间互操作㊂O-RAN 的理念是基于开放式体系结构㊁开放式接口和开放式空间,通过开放协议和接口来支持不同厂商的设备㊁软件和服务的互操作性㊂通过借助开放式体系结构和接口,推进无线通信产业的开放化㊁互联互通和创新,打破当前封闭式网络结构,降低部署㊁运维成本,推动数字经济的发展㊂O-RAN架构如图1所示㊂图1㊀O-RAN架构O-RAN架构是开放式无线接入网架构,将基带单元和射频单元分割为3个不同的功能模块和协议层[7],每层设备均可以由不同的厂商提供㊂O-CU (中央单元)和核心网之间的接口称为回传,O-DU (分布单元)和O-CU之间的接口称为中传,O-DU和O-RU(射频单元)之间的接口称为前传㊂各分层单元的实现功能如图2所示㊂O-RU负责处理射频和物理层下部(LowPHY);O-DU负责执行物理层上部(HighPHY)㊁介质访问控制(MAC)和无线电链路控制(RLC)的任务;O-CU负责管理分组数据聚合协议(PDCP)㊁服务数据适配协议(SDAP)和无线电资源控制(RRC)协议实体㊂图2㊀O-RAN分层功能2㊀总体方案设计2.1㊀LowPHY功能分析O-RAN联盟选择Option7-2x拆分选项将5G PHY分为HighPHY与LowPHY,5G PHY下行㊁上行传输链路需要完成的工作分别如图3与图4所示㊂图3㊀5G PHY下行功能框图图4㊀5G PHY上行功能框图如图3所示,HighPHY下行方向需要完成的功能是:同步信号及辅助同步信号(PSS/SSS)处理㊁物理广播信道(PBCH)处理㊁物理下行控制信道(PD-CCH)处理㊁物理共享数据信道(PDSCH)处理㊁参考信号(RS)处理及RE映射(Resource Element Map-ping)㊂RE映射后的数据进入LowPHY部分进行进一步下行处理,在LowPHY部分中,LowPHY主要完成的工作有:OFDM相位补偿㊁IFFT和插入循环前缀(Cyclic Prefix,CP)功能,LowPHY处理完成的下行数据进入射频处理部分发射出去㊂如图4所示,在上行方向,射频部分接收的数据进入5G PHY处理后,首先是LowPHY的数据信息处理,LowPHY对帧数据进行去CP操作,然后分为2路,一路进行OFDM相位补偿㊁FFT;另一路是物理随机接入信道(Physical Random Access Channel,PRACH)的数据处理,频率移位㊁DDC(数据下采样)和FFT㊂LowPHY 处理完成的数据进入HighPHY 部分进一步处理,HighPHY 上行方向主要完成的功能是:RE 解映射㊁上行控制信道(PUCCH)处理㊁上行共享信道(PUSCH)处理㊁随机接入信道(PRACH)处理和RS 处理㊂2.2㊀方案设计本设计以Xilinx 公司UltraScale +及以上系列产品作为设计芯片平台㊂UltraScale +系列采用最先进的16ns /20ns 纳米制程工艺,可以实现更快速㊁更高效和更低功耗的系统设计㊂同时,此系列产品具备丰富的DSP48E2和36kB RAM 资源,十分适合通信算法的实现,此外Xilinx 开发工具具有丰富的IP 资源,可以大大提高软件设计效率㊂将LowPHY 处理模块分为3个子模块进行设计[8],分别是DL LowPHY Process 模块㊁UL LowPHY Process 模块和PRACH LowPHY Process 模块㊂方案具体功能模块示意如图5所示㊂从工程实现角度出发,在协议规定的功能模块基础上,增加IQ_map 模块和IQ_Demap 模块,此2种模块是为了解决无线帧数据与FFT /IFFT 之间数据匹配重构而设计㊂图5㊀LowPHY FPGA 模块示意图5所示的LowPHY 数据处理模块处理的是一路天线数据,对于2T2R 或4T4R 设备来说,各天线的数据处理过程是独立的,在FPGA 工程中复制相应数量的模块即可完成多天线数据处理㊂3㊀FPGA 软件设计3.1㊀下行LowPHY 实现根据图5中下行LowPHY 子功能模块划分,按数据流方向依次实现其FPGA 设计[9-10]㊂相位补偿模块的功能是完成HighPHY 下发的相位补偿因子缓存㊁根据不同symbol 号查找不同的相位因子㊁将天线数据以复数乘法的方式进行相位补偿处理以及将复乘后的IQ 数据进行截位处理㊂对于补偿因子缓存及因子查找输出功能,以RAM 为核心实现,将相位因子缓存进RAM,后续不同的symbol 数据流到此处理过程时,相位因子选取逻辑通过符号数据其time 信息的symbol 号读取相应的相位因子供下级复数乘法处理使用㊂复数乘法器将IQ (I㊁Q 均16bit)数据与其相对应相位因子进行相乘,完成相位补偿处理,此时乘法器输出I /Q 数据为32bit,通过截位操作,丢弃低16bit,保留高16bit 数据来实现功率控制,完成相位补偿处理㊂在5G FR1中,有273个物理资源块(Physical RB,PRB ),每个PRB 有12个子载波,共3276(273ˑ12)个采样点,而5G IFFT 处理的采样点为4096,因此IQ 数据在进行IFFT 处理前需要进行补0及数据重构,此步通过2个RAM 以乒乓的方式控制读写来实现IFFT 输入数据的排序,命名为IQ_map 模块㊂具体数据重构逻辑如图6所示,将1个symbol 数据的3276个点缓存后,分为两部分,首先读出高部分1638个32bit 数据,在1639~2459位置填充0值,再读出低部分1638个32bit 数据㊂图6㊀下行数据重构格式示意IFFT IP 核定制部分截图如图7所示㊂图7㊀IFFT IP 定制部分配置IFFT 功能通过使用Xilinx 公司官方IP 核来实现,IP 定制的配置是:数据点4096,实现架构Pipe-lined,Streaming I /O,数据格式Fixed Point,Un-scaled,数据输入㊁系数输入均为16bit㊂经过IFFT 处理的数据,截位处理恢复到I /Q 均为16bit 的格式,根据其symbol 号来动态配置添加CP,至此下行帧数据完成了LowPHY 处理,频域数据转为时域数据,传递到下一阶段进行数字上变频(DUC)㊁波峰消减(CFR)和数字预失真(DPD)数字域处理,直至DAC 后在射频域发射至无线空间㊂3.2㊀上行LowPHY 实现上行是下行的逆过程,数据处理过程极为相似,部分逻辑代码可以移植复用㊂其中,OFDM 相位补偿子模块,上下行均在频域完成,功能一致,上行LowPHY 的FPGA 模块实现直接通过例化上述设计文件的方式实现㊂去CP 子模块,根据symbol 数据的time 信息,判读其CP 长度,以计数器为基准,将CP 数据剔除,最终输出4096点时域symbol 数据完成去CP 操作的symbol 数据进入FFT 模块,进行时域向频域的转换,FFT 功能与IFFT 功能一样,使用IP 核实现,配置保持一致,输出数据进行截位处理,恢复I /Q 均为16bit 的数据格式㊂上行数据重构格式示意图如图8所示㊂图8㊀上行数据重构格式示意IQ_Demap 是IQ_map 的逆过程,按照图8所示的处理方式将FFT 输出的4096点symbol 数据处理成3276点数据㊂实现逻辑依然是通过控制2个乒乓RAM 读写来实现数据重构㊂完成OFDM 相位补偿处理的上行帧数据就完成了LowPHY 处理,传递到HighPHY 进行进一步处理,就完成了5G 上行PHY 处理㊂3.3㊀PRACH LowPHY 实现由于功能相同,PRACH LowPHY 的去CP 模块,直接例化UL 方向的去CP HDL 文件㊂由于prach 的种类很多,不同种类的cp 长度㊁数据长度和重复次数不同,但处理流程相似,增加prach_ctrl 控制逻辑,用于完成对不同prach 场景的控制[11]㊂prach_ctrl 功能逻辑由10ms 帧位置定位㊁slot 号位置定位及symbol 位置定位提取模块构成㊂图9是控制逻辑状态机状态转移图㊂10ms 帧位置定位模块用来检测10ms 帧是否有prach,对应用prach 的10ms 帧的位置输出指示信号到slot 号位置定位模块,然后进一步精确到slot 位置,输出信息到symbol 位置定位提取模块,最终确定prach 的详细位置㊂图9㊀prach_ctrl 状态机状态转移DDC 模块目的是将IQ 数据流搬移至0频,对数据进行降采样操作,实现方式是使用Xilinx 官方FIR 滤波器IP 核,通过多级半带滤波器的滤波㊁抽取,达到设计目标;FFT 模块同样使用FFT IP 核来实现,与Ul LowPHY 中IP 定制参数一致;IQ_Demap模块根据prach 长度命令参数值的大小,通过选择与计数逻辑,输出数据,存至乒乓FIFO 组成的IQ_buf 模块,最终发送至上层HighPHY,完成PRACH LowPHY 的处理过程㊂4㊀功能测试验证LowPHY 功能各单元小模块在完成单元测试后需进行整体功能测试验证㊂作为O-RU 单元的组成部分,将LowPHY 功能与其他功能集成为整机,并在5G 基站系统中进行测试,更加能够测试出设计的性能,因此本设计使用系统测试环境进行功能验证测试㊂对于下行测试,第一种方式使用MAC 层下发测试向量的方式进行测试㊂MAC 层通过配置发送测试数据到HighPHY,HighPHY 将测试数据传输给LowPHY 处理,LowPHY 处理完成的数据经过后级数据处理模块进一步处理最终发射到空间㊂将O-RU 天线口通过衰减器连接至频谱分析仪,可以观测下行信号的EVM㊁星座图等射频指标,通过这些指标可以测试出设计的性能㊂图10是发送ETM3-1a 向量在频谱仪的显示结果,向量ETM3-1a 发送的是100MHz 带宽256QAM 调制数据,可以看到EVM 为2.80,小于标准4.50,满足3GPP 标准,星座图打点清晰,证明在幅度失衡㊁正交误差㊁相位噪声㊁相位误差和调制误差等指标方面,本设计的数据处理功能有比较优良的性能,对于QPSK㊁16QAM 和64QAM 调制数据的测试,结果同样满足标准规定㊂图10㊀频谱分析仪截图㊀㊀对于上行测试和PRACH LowPHY 功能测试,可以合并进行㊂将手机在5G 核心网完成开户,测试其能否入网,并在入网后在手机侧使用Iperf 工具向MAC 层灌包,观测MAC 层接收数据包速率,验证其功能及性能㊂同时MAC 层向手机侧灌包,进一步验证下行性能,为下行功能验证的第2种方式㊂测试系统设置为帧格式2.5ms 双周期,双流灌包㊂图11是2.5ms 双周期的帧结构,每5ms 里面包含5个全下行时隙㊁3个全上行时隙和2个特殊时隙㊂slot3和slot7等为特殊时隙,配比为10ʒ2ʒ2,理论峰值灌包速率,下行660Mb /s㊁上行330Mb /s㊂图11㊀ 2.5ms 双周期帧结构㊀㊀在完成入网的手机上设置上行Iperf 灌包,在MAC 层设置下行灌包,图12是上下行灌包速率统计过程的截图㊂从图中可以看到,左侧显示下行灌包速率约为660Mb /s㊁右侧显示上行灌包速率约为332Mb /s,证明测试手机不但在测试系统完成了入网,验证了PRACH LowPHY 功能,同时,上下行数据通道功能㊁性能良好,也验证测试了UL /DL LowPHY 功能㊂图12㊀上下行灌包速率结果截图㊀㊀以上测试结果表明,本文基于FPGA设计的5G LowPHY功能模块,实现了3GPP标准规定的功能,同时满足指标要求㊂5㊀结束语本文根据实际项目需求,设计实现了基于FPGA 的5G物理层LowPHY功能,并详细阐述了LowPHY 的数据处理过程划分㊁总体方案设计以及在FPGA平台的实现过程,最终通过将功能模块嵌入测试系统的方式对其功能㊁性能进行了测试㊂本文设计的功能模块具备较高的移植适应性,不但可以在多种FPGA型号上运行,还可以根据项目总体设计需要,在不同的O-RAN切分方式下,将功能部署在不同的实体硬件单元设备上,大大扩展了其应用场景㊂参考文献[1]㊀ANDREWS J G,BUZZI S,CHOI W,et al.What Will5GBe?[J].IEEE Journal on Selected Areas in Communica-tions,2014,32(6):1065-1082.[2]㊀尤肖虎,潘志文,高西奇,等.5G移动通信发展趋势与若干关键技术[J].中国科学:信息科学,2014,44(5):551-563.[3]㊀邝野.基于5G网络的无人机超清实时图传系统设计与实现[D].广州:广东工业大学,2022.[4]㊀陈斌,陈武军,樊忠文,等.5G+MEC专网智能制造工厂[J].通信技术,2021,54(1):215-223. [5]㊀王霁超.5G NR物理层软件无线电设计与实现[D].南京:东南大学,2021.[6]㊀章辰.面向5G的大规模MIMO物理层关键技术的研究和仿真[D].北京:北京邮电大学,2020.[7]㊀李剑.O-RAN网络中基于QEE优化的休眠策略研究[D].桂林:桂林电子科技大学,2021.[8]㊀龙凯.5G物理层比特级处理并行架构设计与实现[D].成都:电子科技大学,2020.[9]㊀黄旭.5G通信系统中载波同步帧同步系统的研究[D].南京:南京邮电大学,2019.[10]张越良.5G新空口下行同步和广播信道的仿真与FPGA实现[D].北京:北京邮电大学,2019.[11]朱恒恒.5G移动通信系统物理随机接入信道的实现[D].成都:电子科技大学,2022.作者简介范晓星㊀男,(1987 ),硕士,工程师㊂。

asic设计解决方案

ASIC 设计解决方案简介ASIC(Application Specific Integrated Circuit)即应用特定集成电路,是一种可根据特定应用要求进行定制设计的集成电路。

它具有高度的集成度、低功耗和高性能的特点,被广泛应用于各种领域,如通信、计算机、汽车电子等。

本文将介绍ASIC设计的解决方案以及它在现代电子领域的重要性。

ASIC 设计解决方案的基本流程ASIC设计的基本流程包括需求分析、架构设计、逻辑设计、验证、物理设计和测试等几个阶段。

下面将对每个阶段进行详细介绍。

需求分析需求分析是ASIC设计过程的起点,目的是明确ASIC的功能和性能要求。

在这个阶段,设计团队与客户或系统架构师合作,详细了解所需的功能和性能需求,包括输入输出接口的数量和类型、时钟频率、功耗、可靠性等。

根据需求分析的结果,确定设计的目标和约束条件,为后续的设计提供指导。

架构设计在架构设计阶段,设计团队将需求分析结果转化为一个高层次的硬件结构。

这个阶段主要涉及系统级规划、模块划分和接口定义等工作。

ASIC的架构设计需要考虑到硬件资源的利用效率、功能模块之间的通信和协作方式,以及整体系统的可扩展性和可维护性。

逻辑设计逻辑设计是将架构设计转化为具体的逻辑电路设计的过程。

在这个阶段,设计团队根据架构设计的要求,使用HDL(Hardware Description Language)或图形化工具进行电路设计。

逻辑设计包括电路元件的选型和连接、逻辑功能的实现以及时序和时钟域的设计等。

设计团队需要通过仿真和验证来确保设计的正确性和性能满足需求。

验证验证是ASIC设计过程中非常重要的一步,目的是验证设计是否符合需求,并发现和解决设计中的错误和问题。

验证阶段可以通过多种方法进行,包括仿真测试、形式验证和硬件验证等。

通过验证可以提高设计的可靠性和正确性,减少后续的修复和修改工作。

物理设计物理设计阶段将逻辑电路转化为实际的布局与布线,并进行后端流程的规划和优化。

数字集成电路低功耗物理实现技术与UPF

数字集成电路低功耗物理实现技术与UPF孙轶群sun.yiqun@国民技术股份有限公司Nationz Technologies Inc摘要本文从CMOS电路功耗原理入手,针对不同工艺尺寸下数字集成电路的低功耗物理实现方法进行描述,并着重描述了Synopsys UPF(Unified Power Format)对低功耗设计的描述方法。

UPF是Synopsys公司提出的一种对芯片中电源域设计进行约束的文件格式。

通过与UPF 格式匹配的Liberty文件,UPF约束文件可以被整套Galaxy物理实现平台的任何一个环节直接使用,并将设计者的电源设计约束传递给设计工具,由工具完成设计的实现工作,从而实现整套数字集成电路低功耗物理实现的流程。

1.0 概述本文从数字集成电路低功耗设计原理下手,对设计中低功耗的实现技术进行描述,包括完成低功耗设计需要的库资料以及常用EDA工具对低功耗技术实现的方法。

2.0 CMOS电路的低功耗设计原理CMOS电路功耗主要分3种,静态功耗主要与工艺以及电路结构相关,短路电流功耗主要与驱动电压、p-MOS和n-MOS同时打开时产生的最大电流、翻转频率以及上升、下降时间有关,开关电流功耗主要与负载电容、驱动电压、翻转频率有关。

做低功耗设计,就必须从这些影响功耗的因素下手。

3.0 低功耗设计手段及Library需求低功耗的设计手段较为复杂,但对于不同的设计,或者不同的工艺,实现的方法却各不相同。

3.1 0.18um及以上工艺0.18um及以上工艺,在低功耗设计手段上较为有限,主要原因在于,静态功耗很小,基本不用关心。

动态功耗方面,主要的功耗来自于Switching Power,即与负载电容、电压以及工作中的信号翻转频率相关。

减小负载电容,就必须在设计上下功夫,减少电路规模。

减少信号翻转频率,除了降低时钟频率外,只有在设计上考虑,能不翻转的信号就不翻转。

至于电压,由于0.18um及以上工艺的阈值电压有一定的限制,因此,供电电压降低,势必影响工作频率。

芯片设计中的低功耗技术有何创新

芯片设计中的低功耗技术有何创新在当今科技飞速发展的时代,芯片作为电子设备的核心组件,其性能和功耗一直是人们关注的焦点。

随着移动设备、物联网等应用的普及,对芯片的低功耗要求越来越高。

为了满足这些需求,芯片设计领域不断涌现出各种创新的低功耗技术,为电子设备的续航能力和性能提升带来了新的突破。

一、工艺制程的优化芯片制造工艺的不断进步是实现低功耗的重要基础。

更小的制程节点意味着晶体管的尺寸更小,导通电阻更低,从而能够降低静态功耗和动态功耗。

例如,从 28 纳米制程到 7 纳米制程,芯片的功耗大幅降低。

同时,先进的制程还能够提高晶体管的开关速度,减少信号传输的延迟,从而在提高性能的同时降低功耗。

然而,工艺制程的进步并非一帆风顺。

随着制程越来越小,面临的技术挑战也越来越多,如漏电问题、量子效应等。

为了解决这些问题,芯片制造商们不断研发新的材料和工艺,如采用高介电常数材料、金属栅极技术等,以进一步优化芯片的功耗性能。

二、电源管理技术的创新电源管理是芯片低功耗设计中的关键环节。

动态电压频率调整(DVFS)技术是一种常见的电源管理方法,它根据芯片的工作负载实时调整电压和频率,在负载较低时降低电压和频率,从而减少功耗。

例如,在智能手机中,当处理器处理简单任务时,DVFS 技术会降低其工作频率和电压,以节省电量。

此外,电源门控技术也是一种有效的电源管理手段。

通过关闭暂时不使用的电路模块的电源,可以显著降低静态功耗。

这种技术在芯片处于待机状态或部分模块闲置时能够发挥重要作用,有效延长电池续航时间。

三、架构设计的优化芯片的架构设计对功耗有着重要影响。

采用精简指令集(RISC)架构相对于复杂指令集(CISC)架构,通常能够减少指令执行的功耗。

此外,多核架构的出现使得芯片能够在不同的核心上处理不同的任务,根据负载灵活分配计算资源,从而提高能效比。

在存储架构方面,缓存层次结构的优化也能够降低功耗。

合理设计缓存的大小、命中率和替换策略,可以减少对主存的访问次数,降低访存功耗。

rtl8211f硬件设计

rtl8211f硬件设计RTL8211F是一款高性能、低功耗的千兆以太网物理层收发器。

它具有低功耗特性、支持远距离传输和高速数据传输等特点。

RTL8211F在计算机网络领域具有广泛的应用,比如在路由器、交换机和工控设备中等。

硬件设计中,对于RTL8211F的引脚分配、时钟设计和电源稳定等方面的考虑都非常重要。

下面是对RTL8211F硬件设计的一些参考内容:1. 引脚分配:RTL8211F共有48个引脚,其中包括数据收发、时钟、配置和电源等相关引脚。

在引脚分配设计中,需要根据实际需求将相应的引脚连接到其他硬件部件中,如MAC控制器、PHY接口等。

同时需要注意信号的布线和阻抗匹配,以保证高速数据传输的可靠性。

2. 时钟设计:RTL8211F支持多种时钟源,包括外部晶振时钟和内部RC振荡器等。

在时钟设计中,需要根据实际应用场景选择合适的时钟源,并确保时钟信号的稳定性和精确性。

此外,还需要在设计中考虑时钟的布线、屏蔽和对地布线等,以避免时钟信号的干扰和串扰。

3. 电源设计:RTL8211F对于电源的要求较低,通常采用单一的3.3V电源供电。

在电源设计中,需要保证电源线路的稳定性和纹波控制,以避免电源噪声对正常工作的影响。

此外,还需要注意电源线路的布线和电源线与地线的分离,以减小信号的干扰。

4. 信号完整性:在高速数据传输时,需要考虑信号的完整性。

关注布线规则、阻抗匹配和屏蔽设计等方面,以减小串扰、干扰和衰减,提高信号传输的质量和可靠性。

5. ESD保护:RTL8211F应注意对静电击穿的保护。

为了防止静电对芯片的损害,应在设计中加入合适的ESD保护电路,如TVS二极管。

6. 封装与散热设计:RTL8211F有多种封装形式可供选择,如QFN、LQFP等。

在硬件设计中,需要根据实际应用场景选择合适的封装形式,并设计合理的散热结构,以确保芯片工作温度的控制和散热效果的良好。

总之,RTL8211F的硬件设计需要综合考虑引脚分配、时钟设计、电源设计、信号完整性、ESD保护、封装和散热等多个方面。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

复旦大学硕士学位论文低功耗物理设计姓名:郭小川申请学位级别:硕士专业:电子与通信工程指导教师:曾晓洋20070526第一章功耗的介绍1.1CMOS功耗介绍下图为典型CMOS数字电路反向器的功耗物理组成。

图一:反向器的功耗物理组成C~tOS数字电路无论是在逻辑状态保持还是在动态的逻辑传输都要消耗功耗,其总功耗可以分为三个部分:电平转换功耗,内部功耗和漏电功耗。

P=PS-+P埘+P&(i.1)艮。

电平转换功耗P“。

内部功耗凡漏电功耗4其中V”是N110S的门限电压,‰是PMOS的门限电压,这时在v。

到地之间的NMOS和PMOS就会同时打开,产生从供电端直接到地的导电通路产生短路电流。

内部功耗还包括由于输入端信号翻转而输出端信号不变化而引起的只对器件内部负载充放电的功耗。

在深亚微米工艺工艺条件下。

器件内部各个节点对地电容在输入端信号翻转而输出端信号不变化时充放电引起的功耗之和通常小于总功耗的5%.1.1.3静态漏电功耗(LeakagePower)上面描述的是电路处于工作状态时产生的功耗,当电路通电,没有输入或非正常工作状态下电路依然消耗功耗,我们称之为静态漏电功耗。

它是由门电流和亚阈值电流两部分引起的。

亚阈值电流是当栅极输入电压‰小于阈值电压时产生的,它随温度的升高而增大,随阈值电压的降低而增大。

门电流是由于在MOS管导通时栅极氧化层的降低导致的,它不受温度变化的影响,在90纳米以下工艺,门电流导致的功耗占静态功耗的主导地位。

随着工艺的进步,静态功耗占芯片总功耗的比重逐步提高。

成为ASIC设计工程师关注的重点。

图二:静态功耗占总功耗的比重62.2多阈值电压器件MTCMOS的应用2.2.1MT∞S降低静态功耗方法简介便携式电子设备要求系统在待机模式下具有极低的漏电功耗,比如掌上电脑或手机。

在90纳米工艺技术以下,通过输入状态分配和输入管脚的交换的方式已经很难满足设计的需求,只有关闭在待机模式下的逻辑电路的电源供应才能得到超低的漏电功耗。

通过睡眠晶体管来实现供电电源的门控是现在设计者比较关注的课题。

这种方法又被称为地线门控,多阈值电压技术等。

其实现方法是在工艺技术支持双阈值电压技术的基础上,用低阈值电压晶体管实现器件逻辑功能,以保证期间的高工作频率,然后在器件与电源线或底线之间串行插入高阈值电压的晶体管开关。

如下图所示:图三:通过睡眠晶体管来实现供电电源的门控MTCMOS是通过高阙值晶体管开关的控制段进行有效地功耗控制。

在工作状态,功耗控制信号使能,开关打开,由于开关电阻很小,虚拟供电电压和实际供电电压基本相同:在待机模式时,功耗控制信号关闭开关,从而使漏电电流降低。

功耗控制开关可以加在电源端,也可以加在地端。

在实际应用中,由于NMOS开关同PMoS开关相比具有更小的尺寸和导通电阻的优点,所以通常插入NMOS开关.MTCMOS的应用可分为三种方法:基于门器件的应用(finegrainMTCMOS)。

基于器件组的应用(coarsegrainMT040S)和基于电压区域的应用。

采用比较多的是前两种。

图四:睡眠晶体管在门器件及器件组中的应用2.2.1.1基于门的多阈值电压(FineGrainMr∞S)基于门的多阈值电压器件是在每个低闺值电压的器件供电端supplyport连接MOS开关器件,当期间处于逻辑不需要工作期内,通过控制端口sleepport控制关闭开关器件。

基于门的多阈值电压器件具有以下优点:在器件不需要工作时关掉开关器件,从而关闭了低阈值电压器件的漏电流通道,降低了器件的漏电功耗。

可以优化睡眠控制器件的晶体管尺寸,可以基于器件模型进行精确的时序分析和漏电功耗分析,不需要进行额外的电压降分析。

并且可以通过使用普通的器件库的工具进行物理综合,布局和布线,对于设计者最初应用的设计流程,存在的时序分析优化及电压降分析等不会有太大的影响。

但是,由于基于门的多阈值电压器件在每个低阈值电压的器件内集成了一个睡眠晶体管,从而使得与基于器件组的多阈值相比,增加了器件的尺寸。

并且连接睡眠信号到每一个门单元也增加了物理布线的难度。

(dontuse)。

在将来,睡眠控制管脚将被定义为信号管脚,具有器件部分功能,在逻辑库的功能描述中将出现,将会对睡眠控制管脚进行时序约束。

对于基于门的多阈值电压的设计的网表综合阶段,现在支持的做法是采用没有睡眠控制管脚的逻辑库进行电路的网表综合。

很快可以支持采用睡眠控制管脚设置为不可使用的逻辑库:能够像双阈值电压器件的流程一样实现高速的带有睡眠管脚的单元期间与低速无睡眠管脚器件的相互调换:睡眠管脚将不做连接,在输出的网表中处于悬浮状态。

睡眠管脚的连接需要设计者手工定义添加进网表或手工连接;在器件布局时不需特殊的设置。

在将来,需要支持器件睡眠控制管脚的功能描述,在逻辑综合时自动生成睡眠管脚的连接关系。

但现在,大部分工作都需要设计者手工实现。

对于睡眠控制信号的连接,设计者需要在网表里手工连接,并在进行读入网表后的最初的芯片规划前手工创建睡眠信号的对外管脚,就像添加电源管脚一样,并直需要对睡眠控制信号网络进行多扇出网络的优化或进行虚假的时钟树综合,以便加入缓冲器间使得网络满足物理设计规则和同步各个控制端。

在布线结束后抽取电阻电容的寄生参数后,也需要手工的进行期间的替换或插入。

在将来,这部分手动的工作会有新的函数提供支持。

物理实现的原理图如下:图五:睡眠控制信号网络实现原理图现在手工操作中也可以采用部分工具命令来完成操作,具体包括:睡眠网络,物理端口,逻辑端13,端1:3方向和端1:3连接关系的创建:15理位置产生影响。

需要创建虚拟的地线,正常的单元器件连接到虚地,而睡眠开关通过金属带保证其能正常工作。

图六:基于器件组的多阈值电压方法设计原理图对于睡眠信号的连接有两种方法:使用电源金属带的方法连接,和采用时钟树综合的方法连接。

使用电源金属带的方法不能考虑到达各个开关的时间同步问题。

其睡眠信号连接如下图所示:图七;电源金属带的方法连接睡眠信号采用时钟树综合的方法连接是考虑到开关器件分散于芯片上,从睡眠信号输入端到各个接受端连线延时不等,所以采用时钟树综合的方法插入始终工作的缓冲器,原理如下图所示:图八:时钟树综合的方法连接睡眠信号3.3多供电电压技术的应用3.3.1多电压设计方法(Multi-Voltage)简介动态功耗直接与CV2f有关(c=电容,V=电压,f=频率).动态功耗与电压的平方成正比,则电压的降低同电容和频率的降低相比对降低功耗有着更加显著的作用。

多电压设计是在当今的芯片设计中设计者比较有效降低动态功耗的设计方法。

多电压设计的芯片划分成几个区域,不同的区域器件工作电压不同,这些不同工作电压的区域被称之为Voltageisland。

低工作电压区域工作频率较低,但可以有效降低区域内的动态功耗。

如下图所示:图十四:多电压工作区域所谓的电压区域其实就是一个物理的区域面积,将需要相同供电电压的单元器件集中在这个区域里面进行电源管理。

Synopsys通过单元器件的操作环境作为划分电源区域的一个依据。

操作环境(operatingcondition)操作环境指的是标准单元的工艺、工作电压、温度情况(PVT:process,operatingvoltage,temperature),是一个逻辑概念,在做时序分析对用来计算一个标准单元的时间延迟,和一个标准单元的物理性质(大小)没有关系。

隔离的单元器件(Mv-lso):在一些芯片设计中,所有的器件供电电压是~样的,但一些模块在某些时候可以被关闭供电电源。

这时被关闭的模块的输入输出信号需要被隔离保存,这些信号的隔离是通过MV—ISO来实现的。

所有的器件工作电压一致,但静态时序分析不会考虑穿过关闭的模块边界的路径。

电压转换器件levelshifter(肌Ls):在一些芯片设计中,具有不同的功能的模块工作要求不同,他们不会在芯片工作模式中被关闭电源供应,但可以根据工作频率的不同而采用不同的工作电压。

在不同的功能模块之间需要传递信号,信号的传递是通过电压转换器件来实现的。

在静态时序分析中,穿过不同工作电压区域的路径需要被分析,电压转换器件的模型定义了多种工作环境,它的器件延时会被计算在内,位于不同工作区域内的路径采用不同的工作条件。

带有使能端的电压转换器件:enablelevelshifter(M卜ELS):这种类型的器件可以在不同的电压区域间传递信号,又由于使能信号的控制可以隔离信号。

这种器件用于存在多个工作电压区域,同一模块又有多种工作模式的芯片中。

利用levelshifter在不同的电压区域间传递信号:图十六:电压转换器件在多电压区域的应用图十七:多电压区域放置效果图4)运用JupiterXT对不同的电压区域设置电源网络:图十八:基于多电压区域得到的电源网络模拟图5)根据用户设定的约束条件,最后得到的电源网络图如下图十九:基于电压区域的电源网络图在芯片规划阶段,应用JupiterXT规划Plangroup来做不同电压区域的模型,并进行电源线的布置和分析,并对电压区域进行调整。

具体流程包括Plangroup的创建,放置器件的Row的调整编辑,器件虚拟布局,然后是Voltagearea的确立和电源线的规划分析。

如果采用ICC进行blocklevel的设计对系统进行flatten流程设计时,可以采用下面的流程:MVFlowinICC图二十:多供电电压技术在synopsys中的流程图采用ICe进行Levelshifter的插入。

需要采用多个具有相同器件名称的NLDM模型的参考库进行优化,在优化使工具会针模块工作环境的设置从相应的库中选择器件.用于电压区创建的指令有:create_voltagearea;report_voltage_area;remove_voltagearea创建电压区周围的Guardband和movebound的指令有:createvoltage_area—。

guard_bandx‘’guard_band_ycreate_bound—coord{..·.)<cell—list>图二十一:常规方法构件的电源网络很难得到好的IRDrop=124mv运用JupiterXT的自动综合来构建一个电源网络:根据用户设置的约束条件,在几乎相同的布线资源下用JupiterXY综合命令自动得到的电源网络几乎一次就能满足用户电压降的要求:图二十二:自动综合所得到电源网络:IRDrop=68mv3lPNA&PNS在当前的JupiterXT版本可以提供的应用包括:1.支持规则或者不规贝|j形状的供电网络;2.支持基于功能模块的电网构建;3.支持基于电压区域的电网构建;4.支持对已存在电网的改造;5.支持PowerCompiler和PrimePower提供的功耗分配文件;4.3.1多金属层的电网综合:在多金属层的电网综合应用中,金属层一般采用从低到高的顺序进行综合。