计算机组成原理课程设计报告

计算机组成原理实验报告

计算机组成原理实验报告实验目的,通过本次实验,深入了解计算机组成原理的相关知识,掌握计算机硬件的基本组成和工作原理。

实验一,逻辑门电路实验。

在本次实验中,我们学习了逻辑门电路的基本原理和实现方法。

逻辑门电路是计算机中最基本的组成部分,通过逻辑门电路可以实现各种逻辑运算,如与门、或门、非门等。

在实验中,我们通过搭建逻辑门电路并进行实际操作,深入理解了逻辑门的工作原理和逻辑运算的实现过程。

实验二,寄存器和计数器实验。

在本次实验中,我们学习了寄存器和计数器的原理和应用。

寄存器是计算机中用于存储数据的重要部件,而计数器则用于实现计数功能。

通过实验操作,我们深入了解了寄存器和计数器的内部结构和工作原理,掌握了它们在计算机中的应用方法。

实验三,存储器实验。

在实验三中,我们学习了存储器的原理和分类,了解了不同类型的存储器在计算机中的作用和应用。

通过实验操作,我们进一步加深了对存储器的认识,掌握了存储器的读写操作和数据传输原理。

实验四,指令系统实验。

在本次实验中,我们学习了计算机的指令系统,了解了指令的格式和执行过程。

通过实验操作,我们掌握了指令的编写和执行方法,加深了对指令系统的理解和应用。

实验五,CPU实验。

在实验五中,我们深入了解了计算机的中央处理器(CPU)的工作原理和结构。

通过实验操作,我们学习了CPU的各个部件的功能和相互之间的协作关系,掌握了CPU的工作过程和运行原理。

实验六,总线实验。

在本次实验中,我们学习了计算机的总线结构和工作原理。

通过实验操作,我们了解了总线的分类和各种总线的功能,掌握了总线的数据传输方式和时序控制方法。

结论:通过本次实验,我们深入了解了计算机组成原理的相关知识,掌握了计算机硬件的基本组成和工作原理。

通过实验操作,我们加深了对逻辑门电路、寄存器、计数器、存储器、指令系统、CPU和总线的理解,为进一步学习和研究计算机组成原理奠定了坚实的基础。

希望通过不断的实践和学习,能够更深入地理解和应用计算机组成原理的知识。

课程设计报告(计算机组成原理)

课程设计(大作业)报告一、题目分析本次课程设计课题是设计基于微程序控制器的简单计算机设计与实现,宏观上利用CPU、cache、存储器以及一些外设设备来组成一台简单计算机,微观上由运算器、译码电路、和存储器指令用的控制存储器构成。

此次设计要求完成各个指令的格式以及编码的设计,实现各个机器指令的微代码。

本计算机实现的功能有:IN(输入),OUT(输出),ADD(加法),SUB(减法),STA(存数),JMP(跳转)。

设计进行开始,在了解微程序的基本格式, 及各个字段值的作用后, 按微指令格式参照指令流程图,设计出程序以及微程序,将每条微指令代码化,译成二进制代码表,并将二进制代码转换为联机操作时的十六进制格式文件。

根据机器指令系统要求,设计微程序流程图及确定微地址。

设计的加法和减法中, 被加数和被减数都由调试人员输入, 而加数和减数都从存储器中读取. 最后上机调试,各个功能运行结果正确。

二、基本理论计算机原理图(一)、ALU1、功能及组成它是数据加工处理部。

执行所有的算术运算执行所有的逻辑运算,并进行逻辑测试,通常,一个算术操作产生一个运算结果,而一个逻辑操作则产生一个判决。

2、设计图(二)、CPU1、如何执行指令(1)MOV指令a. 程序计数器PC中装入第一条指令地址101b. PC的内容被放到指令总线ABUS上,对指存进行译码,并启动读命令。

c. 从101号地址读出的MOV指令通过指令总线IBUS装入指令寄存器IR。

d. 程序计数器内容加1,变成102,为取下一条指令做好准备。

e. 指令寄存器中的操作码被译码。

f. CPU识别出是MOV指令。

至此,取值周期结束。

g. 操作控制(OC)器送出控制信号到通用寄存器,选择R1作源寄存器,选择R0作目标寄存器。

h. OC送出控制信号到ALU,制定ALU做传送操作。

i. OC送出控制信号,打开ALU输出三态门,将ALU输出送到数据总线DBUS 上。

(任何时候DBUS上只能有一个数据)j. OC送出控制信号,将DBUS上的数据打入到数据缓冲寄存器DR。

计算机组成原理课程设计报告

计算机组成原理课程设计实验报告目录一、程序设计 (1)1、程序设计目的 (1)2、程序设计基本原理 (1)二、课程设计任务及分析 (6)三、设计原理 (7)1、机器指令 (7)2、微程序流程图 (9)3、微指令代码 (10)4、课程设计实现步骤 (11)四、实验设计结果与分析 (15)五、实验设计小结 (15)六、参考文献 (15)一、程序设计1、程序设计目的(1)在掌握部件单元电路实验的基础上,进一步将其组成系统构造一台基本模型计算机。

(2使用简单模型机和复杂模型机的部分机器指令,并编写相应的微程序,具体上机调试掌握整机概念。

(3)掌握微程序控制器的组成原理。

(4)掌握微程序的编写、写入,观察微程序的运行。

(5)通过课程设计,使学生将掌握的计算机组成基本理论应用于实践中,在实际操作中加深对计算机各部件的组成和工作原理的理解,掌握微程序计算机中指令和微指令的编码方法,深入理解机器指令在计算机中的运行过程。

2、程序设计基本原理(1)实验模型机结构[1] 运算器单元(ALU UINT)运算器单元由以下部分构成:两片74LS181构成了并-串型8位ALU;两个8位寄存器DR1和DR2为暂存工作寄存器,保存参数或中间运算结果。

ALU的S0~S3为运算控制端,Cn为最低进位输入,M为状态控制端。

ALU的输出通过三态门74LS245连到数据总线上,由ALU-B控制该三态门。

[2] 寄存器堆单元(REG UNIT)该部分由3片8位寄存器R0、R1、R2组成,它们用来保存操作数用中间运算结构等。

三个寄存器的输入输出均以连入数据总线,由LDRi和RS-B根据机器指令进行选通。

[3] 指令寄存器单元(INS UNIT)指令寄存器单元中指令寄存器(IR)构成模型机时用它作为指令译码电路的输入,实现程序的跳转,由LDIR控制其选通。

[4] 时序电路单元(STATE UNIT)用于输出连续或单个方波信号,来控制机器的运行。

计算机组成原理课程设计报告书

计算机组成原理课程设计报告书计算机组成原理课程设计报告书目录一.实验计算机设计 1 1.整机逻辑框图设计1 2.指令系统的设计2 3.微操作控制部件的设计5 4.设计组装实验计算机接线表 13 5.编写调试程序 14 二.实验计算机的组装 14 三.实验计算机的调试 15 1.调试前准备 15 2.程序调试过程16 3.程序调试结果16 4.出错和故障分析16 四.心得体会17 五.参考文献 17 题目研制一台多累加器的计算机一实验计算机设计1.整机逻辑框图设计此模型机是由运算器,控制器,存储器,输入设备,输出设备五大部分组成。

1.运算器又是有299,74LS181完成控制信号功能的算逻部件,暂存器LDR1,LDR2,及三个通用寄存器R0,R1,R2等组成。

2.控制器由程序计数器PC、指令寄存器、地址寄存器、时序电路、控制存储器及相应的译码电路组成。

3.存储器RAM是通过CE和W/R两个微命令来完成数据和程序的的存放功能的。

4输入设备是由置数开关SW控制完成的。

5.输出设备有两位LED数码管和W/R控制完成的LR0 LR1 LR2 寄存器Ax Bx Cx R0-G R1-G R2-G 数据总线(D_BUS)ALU-G ALU M CN S3S2S1S0 暂存器LT1 暂存器LT2 LDR1 LDR2 移位寄存器 M S1 S0 G-299 输入设备 DIJ-G 微控器脉冲源及时序指令寄存器 LDIR 图中所有控制信号 LPC PC-G 程序计数器 LOAD LAR 地址寄存器存储器 6116 CE WE 输出设备 D-G W/R CPU 图 1 整机的逻辑框图图1-1中运算器ALU由U7--U10四片74LS181构成,暂存器1由U3、U4两片74LS273构成,暂存器2由U5、U6两片74LS273构成。

微控器部分控存由U13--U15三片2816构成。

除此之外,CPU的其他部分都由EP1K10集成。

计算机组成原理课程设计实验报告

计算机组成原理课程设计实验报告(1-3)山东大学计算机组成原理课程设计实验一------利用ispEXPERT SYSTEM软件设计四位全加器(一)实验环境:windows 98上的ispEXPERTSYSTEM(二)实验目的:熟悉ispEXPERTSYSTEM的初步使用(三)实验要求:用门电路设计一个一位二进制全加器。

二个加数为a,b,地位进位ci,向高位进位co.进而使用层次化设计思想设计一个四位全加器。

(四)实验步骤:4.1创建新项目4.1.1启动ISPEXPERTSYSTEM。

在windows下,选Lattice Semiconductor 项的ispEXPERTSYSTEM Project Navigator.4.1.2.建立新项目:选择菜单 File选择New Project键入项目名D:\EXP1\wuyupeng.syn4.1.3项目命名:用鼠标双击Untitled。

在 Title 文本框中输入“EXP1 Project”, 并选 OK。

4.2 选择器件:双击ispLSIispLSI5384V-125LB388,你会看到Choose Device 对话框 ( 如下图所示)在 Choose Device 窗口中选择 ispLSI1000 项按动器件目录中的滚动条,直到找到并选中器件 ispLSI 1032E-70LJ84揿 OK 按钮,选择这个器件(各种参数的设置)4.3设计输入:首先设计一个一位全加器,然后以这个器件作为本地器件来使用设计一个四位全加器4.3.1设计一个一位全加器:4.3.1.1原理图命名:选中Source下的NEW选项选中Schematic(确认按OK)输入文件名ADD.SCH进入原理图编辑窗口。

4.3.1.2 在图纸上添加器件:根据逻辑电路知识可知:s=a b ci; co=a*b+(a)*ci;接下来就是根据逻辑原理选择相信的器件来完成逻辑电路的设计,具体方法是:选择Add菜单下的Symbol)然后在各种库中选择所需要的器件4.3.1.3 添加连线:选择Add菜单下的wire项,进入画线状态,单击左键定义连线的左端,将光标移至线的另一端,在此单击左键即可定义这根线。

计算机组成原理课程设计总结报告[优秀范文5篇]

![计算机组成原理课程设计总结报告[优秀范文5篇]](https://img.taocdn.com/s3/m/13c78fe33086bceb19e8b8f67c1cfad6195fe966.png)

计算机组成原理课程设计总结报告[优秀范文5篇]第一篇:计算机组成原理课程设计总结报告大庆师范学院计算机组成原理课程设计总结报告设计题目:基本模型机的模拟设计与实现子题目:外部中断控制流水灯、蜂鸣器学生姓名:院别:专业:班级:学号:指导教师:2011 年 7 月 5日大庆师范学院课程设计任务书题目基本模型机的模拟设计与实现主要内容:对基本模型机的设计与实现,能够自己设计机器指令并且能够翻译为微程序,并能将机器指令和微程序分别打入模拟机的内存和控制存储其中,并通过程序调试能将所编写的程序正确运行。

参考资料:《计算机组成原理》唐朔飞著《计算机组成原理》白中英著《计算机组成原理实验指导》完成期限:一周指导教师签名:2011年 7 月5日大庆师范学院本科毕业论文(设计)大庆师范学院本科毕业论文(设计)目录一、设计目标 (1)二、采用设备 (1)三、设计的原理 (1)3.1 单片机..............................................................................1 3.2中断方式...........................................................................2 3.3实现控制LED 和蜂鸣器的原理 (3)四、逻辑电路图 (3)4.1LED小灯原理图..................................................................... 3 4.2扬声器原理图..................................................................... 3 4.3单片机的独立按键原理图 (4)五、程序代码...........................................................................4 5.1C语言的特点及选择...............................................................4 5.2 程序代 (5)六、调试情况 (5)6.1在keil环境下,编写外部中断的程序…………………………………6 6.2软件调试的步骤 (6)七、心得体会 (6)八、参考文献 (7)大庆师范学院本科毕业论文(设计)摘要:本文介绍了在89c51单片机系统中设计外部中断流水灯、蜂鸣器的一种方法。

计组实验报告(共10篇)

计组实验报告(共10篇)计组实验报告计算机组成原理实验报告一一、算术逻辑运算器1. 实验目的与要求:目的:①掌握算术逻辑运算器单元ALU(74LS181)的工作原理。

②掌握简单运算器的数据传输通道。

③验算由74LS181等组合逻辑电路组成的运输功能发生器运输功能。

④能够按给定数据,完成实验指定的算术/逻辑运算。

要求:完成实验接线和所有练习题操作。

实验前,要求做好实验预习,掌握运算器的数据传送通道和ALU 的特性,并熟悉本实验中所用的模拟开关的作用和使用方法。

实验过程中,要认真进行实验操作,仔细思考实验有关的内容,把自己想得不太明白的问题通过实验去理解清楚,争取得到最好的实验结果,达到预期的实验教学目的。

实验完成后,要求每个学生写出实验报告。

2. 实验方案:1.两片74LS181(每片4位)以并/串联形式构成字长为8为的运算器。

2.8为运算器的输出经过一个输入双向三态门(74LS245)与数据总线相连,运算器的两个数据输入端分别与两个8位寄存器(74LS273)DR1和DR2的输出端相连,DR1和DR2寄存器是用于保存参加运算的数据和运算的结果。

寄存器的输入端于数据总线相连。

3.8位数据D7~D0(在“INPUT DEVICE”中)用来产生参与运算的数据,并经过一个输出三态门(74LS245)与数据总线相连。

数据显示灯(BUS UNIT)已与数据总线相连,用来显示数据总线上所内容。

4.S3、S2、S1、S0是运算选择控制端,由它们决定运算器执行哪一种运算(16种算术运算或16种逻辑运算)。

5.M是算术/逻辑运算选择,M=0时,执行算术运算,M=1时,执行逻辑运算。

6.Cn是算术运算的进位控制端,Cn=0(低电平),表示有进位,运算时相当于在最低位上加进位1,Cn=1(高电平),表示无进位。

逻辑运算与进位无关。

7.ALU-B是输出三态门的控制端,控制运算器的运算结果是否送到数据总线BUS上。

低电平有效。

计算机组成原理实验报告1

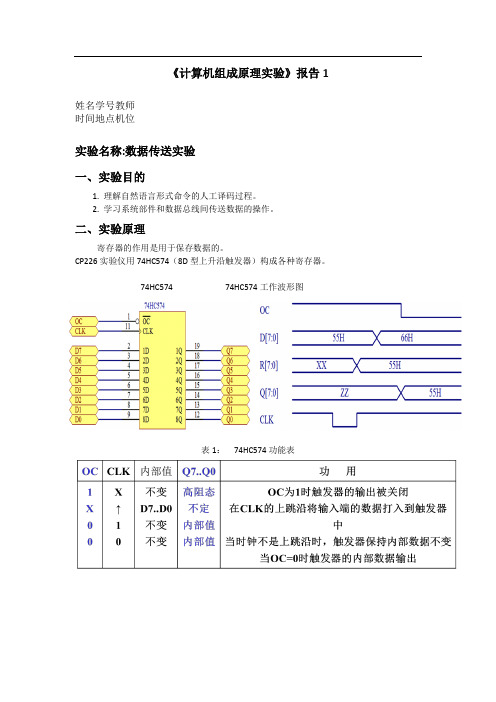

《计算机组成原理实验》报告1姓名学号教师时间地点机位实验名称:数据传送实验一、实验目的1. 理解自然语言形式命令的人工译码过程。

2. 学习系统部件和数据总线间传送数据的操作。

二、实验原理寄存器的作用是用于保存数据的。

CP226实验仪用74HC574(8D型上升沿触发器)构成各种寄存器。

74HC574 74HC574工作波形图表1:74HC574功能表寄存器A的原理图寄存器W的原理图寄存器组(R0-R3)的原理图三、实验内容1、将57H写入A寄存器。

2、将68H写入W寄存器。

3、将12H写入R0寄存器。

四、实验步骤1、将57H写入A寄存器。

①二进制开关K23-K16用于DBUS[7:0]的数据输入,置数据57H。

表2(电平为:低高低高低高高高)置控制信号为选通寄存器A,置K0(AEN)为0。

②关闭机箱电源,用导线把K0 和AEN连接。

③检查连线和电键位置,确信无误。

④开启机箱电源,按下RST键复位,再按小键盘TV/ME键3次显示屏进入Hand…手动状态。

按下小键盘STEP脉冲键,CK由高变低,观察现象;放开小键盘STEP键,CK脉冲由低变高,产生一个上升沿,数据57H打入选通的寄存器A,观察现象。

2、将68H写入W寄存器。

①二进制开关K23-K16用于DBUS[7:0]的数据输入,置数据68H。

置控制信号为选通寄存器W,置K1(WEN)为0,K0(AEN)为1。

②用导线把K1和WEN连接。

③检查连线和电键位置,确信无误。

④按下小键盘STEP脉冲键,CK由高变低,观察现象;放开小键盘STEP键,CK脉冲由低变高,产生一个上升沿,数据68H打入选通的寄存器W,观察现象。

3、将12H写入R0寄存器。

①二进制开关K23-K16用于DBUS[7:0]的数据输入,置数据12H。

置控制信号为选通寄存器R0。

置K1(WEN)为1,K0(AEN)为1。

②用不同颜色的导线把K5和RRD连接,K4和RWR连接,K3和SB连接,K2和SA连接。

计算机组成原理课程设计报告

计算机组成原理课程设计报告姓名:班级:学号:指导老师:赵孟德二〇一一年5 月31 日目录第一章实训任务概述 ------------------------------------------------------------------------------------------------ 11.1实训目的 ------------------------------------------------------------------------------------------------------ 11.2 实训任务------------------------------------------------------------------------------------------------------ 1 第二章题目结果------------------------------------------------------------------------------------------------------- 32.1 指令的执行流程 -------------------------------------------------------------------------------------------- 32.11“异或”指令 ----------------------------------------------------------------------------------------- 32.12 读取指令 --------------------------------------------------------------------------------------------- 32.2 储存器--------------------------------------------------------------------------------------------------------- 32.3 运算器--------------------------------------------------------------------------------------------------------- 42.4 硬件系统------------------------------------------------------------------------------------------------------ 42.5 运算器的组成及设计 -------------------------------------------------------------------------------------- 6 第三章图表格式------------------------------------------------------------------------------------------------------- 73.1 “异或”指令 ----------------------------------------------------------------------------------------------- 73.2 读取指令------------------------------------------------------------------------------------------------------ 73.3 “OUT”指令 ----------------------------------------------------------------------------------------------- 83.4 储存器--------------------------------------------------------------------------------------------------------- 83.5 设计计算机运算器 ----------------------------------------------------------------------------------------- 93.6 运算器的组成及设计 -------------------------------------------------------------------------------------11 第四章个人总结 --------------------------------------------------------------------------------------------------- 124.1 主要结论---------------------------------------------------------------------------------------------------- 124.2 对实训的认识 --------------------------------------------------------------------------------------------- 12 参考文献 --------------------------------------------------------------------------------------------------------------- 14 致谢 ----------------------------------------------------------------------------------------------------------------- 15第一章实训任务概述1.1实训目的通过本周的实训,使我们对计算机组成与体系结构这门课有一个更深入的了解。

计算机组成原理实验报告精品9篇

计算机组成原理实验报告课程名称计算机组成原理实验学院计算机专业班级学号学生姓名指导教师20年月日实验一:基础汇编语言程序设计实验1实验目的●学习和了解TEC-XP+教学实验监控命令的用法;●学习和了解TEC-XP+教学实验系统的指令系统;●学习简单的TEC-XP+教学实验系统汇编程序设计。

2实验设备及器材●工作良好的PC机;●TEC-XP+教学实验系统和仿真终端软件PCEC。

3实验说明和原理实验原理在于汇编语言能够直接控制底层硬件的状态,通过简单的汇编指令查看、显示、修改寄存器、存储器等硬件内容。

实验箱正如一集成的开发板,而我们正是通过基础的汇编语言对开发板进行使用和学习,过程中我们不仅需要运用汇编语言的知识,还需要结合数字逻辑中所学的关于存储器、触发器等基本器件的原理,通过串口通讯,实现程序的烧录,实验箱与PC端的通讯。

4实验内容1)学习联机使用TEC-XP+教学实验系统和仿真终端软件PCEC;2)学习使用WINDOWS界面的串口通讯软件;3)使用监控程序的R命令显示/修改寄存器内容、D命令显示存储内容、E命令修改存储内容;4)使用A命令写一小段汇编程序,U命令反汇编输入的程序,用G命令连续运行该程序,用T、P命令单步运行并观察程序单步执行情况。

5实验步骤1)准备一台串口工作良好的PC机器;2)将TEC-XP+放在实验台上,打开实验箱的盖子,确定电源处于断开状态;3)将黑色的电源线一段接220V交流电源,另一端插在TEC-XP+实验箱的电源插座里;4)取出通讯线,将通讯线的9芯插头接在TEC-XP+实验箱上的串口"COM1"或"COM2"上,另一端接到PC机的串口上;5)将TEC-XP+实验系统左下方的六个黑色的控制机器运行状态的开关置于正确的位置,再找个实验中开关应置为001100(连续、内存读指令、组合逻辑、联机、16位、MACH),6)控制开关的功能在开关上、下方有标识;开关拨向上方表示"1",拨向下方表示"0","X"表示任意,其他实验相同;7)打开电源,船型开关盒5V电源指示灯亮;8)在PC机上运行PCEC16.EXE文件,根据连接的PC机的串口设置所用PC机的串口为"1"或"2",其他的设置一般不用改动,直接回车即可; (8)按一下"RESET"按键,再按一下"START"按键,主机上显示:6实验截图及思考题【例3】计算1到10的累加和。

计算机组成原理实验

计算机组成原理实验计算机组成原理实验报告1. 引言计算机组成原理实验是计算机类专业学生进行的重要实践课程之一。

通过实验,学生可以深入了解计算机系统的各个组成部分以及它们的功能和工作原理。

2. 实验目的本次实验的主要目的是探究计算机中的主要组成部分,包括中央处理器(CPU)、内存、输入输出设备以及硬盘等,并了解它们的相互连接与调度方式。

3. 实验装置和材料本实验使用了一台计算机,配备有Intel Core i7处理器、8GB 内存和500GB硬盘。

实验中还使用了键盘、鼠标和显示器等输入输出设备。

4. 实验过程及结果4.1 CPU实验在这个实验中,我们通过编写汇编语言程序来实现简单的数值运算。

实验结果显示,CPU能够根据程序逐条执行指令,并正确计算出结果。

4.2 内存实验通过编写C语言程序,我们对内存进行读写操作。

实验结果显示,内存可以正确存储和读取数据,并且能够保持数据的一致性。

4.3 输入输出设备实验在这个实验中,我们测试了键盘和鼠标的输入功能以及显示器的输出功能。

实验结果显示,输入设备能够正确识别用户的输入,而输出设备能够正确显示结果。

4.4 硬盘实验通过读写文件的操作,我们测试了硬盘的存储和检索功能。

实验结果显示,硬盘能够正确存储和读取文件,并且能够在短时间内进行大量的数据传输。

5. 结论通过本次实验,我们深入了解了计算机系统的各个组成部分以及它们的功能和工作原理。

实验结果表明,计算机的各个组件能够正常工作,并且能够协同工作以完成复杂的任务。

6. 参考文献[1] 《计算机组成原理实验指导书》[2] Smith, J.E., & Jones, P. 《Computer Organization and Design: The Hardware/Software Interface》. Morgan Kaufmann, 2014.。

计组课程设计报告_图文

《计算机组成原理》课程设计报告年级专业班级:完成日期: 2015.12.51.引言1.1 实验目的1)在掌握传统的、顺序执行的CPU工作原理基础上,理解掌握流水CPU的工作原理;2)掌握流水线的设计思路和方法,尤其是对结构相关、数据相关和控制相关的解决思路;3)理解硬件设计流程,熟悉掌握指令系统的设计方法,并设计简单的指令系统;4)理解和掌握基于VHDL语言和TEC-CA硬件平台设计模型机的方法,并藉此掌握工程设计的思路和方法。

1.2 实验要求1)基本设计要求参考《16位5级流水无cache实验CPU课程设计实验要求》文档及其VHDL 代码,在理解其思想和方法的基础上,将其改造成8位的5级流水无cache的实验CPU,包括对指令系统、数据通路、各流水段模块、存储器模块等方面的改造。

利用VHDL语言编程实现,并在TEC-CA平台上进行仿真测试。

为方便起见,后续16位5级流水无cache实验CPU简记为ExpCPU-16,而8位的则记为ExpCPU-8。

对于存储器模块的改造,参考《计算机组成原理》课程综合实验的方法,独立设计一块8位的RAM。

要求测试减法的溢出标志位,如测试192-(-96)或者-192-96的溢出标志位。

2)额外设计要求时间允许的情况下,进行一些额外的、探索性的改造,可用于加分。

例如:(1)利用TEC-CA平台上的16位RAM来存放8位的指令和数据;(2)实现一条JRS指令,以便在符号标志位S=1时跳转。

需要改写ID段的控制信息,并改写IF段;(3)实现一条CMPJ DR,SR,offset指令,当比较的两个数相等时,跳转到目标地址PC+1+offset;(4)可以探索从外部输入指令,而不是初始化时将指令“写死”在RAM中;(5)此5段流水模块之间,并没有明显地加上流水寄存器,可以考虑在不同模块间加上流水寄存器;(6)探索5段流水带cache的CPU的设计。

1.3 实验设备本课程综合设计中,需要用到的实验设备如下:1)PC两台;2)TEC-CA硬件实验箱一个;3)Quartus II软件平台一个;4)DebugController软件一个;5)JTAG连接线。

计算机组成原理课程设计的实验报告

计算机组成原理课程设计的实验报告实验报告:计算机组成原理课程设计摘要:本实验报告旨在介绍计算机组成原理课程设计的实验过程和结果。

该实验旨在深入理解计算机的组成和工作原理,并通过设计和实现一个简单的计算机系统来加深对计算机组成原理的理解。

本实验报告将包括实验的目的、实验环境、实验步骤、实验结果以及实验的分析和讨论。

1. 实验目的:本实验的目的是通过设计和实现一个简单的计算机系统,加深对计算机组成原理的理解。

具体目标包括:- 理解计算机的基本组成和工作原理;- 掌握计算机硬件的设计和实现方法;- 学习使用计算机组成原理相关的软件工具。

2. 实验环境:本实验所需的硬件和软件环境如下:- 硬件环境:一台支持计算机组成原理课程设计的计算机;- 软件环境:计算机组成原理相关的软件工具,如Xilinx ISE、ModelSim等。

3. 实验步骤:本实验的步骤主要包括以下几个部分:3.1 系统需求分析在设计计算机系统之前,首先需要明确系统的需求和功能。

根据实验要求,我们需要设计一个简单的计算机系统,包括指令集、寄存器、运算单元等。

3.2 系统设计根据系统需求分析的结果,进行系统设计。

设计包括指令集的设计、寄存器的设计、运算单元的设计等。

3.3 系统实现在系统设计完成后,需要进行系统的实现。

具体步骤包括使用硬件描述语言(如VHDL)进行电路设计,使用Xilinx ISE进行逻辑综合和布局布线,最终生成bit文件。

3.4 系统测试在系统实现完成后,需要进行系统的测试。

测试包括功能测试和性能测试。

功能测试主要是验证系统是否按照设计要求正常工作;性能测试主要是测试系统的性能指标,如运行速度、吞吐量等。

4. 实验结果:经过实验,我们成功设计和实现了一个简单的计算机系统。

该系统具有以下特点:- 指令集:支持基本的算术运算和逻辑运算;- 寄存器:包括通用寄存器、程序计数器、指令寄存器等;- 运算单元:包括算术逻辑单元(ALU)和控制单元。

计算机组成原理课程设计3篇

计算机组成原理课程设计第一篇:CPU设计计算机中心处理器(Central Processing Unit, CPU)是计算机的心脏,它负责执行指令,完成计算和控制计算机的所有运算和数据传输。

在计算机组成原理课程设计中,设计一块CPU是非常重要的一步。

CPU的设计与制作需要有一定的基础和经验。

首先,需要了解CPU的工作原理和基本组成,包括寄存器、ALU、控制器和数据通路等。

其次,需要掌握数字逻辑、硬件描述语言和电子工艺制作等知识和技能,以实现CPU的具体功能。

设计一块CPU可分为以下几个步骤:1.确定CPU的整体架构和指令集。

根据需求和实际应用,确定CPU的整体架构和指令集。

可以参考现有的CPU设计,并根据实际情况进行优化和改进。

2.编写CPU的硬件描述语言代码。

使用硬件描述语言(如VHDL)编写CPU的硬件描述语言代码,包括寄存器、ALU、控制器和数据通路等。

3.使用仿真工具进行验证。

使用仿真工具模拟CPU的运行过程,验证硬件描述语言代码的正确性和功能实现。

4.设计和制作PCB电路板。

将CPU的硬件描述语言代码转换为PCB电路板设计,并制作出实际的电路板。

5.测试CPU的性能和功能。

对制作出的CPU进行测试,验证其性能和功能可靠性。

CPU的设计和制作是计算机组成原理课程设计中非常关键的一步,它直接影响到完成整个计算机系统的可靠性和性能。

因此,设计和制作一块优秀的CPU需要耐心和实践经验的积累。

第二篇:存储器设计存储器是计算机系统中重要的组成部分,用于存储数据和程序。

存储器需要具有读、写、删等常见操作,设计一块性能良好和容量适中的存储器是计算机组成原理课程设计的核心内容之一。

存储器的设计和制作需要掌握数字电路设计、电子工艺制作和人机交互等知识和技能。

下面是存储器设计的主要步骤:1.确定存储器的类型和容量。

根据实际需要和使用场景,确定存储器的类型和容量,包括SRAM、DRAM、FLASH等。

2.设计存储器的电路和控制线路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

计算机组成原理课程设计报告计算机组成原理课程设计报告班级:10计算机1005 班姓名:学号:20102769完成时间:2013年01月01日一、课程设计目的1.在实验机上设计实现机器指令及对应的微指令(微程序)并验证,从而进一步掌握微程序设计控制器的基本方法并了解指令系统与硬件结构的对应关系;2.通过控制器的微程序设计,综合理解计算机组成原理课程的核心知识并进一步建立整机系统的概念;3.培养综合实践及独立分析、解决问题的能力。

二、课程设计的任务针对COP2000实验仪,从详细了解该模型机的指令/微指令系统入手,以实现乘法和除法运算功能为应用目标,在COP2000的集成开发环境下,设计全新的指令系统并编写对应的微程序;之后编写实现乘法和除法的程序进行设计的验证。

三、课程设计使用的设备(环境)1.硬件●COP2000实验仪●PC机2.软件●COP2000仿真软件四、课程设计的具体内容(步骤)1.详细了解并掌握COP 2000模型机的微程序控制器原理,通过综合实验来实现1)该模型机指令系统的特点:COP2000模型机包括了一个标准CPU所具备所有部件,这些部件包括:运算器ALU、累加器A、工作寄存器W、左移门L、直通门D、右移门R、寄存器组R0-R3、程序计数器PC、地址寄存器MAR、堆栈寄存器ST、中断向量寄存器IA、输入端口IN、输出端口寄存器OUT、程序存储器EM、指令寄存器IR、微程序计数器uPC、微程序存储器uM,以及中断控制电路、跳转控制电路。

其中运算器和中断控制电路以及跳转控制电路用CPLD来实现,其它电路都是用离散的数字电路组成。

微程序控制部分也可以用组合逻辑控制来代替。

该模型机具有一套完善的指令系统,有算数运算指令,逻辑运算指令,赋值运算指令,转移指令,调子程序指令,中断指令,端口输入输出指令,外部设备输入输出指令。

该指令系统同时也具有完善的寻址方式,如累加器寻址,寄存器寻址,寄存器间接寻址,立即数寻址,存储器寻址等。

模型机的指令码为8位,根据指令类型的不同,可以有0到2个操作数。

指令码的最低两位用来选择R0-R3寄存器,在微程序控制方式中,用指令码做为微地址来寻址微程序存储器,找到执行该指令的微程序。

在本模型机中,一条指令最多分四个状态周期,一个状态周期为一个时钟脉冲,每个状态周期产生不同的控制逻辑,实现模型机的各种功能。

2)该模型机微指令系统的特点(包括其微指令格式的说明等):(1)模型机的寻址方式表一:模型机的寻址方式模型机的寻址方式寻址方式说明指令举例指令说明累加器操作数为CPL 将累加器A寻址累加器A A 的值取反隐含寻址累加器A OUT将累加器A的值输出到输出端口寄存器OUT寄存器寻址参与运算的数据在R0-R3的寄存器中ADDA,R0将寄存器R0的值加上累加器A的值,再存入累加器A中寄存器间接寻址参与运算的数据在存储器EM中,数据的地址在寄存器R0-R3中MOVA,@R1将寄存器R1的值作为地址,把存储器EM中该地址的内容送入累加器A中存储器直接寻址参与运算的数据在存储器EM中,数据的地址为指ANDA,40H将存储器EM中40H单元的数据与累加器A的值作逻辑与运令的操作数。

算,结果存入累加器A立即数寻址参与运算的数据为指令的操作数。

SUBA,#10H从累加器A中减去立即数10H,结果存入累加器A(2)模型机微指令系统有24位控制位以控制寄存器的输入、输出,选择运算器的运算功能,存储器的读写。

24位控制位分别介绍如下:XRD :外部设备读信号,当给出了外设的地址后,输出此信号,从指定外设读数据。

EMWR:程序存储器EM写信号。

EMRD:程序存储器EM读信号。

PCOE:将程序计数器PC的值送到地址总线ABUS上。

EMEN:将程序存储器EM与数据总线DBUS接通,由EMWR和EMRD决定是将DBUS数据写到EM中,还是从EM读出数据送到DBUS。

IREN:将程序存储器EM读出的数据打入指令寄存器IR和微指令计数器uPC。

EINT:中断返回时清除中断响应和中断请求标志,便于下次中断。

ELP: PC打入允许,与指令寄存器的IR3、IR2位结合,控制程序跳转。

MAREN:将数据总线DBUS上数据打入地址寄存器MAR。

MAROE:将地址寄存器MAR的值送到地址总线ABUS上。

OUTEN:将数据总线DBUS上数据送到输出端口寄存器OUT里。

STEN:将数据总线DBUS上数据存入堆栈寄存器ST中。

RRD:读寄存器组R0-R3,寄存器R?的选择由指令的最低两位决定。

RWR:写寄存器组R0-R3,寄存器R?的选择由指令的最低两位决定。

CN:决定运算器是否带进位移位,CN=1带进位,CN=0不带进位。

FEN:将标志位存入ALU内部的标志寄存器。

X2: X2、X1、X0三位组合来译码选择将数据送到DBUS上的寄存器。

表二:输入输出X2 X1X0输出寄存器0 0 0 IN_OE 外部输入门0 0 1 IA_OE 中断向量0 1 0 ST_OE 堆栈寄存器0 1 1 PC_OE PC寄存器1 0 0 D_OE 直通门1 0 1 R_OE 右移门1 1 0 L_OE 左移门WEN : 将数据总线DBUS 的值打入工作寄存器W 中。

AEN : 将数据总线DBUS 的值打入累加器A 中。

S2: S2、S1、S0三位组合决定ALU 做何种运算。

1 1 1 没有输出 表三:运算功能 S2 S1 S0功能0 0 A+W2。

计算机中实现乘法和除法的原理 (1)无符号乘法①实例演示(即,列4位乘法具体例子演算的算式): 被乘数:5乘数:40 加0 0 1A-W 减 0 1 0A|W 或 0 1 1A&W 与 1 0 0 A+W+C 带进位加 1 0 1 A-W-C 带进位减 1 1 0 ~A A 取反 1 1 1A 输出A01010000 0010100*②硬件原理框图:AL A WRR 被乘D L RR2(部判断乘数末位乘数被乘数③算法流程图:开被乘数—>R0 R1右(A )+(R0)A 清零 输出乘R3 R0左R3=C=1结Y N Y N(2)无符号除法①实例演示(即,列4位除法具体例子演算的算式):被除数:8 除数:30000000010010001101000011001001②硬件原理框图:AL A W R1R0 被除D L R标志除数R2R3(结初始化:③算法流程图:3.对应于以上算法如何分配使用COP2000实验仪中的硬件(初步分配,设计完成后再将准确的使用情况填写在此处)(1)无符号乘法符号乘法对应于COP2000实验仪的硬件具体分配使用情况如下表所示:表四:无符号乘法的硬件分配情况硬件名称实现算法功能描述寄存器R0 1)初始化时,用来存放被乘数;2)在程序执行的过程中,用来存放向左移位后的被乘数。

寄存器R1 1)初始化时,用来存放乘数;2)在程序执行的过程中,用来存放向右移位后的乘数。

寄存器计算时用来存放部分积和最后R2 的积累加器A 执行ADD A,R?(加法)、SHL R?(左移一位)、SHR (右移一位)等命令时所必须使用的寄存器。

寄存器W 执行ADD A,R?(加法)等双操作数命令及OR R?时所必须使用的寄存器。

左移门L 用来实现相应数据左移一位的运算,并能够控制该运算后的结果是否输出到数据总线。

直通门D 用来控制ALU的执行结果是否输出到数据总线。

右移门R 用来实现相应数据右移一位的运算,并能够控制该运算后的结果是否输出到数据总线。

程序计数器PC 1)控制程序按顺序正常执行;2)当执行转移指令时,从数据线接收要跳转的地址,使程序能够按需要自动执行。

3)当要从EM中读取数据时,由PC提供地址。

存储器EM存储指令和数据。

微程序计数器μPC 向微程序存储器μM提供相应微指令的地址。

微程序存储器μM存储相应指令的微指令。

输出寄存器OUT 将运算结果输出到输出寄存器OUT。

堆栈ST 当存储于累加器A的值将要受到破坏时,将其数据保存在堆栈ST中,使程序能够正常地执行。

(2)无符号除法无符号除法对应于COP2000实验仪的硬件具体分配使用情况如下表所示:表五:无符号除法的硬件分配情况硬件名称实现算法功能描述寄存器R0 初始化时,用来存放被除数和计算后的余数。

寄存器1)初始化时,用来存放除数;R1 2)在程序执行的过程中,用来存放向右移位后的除数。

寄存器R2 在程序执行过程中,用来保存当前算得的商。

寄存器R3 当结束标志使用,用来控制程序是否结束(R1右移一位值)。

累加器A执行ADD A,R?(加法)、SUB A,R?(减法)等命令时所必须使用的寄存器。

寄存器W 执行SUB A,R?(减法)等双操作数命令时所必须使用的寄存器。

左移门L 用来实现相应数据左移一位的运算,并能够控制该运算后的结果是否输出到数据总线。

直通门D 用来控制ALU的执行结果是否输出到数据总线。

右移门R 用来实现相应数据右移一位的运算,并能够控制该运算后的结果是否输出到数据总线。

程序计数器PC 1)控制程序按顺序正常执行;2)当执行转移指令时,从数据线接收要跳转的地址,使程序能够按需要自动执行。

3)当要从EM中读取数据时,由PC提供地址。

存储器EM存储指令和数据。

微程序计数器μPC 向微程序存储器μM提供相应微指令的地址。

微程序存储器μM存储相应指令的微指令。

堆栈ST 当存储于累加器A的值将要受到破坏时,将其数据保存在堆栈ST中,使程序能够正常地执行。

4.在COP2000集成开发环境下设计全新的指令/微指令系统设计结果如表所示:(1)新的指令集(设计两个不同指令集要分别列表)助记符机器码1 机器码2指令说明MOV A,#II 000000xx 04-07II 将立即数送入A中ADD A,R? 000001xx 08-0B寄存器A,R内容相加,结果送入A中JMP MM 000011xx 0C-0FMM无条件跳转JC MM 000100xx 10-13 MMC=1时,跳转JZ MM 000101xx 14-17 MMZ=1时,跳转OR A,#II 000110xx 18-1BII A中内容与立即数做或运算,结果给ACLP R? 000111xx 1C-1F将R中内容取反MOV R?,#II 001000xx 20-23II 将立即数送入寄存器RRL R? 001001xx 23-27 将寄存器R中内容左移RLC R? 001010xx 28-2B 将寄存器R中内容带进位左移RRC R? 001011xx 2C-2f 将寄存器R中内容带进位右移SUB R?,#II 001100xx 30-33II 从寄存器R中减去一个立即数OUT R? 001101xx 34-37 显示寄存器R的内容MOE MM,A 001110xx 38-3BMM将寄存器A的内容送入存储器ADW A,R? 001111xx 3C-3F寄存器W,R内容相加,结果送入W中SUB A,R? 010000xx 40-43从寄存器A中减去R中的内容ORW A,R? 010001xx 44-47W中内容与R中内容或运算,结果给WOUT A 010010xx 48-4B 显示寄存器A的内容MOV R?,A 010011xx 4C-4F将寄存器A的内容送入寄存器RMOV 010100x将寄存器R的内容A,R? x 50-53 送入寄存器ARR R? 010101xx 54-57 将寄存器R中内容右移MOV A,MM 010110xx 58-5BMM将存储器的内容送入寄存器ASUB A,#II 010111xx 5C-5FII 从寄存器A中减去一个立即数(2)新的微指令集5.用设计完成的新指令集编写实现无符号二进制乘法、除法功能的汇编语言程序(1)乘法:1)4位乘法的算法流程图:(见下页)2)汇编语言程序清单:MOV R0,#04H //被乘数MOV R1,#05H //乘数MOV R2,#00HMOV R3,#04H //计数器MOV A,#00H //A寄存器,记录最终结果OUT ALOOP: //总循环MOV R2,ARRC R1MOV A,R2JC CALJMP SHIFT//对被乘数,乘数进行处理CAL://乘积加上加数ADD A,R0SHIFT:MOV R2,ARL R0SUB R3,#01HMOV A,R2JZ OVERJMP LOOPOVER://结束处理OUT ASTOP:JMP STOP(2)除法(选作)1)4位除法的算法流程图:Y N N(A )+(R1)输出商(R2)R3 R3=C=1结YR1右R2左开被除数—>R0 (R0)R1左(A )—(R1)R2左移移R1右2)汇编语言程序清单:MOV R0,#08H//被除数MOV R1,#03H//除数MOV R2,#00H//商MOV A,R0SUB A,R1JC ERRORZERO//被除数小于除数时商为零MOV A,R1OR A,#00HJZ ERROR//除数为0时报错RL R1RL R1RL R1MOV R3,#04H//计数器MOV A,R0LOOP:SUB A,R1JC ZEROJMP NONOZERO://除数大于余数ADD A,R1MOE 01,ARL R2RR R1MOV A,01JMP TESTNONO: //除数小于余数MOE 01,AMOV A,#01HSUB A,#02HRLC R2RR R1MOV A,01TEST://循环测试OUT A//余数MOE 01,ASUB R3,#01HMOV A,01JZ OVERJMP LOOPOVER:OUT R2JMP STOP ERRORZERO://商为0 JMP STOPMOV A,R0OUT AMOV R2,#00HOUT R2ERROR://出错处理MOV R2,#-1HOUT R2STOP:JMP STOP6.上述程序的运行情况(跟踪结果)(1)乘法程序运行的过程汇编指令程序地址机器码指令说明微程序PCPC运行时寄存器或存储器的值MOVR0,#04 H 00 2004将被除数送入R0C7FBFFCBFFFF12221IR:20EM:04,R0:04MOVR1,#05 H 02 2105将除数送入R1 C7FBFFCBFFFF34221IR:21EM:05,R1:05MOVR2,#00 H 04 220将R2清零C7FBFFCBFFFF56221IR:22EM:00,R2:00MOV 06 230将R2清零C7FBFF 02IR:23R3,#04 H 4 CBFFFF 7821EM:04,R2:04MOV A,#00H 08 040将被除数送入AC7FFF7CBFFFF9A45IR:04EM:00,A:00OUT A 0A 48 FFDF9FCBFFFF 0BB4849IR:48D:00,OUT:00MOV R2,A 0B 4E FFFB9FCBFFFFCC4C4DIR:4ED:00,R2:00RRC R1 0C 2D FFF7F7FFFABFCBFFFF 0DDD2C2D2EIR:2DR1:01,A:05R:02,R1:02MOV 0D 52 FFF7F7 05IR:52A,R2 CBFFFF EE 051R2:00,A:00JC CAL 0E 1012 C6FFFFCBFFFFF12111IR:10EM:12ADD A,R0 12 08 FFF7EFFFFE90CBFFFF13131389AIR:08R0:04,W:04D:04,A:04MOV R2,A 13 4E FFFB9FCBFFFF14144C4DIR:4ED:04,R2:04RL R0 14 24 FFF7F7FFF8DFCBFFFF 1515124252IR:24R0:04,A:04L:08,R0:085 6SUBR3,#01 H 15 3301FFF7F7C7FFEFFFFA999CBFFFF161617173313233IR:33R3:04,A:04EM:01,W:01D:03,R3:03MOV A,R2 17 52 FFF7F7CBFFFF1818551IR:52R2:04,A:04JZ OVER 18 141C C6FFFFCBFFFF191A1415IR:14EM:1CJMP LOOP 1A 0C0BC6FFFFCBFFFF1BBCDIR:0CEM:0BMOV 0B 4E FFFB9F 04IR:4E0 C 4D04RRC R1 0C 2D FFF7F7FFFABFCBFFFF 0DDD2C2D2EIR:2DR1:02,A:02R:01,R1:01MOV A,R2 0D 52 FFF7F7CBFFFFEE551IR:52R2:04,A:04JC CAL 0E 1012 C6FFFFCBFFFFF1111IR:10EM:12JMP SHIFT 10 0C13C6FFFFCBFFFF1113CDIR:0CEM:13MOV 13 4E FFFB9F 14IR:4E1 4 4D04. . . .....................(2)除法程序运行的过程汇编指令程序地址机器码指令说明微程序PCPC运行时寄存器或存储器的值MOVR0,#08 H 00 2008将被除数送入R0C7FBFFCBFFFF12221IR:20EM:08,R0:08MOVR1,#03 H 02 2103将除数送入R1 C7FBFFCBFFFF34221IR:21EM:03,R1:03MOVR2,#00 H 04 220将R2清零C7FBFFCBFFFF56221IR:22EM:00,R2:00MOV A,R0 06 50 将被除数送入AFFF7F7CBFFFF77551IR:50R0:08,A:08SUB A,R1 07 41 用于比较除数,被除数大小FFF7EFFFFE91CBFFFF88844142IR:41R1:08,W:08D:05,A:05JC ERRORZ ERO 08 103B如果被除数小于除数则,直接得结果C6FFFFCBFFFF9A111IR:10EM:3BMOV A,R1 0A 51 将除数送入A FFF7F7CBFFFFBB551IR:51R1:03,A:03。