几种 DSP 与外接存储器的连接方法 摘要

TMS320C54xx DSP的USB接口实现

TMS320C54xx DSP的USB接口实现通用串行(Universal Serial Bus)应用由三部分组成:具有USB接口的PC系统、能够支持USB的系统软件和用法USB接口的设备。

USB应用采纳通用衔接技术,实现外设的容易迅速衔接,借以达到便利用户、降低成本、扩展PC机衔接外设范围的目的。

USB的特点如下:(1)衔接灵便、用法便利现在计算机系统衔接外围设备的接口并无统一的标准,如键盘用PS/2接口,打印机用25针的并行接口等。

USB则将这些不同的接口统一起来,由一组极小的矩型插座和软件构成。

用户插入外设后,计算机系统能够自动识别接入的外设,而不需要重新启动系统,用户可以带电插拔;为USB设计的驱动程序和应用软件可以自动启动,无需用户干预USB设备,也不涉及IRQ矛盾等问题;USB单独用法自己的保留中断,不会同其它设备争用PC机的有限资源。

(2)为外设提供电源 USB能自动识别外设所需的电源,并通过USB电缆向该设备供电(最高可达500mA)。

(3)速度快 USB的最高传输率可达12Mbit/s,比串口速度快100倍,比并口速度快近10倍。

USB端口的传输速率比目前PC机平台上的任何其它类型端口的传输速率都快。

预计今后USB的速度将会提高到100Mbit/s以上。

(4)支持多媒体 USB提供了对电话的两路数据支持,它可支持异步及等时数据传输,使电话可与PC机集成,分享语音邮件及其它功能。

因为USB音频信息生成于计算机外,因而削减了噪音干扰声音质量的机会,从而使音频系统具有更高的保真度。

1 USB接口芯片AN2131Q目前市场上USB接口芯片无数,用法较为广泛的是Crypress公司的AN2131系列的USB接口芯片AN2131Q。

AN2131Q具有以下优点:(1)基于RAM的"软"系统解决计划(SOFT,RAM BASED),不需要ROM或其它的固化存储器,而只用法片内的程序/数据RAM。

DSP(TMS320C6713)入门之旅五、I2C的理解和使用

一般DSP上面都集成了I2C模块,这样在连接外部器件时可以很方便的控制外部的器件。

I2C 基本上都是用于外部控制的,因为是是串行总线。

在我们的实验板上I2C总线连接到了两个从设备上面,一个是我们的eeprom,另一个是我们的音频芯片AIC23。

通过I2C协议我们写入和读取eeprom数据,控制AIC23的声音一些属性!简介一下I2C协议的规则:一. 技术性能:工作速率有100K和400K两种;支持多机通讯;支持多主控模块,但同一时刻只允许有一个主控;由数据线SDA和时钟SCL构成的串行总线;每个电路和模块都有唯一的地址;每个器件可以使用独立电源二. 基本工作原理:以启动信号START来掌管总线,以停止信号STOP来释放总线;每次通讯以START开始,以STOP结束;启动信号START后紧接着发送一个地址字节,其中7位为被控器件的地址码,一位为读/写控制位R/W,R/W位为0表示由主控向被控器件写数据,R/W为1表示由主控向被控器件读数据;当被控器件检测到收到的地址与自己的地址相同时,在第9个时钟期间反馈应答信号;每个数据字节在传送时都是高位(MSB)在前;写通讯过程:1. 主控在检测到总线空闲的状况下,首先发送一个START信号掌管总线;2. 发送一个地址字节(包括7位地址码和一位R/W);3. 当被控器件检测到主控发送的地址与自己的地址相同时发送一个应答信号(ACK);4. 主控收到ACK后开始发送第一个数据字节;5. 被控器收到数据字节后发送一个ACK表示继续传送数据,发送NACK表示传送数据结束;6. 主控发送完全部数据后,发送一个停止位STOP,结束整个通讯并且释放总线;读通讯过程:1. 主控在检测到总线空闲的状况下,首先发送一个START信号掌管总线;2. 发送一个地址字节(包括7位地址码和一位R/W);3. 当被控器件检测到主控发送的地址与自己的地址相同时发送一个应答信号(ACK);4. 主控收到ACK后释放数据总线,开始接收第一个数据字节;5. 主控收到数据后发送ACK表示继续传送数据,发送NACK表示传送数据结束;6. 主控发送完全部数据后,发送一个停止位STOP,结束整个通讯并且释放总线;DSP中IIC模块框图:1. 总线空闲状态SDA和SCL两条信号线都处于高电平,即总线上所有的器件都释放总线,两条信号线各自的上拉电阻把电平拉高;2. 启动信号START时钟信号SCL保持高电平,数据信号SDA的电平被拉低(即负跳变)。

如何设计TMS320C32DSP的存储器接口(精)

如何设计TMS320C32 DSP的存储器接口摘要通过对高性能浮点DSP处理器TMS320C32的外部存储器接口的研究,介绍其存储器结构的特点,并根据其特点给出3种设计方案。

这3种不同的方案,分别可以实现3种宽度的存储器接口,即8位、16位和32位的外部数据访问或是16位和32住的外部程序访问。

这一特点使得TMS320C32芯片非常适合于时变系统的控制与处理。

关键词 TMS320C32 浮点DSP处理器存储器接口存储器宽度TMS320C32是美国TI公司生产的一款浮点数字信号处理器(DSP),其CPU是在TMS320C30和TMS320C3l的基础上进行改进和简化来的,是C3X系列中的增强版。

增强的功能有:可变宽度的存储器接口,更快的指令周期,节电模式,可重定位的中断向量表,以及外部中断可由电平的边沿或电平触发等。

1 TMS320C32的外部存储器接口的特点TMS320C32是一个32位微处理器,它可通过24位地址总线、32位数据总线和选通信号对外部存储器进行访问。

其外部存储器接口结构如图l所示。

图l中,引脚PRGW是用来配置外部程序存储器宽度的。

当PRGW引脚为低电平时程序存储器宽度为16位;为高电平时程序存储器宽度为32位。

STRBO 和STRBl各为一组访问外部存储器的选通信号,各有4个信号引脚(STRBx_B3/A_1、STRBx_B2/A_2、STRBx_Bl和STRBx_B0)。

从图l中可以看出,选通信号STRB0和STRBl能从8/16/32位存储器中访问8/16/32位数据,或从16/32位存储器中执行32位程序;IOSTRB是外设I/O的选通信号引脚,它只能从32位宽度的存储器中访问32位的数据和程序。

可以通过对STRBx和IOSTRB的设置,从8/16/32位的存储器中访问8/16/32位数据或程序。

也就是说,可以从任何一个外部存储器中访同任何一种类型的数据。

这就说明可以通过设置IOSTRB、STRB0和STRB1的选通信号来寻址整个外部存储器空间。

DSP原理及应用TMS320C54x片内外设及应用实例

应用领域拓展

随着数字信号处理技术的不断发展,DSP的应用领 域也在不断拓展,需要不断探索新的应用场景和市 场需求。

人才培养和生态系统建设

为了推动DSP技术的发展和应用,需要加强 人才培养和生态系统建设,建立完善的开发 环境和工具链。

06

参考文献

参考文献

1

[1] 张雄伟, 杨吉斌. 数字信号处理——原理、算 法与实现[M]. 北京: 清华大学出版社, 2011.

应用场景

在音频处理、信号测量、控制系统 等领域广泛应用。

存储器和I/O引脚

存储器和I/O引脚功能

01

TMS320C54x芯片具有外部存储器和多个I/O引脚,用于扩展外

部存储空间和连接外设。

工作原理

02

通过读写外部存储器实现数据存储,I/O引脚用于输入输出电平

信号。

应用场景

03

在数据存储、外设控制、信号采集等方面具有广泛应用。

FFT在TMS320C54x上的实现

TMS320C54x的硬件结构支持FFT运算,其乘法器和累加器运算单元可以高效地完成 FFT计算。在实现FFT时,需要注意数据的位序和存储方式。

FFT应用实例

通过FFT算法,可以分析语音、图像、雷达等信号的频谱成分,从而实现信号的频域分 析、滤波、调制解调等功能。

TMS320C54x的优势与局限性

• 丰富的外设接口:TMS320C54x系列DSP具有多种外设接口, 如串行通信接口、并行输入输出接口等,方便与外部设备进行 数据交换。

TMS320C54x的优势与局限性

价格较高

由于TMS320C54x系列DSP采用高性能的制程技术和复杂的内 部结构,导致其价格较高,增加了应用成本。

DSP原理与应用---第3章 EMIF

DRAM是Dynamic RAM的缩写,中文含义为动态随机存取存储器, 需要不断的刷新,才能保存数据。而且是行列地址复用的,许多都有 页模式。SDRAM:Synchronous DRAM,即数据的读写需要时钟 来同步。 一个是静态的,一个是动态的,静态的是用的双稳态触发器来保存信 息,而动态的是用电子,要不时的刷新来保持。

DRAM容量大,SRAM容量小

SDRAM的结构

FLASH ROM

Flash-ROM(闪存)已经成为了目前最成功、流行的一种固态内存,与 EEPROM 相比具有读写速度快,而与 SRAM 相比具有非易失、以及价廉等优 势。而基于 NOR 和 NAND 结构的闪存是现在市场上两种主要的非易失闪存技 术。 Intel 于 1988 年首先开发出 NOR flash 技术,彻底改变了原先由 EPROM 和 EEPROM 一统天下的局面。紧接着,1989 年东芝公司发表了 NAND flash 技术(后将该技术无偿转让给韩国 Samsung 公司),强调降低每比特的成 本,更高的性能,并且象磁盘一样可以通过接口轻松升级。 NOR 的特点是芯片内执行(XIP,eXecute In Place),这样应用程序可以直 接在闪存内运行,不必再把代码读到系统 RAM 中。NOR 的传输效率很高,在 1~4MB 的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大影 响了它的性能。 NAND 结构能提供极高的单元密度,可以达到高存储密度,并且写入和擦除的 速度也很快,这也是为何所有的 U 盘都使用 NAND 闪存做为存储介质的原因。 应用 NAND 的困难在于需要特殊的系统接口。

NAND flash和NOR flash的对比

接口差别 NOR 闪存带有SRAM接口,有足够的地址引脚来寻址,可 以很容易地存取其内部的每一个字节。 NAND闪存使用复杂的I/O口来串行地存取资料,各个产品 或厂商的方法可能各不相同。8个引脚用来传送控制、地 址和资料信息。NAND读和写操作采用512字节的块,这 一点有点像硬盘管理此类操作,很自然地,基于NAND的 闪存就可以取代硬盘或其它块设备。

基于DSP串行外设接口的通信

文章编号:1006-1576(2003)05-0039-02基于DSP串行外设接口的通信徐朝阳,朱春光,孙海洋(国防科技大学机电工程与自动化学院,湖南长沙410073)摘要:基于DSP串行外设接口(SPI)的通信,以TMS320LF2407为主机,DAC7614为从机。

主从机数据均在SPICLK的一个边沿移出移位寄存器,在另一个边沿锁存到移位寄存器。

由系统软件决定主机对从机的检测,通过I/O口设置控制数据的发送。

以一路模拟电压输出设计为例,其DSP采用无延时下降沿时钟方式发送数据以配合DAC7614上升沿接收数据的时序,通过查询方式来控制数据的发送。

关键词:DSP控制器;串行外设接口;通信中图分类号:TP393.03 文献标识码:ACommunication of Serial Peripheral Interface Based on DSPXU Zhao-yang, ZHU Chun-guang, SUN Hai-yang(College of Electromechanical Engineering & Automation, National University of Defence Technology,Changsha 410073, China)Abstract: In the communication of serial peripheral interface (SPI) based on DSP, TMS320LF2407 is used as the host controller and DAC7614 used as the obedient controller. The data is sent out from the shift register on one edge of the SPICLK and received on another. How the host controller check up the obedient controller is decided with system software, and TXD controlled by setting I/O. Taking design of simulation voltage output as example, the data is sent out with the timing mode for the descend edge without delay to suit to suit the timing sequence for receiving data on ascend edge of DAC7614, sending and receiving data is controlled with inquiring mode in DSP.Key words: DSP Controller; Serial peripheral interface (SPI); Communication1 引言DSP的串行外设接口(SPI)是一个高速、同步串行输入/输出端口,允许长度可编程的串行位流(1~16位)以可编程的位传输速率从设备移入或移出。

06_DSP外围设备接口

;***************************************************************** ;** Function: AddaInit ;** Description: AD_DA initialization for TLC320AD50C ;***************************************************************** AddaInit: stm #0x0010, IMR st #0, *(serial_int_flag) ;clear the interrupt flag McBSP0_ENABLE AR3 ;enable McBSP rsbx INTM ;enabling interrupts Wait_1st_int: ld *(serial_int_flag), A nop nop bc Wait_1st_int, AEQ ;if no interrupt,wait st #0, *(serial_int_flag) ;clear the interrupt flag ;****************************************************************** ; Data Format in Secondary Communication ; D15 D14 D13 |D12 D11 D10 D9 D8| D7 D6 D5 D4 D3 D2 D1 D0 ; | | register | register ; R/W | address | data ;******************************************************************

TMS320C6201DSP处理器与FLASH存储器接口设计(精)

TMS320C6201 DSP处理器与FLASH存储器接口设计DSP是针对实时数字信号处理而设计的数字信号处理器,由于它具有计算速度快、体积小、功耗低的突出优点,非常适合应用于嵌入式实时系统。

自世界上第一片通用D5P芯片TMS320C10于1982年在美国T1公司产生以来,DSP处理器便显示出强盛的生命力。

短短二十多年,世界上许多公司便开发出各种规格的DSP处理器,并使它们在通信、自动控制、雷达、气象、导航、机器人等许多嵌入式实时领域得到了广泛应用。

20世纪90年代后期美国TI公司推出的面向通讯领域的新一代32位的T MS320C6000系列DSP芯片(简称C6000)是目前世界上最先进的DSP处理器,其中C62XX和C64XX为通用32位定点系列DSP处理器,C67XX为通用32位浮点系列DSP处理器,其指令速度分别高达960~4800MIPS和600MFLOPS~1GFLOPS,可与早期的巨型计算机速度相媲美,且单芯片功耗小于1.5W、采用BGA封装(小型球栅阵列)、体积也很小(最大35mm×35mm×3.5mm)。

因此,这些DSP处理器将在许多科技领域发挥重要作用。

FLASH存储器是新型的可电擦除的非易失性只读存储器,属于EEPROM器件,与其它的ROM器件相比,其存储容量大、体积小、功耗低,特别是其具有在系统可编程擦写而不需要编程器擦写的特点,使它迅速成为存储程序代码和重要数据的非易失性存储器,成为嵌入式系统必不可少的重要器件。

DSP与FLASH存储器的接口设计是嵌入式系统设计的一项重要技术,本文以基于三个C6201/C6701 DSP芯片开发成功的嵌入式并行图像处理实时系统为例,介绍这一设计技术。

1 C6201/C6701新一代DSP处理器1.1 C6201/C6701的特点及外部存储器接口EMIFC6201为通用32位定点DSP处理器,C6701为通用32位浮点DSP处理器,它们采用并行度很高的处理器结沟,从而具有许多突出的特点:DSP核采用改进的超长指令字(VLIW)体系结构和多流水线技术,具有8个可并行执行的功能单元,其中6个为ALU,两个为乘法器,并分成相同功能的两组,在没有指令相关情况下,最高可同时执行8条并行指令;·具有32个32位通用寄存器,并分成两组,每组16个,大大加快了计算速度;片上集成了大容量的高速程序存储器和数据存储措,最高可以200Mbit/s 的速度访问,并采用改进的多总线多存储体的哈佛结构。

DSP存储器及扩展接口详解

提示:初始化Flash寄存器的代码必须从RAM中运行,从 Flash中执行将导致不可预测的结果。

11

外设寄存器空间

F281X和C281X器件包含三个外设寄存器空间。这些空间分 为以下三组:

1) Peripheral Frame0: 直接映射到CPU的存储器总线,支持 16位和32位数据访问。 2) Peripheral Frame1: 映射到32位的外设总线,必须采用32 位读写方式(限对偶地址访问)。 3) Peripheral Frame2: 映射到16位的外设总线,仅支持16为 访问。

16

/* Peripheral Frame 2: SYSTEM : origin XINTRUPT : origin GPIOMUX : origin GPIODAT : origin EV_A : origin EV_B : origin MCBSP_A : origin SCI_A : origin SCI_B : origin SPI_A : origin ADC : origin

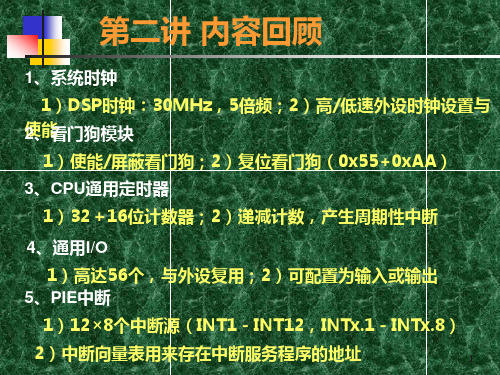

第二讲 内容回顾

1、系统时钟 1)DSP时钟:30MHz,5倍频;2)高/低速外设时钟设置与使能 2、看门狗模块 1)使能/屏蔽看门狗;2)复位看门狗(0x55+0xAA) 3、CPU通用定时器 1)32+16位计数器;2)递减计数,产生周期性中断 4、通用I/O 1)高达56个,与外设复用;2)可配置为输入或输出 5、PIE中断

EPROM FLASH EEPROM DiskOnChip

数据存储器:

SRAM

DRAM EEPROM Dual Port RAM

PC/104兼容的Flash Disk模块

3

F281X的存储器

第六章 TMS320C6000 DSP外部存储器接口讲解

*(unsigned int *)EMIF_SDRAMTIM = 0x00000350; /* SDRAM timing (refresh) 64ms,8192rows refresh, 7.8125us/row */

*(unsigned int *)EMIF_SDRAMEXT = 0x00018F5E;//0x0017DF3F; /* SDRAM Extension register */

*ptr = i; ptr++; } ptr=(Uint16 *)0x80000000; for(i=0;i<0x100;i++) { if(*ptr != i) {

result =0x01; return(result); } ptr++; } result=0x00; return(result); }

#define EMIF_GCTL 0x01800000 #define EMIF_CE1 0x01800004 #define EMIF_CE0 0x01800008 #define EMIF_CE2 0x01800010 #define EMIF_CE3 0x01800014 #define EMIF_SDRAMCTL 0x01800018 #define EMIF_SDRAMTIM 0x0180001C #define EMIF_SDRAMEXT 0x01800020 #define EMIF_CCFG 0x01840000 /*

课外资料查阅:SDRAM原理(作业)

6.2 EMIF 概述

DSPs访问片外存储器时必须通过外部存储器接 (External Memory Interface,EMIF)。C6000 系列 DSPs 的 EMIF 具有很强的接口能力,不仅 具有很高的数据吞吐率(最高达 1 200 MB/s), 而且可以与目前几乎所有类型的存储器直接接口。 存储器包括:

EEPROM与DSP的接口技术

EEPROM与 DSP的接口技术

王典洪 ,李东峰 ,刘 兵

(中国地质大学机械与电子工程学院 ,武汉 430074)

摘 要 : I2 C总线是一种用于 IC器件之间连接的二线制总线 。 I2 C增加了高速模式 ,其速度可 达 3. 4M bits/ s。它使得 I2 C 总线能够支持现有以及将来的高速串行传输应用 ,例如 EEPROM 和 Flash存储器 。而 AT24C02是美国爱特梅尔 (ATM EL )公司生产的最新串行 CMOS EEPROM 芯片 , 支持 I2 C总线协议 。数字信号处理器 (DSP)具有丰富的接口 ,将 DSP的多通道缓冲串行接口 (简称 MCBSP)配置成 GP IO (一般通用输入输出口 ) ,能够按照 I2 C协议进行工作 。

能改变 。通过 SCL 高电平期间数据的改变表示“开

始 ”或“停止 ”两种状态 :当 SCL 为高电平时 , SDA 由

高电平转向低电平时表示“开始 ”状态 ,由低电平转

向高电平表示“停止 ”状态 。其中“开始 ”状态必须

在其他操作之前执行 ,而“停止 ”状态则终止所有操

作 。同时 AT24C02与设备的信息交换还需要另外

transport now and in future, for examp le, EEPROM and Flash component. AT24C02 is p roduced by ATM EL. It is the newest serial CMOS EEPROM chip , and it supports I2 C m ain bus p rotocol. D igital Signal Process (DSP) has rich interface, we can configure MCBSP of DSP into GP IO , then it can work accord to I2 C p rotocol.

DSP第六章TMS320C2000系列DSP的典型外

1、时钟电路 2、复位和监控电路 3、外部RAM扩展 、外部RAM扩展 4、外部I/O扩展 、外部I/O扩展 5、DSP的片选电路设计 DSP的片选电路设计 6、DSP的仿真JTAG口设计 DSP的仿真JTAG口设计

2片8KX8RAM构建的8K片外数据存储器扩展例

32KX16 片外RAM扩展

局部数据存储器和全局数据存储器的扩展

4、外部I/O口扩展 、外部I/O口扩展

TMS320C20X支持64k16位字的I/O口地址范围, 对外部并行I/O端口的访问和对程序/数据存储器 的访问多路复用同样的地址和数据总线。并且/IS 管脚变为低电平将把I/O口访问和外部数据/程序 存储器的访问加以区别。

1、TMS320C20X系列时钟电路 TMS320C20X系列时钟电路 TMS320C20X系列DSP时钟发生器相关的硬 TMS320C20X系列DSP时钟发生器相关的硬 件引脚主要包括: (1)时钟方式设置输入:DIV1和DIV2 )时钟方式设置输入:DIV1和 (2)时钟输入端:CLKIN/X2 )时钟输入端:CLKIN/X2 (3)时钟输出端:X1 )时钟输出端:X1 (4)主时钟输出端:CLKOUT1 )主时钟输出端:CLKOUT1 (5)时钟锁相环PLL电源选择:PLL5V )时钟锁相环PLL电源选择:P的时间内没有 看门狗功能:若DSP在看门狗定义的时间内没有 输出,看门狗没有收到输入触发信号则说明应用 软件操作不正常(陷入死循环或掉入陷阱等), 此时监控复位电路应立即产生一个复位脉冲信号 将DSP复位; DSP复位; 备用电源切换和存储器写保护功能 当电源电压跌落到复位门限以下且低于后备电源 电压时,后备电源切换到被保护得SRAM和RTC, 电压时,后备电源切换到被保护得SRAM和RTC, 保证不丢失重要的数据,常用的后背电源有锂电 池和超级电容。

基于DSP的外部并行存储器接口设计

课程设计(论文)题目名称基于DSP的外部并行存储器接口设计课程名称专业课程设计II学生姓名段红飞学号0941301200系、专业信息工程系、通信工程指导教师李星亮2012年6月10日目录1存储器TMS320C54X的接口设计 (2)1.1外部RAM接口的设计 (2)1.2 Flash接口的设计 (2)2 系统硬件设计 (3)2.1方案选择 (3)2.2系统的开发平台与环境 (4)2.3元器件介绍 (4)2.4硬件核心设计图 (5)3系统软件设计 (6)3.1 软件流程图 (6)3.2 软件核心代码 (8)3.3程序运行后CPU寄存器和DSP存储器的数据 (12)4课程设计总结 (13)参考文献资料 (14)致谢 (15)1存储器TMS320C54X的接口设计1.1外部RAM接口的设计C54x系列DSP芯片外部RAM接口设计主要有以下三种扩展分离的方法:(1)外接一个128K*16的RAM,程序区和数据区分开它采用程序选通线(/PS)接外部RAM的A16地址线实现。

因此,程序区为RAM的钱64K,数据区为RAM的后64K。

(2)混合程序区和数据区当OVL Y=1时,内部RAM即使数据区又是程序区,这样设置的好处是程序可以在内部全速运行。

缺点是由于程序和数据是共用的,存储区就变小了,此外,在链接时必须将程序和数据分开,以避免重叠。

(3)一种优化的混合程序和数据区外接RAM方法这种方法省去了DSP的A15地址线,将RAM分为32K长度的块。

采用这种方法吗,可充分利用外接的RAM,不会因内部RAM和外部RAM的地址重叠而造成外部RAM的浪费。

这种优化的外部RAM配置方法,使得在使用DSP内部RAM的情况下能够充分利用外部扩展RAM。

1.2 Flash接口的设计(1) Flash的控制逻辑信号Flash有6根控制逻辑信号,如表2-1所示。

(2)控制信号Flash的工作状态是由命令控制的,有三个常用的命令,如表2-2所示。

DSP处理器与FLASH存储器的接口设计

DSP处理器与FLASH存储器的接口设计发布日期:2008-5-20 20:07:23文章来源:搜电浏览次数:110DSP是针对实时数字信号处理而设计的数字信号处理器,由于它具有计算速度快、体积小、功耗低的DSP/FLASH突出优点,非常适合应用于嵌入式实时系统。

自世界上第一片通用D5P芯片TMS320C10于1982年在美国T1公司产生以来,DSP处理器便显示出强盛的生命力。

短短DSP/FLASH二十多年,世界上许多公司便开发出各种规格的DSP处理器,并使它们在通信、自动控制、雷达、气象、导航、机器人等许多嵌入式实时领域得到了广泛应用。

20世纪90年代后期美国TI公司推出的面向通讯领域的新一代32位的TMS320C6000系列DSP芯片(简称C6000)是目前世界上最先进的DSP处理器,其中C62XX和C64XX 为通用32位定点系列DSP处理器,C67XX为通用32位浮点系列DSP处理器,其指令速度分别高达960~4800MIPS和600MFLOPS~1GFLOPS,可与早期的巨型计算机速度相媲美,且单芯片功耗小于1.5W、采用BGA封装(小型球栅阵列)、体积也很小(最大35mm×35mm×3.5mm)。

因此,这些DSP处理器将在许多科技领域发挥重要作用。

FLASH存储器是新型的可电擦除的非易失性只读存储器,属于EEPROM器件,与其它的ROM器件相比,其存储容量大、体积小、功耗低,特别是其具有在系统可编程擦写而不需要编程器擦写的特点,使它迅速成为存储程序代码和重要数据的非易失性存储器,成为嵌入式系统DSP/FLASH必不可少的重要器件。

DSP与FLASH存储器的接口设计是嵌入式系统设计的一项重要技术,本文以基于三个C6201/C6701 DSP芯片开发成功的嵌入式并行图像处理实时系统为例,介绍这一设计技术。

1、C6201/C6701新一代DSP处理器C6201/C6701的特点及外部存储器接口EMIFC6201为通用32位定点DSP处理器,C6701为通用32位浮点DSP处理器,它们采用并行度很高的处理器结沟,从而具有许多突出的特点:DSP核采用改进的超长指令字(VLIW)体系结构和多流水线技术,具有8个可并行执行的功能单元,其中6个为ALU,两个为乘法器,并分成相同功能的两组,在没有指令相关情况下,最高可同时执行8条并行指令;具有32个32位通用寄存器,并分成两组,每组16个,大大加快了计算速度;片上DSP/FLASH集成了大容量的高速程序存储器和数据存储措,最高可以200Mbit/s的速度访问,并采用改进的多总线多存储体的哈佛结构。

dsp与外扩展存储器的连接方法

几种DSP 与外接存储器的连接方法俞斌贾雅琼引言存储器接口分为ROM 接口和RAM 接口两种。

ROM 包括EPROM 和FLASH ,而RAM 主要是指SRAM 。

TMS320C5409 具有32K 字的片内RAM 和16K 字的掩膜ROM 。

但是在DSP 应用的很多场合,尤其是带信号存储的DSP 应用来说,TMS320C5409 的片内存储资源是远远不够用的。

因此,设计一个TMS320C5409 硬件系统一般应该包括其与EPROM/FLASH 和SRAM 的接口设计,以存放程序和数据。

本文介绍TMS320C5409 与存储器的接口设计方案。

2 DSP 与SRAM 的接口设计除了内部32k 字RAM 和16K 字ROM 之外,TMS320C5409 还可以扩展外部存储器。

其中数据总空间总共为64k字(0000H ~FFFFH ),I/O 空间为64K 字(0000H ~FFFFH ),程序空间为8M。

8M的程序空间的寻址是通过额外的7根地址线(A16~A22)实现的,由XPC寄存器控制。

根据程序和数据的空间配置,扩展的方法主要有3 种。

2.1 分开的程序和数据空间配置这种方案是采用外接一个128k×16位的RAM ,将程序区和数据区分开,如图1所示。

采用程序选通线接外部RAM 的A16 地址线实现,因此,程序区为RAM 的前64k 字(0000H~FFFFH ),数据区为RAM 的后64k 字(10000H ~1FFFFH )。

对DSP而言,程序区和数据区的地址范围均为0000H~FFFFH。

采用这种配置方法需要注意:如果内部RAM 设置为有效,则相同地址的外部RAM 自动无效;当外部RAM 不能全速运行时,需要根据速度设置插入等待状态(设置SWWSR )。

2.2 混合的程序和数据空间配置这种方案是令OVLY=1 ,此时内部RAM 既是数据区也是程序区。

这样设置的优点是程序可以在内部全速运行,缺点是由于程序和数据是共用的,因此存储区就变小了。

TMS320C54X系列DSP扩展外部Flash存储器的方法及应用

T M S 320C 54X 系列D SP 扩展外部Flash 存储器的方法及应用Technology of Extend i ng Externa l Fla sh M em ory ofT M S 320C 54X D SP and Appl ica tion温 静(北方自动控制技术研究所 太原 030006)【摘 要】 介绍了TM S 320C 54X 内部存储器的组织和扩展外部F lash 存储器的方法。

结合TM S 320C 54X 系列D SP 的上电系统自动引导功能,介绍了利用该技术将用户程序代码烧写到F lash 存储器中的方法。

【关键词】 闪速存储器,D SP ,系统编程,引导ABSTRACT T he o rganizati on of TM S 320C 54X internal m emo ry and app roach of extending external F lash m emo ry are intro 2duced .In com binati on of autom atic boo t loader functi on of pow er on system of TM S 320C 54X D SP ,th is paper p resents the tech 2niques that F lash m emo ry is used as a fir mw are .KEYWOR D S flash m emo ry ,D SP ,system p rogramm ing ,boo t loader 现在,数字信号处理器(D SP )正越来越多地应用到各种场合。

TM S 320C 54X 系列的D SP 的低功耗特性,使得它特别适合于便携式设备。

FLA SH 存储器具有功耗低、尺寸小且装配后可以编程的特性,也适合于便携式设备。

目前F lash 存储器正在从单纯的EPROM 的替换件演变为许多电路系统中的不可缺少的组成部分。

DSP外设端口

预定标模块包括TCR中的TDDR和PSC位,由CPU 时钟定时,每来一个CPU时钟,PSC值减1。

当PSC减至0、设备复位或定时器复位时, TDDR的内容复制到PSC中。

4位预定标计数器PSC和16位定时计数器TIM组成 一个20位计数器,定时器每接收一个CPU时钟减1,当 计数器减到0时,产生定时中断(TINT),同时PSC和 TIM重新装入预设的值。

’C54x的定时器

1.定时器结构

2.定时器工作原理 3.定时器的初始化

1.定时器结构

定时器主要由定时寄存器TIM、定时周期寄存 器PRD、定时控制寄存器TCR及相应的逻辑控制电路

组成。

寄存器TIM、PRD和TCR是存储器映像寄存器,

地址分别为0024H、0025H和0026H。

1 3

1 2 预定标分频系数 TDDR 预定标计数器 PSC

;不插等待时间 ;TSS=1关闭定时器 ;加载周期寄存器(PRD) ;装入定时器控制字,启动定时器 ;消除尚未处理完的定时器中断 ;开放定时器中断 ;开放中断

’C54x的串行口

多通道带缓冲串行口McBSP

’C54x的多通道缓冲串行口McBSP是在缓冲串 行口的基础上发展起来的。在外部通道选择电路的 控制下,采用分时方式实现多路缓冲串行通信。 McBSP串行口可以与其他’C54x器件、编程器 或其他串口器件通信。

0

1

1

0

1

1

主机可以读/写HPID寄存器。 HPIA寄存器不受影响

HDS1、HDS2:数据选通信号,与主机读选通和写 选通或数据选通线连接,用于在主机寻址HPI 周期内,控制HPI数据的传送。

HDS1和HDS2信号与HCS一道产生内部选通信号。 HINT: HPI中断输出信号,与主机中断输入相连。受 HPIC寄存器中的HINT位控制。

DSP之外部设备连接接口之HPI

通过主机借口HPI,外部主机可以直接访问DSP内部的双访问RAM(DARAM).HPI可以让外部的主处理器直接访问DSP内存映射中的部分内存,而无需DSP 干预。

通过主机接口还可以完成DSP的程序引导,DSP向主机发出中断信号要求主机响应中断等功能。

HPI提供了一个16位宽的并口,使用14位地址,每个地址装一个16位的字。

HPI不能直接访问其他的外设寄存器,如果主机需要从其他外设获取数据,则必须通过CPU或6个DMA通道中的一个,先将数据搬到DARAM 中,反之依然。

主机在HPI外部地址线上的地址,当成字地址,而不是字节地址来对待。

HPI的14根地址线,使主机可以访问到内部的地址为000060H~003FFFH的双访问RAM(DARAM)。

0~00005Fh为MMR保留,HPI不能访问。

在所有的C5509上,HPI和EMIF共享一个并口。

EBSR(外部总线选择寄存器)中的并行端口位决定这个端口用于数据EMIF模式(00b),完全 EMIF(01b),非复用HPI(10b)或者HPI模式(11b)。

并口模式位的复位值由复位时GPIO 0引脚的状态决定。

复位是GPIO 0引脚为高,是完全EMIF模式,低,复用HPI模式。

HPI信号简介信号名称类型说明HD[15:0]输入/输出/高阻主机数据总线在非复用模式下,只传输数据信号;复用模式下传输数据和地址信号HA[19:0]输入主机地址总线复用模式下传输主机到HPI口的地址信号;复用模式下HA[1]变成HCNTL1,HA[2]变为HAS_,其他引脚没有使用HBE[1:0]输入主机字节选择信号,但在TMS320VC5510的2.0版本之后不再支持该信号HCS_输入片选信号,低有效HR/W_输入读写信号HDS1_,HDS2_输入数据选通信号,HPI接口的数据选通信号是这两个信号的同或结果。

选通信号至少应持续2个CPU周期,HDS1_和HDS2_信号的连接根据主机选通信号而对应不同的接法。

DSP接口技术

DSP接口技术发布日期:2005-12-05作者:Jim Ryan 来源:电子产品世界随着数字信号处理(DSP)在各种应用中(从高级消费类产品到高规格军事系统)变得更加普遍,电子设备设计人员在DSP软件和硬件开发领域必须学习新的技能。

到DSP的接口变换器所有现代的定点和浮点DSP引擎都具有一个串行接口或并行存储器接口。

并行数据总线宽度等于DSP的内部字长,对于大多数的定点处理器其字长通常为16位。

然而,在某些DSP家庭中其字长为24位,在音频处理应用中需要采用这种特高的分辨率。

浮点处理的数据总线宽度为32位或更宽。

串行接口可全双工同步操作,而输入和输出数据以位方式串行格式进行操作。

每次传送的最大位数通常等于处理器的内部数据总线宽度,但通常可通过编程以适于接口各种不同的外设。

一般意义上,变换器可以认为是DSP处理器的"存储器寻址"外设。

可以读或写表示变换值的数据。

初看起来,选定变换器和DSP之间所采用的接口类型似乎很容易。

在DSP引擎中采用的变换器接口也有两种基本的接口类型--串行和并行。

实际上所有DSP 都提供串行接口。

用于嵌入应用的服务器件只提供串行接口,因为去掉成本高的外部数据和地址总线可使器件成本降低。

并行接口原来把变换器设想为接口,让它们配置在早期计算机的存储器地址图中。

结果,变换器表现为处理器的存储器地址图中一个地址或一系列地址,使得在一个周期内读(从ADC)或写(到ADC)所传送的变换数据。

传送是快速的,可以认为是简单存储器存取周期。

工作在100MIP和更高指令速率的高速DSP具有非常短的存储器存储周期时间。

为了成功地与一个变换器接口,往往需要对DSP进行编程,以便在变换器存取周期时间内插入等待状态。

在很多DSP中此特性是可编程的而且单独地为不同外部存储器地址区编程。

另一种技术是利用存储器认可信号,此信号告知处理器何时准备好供读或写的数据。

有些DSP为变换器和其他无存储器外设(如UART等)提供一个独立的外部地址区(或I/O空间)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

几种DSP与外接存储器的连接方法

摘要

存储器接口分为ROM接口和RAM接口两种。

ROM包括EPROM和FLASH,而RAM主要是指SRAM。

TMS320C5409具有32K字的片内RAM和16K字的掩膜ROM。

但是在DSP 应用的很多场合,尤其是带信号存储的DSP应用来说,TMS320C5409的片内存储资源是远远不够用的。

因此,设计一个TMS320C5409硬件系统一般应该包括其与EPROM/FLASH 和SRAM的接口设计,以存放程序和数据。

本文介绍TMS320C5409与存储器的接口设计方案。

关键词:DSP,存储器

1引言

存储器接口分为ROM接口和RAM接口两种。

ROM包括EPROM和FLASH,而RAM主要是指SRAM。

TMS320C5409具有32K字的片内RAM和16K字的掩膜ROM。

但是在DSP 应用的很多场合,尤其是带信号存储的DSP应用来说,TMS320C5409的片内存储资源是远远不够用的。

因此,设计一个TMS320C5409硬件系统一般应该包括其与EPROM/FLASH 和SRAM的接口设计,以存放程序和数据。

本文介绍TMS320C5409与存储器的接口设计方案。

2DSP与SRAM的接口设计

除了内部32k字RAM和16K字ROM之外,TMS320C5409还可以扩展外部存储器。

其中,数据总空间总共为64k字(0000H~FFFFH),I/O空间为64K字(0000H~FFFFH),程序空间为8M。

8M的程序空间的寻址是通过额外的7根地址线(A16~A22)实现的,由XPC寄存器控制。

根据程序和数据的空间配置,扩展的方法主要有3种。

2.1分开的程序和数据空间配置

这种方案是采用外接一个128k×16位的RAM,将程序区和数据区分开,如图1所示。

采用

程序选通线接外部RAM的A16地址线实现,因此,程序区为RAM的前64k字(0000H~FFFFH),数据区为RAM的后64k字(10000H~1FFFFH)。

对DSP而言,程序区和数据区的地址范围均为0000H~FFFFH。

采用这种配置方法需要注意:如果内部RAM设置为有效,则相同地址的外部RAM自动无效;当外部RAM不能全速运行时,需要根据速度设置插入等待状态(设置SWWSR)。

2.2 混合的程序和数据空间配置

这种方案是令OVLY=1,此时内部RAM既是数据区也是程序区。

这样设置的优点是程序可以在内部全速运行,缺点是由于程序和数据是共用的,因此存储区就变小了。

此外,在链接时必须将程序和数据分开,以避免重叠。

这种配置方法如图2所示。

将和信号接至一与非门,形成PDS信号,这个信号不论是有效还是有效都呈现有效(高电平),将这个信号经反向用作片选信号,就可以保证外部RAM既作为程序区也作为数据区。

图1 分开的数据和程序空间配置

图2 混合的数据和程序空间配置

2.2优化的混合程序和数据空间配置

图3所示为一种优化的混合程序和数据区外接RAM的方法。

这种配置方法省去了DSP的A15地址线,将RAM分成32k字长的块。

采用这种方法后,可充分利用外接的RAM,不会因内部RAM和外部RAM的地址重叠而造成外部RAM的浪费。

图3 优化的混合数据和程序空间配置

由于外部扩展的空间很大,因此DSP程序区另外的地址空间也能访问到外部RAM。

这种优化的外部RAM配置方法,使得在使用DSP的内部RAM的情况下,能够充分利用外部扩展RAM。

图4 DSP与FLASH的接口

3DSP与FLASH的接口设计

图4为DSP与FLASH的一种接口配置。

图中FLASH采用Silicon Storage 公司的新一代256K×16位CMOS FLASH Memory产品SST39VF400A作为DSP的外部数据存储器,地址总线和数据总线接至DSP的外部总线,接至DSP的。

DSP上的XF引脚用于启动编程。

当XF为低时,FLASH处于读状态;当XF为高时,FLASH可擦或编程。

为了满足

SST39VF400A的时序要求,XF与相“或”后接至,引脚与相“或”后接至。

4 FLASH的擦写

4.1 片外FLASH擦写原理

在实际应用中,选择的片外存储器通常是片外的RAM或FLASH Memory。

但是,由于RAM

中数据掉电即丢失,不适合长期保存数据,因此当需要保存到片外存储器的是一些无需频繁读/写但需要长期保存的数据时,如字模数据、端口地址等,通常选择使用片外的FLASH扩展DSP芯片的存储器空间。

但是,使用片外的FLASH必须要解决对其的擦写问题。

在实际应用中,对FLASH的擦写主要有两种方式:一是使用通用编程器对FLASH芯片进行擦写;二是直接由DSP对FLASH进行擦写。

这里介绍一种利用存储器映射技术,通过对DSP芯片编程实现片外FLASH擦写的方法。

CCS5000 IDE是TI公司专为TMS320C5409设计的开发平台,该平台具有简单明了的图形用户界面和丰富的软件开发工具。

利用GPIO0口可以生成合适的片外FLASH和片内RAM片选信号,从而实现片外FLASH

和片内RAM访问的切换,在电路上可以将GPIO0信号与数据选择信号或程序选择信号相“或”实现。

4.2 片外FLASH擦写流程

编写FLASH擦写程序的流程图如图5所示。

图5 FLASH擦写程序流程图

(1) 将character[180][32]设置为全局变量。

(2)将程序编译下载到DSP芯片中,打开工程目录中output文件夹中的.map文件,找到character数组在RAM中存放的起始地址和长度。

(3)使用Save Memory命令将RAM中对应于character数组的地址段的数据以二进制形式

保存在计算机上。

(4)打开FLASH擦写程序,修改数据在片内RAM中存储的起始地址和FLASH擦写的起始地址和数据长度,编译下载后,单步执行,直到擦写完FLASH,并将地址映射方式设置为映射到片内RAM处,数据便写到片外FLASH的相应地址中。

这一种通过地址映射方式的方法可适用于多种场合,针对多个FLASH芯片使用多个GPIO 端口进行地址的扩展,即可实现对其进行擦写操作;若将部分擦写程序放置到片外FLASH 中并作相应设置,即可实现系统得自举运行。

4Bootload的设计

BootLoader是嵌入式系统加电后在操作系统内核运行之前运行的第一段代码。

BootLoader 用于初始化硬件设备、建立内存空间的映射图,从而将系统的软硬件环境带到一个合适的状态,以便为最终调用操作系统内核准备好正确的环境。

通常,Boot Loader是严重地依赖于硬件而实现的,特别是在嵌入式世界。

因此,在嵌入式世界里建立一个通用的Boot Loader 几乎是不可能的。

BootLoader一般它只在系统启动时非常短的时间内运行。

对于嵌入式系统来说,这是至关重要的一步。

TMS320C54x内部具有16K×16位的掩模ROM,其内部具有Bootloader程序,工作在微计算机方式下可以启动ROM中的引导程序,将用户程序从EPROM(FLASH)、串行口、I/O 口或HPI口引导到内部RAM或外部的高速SRAM中全速运行。

TMS320C5409硬件复位后采样引脚如果为低,则DSP从FF80H开始执行片内的引导程序,FF80H包含一条跳转到Bootloader程序的语句,Bootloader程序将用户程序下载到RAM中运行。

在硬件复位期间,如果TMS320C5409的为高电平,则从片外的0FF80H开始执行程序。

选择过程如图6所示。

图6 自举加载方式的选择过程

5结束语

实践证明,在DSP的使用中,以上介绍的DSP与其外围存储器的接口设计是切实可行的。

/show.aspx?id=1768&cid=63。