EDA参考手册

集成电路设计EDA工具应用作业指导书

集成电路设计EDA工具应用作业指导书第1章 EDA工具概述 (5)1.1 EDA工具发展历程 (5)1.2 EDA工具在集成电路设计中的作用 (5)1.3 常用EDA工具简介 (6)第2章集成电路设计流程 (6)2.1 设计准备阶段 (6)2.1.1 需求分析 (6)2.1.2 技术选型 (6)2.1.3 设计规划 (6)2.1.4 电路架构设计 (6)2.2 设计实现阶段 (6)2.2.1 电路设计 (7)2.2.2 仿真验证 (7)2.2.3 布局布线 (7)2.2.4 版图设计 (7)2.3 设计验证阶段 (7)2.3.1 功能验证 (7)2.3.2 时序验证 (7)2.3.3 电源完整性分析 (7)2.3.4 热分析 (7)2.4 设计后处理阶段 (7)2.4.1 版图检查 (7)2.4.2 后仿真分析 (7)2.4.3 生产数据 (7)2.4.4 文档编写 (7)第3章数字集成电路设计 (7)3.1 数字电路设计基础 (8)3.1.1 数字逻辑元件 (8)3.1.2 组合逻辑电路设计 (8)3.1.3 硬件描述语言(HDL) (8)3.2 逻辑合成与优化 (8)3.2.1 逻辑合成 (8)3.2.2 逻辑优化 (8)3.2.3 EDA工具在逻辑合成与优化中的应用 (8)3.3 时序分析 (8)3.3.1 时序分析基础 (9)3.3.2 时序约束与优化 (9)3.3.3 EDA工具在时序分析中的应用 (9)3.4 电源网络设计 (9)3.4.1 电源网络设计基础 (9)3.4.2 电源网络设计方法 (9)3.4.3 EDA工具在电源网络设计中的应用 (9)第4章模拟集成电路设计 (9)4.1 模拟电路设计基础 (9)4.1.1 模拟电路概述 (9)4.1.2 模拟电路设计流程 (9)4.1.3 模拟电路设计方法 (9)4.2 模拟电路仿真 (9)4.2.1 仿真概述 (10)4.2.2 仿真工具与流程 (10)4.2.3 仿真参数设置与优化 (10)4.3 模拟电路布局与布线 (10)4.3.1 布局与布线概述 (10)4.3.2 布局设计 (10)4.3.3 布线设计 (10)4.4 模拟电路后处理 (10)4.4.1 后处理概述 (10)4.4.2 版图检查与修正 (10)4.4.3 后仿真与功能验证 (10)4.4.4 生产工艺与封装 (10)第5章混合信号集成电路设计 (10)5.1 混合信号电路设计基础 (10)5.1.1 混合信号电路概述 (11)5.1.2 混合信号电路设计流程 (11)5.1.3 混合信号电路关键功能指标 (11)5.2 混合信号电路仿真 (11)5.2.1 仿真方法 (11)5.2.2 仿真工具 (11)5.2.3 仿真步骤 (12)5.3 混合信号电路布局与布线 (12)5.3.1 布局与布线概述 (12)5.3.2 布局与布线原则 (12)5.3.3 布局与布线工具 (12)5.4 混合信号电路后处理 (12)5.4.1 后处理概述 (12)5.4.2 后处理流程 (12)5.4.3 后处理工具 (13)第6章射频集成电路设计 (13)6.1 射频电路设计基础 (13)6.1.1 射频信号特性 (13)6.1.2 射频电路元件 (13)6.1.3 射频电路拓扑 (13)6.2 射频电路仿真 (13)6.2.1 电路仿真原理 (13)6.2.2 仿真工具及参数设置 (13)6.2.3 仿真结果分析 (14)6.3 射频电路布局与布线 (14)6.3.1 布局原则 (14)6.3.2 布线技巧 (14)6.3.3 射频电路版图设计 (14)6.4 射频电路后处理 (14)6.4.1 参数提取 (14)6.4.2 功能评估 (14)6.4.3 优化策略 (14)第7章系统级集成电路设计 (14)7.1 系统级电路设计基础 (14)7.1.1 设计流程概述 (15)7.1.2 设计规范与要求 (15)7.1.3 顶层模块划分 (15)7.1.4 通信协议与接口设计 (15)7.2 系统级电路仿真 (15)7.2.1 仿真工具与流程 (15)7.2.2 仿真模型与参数设置 (15)7.2.3 功能仿真与功能仿真 (15)7.2.4 仿真结果分析 (15)7.3 系统级电路布局与布线 (15)7.3.1 布局布线概述 (15)7.3.2 布局布线策略与方法 (15)7.3.3 布局布线工具与流程 (16)7.3.4 布局布线优化与后处理 (16)7.4 系统级电路后处理 (16)7.4.1 后处理概述 (16)7.4.2 版图检查与修正 (16)7.4.3 参数提取与后仿真 (16)7.4.4 设计交付与生产 (16)第8章设计验证与测试 (16)8.1 功能验证 (16)8.1.1 验证目的 (16)8.1.2 验证方法 (16)8.1.3 验证步骤 (16)8.2 时序验证 (17)8.2.1 验证目的 (17)8.2.2 验证方法 (17)8.2.3 验证步骤 (17)8.3 功耗验证 (17)8.3.1 验证目的 (17)8.3.2 验证方法 (17)8.3.3 验证步骤 (17)8.4 DFT与测试 (18)8.4.1 DFT(Design for Testability)设计 (18)8.4.2 测试方法 (18)8.4.3 测试步骤 (18)第9章设计收敛与优化 (18)9.1 设计收敛策略 (18)9.1.1 确定设计目标 (18)9.1.2 分阶段收敛 (18)9.1.3 迭代优化 (18)9.1.4 设计收敛监控 (19)9.2 逻辑合成优化 (19)9.2.1 逻辑简化 (19)9.2.2 逻辑层次优化 (19)9.2.3 时序优化 (19)9.2.4 功耗优化 (19)9.3 布局与布线优化 (19)9.3.1 布局优化 (19)9.3.2 布线优化 (19)9.3.3 热点分析与优化 (19)9.4 电源网络优化 (19)9.4.1 电源规划 (19)9.4.2 电源网络分割 (19)9.4.3 电源网络优化算法 (20)9.4.4 电源噪声分析与控制 (20)第10章 EDA工具在特定领域应用 (20)10.1 EDA工具在嵌入式系统设计中的应用 (20)10.1.1 硬件描述语言(HDL)设计 (20)10.1.2 仿真验证 (20)10.1.3 逻辑综合 (20)10.1.4 布局布线 (20)10.2 EDA工具在人工智能芯片设计中的应用 (20)10.2.1 高层次综合 (21)10.2.2 基于FPGA的加速 (21)10.2.3 数据流优化 (21)10.3 EDA工具在物联网芯片设计中的应用 (21)10.3.1 低功耗设计 (21)10.3.2 射频设计 (21)10.3.3 系统集成 (21)10.4 EDA工具在汽车电子设计中的应用 (21)10.4.1 功能安全 (21)10.4.2 硬件在环仿真 (21)10.4.3 系统级设计 (22)第1章 EDA工具概述1.1 EDA工具发展历程电子设计自动化(Electronic Design Automation,EDA)工具起源于20世纪60年代,集成电路(Integrated Circuit,IC)技术的飞速发展,EDA工具逐渐成为集成电路设计领域不可或缺的辅助工具。

EDA实验手册

EDA 实验手册实验一3-8线译码器的设计一、实验目的同3-8线译码器的设计,让同学们掌握组合逻辑电路的设计方法,熟悉Quartu s Ⅱ设计硬件电路的基本流程。

二、实验步骤1、新建一个工程,注意工程名、文件名还有实体名要一致。

2、新建一个VHDL文件,输入设计程序并保存。

3、对新建的VHDL文件进行语法编译。

4、进行仿真(也可以跳过这一步)。

5、进行引脚分配,并进行总编译。

6、将程序下载到实验箱,在实验箱上连线进行实验。

三、参考程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity decoder3to8 isport(input:in std_logic_vector(2 downto 0);output:out bit_vector(7 downto 0));end decoder3to8;architecture behave of decoder3to8 isbeginoutput<="00000001" sll conv_integer(input);--用输入值来控制左移的位数end behave;四、实验要求1、仿真出3-8线译码器的实际波形。

2、根据实验结果画出3-8线译码器的真值表。

实验二十进制计数器的设计一、实验目的设计一个带使能输入、同步清零和同步加载功能的加1/减1计数器。

二、功能分析(1)同步清零端低电平有效,当其为低电平时,在下一个时钟上升沿来临时计数值清零,即清零功能与时钟同步。

(2)同步加载端低电平有效,当其为低电平时,在下一个时钟周期来临时将要加载的计数值读入计数器,然后将其置为高电平后,在读入的数的基础上加1或减1计数。

(3)使能输入端高电平有效,当其为高电平时正常计数,当其为低电平时停止计数。

(4)当计数方向控制端为高电平时加1计数,当其为低电平时减1计数。

EDA实验指导书全

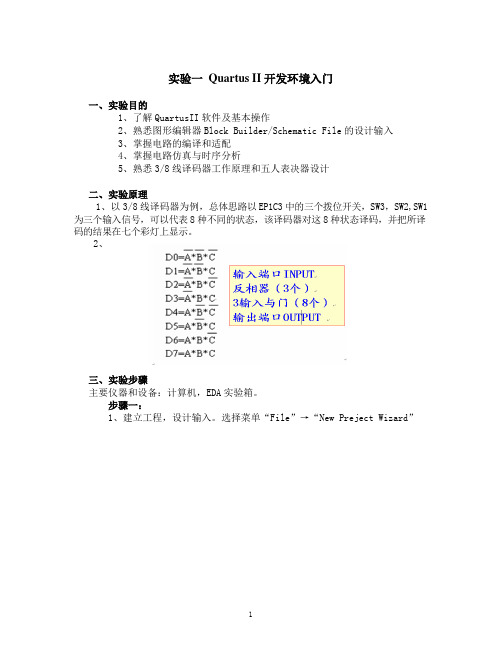

实验一Quartus II开发环境入门一、实验目的1、了解QuartusII软件及基本操作2、熟悉图形编辑器Block Builder/Schematic File的设计输入3、掌握电路的编译和适配4、掌握电路仿真与时序分析5、熟悉3/8线译码器工作原理和五人表决器设计二、实验原理1、以3/8线译码器为例,总体思路以EP1C3中的三个拨位开关,SW3,SW2,SW1为三个输入信号,可以代表8种不同的状态,该译码器对这8种状态译码,并把所译码的结果在七个彩灯上显示。

2、三、实验步骤主要仪器和设备:计算机,EDA实验箱。

步骤一:1、建立工程,设计输入。

选择菜单“File”→“New Preject Wizard”将设计文件加入工程中:点击下方的“Next” 按钮,在弹出的对话框中点击“File”栏的按钮,将此工程相关的所有VHDL文件加入进此工程(如果有的话)。

Cyclone系列的EP1C3T144C8按下“Next”后,出现仿真工具选择对话框。

不作任何选择。

4、完成设置点击“Next”后,完成工程的设定,点击“finish”。

步骤二:1、选择File/New或点击主菜单中的空白图标,进入新建程序文件状态,选择VHDL file 。

VHDL程序文件的扩展名是:* .vhd程序代码:-- A simple 3 to 8 decoderlibrary ieee;use ieee.std_logic_1164.all;entity decoder isport ( inp: in std_logic_vector(2 downto 0);outp: out std_logic_vector(7 downto 0)); end decoder;architecture behave of decoder isbeginoutp(0) <= '1' when inp = "000" else '0';outp(1) <= '1' when inp = "001" else '0';outp(2) <= '1' when inp = "010" else '0';outp(3) <= '1' when inp = "011" else '0';outp(4) <= '1' when inp = "100" else '0';outp(5) <= '1' when inp = "101" else '0';outp(6) <= '1' when inp = "110" else '0';outp(7) <= '1' when inp = "111" else '0';end behave;步骤三:1、选择菜单“File”→“New ” →“ Schematic File”,即弹出原理图编辑框。

EDA 实验指导书

EDA技术基础实验指导书海南大学信息学院编目录实验一MAX –plusII及开发系统使用 1 实验二高速四位乘法器设计7 实验三秒表的设计9 综合性设计性实验实验四序列检测器的设计12 实验五数字频率计的设计14 数字密码锁17 交通灯控制器182EDA实验指导书实验一MAX –plusII及开发系统使用一、实验目的1、熟悉利用MAX-plusⅡ的原理图输入方法设计简单的组合电路2、掌握层次化设计的方法3、熟悉DXT-BⅢ型EDA试验开发系统的使用二、主要实验设备PC 机一台(中档以上配置),DXT-B3 EDA实验系统一台。

三、实验原理数字系统设计系列实验是建立在数字电路基础上的一个更高层次的设计性实验。

它是借助可编程逻辑器件(PLD),采用在系统可编程技术(ISP),利用电子设计自动化软件(EDA),在计算机(PC)平台上进行的。

因为本实验是在计算机平台上进行,因此实验方式,实验手段和实验仪器与传统的实验有很大的区别,主要体现在以下几个方面:1、实验器材集中化,所有实验基本上在一套实验设备上进行。

传统的实验每作完一个实验,实验器材基本上都要变动(个别除外)。

而做本实验时,只要在计算机上把不同的程序输进去,其它步骤所有实验都一致;2、实验耗材极小(基本上没有耗材);3、在计算机上进行,自动化程度高,人机交互性好,修改、验证实验简单;4、下载后,实验结果清晰;5、实验仪器损耗少,维护简单;下面,我们就本套实验设备做一个简单的介绍。

3(一)Max+plusⅡ10.0的使用。

1、Max+PlusII软件的安装步骤:第一步:系统要求奔3CPU以上,128M内存以上,4G 以上硬盘,98 操作系统(98或Me操作系统才可以下载,其他操作系统下载必须安装驱动,否则只能仿真,如果大家只进行仿真的话,对系统没要求)第二步:安装点击安装可执行文件进行安装,安装完毕后会弹出一对话框,点击是或否都可以。

第三步:将安装文件夹中的License 文件夹打开,里面有一个License.bat 注册文件,将此文件复制到你的安装目录下(你的安装目录可放在任一个驱动器下,然后建立一个Max10的文件夹,将系统安装在此文件夹中,安装后此文件夹中会有三个文件夹)的任一个文件夹中,要清楚位置。

Cadence-使用参考手册

Cadence 使用参考手册邓海飞微电子学研究所设计室20XX7月目录概述11.1 Cadence概述11.2 ASIC设计流程1第一章Cadence 使用基础52.1 Cadence 软件的环境设置52.2 Cadence软件的启动方法102.3库文件的管理122.4文件格式的转化132.5 怎样使用在线帮助132.6 本手册的组成14第二章Verilog-XL 的介绍153. 1 环境设置153.2 Verilog-XL的启动153.3 Verilog-XL的界面173.4 Verilog-XL的使用示例183.5 Verilog-XL的有关帮助文件19第四章电路图设计与电路模拟214.1 电路图设计工具Composer (21)4.1.1 设置214.1.2 启动224.1.3 用户界面与使用方法224.1.4 使用示例244.1.5 相关在线帮助文档244.2 电路模拟工具Analog Artist (24)4.2.1 设置244.2.2 启动254.2.3 用户界面与使用方法254.2.5 相关在线帮助文档25第五章自动布局布线275.1 Cadence中的自动布局布线流程275.2 用AutoAbgen进行自动布局布线库设计28第六章版图设计与其验证306.1 版图设计大师Virtuoso Layout Editor (30)6.1.1 设置306.1.2 启动306.1.3 用户界面与使用方法316.1.4 使用示例316.1.5 相关在线帮助文档326.2 版图验证工具Dracula (32)6.2.1 Dracula使用介绍326.2.2 相关在线帮助文档33第七章skill语言程序设计347.1 skill语言概述347.2 skill语言的基本语法347.3 Skill语言的编程环境347.4面向工具的skill语言编程35附录1 技术文件与显示文件示例60附录2 Verilog-XL实例文件721.Test_memory.v (72)2.SRAM256X8.v (73)3.ram_sy1s_8052 (79)4.TSMC库文件84附录3 Dracula 命令文件359概述作为流行的EDA工具之一,Cadence一直以来都受到了广大EDA工程师的青睐。

立创eda操作手册(3篇)

第1篇目录1. 简介2. 系统安装与启动3. 界面介绍4. 基本操作5. 元件库管理6. 布局与布线7. 印制电路板设计8. 生成报表9. 设计文件输出10. 常见问题解答11. 总结1. 简介立创EDA是一款功能强大的电子设计自动化(EDA)软件,适用于电路设计、原理图绘制、PCB设计等领域。

本手册旨在帮助用户快速上手立创EDA,掌握其基本操作和设计流程。

2. 系统安装与启动2.1 系统要求- 操作系统:Windows 7/8/10- 处理器:Intel Core i3 或 AMD Athlon II 或更高- 内存:4GB RAM 或更高- 硬盘空间:1GB 或更高- 显卡:DirectX 9 或更高版本2.2 安装步骤1. 下载立创EDA安装包。

2. 双击安装包,按照提示完成安装。

3. 安装完成后,双击桌面上的立创EDA快捷方式启动软件。

3. 界面介绍立创EDA界面主要由以下部分组成:- 菜单栏:提供各种操作命令。

- 工具栏:提供常用的快捷工具。

- 设计区域:显示电路原理图或PCB布局。

- 元件库:提供各种元件供设计使用。

- 属性栏:显示当前选中元件或图形的属性。

4. 基本操作4.1 新建项目1. 点击“文件”菜单,选择“新建”。

2. 在弹出的对话框中,选择项目类型(原理图或PCB)。

3. 输入项目名称和保存路径,点击“确定”。

4.2 打开项目1. 点击“文件”菜单,选择“打开”。

2. 在弹出的对话框中,选择要打开的项目文件。

3. 点击“打开”按钮。

4.3 保存项目1. 点击“文件”菜单,选择“保存”或“另存为”。

2. 在弹出的对话框中,选择保存路径和文件名。

3. 点击“保存”按钮。

5. 元件库管理5.1 添加元件库1. 点击“元件”菜单,选择“添加元件库”。

2. 在弹出的对话框中,选择要添加的元件库。

3. 点击“确定”。

5.2 搜索元件1. 在元件库中,输入要搜索的元件名称。

2. 按下回车键或点击搜索按钮,搜索结果将显示在元件列表中。

EDA综合实验箱使用手册.

EDA综合实验箱使用说明手册一.系统概述1. 系统结构及说明系统结构如图1.1所示:图1.1 系统结构框图2. 硬件资源 1.1单片机资源◆完全兼容51内核的SST89E516RD,管脚兼容AT89C51,带仿真监控程序◆时钟频率:0~40MHz ◆集成1KBy片内RAM◆64Kbyte + 8Kbyte Flash EEPROM ◆看门狗◆可编程计数器阵列(PCA)◆SPI接口◆I2C接口1.2可编程逻辑器件资源(EP3C10E144)◆10,320逻辑单元(LE)◆46个M9K◆423,936bit RAM◆23个18*18硬件乘法器◆2个锁相环(PLL)◆10个全局时钟网络◆最大94个用户IO口◆最大22组差分接口1.3常用外围设备资源◆4*4矩阵按键◆8*1独立按键◆8个发光二极管◆8位7段数码管◆字符液晶1602◆点阵液晶12864(带字库)◆蜂鸣器◆8K串口存储器(仅单片机模式可用)◆10位高精度AD转化器(仅单片机模式可用)◆12位高精度DA转换器二.操作说明1. 人机交互模块功能说明该模块是本EDA实验箱的人机对话界面,主要实现对本EDA实验箱的模式选择、电压测量、信号输出、频率测量以及系统复位等功能。

其主要部件及功能如表2.1所示:2. 实验箱上电或复位当实验箱初次上电或者按Reset(复位)键,都将进入初始化界面,该界面将显示重庆邮电大学徽标以及实验平台的名称、制作者等信息,随后即自动进入功能选择界面。

如图2.1所示:图2.1 功能选择界面功能1:电压测量能够完成对实验箱上+5V、+3.3V两路电源电压以及外接直流电压(VT)的测量。

功能2:信号输出能够同时产生多路不同频率的方波信号,频率调节范围(1Hz~1MHz)。

功能3:频率测量可以测量外接频率(FT)。

功能4:模式选择实现不同工作模式间的切换。

目前本实验箱共设计有9种不同的工作模式(模式0~模式8),不同模式对应有不同的电路结构,各模式下的电路结构图可参见模式介绍。

EDA课程设计说明书正文

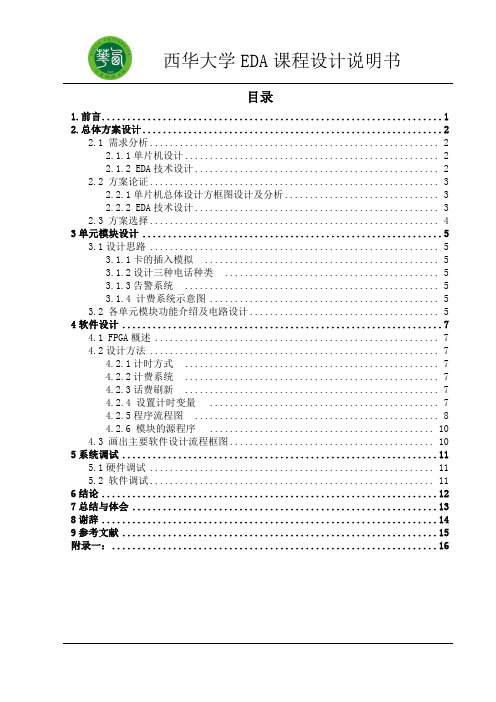

目录1.前言 (1)2.总体方案设计 (2)2.1 需求分析 (2)2.1.1单片机设计 (2)2.1.2 EDA技术设计 (2)2.2 方案论证 (3)2.2.1单片机总体设计方框图设计及分析 (3)2.2.2 EDA技术设计 (3)2.3 方案选择 (4)3单元模块设计 (5)3.1设计思路 (5)3.1.1卡的插入模拟 (5)3.1.2设计三种电话种类 (5)3.1.3告警系统 (5)3.1.4 计费系统示意图 (5)3.2 各单元模块功能介绍及电路设计 (5)4软件设计 (7)4.1 FPGA概述 (7)4.2设计方法 (7)4.2.1计时方式 (7)4.2.2计费系统 (7)4.2.3话费刷新 (7)4.2.4 设置计时变量 (7)4.2.5程序流程图 (8)4.2.6 模块的源程序 (10)4.3 画出主要软件设计流程框图 (10)5系统调试 (11)5.1硬件调试 (11)5.2 软件调试 (11)6结论 (12)7总结与体会 (13)8谢辞 (14)9参考文献 (15)附录一: (16)1.前言EDA使用户在无需实际芯片、电路板和仪器仪表的情况下进行电路设计和分析;采用在系统编程技术,在现场对系统进行逻辑重构和升级,实现硬件设计软件化。

EDA技术以可编程逻辑器件FPGA和CPLD及其开发系统为硬件平台,以EDA开发软件如Quartus Ⅱ为开发工具,基于逻辑功能模块的层次化设计方法设计数字系统。

Quartus Ⅱ设计可采用原理图、硬件描述语言(VHDL)等多种输入方式,并支持这些文件的任意混合设计。

对于不同层次,可采用不同的输入方式进行设计。

由于VHDL擅长描述模块的逻辑功能,所以在对底层模块设计中,常采用VHDL进行描述,而原理图则擅长描述模块间的连接关系,故在顶层设计中,常采用原理图输入方法。

模拟IC卡电话计费器通常以单片机为核心进行设计,本文以为它例介绍基于EDA技术的数字系统混合设计方法。

EDA 产品选择指南说明书

ED. 1 | 08.2019

Catalog E 074691

Product Selector Guide WIRE-TO-BOARD & I/O INTERCONNECT SOLUTIONS

MicroCon MicroBridge MiniBridge | MiniBridge Koshiri

12 - 80

2, 3, 4, 2, 3, 4, 5,

5, 6, 8, 6, 8, 10,

10, 12

20

1

2

1

1

2

1

1, 2

-

0.8

1.27

1.27

1.27

2.0

2.54

-

2.3

up to 9.0 (2 pins)

8.7

1.7

5

12

17.5

3

-

-

3

-

-

-

SMT

SMT

SMT

SMT, Solder, Pressfit SMT

AWG 22, 24, 26

AWG 30

AWG 22, 24

AWG 18, 20, 22, 24,

26

AWG 22, 24, 26

-

Latching

Yes

Yes

Yes

Yes

Yes

Yes

-

-

-

400

1000

100

-

AWG 20 26, 24 - 28

-

AWG 22 - 26

-

Optional (housing)

Yes

Yes

EDA使用手册

前言前言中国航空工业总公司第615研究所下属的上海埃威航空电子有限公司是开发、研制、生产AEDK仿真机、教学实验机、LED显示屏和工控机的高新技术企业。

其开发生产的爱迪克仿真机曾荣获上海科技进步奖和航空部科技进步奖;其开发的爱迪克仿真机和教学实验系统在国家教委招标中,曾多次中标。

AEDK-EDA教学实验机是集实验、开发等功能于一体的高新技术实验系统。

该系统自带微处理器、大规模可编程逻辑芯片、键盘、数码管、液晶、A/D、D/A、以及各种输入/输出模块,具有与PC机通讯的功能。

能够开发各类高速/低速信号处理以及模拟信号处理的系统。

该实验系统性能优越,功能齐全,价格低廉。

提供的实验完全满足教学大纲的要求。

同时,该实验系统可以外接机电实验平台(我公司研制开发),做机电一体化实验。

总之,该实验系统是大中专院校、技校、职校学习微处理器原理和微机外围接口的最佳选择。

本书是一本与AEDK-EDA实验系统相配套的使用手册,在该使用手册中,主要介绍了实验系统的硬件结构、配置方式和软件的使用方法等内容。

与AEDK-EDA实验系统相关的指导书还有《AEDK-EDA实验指导书》。

在使用实验机前,请认真阅读本书的各章,这样有助于使用者能更全面地了解该类型的实验机的系统资源配置和系统硬件配置。

由于编者水平有限,书中难免有不当之处,谨请读者批评指正。

最后,向关心和厚爱爱迪克仿真机和教学实验机等系列产品的广大用户表示衷心的感谢!编者上海埃威航空电子有限公司第一章 性 能 特 点第一章 性 能 特 点1.1 系统组成AEDK-EDA 教学实验系统是上海航虹高科技有限公司在继承各种教学实验机优点的基础上,广泛地吸取用户的使用意见和建议,结合长期使用大规模可编程芯片经验的基础上,推出的新一代EDA 教学实验系统。

本实验系统由大规模可编程芯片为核心实验机外配辅助实验模块以及微控制器和通讯接口及选配件组成(图1.1所示)。

该实验系统,一般需要通过PC 机才能完成所有功能的运行,又可以通过串口接PC 机调试通讯实验。

EDA的入门资料文档课件

积项分配。 • 作为触发器功能,每个宏单元寄存器可以单独编程为具有可编程时

钟控制的D、T、JK或SR触发器工作方式。每个宏单元寄存器也可 以被旁路掉,以实现组合逻辑工作方式。在设计输入时,设计者指 明所需的触发器类型,然后由Quartus Ⅱ和MAX+PLUSⅡ为每一个 触发器功能选择最有效的寄存器工作方式,以使设计资源最少。 • 每一个可编程寄存器的时钟可配置成三种不同方式。 • ① 全局时钟:这种方式能实现从时钟到输出最快的性能。 • ② 带有高电平有效的时钟使能的全局时钟:这种方式为每个寄存 器提供使能信号,仍能达到全局时钟的快速时钟到输出的性能。 • ③ 乘积项时钟:在这种方式下,寄存器由来自隐埋的宏单元或I/O 引脚的信号进行时钟控制。

6016、 6010A 、 6016A 、 6024A 、 8282A 、 8282AV 、

8452A、 8636A 、 8820A、 81188A 、 81500A

速度等级

EPC: 1064、 1064V、 1213、 1441、 1、 2、 4、 8、 16

EPM : 7032、 7064、 7096、 7032S、 7064S、 7128S、 7160S、

CMOS EEPROM技术制造的。MAX 7000器件提供多达5000个可 用门和在系统可编程(ISP)功能,其引脚到引脚延时快达5ns, 计数器频率高达175.4MHz。各种速度等级的MAX 7000S、MAX 7000A/AE/B和MAX 7000E器件都遵从PCI总线标准。 • MAX 7000器件具有附加全局时钟,输出使能控制,连线资源和 快速输入寄存器及可编程的输出电压摆率控制等增强特性。MAX 7000S器件除了具备MAX 7000E的增强特性之外,还具有JTAG BST边界扫描测试,ISP在系统可编程和漏极开路输出控制等特性。

EDA实验指导书(EP3C16Q240C8)(2011.10.28)

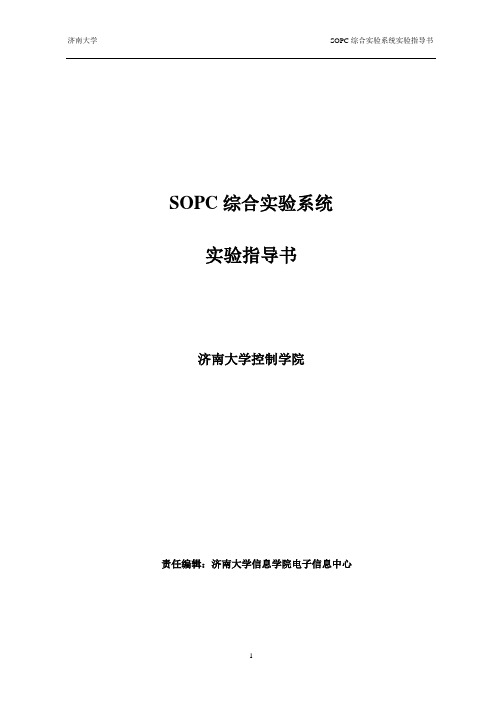

SOPC综合实验系统实验指导书济南大学控制学院责任编辑:济南大学信息学院电子信息中心目录目录 (1)第三章VHDL基本程序设计实验 (22)实验一组合逻辑半加器的设计 (22)实验二使用VHDL设计组合逻辑全加器 (29)实验三带进位输入的8位加法器 (34)实验四全减器 (39)实验五四位向量加法/减法器 (42)实验六组合逻辑3-8译码器的设计 (46)实验七数据比较器 (50)实验八多路数据选择器 (53)实验九编码器 (57)实验十计数器 (62)实验十一7段数码管控制接口 (65)实验十二16*16点阵设计 (69)实验十三MOORE机 (76)实验十四MEALY机 (80)实验十五D/A接口 (84)实验十六A/D接口 (87)实验十七动态数码管显示实验 (91)第四章SOPC系统基本实验 (95)实验一Hello-Led流水灯实验 (95)实验二数码管显示实验 (103)实验三按键输入中断实验 (107)实验四4乘4键盘实验 (111)第三章VHDL基本程序设计实验实验一组合逻辑半加器的设计一、实验目的2、通过一个简单的一位半加器的设计,让学生掌握组合逻辑电路的设计方法。

3、掌握组合逻辑电路的静态测试方法。

4、初步了解可编程逻辑器件设计的全过程。

5、熟识quartus II软件基本功能的使用。

二、实验原理半加器实现两位不带进位加法输出和及进位。

一位半加器有两个输入a、b;两个输出s,Co。

加数a 和s三、实验步骤1、创建工程运行Quartus II软件,如下图所示:建立工程,File New Project Wizad,既弹出“工程设置”对话框,如图所示单击此对话框最上一栏右侧的“...”按钮选择工作目录,在D盘中建一个工程文件夹,取名为test。

单击“打开”按钮,在第二行和第三行中写工程名为“half_adder”。

按Next按钮,出现添加工程文件的对话框,如下图所示:这里无需添加文件,我们跳过此步,直接按next进行下一步,如下图所示,选择FPGA/CPLD 器件的型号,本试验箱选用Altera公司的Cyclone III 系列FPGA 芯片EP3C16Q240C8。

eda实验1指导手册

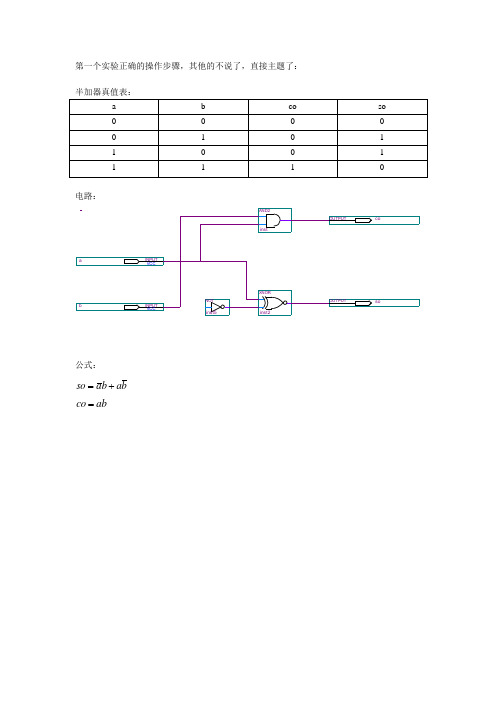

第一个实验正确的操作步骤,其他的不说了,直接主题了:电路:公式:=so+b aabco=ab实验步骤:点File->New Project Wizard,弹出下图,按page 1、2、3、4、5 of 5,分布设置以下5个对话框。

点击Finish结束。

在Project Navigator卡中呈现如下:点按钮,出现下列对话框,选择蓝色部分,点ok出现点符号,出现下框,并选择primitives库,在Name出输入相应的名称,获得元件图后,点击OK,就能在图形输入框中把元件逐个放入。

并用连线。

结果如下点击工具栏上的图标,对原理图进行编译,当出现如下信息,编译成功。

在点击,出现下图,选择蓝色部分,点击ok在右边出现waveform1.vmf文件内容:在如下框内鼠标右击,出现insert node or bus,点击。

出现:点击Node Finder按钮,点击list,在nodes found卡中出现a、b、co、so端口,选中所有,按键,将所有节点放入Selected Nodes卡中,点击OK结果如下:选中入口a,如图呈现天蓝色,点击左边的按钮,出现clock对话框,设置Period值,重复操作入口b结果如下:保存vwf文件点击Assignment->setting->simulator setting,选择Simulation mode模式为functional,并确认simulation input为对应vwf文件。

点击Processing->Generation Functional Simulation Netlist,注意这个一定要点,否则出现的结果有错误,就像课堂上老师犯的错误一样。

出现成功对话框,按确定即可。

点击,开始仿真,结果如下:按确定,查看仿真结果,比较真值表中数据,看是否正确。

做完这个部分,如果要把半加器封装成一个模块,可以点击file->creat/update->create symbol files for current file, 弹出如下对话框,设置默认名保存即可。

【商品说明书】eda产品手册

eda产品手册嘿,各位数字设计界的探索者们,你们是否曾在复杂的电路设计中迷失方向?是否渴望拥有一款能够助你轻松驾驭各种设计挑战的神器?今天,就让我带你走进EDA(电子设计自动化)产品的神秘世界,一起解锁数字设计的无限可能!首先,咱们得明确一个核心观点:EDA产品,就是数字设计师手中的那把瑞士军刀,无所不能!它集成了原理图设计、布局布线、仿真验证、生产制造等一系列功能于一体,让你的设计之路从此畅通无阻。

是不是已经迫不及待想要了解它的庐山真面目了?别急,咱们慢慢来!一、EDA产品初印象:界面友好,操作便捷当你第一次打开EDA产品,你会发现它的界面设计得既专业又不失亲和力。

各种工具栏、菜单栏、属性窗口一目了然,仿佛是在告诉你:“嘿,朋友,我很好上手哦!” 不仅如此,EDA产品还支持多种快捷键操作,让你在设计过程中能够行云流水,效率倍增。

二、原理图设计:从零到一的创造之旅在EDA的世界里,原理图设计是基石。

你可以在这里尽情挥洒创意,将脑海中的电路构思转化为实实在在的图形表达。

EDA产品提供了丰富的元件库,无论是电阻、电容、电感,还是复杂的集成电路,都能轻松找到。

而且,它还支持元件的拖拽、旋转、缩放等操作,让你的设计更加灵活多变。

怎么样,是不是已经跃跃欲试,想要亲手绘制一张属于自己的原理图了呢?三、布局布线:精准高效,打造完美作品如果说原理图设计是构思阶段,那么布局布线就是将构思付诸实践的关键步骤。

EDA产品在这方面同样表现出色。

它可以根据你的设计需求,自动或手动进行元件的布局和布线。

无论是紧凑型的嵌入式系统,还是复杂的PCB板,都能在它的帮助下变得井井有条。

而且,EDA产品还支持多种布线规则检查,确保你的设计符合生产要求,避免不必要的返工。

四、仿真验证:让想法在虚拟世界中飞翔在EDA产品中,仿真验证是不可或缺的一环。

它可以帮助你在设计初期就发现潜在的问题,从而避免在后续的生产制造中造成损失。

EDA产品提供了多种仿真工具,如电路仿真、信号完整性仿真、热仿真等,让你的设计在虚拟世界中得到充分验证。

EDA指导书2011

第二部分实验部分实验一ISE软件的基本操作与应用一、实验目的:1、通过一个1位全加器的设计,熟悉ISE软件的基本应用。

2、掌握VHDL设计输入方法和测试基准波形文件输入方法。

3、熟悉ModelSim软件的基本应用,掌握功能仿真过程。

二、实验步骤:1、启动ISE集成开发环境,新建一个工程。

2、为工程添加设计源文件。

3、对源文件进行语法检查,并改正错误之处。

4、输入测试基准波形文件。

5、进行仿真,记录仿真结果。

6、检查仿真结果的正确性。

7、若仿真结果不正确,说明设计有错误(非语法错误,而是设计的功能不正确)。

修改设计源文件,重新仿真直至得到正确的结果。

三、实验报告预习要求:1、阅读教材第二章、第三章,熟悉ISE软件的VHDL语言设计输入方法,掌握使用ModelSim对设计进行仿真的流程。

2、熟读教材7.2实例一,掌握使用ISE进行设计输入与功能仿真的过程。

3、写出1位全加器的VHDL源程序。

4、画出1位全加器的测试基准波形文件,并画出1位全加器正确的输出波形。

实验记录:5、记录1位全加器功能仿真结果(波形)。

6、说明实验中遇到的问题及解决方法,写出实验心得体会。

实验二3-8译码器一、实验目的:1、通过一个3-8译码器的设计,巩固ISE软件的应用。

2、掌握ISE软件的综合与设计实现流程。

3、掌握设计约束的输入方法。

4、掌握组合逻辑电路的时序仿真方法。

二、实验步骤:1、启动ISE集成开发环境,新建一个工程。

2、为工程添加设计源文件。

3、对源文件进行语法检查,并改正错误之处。

4、对设计进行综合、翻译与映射。

5、创建UCF文件,添加I/O约束,锁定引脚。

6、对设计进行布局布线,生成布局布线后仿真模型。

7、输入测试基准波形文件。

8、进行时序仿真,修改设计中的错误,记录仿真结果。

三、实验报告预习要求:1、阅读教材第五章5.1~5.3节,熟悉ISE软件的设计实现过程,掌握引脚锁定方法。

2、熟读教材7.3实例二,巩固使用ISE对进行设计和仿真的过程。

EDA用户使用手册及引脚

EDA/SOPC系统开发平台用户使用手册北京百科融创教学仪器设备有限公司目录第一章综述 (3)第二章系统模块 (7)2.1 系统组成 (7)2.2 模块介绍 (9)2.3 使用注意事项: (35)2.4 SOPC-NIOSII EDA/SOPC 系统开发平台说明 (36)第一章综述SOPC-NIOSII EDA/SOPC 实验开发系统是根据现代电子发展的方向,集EDA 和SOPC 系统开发为一体的综合性实验开发系统,除了满足高校专、本科生和研究生的SOPC 教学实验开发之外,也是电子设计和电子项目开发的理想工具。

整个开发系统由核心板SOPC-NiosII-EP2C35、系统板和扩展板构成,根据用户不同的需求配置成不同的开发系统。

SOPC-NiosII-EP2C35 开发板为基于Altera Cyclone II 器件的嵌入式系统开发提供了一个很好的硬件平台,它可以为开发人员提供以下资源:拥有33216 个逻辑单元和483840 bits片上存储单元Cyclone II EP2C35F672C8 FPGA16 Mbits 的EPCS16 配置芯片1 Mbytes SRAM32 Mbytes SDRAM8 Mbytes NOR Flash ROM64 Mbytes NAND Flash ROMRS-232 DB9 串行接口USB2.0 设备接口10BASE-T J45 接口多路音频CODEC 接口4 个用户自定义按键4 个用户自定义LED1 个七段码LED标准AS 编程接口和JTAG 调试接口50MHz 高精度时钟源两个高密度扩展接口(可与配套实验箱连接)两个标准2.54mm 扩展接口,供用户自由扩展系统上电复位电路支持+5V 直接输入,板上电源管理模块SOPC-NiosII-EP2C35开发板是在经过长期用户需求考察后,结合目前市面上以及实际应用需要,同时兼顾入门学生以及资深开发工程师的应用需求而研发的。

EDA说明书

目录1 绪论 (1)2 设计要求 (1)3 Quartus II软件简介 (1)4 方案设计 (1)4.1方案选择及论证 (1)4.2设计框图 (2)5 设计过程 (2)5.1抢答模块的设计 (2)5.2扬声器模块的设计 (2)5.3计分模块的设计 (3)5.4主程序设计 (3)6模块电路图 (3)7 仿真及调试 (4)7.1 2号抢答并回答错误扣十分 (4)7.2 3号抢答并回答正确加十分 (5)8 心得体会 (5)参考文献 (6)程序清单 (7)1 绪论在许多比赛活动中,为了准确、公正、直观地判断出第一抢答者,通常设置一台抢答器,通过数显、灯光及音响等多种手段指示出第一抢答者。

为了能在实际中得到真正的应用,它必须有以下功能:1)有在主持人按下开始开关后,抢答才有效。

2)当其中有一路选手按下后,其它的开关失效。

3)具有声音报告功能,当有选手按下时,同时有响声表示有人抢答。

当然以上只是最简单而且是十分必要的功能。

为了做到这点,必须设计一个所用元件最少,结构最简单,成功率最高的作品来。

2 设计要求1)设计一个4组参赛的数字式抢答器2)抢答器具有第一信号鉴别和锁存功能,使除第一抢答外地按钮不起作用。

3)设置一个主持人“复位”按钮。

4)主持人复位后,开始抢答,第一信号鉴别锁存电路得到信号后,有指示灯显示抢答组别,扬声器发出2-3秒的音响。

5)设置一个记分电路,每组开始预置100分,由主持人记分,答对一次加10分,答错一次减10分。

3 Quartus II软件简介Quartus II 是Altera公司的综合性PLD/FPGA开发软件,支持原理图、VHDLVerilogHDL等多种设计输入形式,可以完成从设计输入到硬件配置的完整PLD设计流程。

提供了完善的用户图形界面设计方式。

具有运行速度快,界面统一,功能集中,易学易用等特点。

4 方案设计4.1方案选择及论证数字式抢答器应具备锁存功能,将第一个抢答者的信号进行锁存,并有音响予以配合,来保证抢答的及时性。

EDA工具手册约束管理器分册

EDA工具手册约束管理器分册目录第一章约束管理器介绍 (4)1.1约束管理器简介 (4)1.2约束管理器界面简介 (8)1.2.1worksheet selector (8)1.2.2用户接口 (9)1.2.3View选项 (9)1.3启动约束管理器 (11)第2章OBJECTS介绍 (12)2.1P IN-P AIRS (13)2.1.1Pin-Pair规则 (14)2.2N ETS和X NETS (14)2.3B USES (15)2.4M ATCH G ROUPS (15)2.4.1如何确定target pin pair (16)2.4.2相对/匹配的群组规则 (16)2.5D IFF P AIRS (16)2.5.1差分对工作表 (17)2.5.2差分计算器(Differential Calculator)的使用方法 (19) 2.5.3差分对规则 (19)2.6D ESIGNS AND S YSTEMS (20)第3章设置网络的走线约束 (21)3.1.1设置网络的最大最小传输延迟 (21)3.1.2设置网络相对传输延迟 (24)3.1.3设置差分对约束 (26)3.1.4查看网络规范格式和物理格式 (28)第4章设置网络的时序和信号完整性约束 (30)4.1设置时序约束 (30)4.2设置信号完整性约束 (32)4.2.1设置电气属性约束 (32)4.2.2设置反射属性约束 (33)第5章电子约束创建和应用 (35)5.1创建ECS ET (35)5.2指定ECS ET给网络 (40)5.3不考虑ECS ET的缺省约束值 (41)5.4在原理图中查看ECS ET (41)第6章ECOS实现 (43)6.1在原理图中增加网络 (43)6.2在原理图中修改约束 (45)6.3在约束管理器中修改约束 (46)6.4在约束管理器中删除约束 (46)6.5在原理图中重新命名网络 (47)第7章在原理图和PCB之间同步约束 (50)7.1从原理图中输出约束 (50)7.2在PCB D ESIGN中查看和添加约束 (50)7.3在原理图中导入并查看约束 (51)7.4在PCB和原理图之间同步约束的两种模式 (52) 7.4.1用原理图中的约束重写PCB中的约束 (53) 7.4.2在原理图中导入PCB中变更的约束 (56)第8章约束分析 (58)8.1查看工作表单元格和对象 (58)8.2定制约束、定制测量和定制激励 (59)8.2.1定制约束 (59)8.2.1.1 用户定义的属性 (59)8.2.1.2 约束的定制测量 (59)第9章SCHEDULING NETS (61)9.1S CHEDULING N ETS (61)9.2S CHEDULING N ETS-R EVISITED (65)第10章相对传输延迟 (68)第11章MATCH DELAY (73)第12章解决DRC冲突 (74)第13章约束管理器 (76)13.1层次设计中的电子约束 (76)第一章约束管理器介绍约束管理器是一个交叉的平台,以工作簿和工作表的形式在Cadence PCB设计流程中用于管理所有工具的高速电子约束。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1医学图像三维重建原理医学图像三维重建主要由以下几步:1.对二维图像进行分割,提取有用的信息;2.得到不同的图像并用相应的三维重建算法进行三维重建;3.用相应的软件实现图像重建后的显示。

1.1X射线二维图像的获取原理1.1.1X线的产生特性(一)X线的产生1895年,德国科学家伦琴发现了具有很高能量,肉眼看不见,但能穿透不同物质,能使荧光物质发光的射线。

因为当时对这个射线的性质还不了解,因此称之为X射线。

为纪念发现者,后来也称为伦琴射线,现简称X线(X-ray)。

一般说,高速行进的电子流被物质阻挡即可产生X线。

具体说,X线是在真空管内高速行进成束的电子流撞击钨(或钼)靶时而产生的。

因此,X线发生装置,主要包括X线管、变压器和操作台。

X线管为一高真空的二极管,杯状的阴极内装着灯丝;阳极由呈斜面的钨靶和附属散热装置组成。

变压器为提供X线管灯丝电源和高电压而设置。

一般前者仅需12V以下,为一降压变压器;后者需40~150kV(常用为45~90kV)为一升压变压器。

操作台主要为调节电压、电流和曝光时间而设置,包括电压表、电流表、时计、调节旋钮和开关等。

在X线管、变压器和操作台之间以电缆相连。

X线机主要部件及线路见图2.1.1。

X线的发生程序是接通电源,经过降压变压器,供X线管灯丝加热,产生自由电子并云集在阴极附近。

当升压变压器向X线管两极提供高压电时,阴极与阳极间的电势差陡增,处于活跃状态的自由电子,受强有力的吸引,使成束的电子,以高速由阴极向阳极行进,撞击阳极钨靶原子结构。

此时发生了能量转换,其中约1%以下的能量形成了X线,其余99%以上则转换为热能。

前者主要由X线管窗口发射,后者由散热设施散发。

图2.1.1 X线机主要部件示意图(二)X线的特性X线是一种波长很短的电磁波。

波长范围为0.0006~50nm。

目前X线诊断常用的X线波长范围为0.008~0.031nm(相当于40~150kV时)。

在电磁辐射谱中,居γ射线与紫外线之间,比可见光的波长要短得多,肉眼看不见。

除上述一般物理性质外,X线还具有以下几方面与X线成像相关的特性:穿透性:X线波长很短,具有很强的穿透力,能穿透一般可见光不能穿透的各种不同密度的物质,并在穿透过程中受到一定程度的吸收即衰减。

X线的穿透力与X线管电压密切相关,电压愈高,所产生的X线的波长愈短,穿透力也愈强;反之,电压低,所产生的X线波长愈长,其穿透力也弱。

另一方面,X线的穿透力还与被照体的密度和厚度相关。

X线穿透性是X线成像的基础。

荧光效应:X线能激发荧光物质(如硫化锌镉及钨酸钙等),使产生肉眼可见的荧光。

即X线作用于荧光物质,使波长短的X线转换成波长长的荧光,这种转换叫做荧光效应。

这个特性是进行透视检查的基础。

摄影效应:涂有溴化银的胶片,经X线照射后,可以感光,产生潜影,经显、定影处理,感光的溴化银中的银离子(Ag+)被还原成金属银(Ag),并沉淀于胶片的胶膜内。

此金属银的微粒,在胶片上呈黑色。

而未感光的溴化银,在定影及冲洗过程中,从X线胶片上被洗掉,因而显出胶片片基的透明本色。

依金属银沉淀的多少,便产生了黑和白的影像。

所以,摄影效应是X线成像的基础。

电离效应:X线通过任何物质都可产生电离效应。

空气的电离程度与空气所吸收X 线的量成正比,因而通过测量空气电离的程度可计算出X线的量。

X线进入人体,也产生电离作用,使人体产生生物学方面的改变,即生物效应。

它是放射防护学和放射治疗学的基础。

1.1.2X线成像的基本原理X线之所以能使人体在荧屏上或胶片上形成影像,一方面是基于X线的特性,即其穿透性、荧光效应和摄影效应;另一方面是基于人体组织有密度和厚度的差别。

由于存在这种差别,当X线透过人体各种不同组织结构时,它被吸收的程度不同,所以到达荧屏或胶片上的X线量即有差异。

这样,在荧屏或X线上就形成黑白对比不同的影像。

因此,X线影像的形成,应具备以下三个基本条件:首先,X线应具有一定的穿透力,这样才能穿透照射的组织结构;第二,被穿透的组织结构,必须存在着密度和厚度的差异,这样,在穿透过程中被吸收后剩余下来的X线量,才会是有差别的;第三,这个有差别的剩余X线,仍是不可见的,还必须经过显像这一过程,例如经X线片、荧屏或电视屏显示才能获得具有黑白对比、层次差异的X线影像。

人体组织结构,是由不同元素所组成,依各种组织单位体积内各元素量总和的大小而有不同的密度。

人体组织结构的密度可归纳为三类:属于高密度的有骨组织和钙化灶等;中等密度的有软骨、肌肉、神经、实质器官、结缔组织以及体内液体等;低密度的有脂肪组织以及存在于呼吸道、胃肠道、鼻窦和乳突内的气体等。

当强度均匀的X线穿透厚度相等的不同密度组织结构时,由于吸收程度不同,因此将出现如图2.1.2所示的情况。

在X线片上或荧屏上显出具有黑白(或明暗)对比、层次差异的X线影像。

在人体结构中,胸部的肋骨密度高,对X线吸收多,照片上呈白影;肺部含气体密度低,X线吸收少,照片上呈黑影。

图2.1.2 不同密度组织(厚度相同)与X线成像的关系X线穿透低密度组织时,被吸收少,剩余X线多,使X线胶片感光多,经光化学反应还原的金属银也多,故X线胶片呈黑影;使荧光屏所生荧光多,故荧光屏上也就明亮。

高密度组织则恰相反病理变化也可使人体组织密度发生改变。

例如,肺结核病变可在原属低密度的肺组织内产生中等密度的纤维性改变和高密度的钙化灶。

在胸片上,于肺影的背景上出现代表病变的白影。

因此,不同组织密度的病理变化可产生相应的病理X线影像。

人体组织结构和器官形态不同,厚度也不一致。

其厚与薄的部分,或分界明确,或逐渐移行。

厚的部分,吸收X线多,透过的X线少,薄的部分则相反,因此,X线投影可有图2.1.3所示不同表现。

在X线片和荧屏上显示出的黑白对比和明暗差别以及由黑到白和由明到暗,其界线呈比较分明或渐次移行,都是与它们厚度间的差异相关的。

图2.1.3中的几种情况,在正常结构和病理改变中都有这种例子。

由此可见,密度和厚度的差别是产生影像对比的基础,是X线成像的基本条件。

应当指出,密度与厚度在成像中所起的作用要看哪一个占优势。

例如,在胸部,肋骨密度高但厚度小,而心脏大血管密度虽低,但厚度大,因而心脏大血管的影像反而比肋骨影像白。

同样,胸腔大量积液的密度为中等,但因厚度大,所以其影像也比肋骨影像为白。

需要指出,人体组织结构的密度与X线片上的影像密度是两个不同的概念。

前者是指人体组织中单位体积内物质的质量,而后者则指X线片上所示影像的黑白。

但是物质密度与其本身的比重成正比,物质的密度高,比重大,吸收的X线量多,影像在照片上呈白影。

反之,物质的密度低,比重小,吸收的X线量少,影像在照片上呈黑影。

因此,照片上的白影与黑影,虽然也与物体的厚度有关,但却可反映物质密度的高低。

在术语中,通常用密度的高与低表达影像的白与黑。

例如用高密度、中等密度和低密度分别表达白影、灰影和黑影,并表示物质密度。

人体组织密度发生改变时,则用密度增高或密度减低来表达影像的白影与黑影。

图2.1.3 不同厚度组织(密度相同)与X线成像的关系1.1.3X线成像设备X线机包括X线管及支架、变压器、操作台以及检查床等基本部件。

60年代以来,影像增强和电视系统技术的应用,使它们逐渐成为新型X线机的主要部件之一。

为了保证X线摄影质量,新型X线机在摄影技术参数的选择、摄影位置的校正方面,都更加计算机化、数字化、自动化。

为适应影像诊断学专业的发展,近30多年来,除通用型X线机以外,又开发了适用于心血管、胃肠道、泌尿系统、乳腺及介入放射、儿科、手术室等专用的X线机。

1.2CT图像的特点CT值是指X射线穿过器官或组织后被吸收的程度,其值可以用来衡量器官或组织对X射线的吸收率,单位为Hu(Hounsfidd unit),某物质的CT值等于该物质对X射线的衰减系数减去水的衰减系数之后除以水的衰减系数,最后再乘以1000。

物质的密度越大,则CT值越高,因此可以用CT值来说明物质的密度。

人体不同组织的密度不同,例如骨头的密度较大,软组织的密度相对较小。

水的CT值为0Hu,骨皮质的CT值为+1000Hu,空气为.1000Hu。

其余的不同组织介于.1000Hu.1000Hu之间。

CT图像是指由一定数目的像素按照矩阵排列而成的二维断层图像,这些像素反映了单位容积的X射线的吸收系数。

CT图像本身具有的特点如下:1.象素越小,数目越多,构成图像越细致,即空间分辨力越高。

2.CT图像的密度分辨率高。

CT图像黑影表示低吸收区,如软组织和肺部等部位,白影表示高吸收区,如骨骼的吸收率最高。

3.噪声。

医学图像中可能出现斑点、细粒、网纹、雪花状等结构异常,使图像质量下降,这对图像分析、分类和识别影响很大,甚至使人无法做出正确的判断。

CT图像的噪声主要包括量子噪声和电子噪声。

4.伪影。

在CT图像上非真实的阴影或干扰称为伪影。

它降低图像的质量,易造成误诊或不可诊。

它可分为由病人引起的伪影和由CT设备本身所造成的伪影两大类。

具有模糊性和不均匀性,因为医学器械不可避免的会降低图像的清晰度和均匀性。

1.3面绘制和体绘制目前应用最多的三维重建的方法主要有面绘制和体绘制两类。

面绘制是指表面重建,即从医学影像设备输出的切片数据集构造出三维数据,然后在三维数据中抽取出等值面,然后进行三角剖分,获得三角形面片,再用的图形学中的图元绘制技术将三角形面片绘制出来而实现表面绘制,面绘制可以将三维数据中具有某个特定值的表面有效地绘制出来,但不能有效的表达体数据的内部信息;体绘制(V olume Rendering)将体数据中的“体素"作为基本的绘制单位,这种绘制方法充分利用了三维体数据中的每一个体素,也称直接体绘制,体绘制能够根据需要显示三维对象的内部信息,但计算量大。

体绘制的过程包括对体数据的采样、重构、合成和绘制等操作,交互过程中还涉及到重采样。

1.3.1面绘制面绘制将医学影像设备输出的连续的断层图像序列作为输入,并对这些图像进行经分割和提取,根据不同的方法将提取出来的表面绘制出来。

提出的表面一般以多边形面片来表示,图形学中最常用也是最容易绘制的的多边形是三角形。

早期的医疗影像设备由于技术原因输出的切片的厚度较大,所以当时主要通过轮廓连接(Contour Connection,也称为从平面轮廓重建形体,Shape from Planar Contours)的方法进行体数据的面绘制,也就是轮廓线的提取过程仍是在二维图像上操作。

其中具代表性的是1975Keppel提出的用三角形面片的组合来模拟物体表面的方法。

这种面绘制的方法由于是从断层图像上进行轮廓抽取,因此需要考虑到层间的轮廓吻合以及外表面的拟合等问题。

随着医疗影像设备技术的改进,最新的CT和MRI设备的输出的切片间距可以达到很小,切片内象素分辨率也很高了,这是基于体素的表面重建方法应运而生,目前也逐渐取代了轮廓线提取算法。