输入引脚的过电应力(EOS)保护

EOS验证与失效分析

EOS验证与失效分析赖国印失效分析与终端质量管理全球制造摘要FAE遇到组件失效时,若因无组件失效分析之能力,将失效组件送回厂商分析,但组件厂商的回复报告有极大部分的失效原因为EOS 所导致,造成时间和成本的浪费。

本文探讨EOS之成因且对组件之失效分析应执行的验证及处理流程,透过案例研讨,期有效帮助工程师判断电子组件失效的原因是否为EOS所造成,进而找到根本原因(Root Cause)。

避免因EOS造成之失效组件送厂商分析所产生的时间和成本的浪费。

一. 前言EOS 是"Electrical Overstress"的简称,其造成电子组件失效之原理如同过电流流过保险丝产生热能保险丝烧断为相同的道理。

在大多数的失效案例中电子组件内部电路与地(GND) 或不同电位点之间形成短路,产生过电流而造成组件损坏为大多数电子组件失效的主要因素。

此外有人会对EOS与ESD产生混淆,简言之,ESD也是EOS的一种,但因ESD对电子组件的损害,其严重程度与能量大小有关。

如果能量较小,可能只导致电子组件轻微的损坏影响其可靠度,并未造成立即的功能不良,如果能量较大,可导致电子组件被击穿或形成过电流对组件形成永久性损坏甚至烧毁,就是EOS。

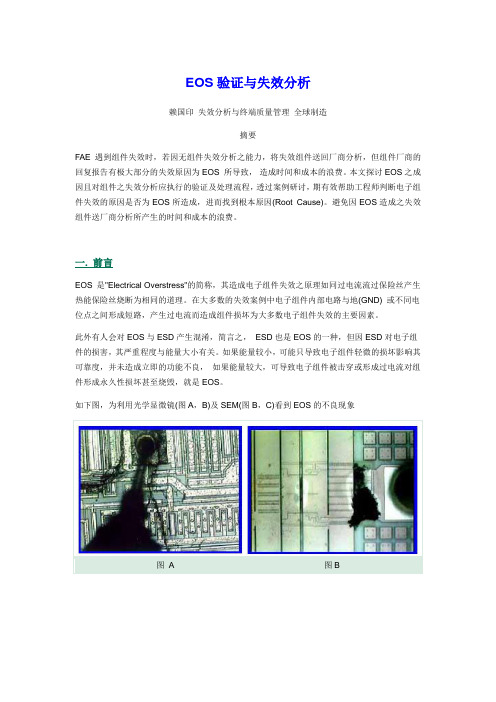

如下图,为利用光学显微镜(图A,B)及SEM(图B,C)看到EOS的不良现象图 C 图D(图片来源: VOLTERRA Silicon Power Solutions –ESD/EOS Differences)二. 为何要做EOS验证根据电子组件业界常见的失效原因分析中,EOS占了约47 %,如图一所示。

由此可知EOS 对制造业产生质量成本的影响相当严重是所有电子组件失效原因之首。

三. 验证流程及方法为因应EOS的问题,本单位发展出一套系统化的分析验证及处理流程能让失效分析工程师在第一时间澄清失效之电子组件是否EOS所造成,及时正确判断不必将有EOS问题的电子组件送厂商分析而丧失寻找问题根本原因及解决问题之黄金时间。

eos电气过应力电路处理方法

eos电气过应力电路处理方法EOS(Electrical Over Stress)是指电路中的电子元器件受到过高的电压、电流或功率而产生的损坏。

EOS可能导致电路性能下降、设备损坏或系统崩溃。

因此,采取有效的EOS电气过应力电路处理方法至关重要。

一、EOS原因分析1. 过电压:当电源电压超过正常范围时,可能会导致元器件损坏。

这是因为过高的电压可能会使元器件承受过大的电应力,从而导致其性能下降或损坏。

2. 过电流:当电流超过元器件的额定值时,也可能会导致元器件损坏。

过大的电流可能会使元器件过热,从而损坏其内部结构或性能。

3. 功率过载:当功率超过元器件的额定值时,可能会导致元器件损坏。

功率过载可能会导致元器件过热,从而损坏其内部结构或性能。

4. 静电放电:静电放电是一种常见的电磁干扰源,它可能会导致元器件损坏。

静电放电可能会产生高电压和电流,从而对元器件造成损坏。

5. 电磁干扰:电磁干扰可能会对电路性能产生负面影响,导致信号失真、误码等问题。

电磁干扰可能来自于各种来源,如电源线、无线电信号等。

二、EOS电气过应力电路处理方法1.电源管理:电源管理在电子设备中起着至关重要的作用。

采用合适的电源管理方案,可以确保电源电压在正常范围内稳定波动,避免电压过高或过低对设备造成损害。

在遇到过电压情况时,可以采取稳压电源或电压保护措施,以防止设备受损。

稳压电源能够稳定输出电压,保证设备在电压波动的情况下仍能正常工作。

电压保护措施则能在电压超出正常范围时,及时切断电源,保护设备免受损害。

2.电流限制:电流限制是电子设备安全运行的关键。

在电路中设置合适的电流限制,能够避免因过电流导致的元器件损坏。

过电流保护电路会在电流超出设备承受范围时,自动切断电源,防止元器件过热、烧毁等现象发生。

此外,合理设置电流限制还能降低设备功耗,延长电池续航时间。

3.功率管理:功率管理对电子设备的稳定运行同样重要。

采用合适的功率管理方案,可以确保设备在功率过载的情况下仍能正常运行。

MiCOM 技术说明书 v C

2.1.2.4

曲线 Laborelec

............................................................................................27

上海施耐德电气电力自动化有限公司

MiCOM P521

第 页 共 页 4 / 66 技术说明书

2.2.6

断路器控制 ............................................................................................................39

2.2.7

断路器状况监视 .....................................................................................................39

MiCOM P521

目录

第 页 共 页 3 / 66 技术说明书

装置简介 1.

...................................................................................................................8

2.2.10

故障记录 ................................................................................................................40

2.2.11

瞬时启动记录.........................................................................................................40

ESD

ESD测试及原理介绍BYD Microelectronics ConfidentialMenu-11 2 3 4ESD基本介绍 ESD失效模式和失效机理 ESD测试模式,原理及测试方法 常见ESD保护结构及原理BYD Microelectronics Confidential一 ESD的基本介绍BYD Microelectronics Confidential背景在人们的日常工作生活中, 静电放电(ESD)现象可谓无处不在, 瞬间产生的上 升时间低于纳秒(ns)、持续时间可达数百纳秒且高达数十安培的电流, 会对手 机、 笔记本电脑等电子系统造成损伤。

对于电子系统设计人员而言, 如果没有采取适 当的ESD 保护措施, 所设计的电子产品就会有遭到损伤的可能。

静电放电( ESD, Electrostatic Discharge) 给电子器件环境会带来破坏性的后 果。

它是造成集成电路失效的主要原因之一。

随着集成电路工艺不断发展,互补 金属氧化物半导体( CMOS, ComplementaryMetal- Oxide Semiconductor) 的特 征尺寸不断缩小,金属氧化物半导体(MOS, Metal- Oxide Semiconductor)的栅氧 厚度越来越薄,MOS 管能承受的电流和电压也越来越小, 因此要进一步优化电路 的抗ESD 性能, 需要从全芯片ESD 保护结构的设计来进行考虑。

BYD Microelectronics ConfidentialESD的产生及影响一般来讲,一个充电的导体接近另一个导体时,就可能发生ESD。

首先,两个导 体之间会建立一个很强的电场,产生由电场引起的击穿。

两个导体之间的电压超 过它们之间空气和绝缘介质的击穿电压时,就会产生电弧。

在0. 7 ns~10. 0 ns 的时间里,电弧电流会达到几十安培,有时甚至超过100 A。

电弧将一直维持直到 两个导体接触短路或者电流低到不能维持电弧为止。

浅谈LED照明的电性应力(EOS)冲击防护方案的区别

浅谈LED照明的电性应力(EOS)冲击防护方案的区

别

随着LED技术的日趋成熟,LED照明的使用越来越广泛,例如手机的LED闪光,LED家用灯具,汽车的LED前灯和尾灯等等。

但是如何有效的延长LED的使用寿命,也许你并不是特别清楚。

我们今天的话题就围绕针对过度电性应力(EOS)的冲击,如何有效的保护LED的方案之间的区别来展开。

EOS是Electrical Over Stress的缩写,指所有的过度电性应力。

EOS冲击的意思是电子元器件被施加的电流或者电压超过该元器件最大的设计规范要求时,该元器件便会发生性能减弱,甚至于直接损坏的现象。

LED器件很容易受到EOS的损伤,这种损坏有时能够直接击坏器件造成失效,而有时失效则可能在EOS发生一段时间后才发生。

电源输出质量的不稳定,各种过电压过电流的噪音,以及热插拔应用使用中的突入电流现象等都是能够产生EOS失效的诸多因素,这种EOS现象都属于短时间的过负荷,在短时间内(一般在一秒钟内)LED受到尖峰电压或者尖峰电流的冲击,这种电压或者电流的能量超过了LED的设计额定值,从而损伤LED器件。

简单介绍了LED的EOS问题后,我们来看看解决方案。

保护LED免受EOS损伤的防护方案基本都是将EOS产生的瞬态电压箝位在器件所能承受的范围内。

理论上消除这种瞬态电压最好的防护器件是电容,电容能很好的将瞬态电压吸收。

但是在实际应用中,由于电容的高温寿命和较大体积等因素,实在不是一种比较好的方案。

因此大多的工程师在解决该问题时往往偏向于使用TVS稳压管来进行保护,但是在选择TVS管的时候必须考虑到TVS管所能承受的最大功率,由。

漏电流的伏安特征曲线在分立器件失效分析中的应用

漏电流的伏安特征曲线在分立器件失效分析中的应用陈松;王友彬【摘要】针对半导体分立器件漏电流失效在后道封装工厂难以确定失效模式和失效机理的问题,引入漏电流的伏安特征曲线分析的方法,针对各种漏电流失效模式进行实验分析,利用漏电流特征曲线的方法将有可靠性风险的器件筛选出来.通过此方法在后道封装测试工厂大规模推广应用,大大提高了失效分析的效率和准确性,提升了产品质量,节约了成本,很好地达到了客户对产品质量和成本的期望.【期刊名称】《电子与封装》【年(卷),期】2018(018)011【总页数】4页(P44-47)【关键词】特征曲线;失效分析;缺陷【作者】陈松;王友彬【作者单位】英飞凌科技(无锡)有限公司,江苏无锡214028;英飞凌科技(无锡)有限公司,江苏无锡214028【正文语种】中文【中图分类】TN3061 引言传统的分立器件封装测试领域,经过多年发展,产量越来越高。

由于人们对汽车电子等涉及安全性领域的要求越来越高,对分立器件的质量要求也越发严苛,特别是针对测试过程中关键电参数失效的过程控制越发严格,对于电参数失效特别是漏电流失效的失效机理的确认,目前最有效的方法是做全面的失效分析(FA),然而全面的失效分析由于时间太长、成本太高而无法在生产过程控制中广泛应用,但没有最终的失效模式和失效机理的确认,产品质量的提高也将是句空话。

2 分立器件漏电流的失效模式和失效机理的确立通过对大量漏电流样本的失效分析得知,半导体后道封装测试中导致半导体分立器件漏电流失效的失效机理有以下几种。

(1)芯片制成过程中造成的失效,例如晶体缺陷(如图1所示为扫描电子显微镜SEM或者发射式电子显微镜EMMI下的晶体缺陷)造成局部漏电流过大,晶体缺陷不会造成器件可靠性风险。

(2)过度掺杂(图2所示为器件横截面图)是由于掺杂过程中离子过度扩散,基极宽度变窄,导致三极管击穿电压变小,漏电流变大。

过度掺杂不会造成器件可靠性风险。

(3)封装过程中造成的缺陷,例如金(铜)线的键合过应力造成的芯片表面弹坑、碎裂,破坏了芯片绝缘层(图3所示为光学显微镜下的键合缺陷)。

电子元器件电应力失效分析

电子元器件电应力失效分析【摘要】为了对电应力失效现象进行深层次的认识和理解,本文对电应力失效的现象特征、失效机理、检测方法和分析结论进行了总结,总结出了电应力的失效分析结论共有三类5种情况。

通过详细的分析对比,可以分析出电子器件电应力失效的根本原因及形成过程。

【关键词】静电损伤过电应力电迁移失效机理失效分析随着现代社会科技化程度的不断提高,电子器件的使用范围不断扩大,电子器件在我们的生活和工作中随处可见。

由于电子器件应用范围的广泛,电子器件的失效现象也是多种多样,随处可见。

电应力失效作为电子器件失效的重要方面,电气器件电应力失效的分析与研究,对电子器件的生产、使用和研发等具有深远的意义。

1 电应力的失效现象特征(1)电应力失效是指由于使用了超出或违背了器件规范规定的电压和电流的电应力,造成封装器件的失效。

电应力失效的主要表现形式有:ESD静电损伤、EOS 过电损伤、电迁移。

(2)静电(ESD)损伤的主要特征有:晶格熔化或金属与硅共熔,使P-N结受损短路;氧化层汽化产生空洞使器件短路、开路;金属联线挥发造成器件之间短路、开路。

过电应力(EOS)失效的主要特征:在失效分析的实践中,过电应力损伤还经常指有明显可见熔蚀痕迹的损伤,特别是封装材料有碳化现象:一般表现为键合丝熔断,造成开路;芯片表面金属布线熔融蒸发,造成开路、短路或漏电;硅材料熔融蒸发键合丝的熔断可以发生在任何管脚上。

(3)电迁移主要失效特征:银离子爬升呈树枝状晶或絮状晶,造成晶圆短路或漏电;当元器件工作时,金属互联线的铝条内有一定强度的电流通过,在电流的作用下,金属离子沿导体移动,产生质量的传输,导致到体内某些部位产生空洞或晶须(小丘),造成开路或漏电。

2 失效机理特征2.1 ESD(1)ESD产生的模式:1)人体模式:静电放电的人体模式(Human Body Model),简称HBM。

主要是人体静电放电对敏感电子器件产生的作用,导致封装器件的失效;2)机器模式:机器模式(Machine Model),简称MM。

FA process instruction (半导体器件失效分析)

表2、X射线透视技术和反射式扫描声学显微术(C-SAM)的 比较

名称

应用优势

X射线透视 以低密度区为背景, 技术(X-Ray) 观察材料的高密度区

的密度异常点(主要 用来判定引线断裂)

反射式扫描 以高密度区为背景, 声学显微术 观察材料内部空隙或 (C-SAM)低密度区(主要用来

1.7.1打开封装

机械开封(磨,撬,加热等方法) 主要针对金属封装的器件。

化学开封(磨,钻,发烟硝酸、发烟硫酸腐 蚀法等) 主要针对塑料封装的器件。

去除塑料封装机器(decapsulator)

1.7.2 去钝化层技术

1为什么要去除钝化层?

2去除钝化层的方法: 化学腐蚀(各向同性) 等离子腐蚀PIE (各向同性) 反应离子刻蚀RIE(各向异性)

一般步骤: 固定器件(石蜡、松香和环氧树脂Epoxy) 研磨(毛玻璃、粗砂纸) 粗抛光(金相砂纸) 细抛光(抛光垫加抛光膏) 染色 金相观察

测量结深的抛光染色图片

1.8显微形貌像技术

光学显微镜和扫描电子显微镜的比较

仪器名称 真空条件 样品要求 理论空间 最大放 景深 分辨率 大倍数

光学显微 无 镜

开封

360nm

1200 小

扫描电子 高真空 开封、去 5nm

显微镜

钝化层

50万 大

光学照片与SEM照片对比

1.9基于测量电压效应的失效定位技术

1.9.1、扫描电子显微镜的电压衬度像 工作原理 :电子束在处于工作状态下的被测芯片表

面扫描,仪器的二次电子探头接收到的电子数量与 芯片表面的电位分布有关。从而得到包含器件中电 极的电势信息的SEM图象(IFA Image-based Failure Analysis)。 判定内容:芯片的金属化层开路或短路失效。

EOS--电气过应力防护

EOS-电气过应力防护 晶科电子 APT Electronics Ltd. APT-PAK-AP03Rev. 1.0目录1. 应用说明 (2)2. 什么是电气过应力(EOS) (2)3. 产生电气过应力(EOS)的原因 (2)1) 静电放电 (ESD) 事件 (2)2) LED 过驱动(持续过电压/过电流事件) (3)3) 瞬态过电流事件 (3)4. 电气过应力(EOS)对APT LED 的影响 (4)1) 接合线熔断、材料烧毁 (4)2) 芯片/齐纳烧毁或是击穿 (5)5. 如何防护电气过应力(EOS) (6)1) 防护器件的类别 (6)2) 静电(ESD )防护 (7)3) 过电压保护 (9)4) 过电流防护 (10)5) 瞬态过电流防护 (浪涌防护) (10)6) LED 驱动电源设计技术 (11)6. 结论 (13)1.应用说明本文主要说明电气过应力(EOS)事件、产生的原因及其对APT LED的影响,以及使用APT LED光源时避免电气过应力的相关措施。

2.什么是电气过应力(EOS)EOS为Electrical Over Stress的缩写,简单而言,电气过应力就是LED上施加的电流超过该LED datasheet中规定的最大电流。

这与EOS事件的次数或持续时间长短无关,因为任何一次EOS事件都可能导致LED损坏。

这种损坏可以表现为LED器件立即失效(接合线熔断、芯片/齐纳击穿、烧毁等),也可能在发生EOS事件后许久后才失效。

3.产生电气过应力(EOS)的原因1)静电放电(ESD) 事件静电实际是由电荷累积构成。

人们在日常生活中,特别是在干燥天气环境中,当用手去触摸门窗类物品时会感觉“触电”,这就是门窗物品静电积累到一定程度时对人体的“放电”。

对羊毛织品、尼龙化纤物品,静电积累的电压可高达一万多伏特,电压十分高,但静电功率不大,不会威胁生命,然而对于某些电子器件却可以致命,造成器件失效。

eos电应力,过电流过电压

EOS电应力和过电流过电压是电力系统中常见的两种问题。

EOS电应力,即电涌应力,是指电力系统中瞬间出现的高电压和大电流现象。

这种现象通常由于雷击、开关操作、短路故障等引起。

EOS电应力会对电力设备造成损坏,降低系统的可靠性。

过电流过电压则是电力系统中电流或电压超过额定值的现象。

过电流通常由于短路、过载等引起,而过电压则可能由于电力系统的参数变化、设备故障、雷击等引起。

过电流过电压会对电力设备的安全运行构成威胁,严重时可能导致设备损坏和系统故障。

为了解决这些问题,通常需要采取相应的防护措施,如安装避雷器、熔断器、过电压保护器等设备,以确保电力系统的稳定运行。

同时,加强设备的维护和检测,及时发现和排除潜在的隐患,也是预防这些问题的有效手段。

静电放电与防护基础知识

简介电子设备抗ESD保护基本方法

1. 2. 3. 4. 5. 6. 介质隔离技术 屏蔽技术 电气隔离技术 使用ESD泄放电路 外接ESD保护器件 合理的PCB板布局布线

外接ESD保护电路和器件 (TVS的特性和使用)

•

1. TVS二极管在线路板上是与被保护线路并联 2. 当瞬时电压超过电路正常工作电压后,TVS 管便发生雪崩,提供给瞬时电流一个超低电 组通路,使瞬时电流通过二极管被引开,避 开被保护器件,并且在电压恢复正常值之前 被保护回路一直保持截止电压 3. 当瞬时脉冲结束以后,TVS二极管自动回复 高阻抗状态,整个回路进入正常电压 --- TVS管的特点:反应迅速、截止电压比较低, 另外对TVS管设计的改进使其更低的漏电流 和结电容

抗esd电磁脉冲干扰得设计规则其他设计规则避免在pcb边缘安排重复的信号线如时钟和复位信号等将pcb上未使用的部分设置为接地面尽量将接口安排在同一个边上避免被保护回路和未实施保护的回路并联将接口信号线接地线路直接接到保护器件上然后再进入回路的其他部分用tvs二极管来保护所有的外部连接采用高集成度器件可节约线路板上空间而且减少由于回路复杂诱发的寄生性线路自感的影响混凝土衬砌渠道具有防渗抗冲效果好输水能力大经久耐用便于管理等特点

静电放电失效

2. 潜在性失效:是指静电放电能量较低, 仅在元器件内部造成轻微损伤,放电 后器件电参数仍然合格或略有变化 对器件使用可靠性的影响 ---器件的抗过电应力能力减弱 ---使用寿命明显缩短 在受到工作应力或经过一段时间工作 后将进一步退化,直至造成彻底失效

TVS二极管的工作原理

抗ESD电磁脉冲干扰得设计规则

1. 减小环路 ---电流通过感应进入电路环路,这些环 路是封闭的,具有变化的磁通量,电 流的幅度与环的面积成正比,环路大 磁通量多,因而在电路中感应出较强 的电流,必须减小环路面积

EOS 电气过应力

EOS和ESD一、什么是EOS?EOS为Electrical Over Stress的缩写,指所有的过度电性应力。

当外界电流或电压超过器件的最大规范条件时,器件性能会减弱甚至损坏。

EOS通常产生于1.电源(AC/DC) 干扰、电源杂讯和过电压。

2.由于测试程式切换(热切换)导致的瞬变电流/峰值/低频干扰。

其过程持续时间可能是几微秒到几秒(也可能是几纳秒),很短的EOS 脉冲导致的损坏与ESD损坏相似。

3.闪电。

4.测试程式开关引起的瞬态/毛刺/短时脉冲波形干扰。

5.测试设计欠佳,例如,在器件尚未加电或已超过其操作上限的情况下给器件发送测试信号。

再比如在对器件供电之前加入测试信号,或超过最大操作条件。

6.来自其他设备的脉冲信号干扰,即从其他装置发送的脉冲。

7.不恰当的工作步骤,工作流程不甚合理8.接地点反跳(由于接地点不够导致电流快速转换引起高电压)二、什麼是ESD?ESD是英文Electrical Static Discharge的缩小,中文释为静电放电。

电荷从一个物体转移到另一个物体。

静电是一种客观的自然现象,产生的方式多种,如接触、摩擦等。

静电的特点是高电压、低电量、小电流和作用时间短的特点。

人体自身的动作或与其他物体的接触,分离,摩擦或感应等因素,可以产生几千伏甚至上万伏的静电。

静电在多个领域造成严重危害。

摩擦起电和人体静电是电子工业中的两大危害。

生产过程中静电防护的主要措施为静电洩露、耗散、中和、增湿,遮罩与接地。

人体静电防护系统主要有防静电手腕带,脚腕带,工作服、鞋袜、帽、手套或指套等组成,具有静电洩露,中和与遮罩等功能。

静电防护工作是一项长期的系统工程,任何环节的失误或疏漏,都将导致静电防护工作的失败。

三、对比区别四、静电防护1.设定静电区域说明:在生产现场设定静电敏感区域,并且要做明显警示,使到现场的每个人都能注意。

2、静电区域内注意事项a.操作者应该佩戴防静电腕带,应该穿着防静电服装,鞋,围巾,椅子应该套防静电套。

电过应力EOS

微电子器件的可靠性

复旦大学材料科学系

4

微电子器件的功率阈值

1。 器件的温度达到半导体材料的本征激发温度

时,半导体材料发生本征激发,载流子数量激 增,器件失去它的正常性能。 2。温度达到金属化铝的熔点时会引起铝膜的熔 化、断裂 。 3。为保持微电子器件的性能正常,器件的温度 有它的极限,从功率来说,就有它的功率阈值。

失效原因

IC设计,制造,装配 EOS ESD阈 EOS\ESD

占百分率%

25 46 6 5

重测合格

17

微电子器件的可靠性

复旦大学材料科学系

3

电过应力失效的类别

过热引起的烧毁、 晶体管的二次击穿(Second Breakdown SB) CMOS的闩锁效应(Latch-up) 静电放电(Electeo-Static Dicharge)

微电子器件的可靠性 复旦大学材料科学系 20

二次击穿的机理

正偏二次击穿: 热不稳定性模型 反偏二次击穿 基区夹紧效应

微电子器件的可靠性

复旦大学材料科学系

21

NMOS 的二次击穿

NMOS 的二次击穿 是一种寄生三极管效应 。

微电子器件的可靠性

复旦大学材料科学系

22

安全工作区

考虑了晶体管的最大工 作电流、最大耗散功率, 击穿电压和二次击穿 后, 器件的工作区域 定义为 安全工作区。 安全工作区的等功率线 和二次击穿线的位置 是与工作脉冲宽度有 关的 函数。

微电子器件的可靠性

复旦大学材料科学系

18

二次击穿

二次击穿分为: 正偏二次击穿 负偏二次击穿。

微电子器件的可靠性

复旦大学材料科学系

19

二次击穿的过程

浅谈EOS机理与防护

浅谈EOS机理与防护EOS英文全称Electrical Over Stress,是对所有的过度电性应力的总称。

当EOS超过其最大指定极限后,器件功能会减弱或损坏,同时EOS也是公认的IC器件的头号杀手。

由于它可能发生在产品的研发、测试乃至生产、存储、运输的各个环节,所以对厂商的电路设计,测试规范,生产流程以及物流中防护都有严格具体的要求,每年耗费整个半导体行业数十亿美金的资金。

更可恨的是,EOS的发生情况复杂,神出鬼没,寻求一个完美的解决方案至今困扰着学术界和工业界。

此文旨在分析EOS的成因,特点,破坏力,以及对于芯片厂商和系统设计人员的启示。

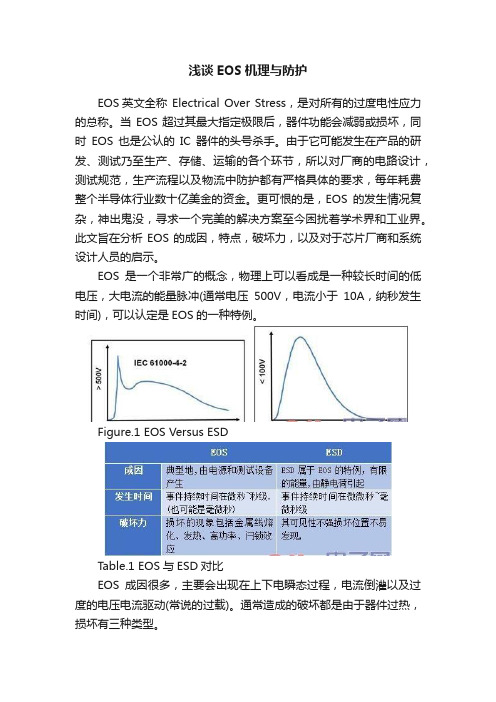

EOS是一个非常广的概念,物理上可以看成是一种较长时间的低电压,大电流的能量脉冲(通常电压500V,电流小于10A,纳秒发生时间),可以认定是EOS的一种特例。

Figure.1 EOS Versus ESDTable.1 EOS与ESD对比EOS成因很多,主要会出现在上下电瞬态过程,电流倒灌以及过度的电压电流驱动(常说的过载)。

通常造成的破坏都是由于器件过热,损坏有三种类型。

Figure.2 PN节击穿Figure.3 金属层熔断Figure.4 金属打线熔断鉴于EOS的成因和特点,成熟的系统厂商通常采用如下的防护方式。

建立和规范工作流程,进行常规的交流电源线监控。

电源√ 确保交流电源配备了瞬态电流抑制器(滤波器)√ 电源过压保护√ 交流电源稳压器(可选)。

√ 电源时序控制器,可调整时序√ 不共用滤波器和稳压器工作流程√ 将正确流程存档。

√ 确保针对以下内容进行培训并给出警示标志电源开/关顺序√ 不可“热插拔”√ 正确的插入方向√ 定期检查以确保遵守相关规定维护√ 定期进行预防性维护。

√ 确保接头良好紧固,以防止其带来间歇性故障。

培训√ 确保对所有人员进行培训并及时复习相关内容。

电路板或元件测试√ 确保不进行热切换。

进行测试时使用存储范围捕获信号或电源的瞬态电流。

MOS管静电击穿失效与防御

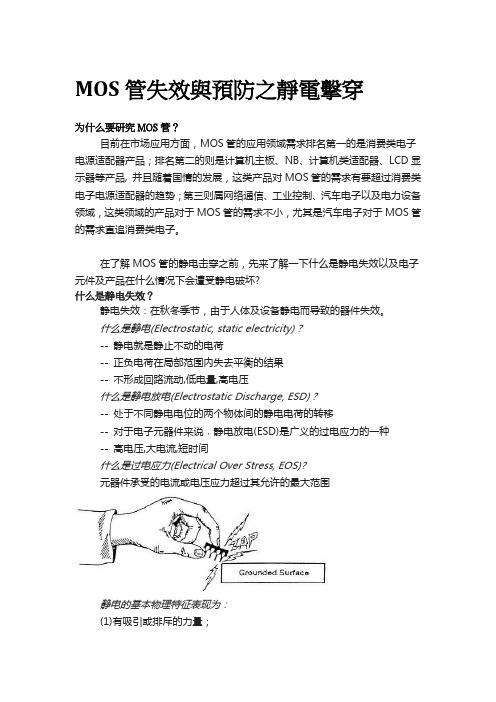

MOS管失效與預防之靜電擊穿为什么要研究MOS管?目前在市场应用方面,MOS管的应用领域需求排名第一的是消费类电子电源适配器产品;排名第二的则是计算机主板、NB、计算机类适配器、LCD显示器等产品, 并且随着国情的发展,这类产品对MOS管的需求有要超过消费类电子电源适配器的趋势;第三则属网络通信、工业控制、汽车电子以及电力设备领域,这类领域的产品对于MOS管的需求不小,尤其是汽车电子对于MOS管的需求直追消费类电子。

在了解MOS管的静电击穿之前,先来了解一下什么是静电失效以及电子元件及产品在什么情况下会遭受静电破坏?什么是静电失效?静电失效:在秋冬季节,由于人体及设备静电而导致的器件失效。

什么是静电(Electrostatic, static electricity)?-- 静电就是静止不动的电荷-- 正负电荷在局部范围内失去平衡的结果-- 不形成回路流动,低电量,高电压什么是静电放电(Electrostatic Discharge, ESD)?-- 处于不同静电电位的两个物体间的静电电荷的转移-- 对于电子元器件来说﹐静电放电(ESD)是广义的过电应力的一种-- 高电压,大电流,短时间什么是过电应力(Electrical Over Stress, EOS)?元器件承受的电流或电压应力超过其允许的最大范围静电的基本物理特征表现为:(1)有吸引或排斥的力量;(2)有电场存在,与大地有电位差;(3)会产生放电电流。

这三种情形即ESD一般会对电子元件造成以下三种情形的影响:(1)元件吸附灰尘,改变线路间的阻抗,影响元件的功能和寿命;(2)因电场或电流破坏元件绝缘层和导体,使元件不能工作(完全破坏);(3)因瞬间的电场软击穿或电流产生过热,使元件受伤,虽然仍能工作,但是寿命受损。

电子元件及产品在什么情况下会遭受静电破坏?MOS管为什么会被静电击穿?MOS管本身属于ESD敏感器件,它本身的输入电阻很高,而栅-源极间电容又非常小,所以极易受外界电磁场或静电的感应而带电,又因在静电较强的场合难于泄放电荷,容易引起静电击穿。

esd器件为过电应力烧蚀失效

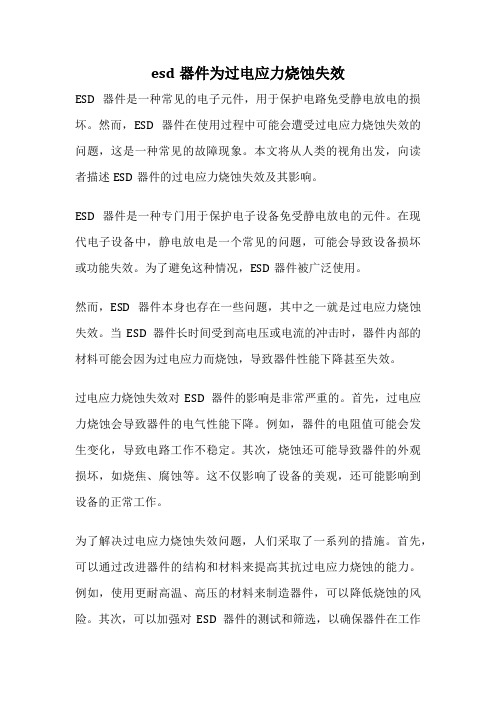

esd器件为过电应力烧蚀失效ESD器件是一种常见的电子元件,用于保护电路免受静电放电的损坏。

然而,ESD器件在使用过程中可能会遭受过电应力烧蚀失效的问题,这是一种常见的故障现象。

本文将从人类的视角出发,向读者描述ESD器件的过电应力烧蚀失效及其影响。

ESD器件是一种专门用于保护电子设备免受静电放电的元件。

在现代电子设备中,静电放电是一个常见的问题,可能会导致设备损坏或功能失效。

为了避免这种情况,ESD器件被广泛使用。

然而,ESD器件本身也存在一些问题,其中之一就是过电应力烧蚀失效。

当ESD器件长时间受到高电压或电流的冲击时,器件内部的材料可能会因为过电应力而烧蚀,导致器件性能下降甚至失效。

过电应力烧蚀失效对ESD器件的影响是非常严重的。

首先,过电应力烧蚀会导致器件的电气性能下降。

例如,器件的电阻值可能会发生变化,导致电路工作不稳定。

其次,烧蚀还可能导致器件的外观损坏,如烧焦、腐蚀等。

这不仅影响了设备的美观,还可能影响到设备的正常工作。

为了解决过电应力烧蚀失效问题,人们采取了一系列的措施。

首先,可以通过改进器件的结构和材料来提高其抗过电应力烧蚀的能力。

例如,使用更耐高温、高压的材料来制造器件,可以降低烧蚀的风险。

其次,可以加强对ESD器件的测试和筛选,以确保器件在工作条件下的稳定性和可靠性。

此外,人们还可以采取外部保护措施,如使用ESD保护电路、地线等,来降低过电应力对器件的影响。

ESD器件的过电应力烧蚀失效是一个需要重视的问题。

它可能导致器件性能下降甚至失效,影响设备的正常工作。

为了解决这个问题,人们需要通过改进器件结构和材料、加强测试筛选以及采取外部保护措施等手段来提高器件的抗过电应力烧蚀能力。

只有这样,才能确保ESD器件在电子设备中的可靠性和稳定性。

ESD与EOS防范资料

ESD 静电防护一、静电线应包括两条:1.ESD Line:与厂内地梉相连。

2.AC Ground Line:与电源地线相连且必须以夹具相接,禁止使用缠绕方式相接。

二、静电接地检验主要包括以下四个方面:1.地梉接地性能测试.2. ESD线量测。

3.各种设备保护接地测试,其包括两部份:a.带电设备:包括锡炉、ICT、UV机、Laser机、电动起子、焊烙铁、流水线、PCB测试治具、计算机、RS232box等设备接地状况的测量,该种设备外壳须接AC ground line。

b.不带电设备:包括IC架、插Membrane治具等设备接地状况的测量,该种设备外壳须接ESD line。

4.静电环的测量。

三、地梉接地性能测量1.测量仪器:地阻仪。

2.测量方法:将地阻仪一接线接地梉(线长为5m),另两导线沿不同方向(两方向夹角一般为90度)选择两测量点(两导线长度分别为30m和20m),测量值应小于2奥姆。

四、ESD线测量程序1.测量方法:用万用表量测ESD line与AC ground line之间阻抗,测量值应大于1.2G奥姆。

2.测量频率:每4小时测量一次并作记录。

3.不良处理对策:测量值如超过规定范围,需停线检查原因,待阻值至规格内方开线生产。

五、设备保护接地测量程序1.测量方法:用万用表量测各设备外壳与AC ground line之间阻抗,测量值应小于10奥姆。

2.测量频率:IPQC每日抽检.3.不良处理对策:测量值如超过规定范围,需停线检查原因,待阻值降至规格之内方可开线生产。

4.输送带接地线每两个月由IPQC会同工程师检查大地接地状况并作记录。

六、设备漏电压测量程序1.测量方法:用万用表量测各设备外壳与AC ground line之间电位差,标准为测量值小于2V.2.测量频率:IPQC每日抽检。

3.不良处理对策:测量值如超过规定范围,需停线检查原因,待电位差降至规格之内方可开线生产。

七、静电环的配戴和测量1. 正确的作业方式如下:a.将静电手环套在手腕上,手环内圈的金属部分必须直接接触手腕皮肤。

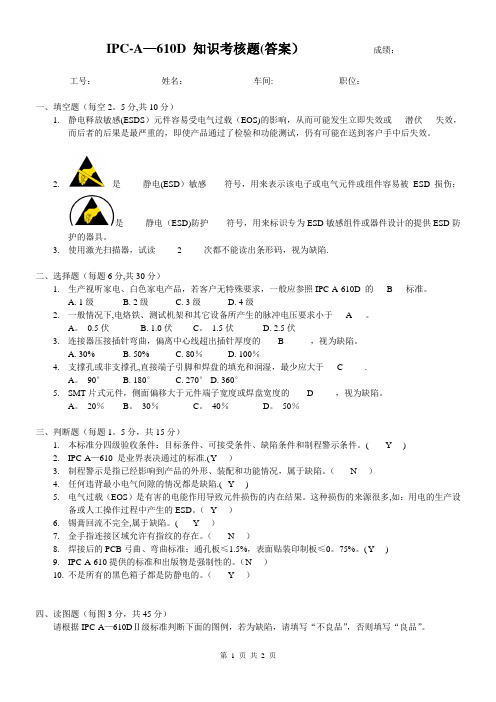

IPC-A-610D 知识考核题(答案)

IPC-A—610D 知识考核题(答案)成绩:______________ 工号:______________ 姓名:______________ 车间:______________ 职位:______________一、填空题(每空2。

5分,共10分)1.静电释放敏感(ESDS)元件容易受电气过载(EOS)的影响,从而可能发生立即失效或___潜伏___失效,而后者的后果是最严重的,即使产品通过了检验和功能测试,仍有可能在送到客户手中后失效。

2.是_____静电(ESD)敏感____符号,用来表示该电子或电气元件或组件容易被ESD损伤;是_____静电(ESD)防护____符号,用来标识专为ESD敏感组件或器件设计的提供ESD防护的器具。

3.使用激光扫描器,试读_____2_____次都不能读出条形码,视为缺陷.二、选择题(每题6分,共30分)1.生产视听家电、白色家电产品,若客户无特殊要求,一般应参照IPC-A-610D 的___B___标准。

A. 1级B. 2级C. 3级D. 4级2.一般情况下,电烙铁、测试机架和其它设备所产生的脉冲电压要求小于___A___。

A。

0.5伏 B. 1.0伏C。

1.5伏 D. 2.5伏3.连接器压接插针弯曲,偏离中心线超出插针厚度的____B______,视为缺陷。

A. 30%B. 50%C. 80%D. 100%4.支撑孔或非支撑孔,直接端子引脚和焊盘的填充和润湿,最少应大于___C_____.A。

90° B. 180° C. 270° D. 360°5.SMT片式元件,侧面偏移大于元件端子宽度或焊盘宽度的____D_____,视为缺陷。

A。

20%B。

30%C。

40%D。

50%三、判断题(每题1。

5分,共15分)1.本标准分四级验收条件:目标条件、可接受条件、缺陷条件和制程警示条件。

( Y )2.IPC-A—610 是业界表决通过的标准.( Y)3.制程警示是指已经影响到产品的外形、装配和功能情况,属于缺陷。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

输入引脚的过电应力(EOS)保护

芯片设计者在将一个运放的敏感引脚引出芯片的时候,会关心这个引脚将被如何对待。

用户会认真处理这个引脚吗?还是只是粗心的把这个引脚直接和交流电连接起来?我们都希望设计出强健的产品,可以应对用户的极端的使用。

那么,如何在设计中防止过电应力造成的产品失效呢?

OPA320是大多数典型运放的一种,其最大额定参数表,它描述了芯片最大允许供电电压、引脚最大允许输入电压和电流。

根据参数表的附加说明,如果限制引脚输入电流,那么就不需要限制输入电压。

内部钳位二极管允许±10mA的输入电流。

但是在输入电压超出正常值很多的情况下,限制输入电流需要较大的输入阻抗,这会增加噪声,降低带宽,同时还可能产生其它错误。

钳位二极管在输入电压超过电源轨大约0.6V时开始导通。

通常,许多设备可以承受较大电流,但是当电压急剧增加时,设备失效的概率就会增加。

通过添加外部二极管可以大大提高设备耐受大电流的能力,同时也可以提高设备的防护等级。

市场上常见的传输信号的二极管,比如无处不在的1N4148,具有非常低的导通压降(实验室测试显示,其至少比运放内部二极管低100mV)。

在与运放内部二极管并联后,当遇到输入过流时,大多数电流将流向外部的二极管。

肖特基二极管具有更低的导通电压,这种特性可以提升保护性能。

但缺点也很明显,它的漏电流太大了。

室温下,它的反向漏电流通常是微安级或者更大,同时,随着温度的升高而增加。

另外,你还需要一个足够强健的电源。

钳位二极管,无论是运放内部或者外部的,都需要一个相对稳定的电源来释放能量。

如果故障脉冲很大,灌入电源轨过多的电流,提高(或拉低负电源)电源电压,那么脉冲会使电源端承受过大的电压应力,。

典型的线性电源不能吸收电流,因此不要指望使用它做为电源有多稳定。

大的旁路电容可以用来吸收大的故障脉冲电流。

对于连续的故障电流,可以在输入引脚和电源上加用齐纳二极管来解决。

齐纳二极管的反向击穿电压要刚好高于系统最大供电电压,这样仅仅在故障时,齐纳二极管才会被导通。

对于正负供电系统,需要在两个电源轨分别设计相同的保护电路。

尽管采取了这些措施,引脚输入电压仍可能超过最大额定参数表中的值,但问题的关键在于:最大额定参数表中的值通常过于保守;在这个电压或者电流下芯片损坏几乎是不可能的。

一般来说,大幅超过这些参数,器件也不太可能损坏(但不保证)。

钳位到比最大额定参数表中的值高几伏的电压,同时获得较低的失效率是很容易的。

在许多情况下,设计的目标是在成本和性能折中的情况下降低失效率。

没有哪一种方案可以应对所有的情况,也没有一种保护电路可以同时满足所有需求。

在不同应用中,保护电路方案差别很大。

不同运放的灵敏度不同,所需保护等级也存在很大差异。

这可能会需要你有一定创造力,最好自己做自己的专家。

虽然在极端的环境中做一些测试会损失一些运放,但这是必要的。

同时,也一如既往的欢迎你访问我们的E2E论坛来寻求一些建议。

当然,也欢迎你通过评论分享一些有用的技巧。