pcb走线时延估算方法.doc

pcb线路增益计算方法

pcb线路增益计算方法(实用版)目录1.PCB 线路增益计算的概述2.PCB 线路增益的计算方法3.PCB 线路增益的实际应用4.PCB 线路增益计算的注意事项正文一、PCB 线路增益计算的概述在印刷电路板(PCB)设计中,线路增益计算是一个关键环节。

线路增益指的是信号在通过线路时所获得的放大或衰减程度,通常以分贝(dB)表示。

对于不同类型的 PCB 线路,增益计算方法也有所不同。

本文主要介绍一种常见的 PCB 线路增益计算方法,即 50 欧姆传输线增益计算方法。

二、PCB 线路增益的计算方法1.50 欧姆传输线增益计算方法50 欧姆传输线是 PCB 设计中最常见的传输线类型,广泛应用于信号传输、放大和衰减等场景。

50 欧姆传输线增益计算公式如下:增益(dB)= 10 × log10 ( (A2 / A1) × (B1 / B2) )其中,A1 和 A2 分别为传输线输入端和输出端的电压幅值;B1 和B2 分别为传输线输入端和输出端的电流幅值。

2.实际应用中的增益计算在实际 PCB 设计中,为了获得所需的增益,需要根据线路的特性阻抗、传输线长度、信号频率等因素进行综合考虑。

此外,还需要考虑传输线的损耗、信号源和负载的阻抗匹配等因素,以确保信号传输的稳定性和可靠性。

三、PCB 线路增益的实际应用PCB 线路增益在实际应用中具有广泛的应用,如信号放大、衰减、滤波等。

通过合理地设计线路增益,可以实现信号的精确传输和处理,提高系统的性能和稳定性。

四、PCB 线路增益计算的注意事项在进行 PCB 线路增益计算时,需要注意以下几点:1.确保传输线的稳定性,避免信号反射、串扰等问题;2.考虑传输线的损耗,如电阻损耗、电感损耗等;3.注意信号源和负载的阻抗匹配,以确保信号传输的效率;4.根据实际应用场景选择合适的增益计算方法。

综上所述,PCB 线路增益计算是 PCB 设计中一个重要环节。

PCB设计的走线技巧

PCB设计的走线技巧PCB 走线技巧推荐布线(Layout)是PCB设计工程师最基本的工作技能之一。

走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中是至关重要的。

下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。

主要从直角走线,差分走线,蛇形线等三个方面来阐述。

1.直角走线直角走线一般是PCB布线中要求尽量避免的情况,也几乎成为衡量布线好坏的标准之一,那么直角走线究竟会对信号传输产生多大的影响呢?从原理上说,直角走线会使传输线的线宽发生变化,造成阻抗的不连续。

其实不光是直角走线,顿角,锐角走线都可能会造成阻抗变化的情况。

直角走线的对信号的影响就是主要体现在三个方面:一是拐角可以等效为传输线上的容性负载,减缓上升时间;二是阻抗不连续会造成信号的反射;三是直角尖端产生的EMI。

传输线的直角带来的寄生电容可以由下面这个经验公式来计算:C=61W(Er)1/2/Z0在上式中,C就是指拐角的等效电容(单位:pF),W指走线的宽度(单位:inch),εr指介质的介电常数,Z0就是传输线的特征阻抗。

举个例子,对于一个4Mils的50欧姆传输线(εr为4.3)来说,一个直角带来的电容量大概为0.0101pF,进而可以估算由此引起的上升时间变化量:T10-90%=2.2*C*Z0/2 = 2.2*0.0101*50/2 = 0.556ps通过计算可以看出,直角走线带来的电容效应是极其微小的。

由于直角走线的线宽增加,该处的阻抗将减小,于是会产生一定的信号反射现象,我们可以根据传输线章节中提到的阻抗计算公式来算出线宽增加后的等效阻抗,然后根据经验公式计算反射系数:ρ=(Zs-Z0)/(Zs+Z0),一般直角走线导致的阻抗变化在7%-20%之间,因而反射系数最大为0.1左右。

而且,从下图可以看到,在W/2线长的时间内传输线阻抗变化到最小,再经过W/2时间又恢复到正常的阻抗,整个发生阻抗变化的时间极短,往往在10ps之内,这样快而且微小的变化对一般的信号传输来说几乎是可以忽略的。

高速PCB设计中的信号完整性和传输延时分析

第19卷 第2期 天 中 学 刊 Vol .19 No .22004年4月 Journal of Tianzhong Apr .2004收稿日期:2004-02-10作者简介:冯志宇(1972− ),男,河南正阳人,电子科技大学电子工程学院信号与信息处理专业硕士研究生.高速PCB 设计中的信号完整性和传输延时分析冯志宇(电子科技大学,四川 成都 610054)摘 要:信号完整性问题及由传输延时引起的时序问题是高速PCB 设计中的主要问题,借助功能强大的Cadence/SpecctraQuest 仿真软件,对高速信号线进行布局布线前仿真,可以发现和解决这些问题,从而缩短设计周期.关键词:信号完整性;时序;仿真 随着IC 工艺的提高,驱动器的上升沿和下降沿越来越陡,由原来的十几ns 提高到几ns ,有的甚至达到几ps ,同时电子系统的时钟频率也在不断提高.对于低频电路设计而言,器件管脚间的逻辑连接可以看成是简单的线迹互联.但对频率超过50 MHz 的高频电路,互连关系必须按传输线考虑,由此产生的信号完整性问题及时序问题成为高速PCB 设计中的主要问题.借助功能强大的Cadence/SpecctraQuest 仿真软件对高速信号线进行布局布线前仿真,可以发现和解决这些问题,从而缩短设计周期.1 高速移动接入系统的信号完整性问题信号完整性(Signal Integrity )简称SI ,是指信号在信号线上的传输质量,主要包括反射、振荡、地弹、串扰等性能参数.信号具有良好的信号完整性是指当在需要的时候,具有所必需达到的电压电平数值.信号完整性是由板级设计中多种因素共同决定的.图1所示是我们所设计的高速移动接入系统,其中虚线框中为该系统高速数据通路的中频和基带部分.A/D 部分通过采样、量化、编码将模拟中频信号转换成数字中频信号,然后利用DDC 部分对其进行混频(解调)、抽取、滤波,将中频带通信号混频成基带信号;DSP 模块负责完成基带信号的调制/解调、数据交织/解交织、数据编码/解码、数据纠错和检验、数据加密/解密、语音压缩/解压缩等;图1 高速移动接入系统框图DUC 和D/A 部分则是DDC 和A/D 部分的逆过程.该系统的中频部分既有频率较高的数字信号又有敏感度很高的模拟信号,基频部分DSP 与SDRAM 之间的数据交换速率高达100 Mb/s ,由此产生的信号完整性及时序问题十分突出.在高速PCB 设计中,信号完整性问题是系统能否正常工作的关键因素之一.因此,有必要在布线前利用仿真软件对该高速系统进行关键信号线的仿真.当信号完整性满足要求后就可以进行时序分析中图分类号:TN405.97文献标识码:A文章编号:1006-5261(2004)02-0018-04了,否则还需调整布局,重新仿真.图2、图3、图4分别是用Cadence/SpecctraQuest 仿真软件得到的该系统中SDRAM 的时钟(SDCLK )、数据写和数据读信号的仿真波形,可以看出这3个典型信号都能够满足波形完整性的要求.2 高速移动接入系统中的时序关系2.1 系统时序分析对于异步时序电路,往往可以灵活地设置建立、选通和保持时间,以满足系统时序要求.而同步时序电路必须从设计上留有充足的建立和保持时间,才能保证系统正常工作.高速移动接入系统中,DSP 与SDRAM 互连的关键信号线有时钟线SDCLK 、数据线D 47∼16和地址线ADDR 23∼0.由于系统工作频率高达100 MHz ,故这些信号线的互连延时是不可忽略的,它对信号的建立和保持时间起着至关重要的作用.仿真应该着重解决这些线网的拓扑问题.布线延时与布线迹的阻抗及布线长度有关,高阻抗线迹能够减少信号的跳变时间.其他因素如驱动特性和负载特性也会影响布线延时.下面在考虑布线延时的基础上,推导DSP 与SDRAM 互连的高速信号线间的时序约束关系.二者间互连的高速信号线时序及延时关系如图5所示.其中,P Clock ,T 表示时钟周期,D Clock ,t 表示时钟布线延时,D(max)Data ,t 和D(min)Data ,t 分别表示数据传输的最长延时和最短延时,isu(DSP)t ,ih(DSP)t 和oh(DSP)t 分别表示DSP 的输入建立时间、输入保持时间和输出保持时间,isu(SDRAM)t ,ih(SDRAM)t 和oh(SDRAM)t 分别表示SDRAM 的输入建立时间、输入保持时间和输出保持时间.(a) SDCLK(out from DSP),(b) SDCLK(into SDRAM), (c) Data(out from SDRAM),(d) Data(into DSP), (e) Data(out from DSP),(f) Data(into SDRAM)图5 高速信号线时序及延时关系读建立时间应满足 isu(DSP)ACC D(max)Data D Clock P Clock t t t t T ≥,,,−−−, (1) 读保持时间应满足 ih(DSP)(min)D Data D Clock oh(SDRAM)t t t t ≥,,++,(2)写建立时间应满足DDATO (max)D Data D Clock P Clock t t t T −−+,,,isu(SDRAM)t ≥,(3) 写保持时间应满足 ih(SDRAM)D Clock (min)D Data oh(DSP)t t t t ≥,,−+,(4)由(1)式,可得 (max)D Data isu(DSP)ACC D Clock P Clock ,,,≥t t t t T −−−, (5) 由(4)式,可得(min)D Data D Clock oh(DSP)ih(SDRAM),,≤t t t t +−, (6)由(5),(6)式,可得isu(DSP)ACC D Clock P Clock t t t T −−−,,D Clock oh(DSP)ih(SDRAM),≥t t t +−,图2 时钟信号的仿真波形图3 数据写信号的仿真波形图4 数据读信号的仿真波形)a ()b ()c ()d ()e ()f (进而有+−2)(ACC P Clock D Clock t T t ,,≤2)(isu(DSP)oh(DSP)ih(SDRAM)t t t −+−.(7)由(2),(3)式,可推导出 +−2)(oh(SDRAM)ih(DSP)D Clock t t t ≥,2)(P Clock isu(SDRAM)DDATO ,T t t −+,(8)由(7),(8)式,可推导出+−−−++−2)(2)()ih(SDRAM ACC P Clock D Clock P Clock isu(SDRAM)DDATO oh(SDRAM)ih(DSP)t t T t T t t t t ,,,≤≤.2)(isu(DSP)oh(DSP)t t −(9)可见,时钟线迹的延时必须在一定范围内波动,才能满足DSP 与SDRAM 间数据交换的时序要求,不能太长也不能太短.较短的延时可以增加读建立时间,却缩短了读保持时间.另外,一旦时钟线迹的延时确定(即时钟走线确定),则数据线的延时必须同时满足读写的时序要求,才能保证正确的读写. 2.2 时序关系在本系统中的应用该系统设计中DSP 采用ADI 公司的ADSP21161芯片,SDRAM 采用MICRON 公司的MT48LC4M16B2-75芯片.DSP 与SDRAM 间的数据交换速率可达100 MHz b/s ,是PCB 设计关注的重点.为保证系统能正常、可靠和稳定地工作,必需进行布线前时序仿真.MT48LC4M16B2-75芯片和ADSP21161芯片的参数如下:ns 8.2isu(DSP)=t ,ns 0.3ih(DSP)=t ,ns 2.1oh(DSP)=t ,ns 5.1isu(SDRAM)=t ,ns 8.0ih(SDRAM)=t ,ns 2.2oh(SDRAM)=t ,ns 10P Clock =,t ,ns 3.7ACC =t ,ns 5.7DDATO =t .将上述参数代入(9)式可得ns 8.0ns 0D Clock ≤≤,t .根据实际布局情况取ns 5.0D Clock =,t ,则由不等式(1)∼(4)得ns 7.0ns 3.0D Data ≤≤,t .任取D16-47中的一根数据线D35,分别取ns 7.0ns 5.0ns 3.0D Clock ,,,=t 做读写扫描仿真,结果如图6所示.其中(a),(c),(e)分别为ns 7.0ns 5.0ns 3.0D Clock ,,,=t 时数据线D35的读波形,(b),(d),(f)分别为ns 7.0ns 5.0ns 3.0D Clock ,,,=t 时数据线D35的写波形.可见在ns 7.0ns 3.0D Data <<,t 范围内数据的读写波形符合完整性要求.把ns 7.0ns 3.0D Data ≤≤,t 作为D40的布线拓扑规则加到Dd16-47进行规则驱动下的布线,布线后D16-47的延时见图7,由图7可知,ns 3282.0D(min)Data =,t ,ns 6090.0D(max)Data =,t ,能够满足ns 7.0ns 3.0D Data ≤≤,t 的要求.制板后用示波器观察到的数据线D35的读波形如图8所示. 图7 布线后数据线的传输延时分析图片图6 数据线D35的仿真波形(b)(a)(c)(d)(e)(f) 图8 制板后用示波器观察到的数据线D35的读波形信号完整性问题和由布线延时引起的时序问题,是高速系统板级实现需要着重解决的问题,利用Cadence/SpecctraQuest仿真软件进行板前和板后仿真,是解决这些问题的有效方法.参考文献: [1] 杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2002.100∼159.[2] 曾峰,侯亚宁,曾凡雨.印制电路板(PCB)设计与制作[M].北京:电子工业出版社,2002.85∼107.[3] Johnson H W.High-Speed Digital Design[M].PrenticeHall PTR,1993.97∼121. 〔责任编辑 张继金〕 Analysis of Signal Integrity and Propagation Delayin High-Speed PCB DesignFENG Zhi-yu(University of Electronic Science and Technology of China, Chengdu Sichuan 610054, China)Abstract: In the high-speed PCB design, the main problems are signal integrity and time sequence caused by propagation delay. We can find out and solve these problems, when simulating high speed signal line in virtue of Cadence/SpecctraQuest Before layout and routing trace which helps to shorten the design period.Key words: signal integrity; time sequence; simulation(上接第9页)Note to the Infinitude Calculation of InfinitesimalMA Ge, SONG Su-luo(Nanyang Institute of Technology, Nanyang Henan 473004, China)Abstract: By analyzing and discussing the sum sequence and product sequence of countable infinite infinitesimal sequence and the sequence of positive infinity power of infinitesimal sequence and positive infinitesimal sequence power of non-negative infinitesimal sequence, the understanding on infinitesimal are deepened.Key words: infinitesimal; infinite sum; infinite product; infinity power。

PCB常用计算公式

PCB常用计算公式PCB(Printed Circuit Board)是一种电子元器件支持结构,用于组织和连接电子元器件。

在设计和制造PCB时,需要考虑各种参数和计算公式来确保电路板的性能和可靠性。

以下是一些PCB常用的计算公式。

1.PCB线宽与电流的关系PCB线宽决定了电路板上的信号或电流的最大容量。

线宽与电流的关系可以用以下公式计算:I=k*A*ΔT*J其中,I是电流(单位为安培A),k是单位转换系数,A是线宽(单位为平方米m^2),ΔT是温升(单位为摄氏度℃),J是电流密度(单位为安培/平方米A/m^2)。

该公式用于计算给定线宽下的最大电流。

2.PCB阻抗的计算PCB阻抗是电路板上信号传输的重要参数,可以用以下公式计算:Zo = sqrt(L/C)其中,Zo是阻抗(单位为欧姆Ω),L是线路的自感(单位为亨利H),C是线路的电容(单位为法拉F)。

该公式用于计算给定线路的阻抗。

3.PCB电容的计算PCB上的电容是由线路的结构和材料决定的,可以通过以下公式进行计算:C=ε*ε0*A/d其中,C是电容(单位为法拉F),ε是相对介电常数,ε0是真空中的介电常量,A是电容的面积(单位为平方米m^2),d是线路间距(单位为米m)。

该公式用于计算给定线路的电容。

4.PCB临界迹宽的计算PCB上的迹通常有最小宽度限制,可以通过以下公式进行计算:W = sqrt(I * K)其中,W是迹的宽度(单位为米m),I是电流(单位为安培A),K是补偿系数。

该公式用于计算给定电流下,迹的最小宽度。

5.PCB残留铜的计算PCB制造过程中,残留铜是未被除去的铜箔或镀层。

可以通过以下公式进行计算:Rc=(Cl*D)/(A*Ct)其中,Rc是残留铜的厚度(单位为米m),Cl是铜的质量(单位为克g),D是相对的粗糙度,A是PCB钢板的表面积(单位为平方米m^2),Ct是表面涂层的厚度(单位为米m)。

该公式用于计算给定条件下的残留铜厚度。

pcb走线优化的走线策略.doc

PCB Layout中的走线策略布线(Layout)是PCB设计工程师最基本的工作技能之一。

走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中是至关重要的。

下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。

主要从直角走线,差分走线,蛇形线等三个方面来阐述。

1.直角走线直角走线一般是PCB布线中要求尽量避免的情况,也几乎成为衡量布线好坏的标准之一,那么直角走线究竟会对信号传输产生多大的影响呢?从原理上说,直角走线会使传输线的线宽发生变化,造成阻抗的不连续。

其实不光是直角走线,顿角,锐角走线都可能会造成阻抗变化的情况。

直角走线的对信号的影响就是主要体现在三个方面:一是拐角可以等效为传输线上的容性负载,减缓上升时间;二是阻抗不连续会造成信号的反射;三是直角尖端产生的EMI。

传输线的直角带来的寄生电容可以由下面这个经验公式来计算:C=61W(Er)1/2/Z0在上式中,C就是指拐角的等效电容(单位:pF),W指走线的宽度(单位:inch),εr指介质的介电常数,Z0就是传输线的特征阻抗。

举个例子,对于一个4Mils的50欧姆传输线(εr为4.3)来说,一个直角带来的电容量大概为0.0101pF,进而可以估算由此引起的上升时间变化量:T10-90%=2.2*C*Z0/2 = 2.2*0.0101*50/2 = 0.556ps通过计算可以看出,直角走线带来的电容效应是极其微小的。

由于直角走线的线宽增加,该处的阻抗将减小,于是会产生一定的信号反射现象,我们可以根据传输线章节中提到的阻抗计算公式来算出线宽增加后的等效阻抗,然后根据经验公式计算反射系数:ρ=(Zs-Z0)/(Zs+Z0),一般直角走线导致的阻抗变化在7%-20%之间,因而反射系数最大为0.1左右。

而且,从下图可以看到,在W/2线长的时间内传输线阻抗变化到最小,再经过W/2时间又恢复到正常的阻抗,整个发生阻抗变化的时间极短,往往在10ps之内,这样快而且微小的变化对一般的信号传输来说几乎是可以忽略的。

基于随机行走电容提取且保证准确度的线网时延计算方法

基于随机行走电容提取且保证准确度的线网时延计算方法一、引言在现代电路设计中,时延计算是一个重要的技术,因为它可以在数字系统中提供信息处理能力。

这些计算可以为芯片设计人员提供在开发过程中细粒度控制的能力,确保电路在各种条件下的正常运行。

现代电路设计需要越来越高的精度要求,因此需要新的方法来提高时延计算的准确性和速度。

二、相关工作回顾已有的时延计算方法通常使用基于查找表的方法进行计算,这些方法通常过于简单,并不考虑实际的物理因素。

然而,现代电路的安装容量已达到数十亿个晶体管,这需要更精确的时延计算方法。

近年来,一些新的方法已经被提出,其中包括随机行走电容提取方法。

这个方法用于计算电容的时延。

这个方法建立在跨导望远镜的顶部和底部加起来之后,采用一种随机行走方法来取得得到电容的参数,然后进行时延计算。

三、提出的方法本文提出了一种新的基于随机行走电容提取并保证准确性的线网时延计算方法。

这个方法最大的优点是提高了计算的准确性,并能够快速处理大型电路的时延计算。

在这个方法中,我们使用了一种改进的随机行走技术,在线路中提取电容值。

基于这个方法,我们可以计算电路元件之间的准确时延,并能够考虑实际的物理因素。

四、实验结果分析通过长时间的实验,本文提出的方法在准确度和速度上均有了显著的提高。

我们将本文提出的方法与现有的方法进行比较,在计算准确度和时间效率方面都能稳定地实现优越性能。

五、结论和未来工作本文提出的基于随机行走电容提取且保证准确度的线网时延计算方法,能够有效提高时延计算的准确性和速度。

未来的工作可以进一步优化本方法的实现,以实现更加快速和准确的电路时延计算。

一、引言在现代电路设计中,时延计算是一个非常重要的技术,因为它可以为数字系统提供信息处理能力。

这些计算可以为芯片设计人员提供在开发过程中细粒度控制的能力,确保电路在各种条件下的正常运行。

但是,现代电路已经达到数十亿个晶体管的规模,因此需要更为精确的时延计算方法。

PCB上的任何一条走线在通太高频信号的情形下都会对该信

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关”信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟线,通常它不需经过任何其它逻辑处理,因而其延时会小于其它相关信号。

高速数字PCB板的等线长是为了使各信号的延迟差保持在一个范围内,保证系统在同一周期内读取的数据的有效性(延迟差超过一个时钟周期时会错读下一周期的数据),一般要求延迟差不超过1/4时钟周期,单位长度的线延迟差也是固定的,延迟跟线宽,线长,铜厚,板层结构有关,但线过长会增大分布电容和分布电感,使信号质量,所以时钟IC引脚一般都接RC端接,但蛇形走线并非起电感的作用,相反的,电感会使信号中的上升元中的高次谐波相移,造成信号质量恶化, 所以要求蛇形线间距最少是线宽的两倍,信号的上升时间越小就越易受分布电容和分布电感的影响.因为应用场合不同具不同的作用,如果蛇形走线在电脑板中出现,其主要起到一个滤波电感的作用,提高电路的抗干扰能力,电脑主机板中的蛇形走线,主要用在一些时钟信号中,如CIClk,AGPClk,它的作用有两点:1、阻抗匹配2、滤波电感。

对一些重要信号,如INTEL HUB架构中的HUBLink,一共13根,跑233MHz,要求必须严格等长,以消除时滞造成的隐患,绕线是唯一的解决办法。

一般来讲,蛇形走线的线距>=2倍的线宽。

PCI板上的蛇行线就是为了适应PCI 33MHzClock的线长要求。

若在一般普通PCB板中,是一个分布参数的LC滤波器,还可作为收音机天线的电感线圈,短而窄的蛇形走线可做保险丝等等.PCB布线的常见规那么1 电源、地线的处置既使在整个PCB板中的布线完成得都专门好,但由于电源、地线的考虑不周到而引发的干扰,会使产品的性能下降,有时甚至影响到产品的成功率。

所以对电、地线的布线要认真对待,把电、地线所产生的噪音干扰降到最低限度,以保证产品的质量。

信号时延介绍

阻抗值 (Ω) 50 50 50 100 100

参考平面层

L2、L7 L2&L4 L5&L7 L2、L7 L2&L4、 L5&L7

代入公式计算得,微带线中单端信号的传播速度大约是6.67in/ns,传播延迟大约为 0.150ns/in(0.150ps/mil);差分信号的传播速度大约是6.70in/ns,传播延迟大约 为0.149ns/in(0.149ps/mil)。

11.8 / Br e r in / ns

信号时延介绍

下面是我司常用的一种八层板叠层结构:

信号时延介绍

该八层板叠层结构的走线要求:

层名

L1、L8层 L3层 L6层 L1、L8层 L3、L6层

类型

单端 单端 单端 差分 差分

线宽/间距(mil)

5.5 6.2 6.2 4.7/10.3/4.7 5.2/9.8/5.2

他对传播时间的估计是以nsin为单位传播延迟微带线br传播延迟带状线传播延迟其中w走线宽度milh走线和参考层之间的距离mil走线和其下方的参考层之间电路板材料的相对介电常数传播速度信号时延介绍信号时延介绍下面是我司常用的一种八层板叠层结构

信号时延介绍

信号时延介绍

传播速度 电信号在导线中或者空气中以光速传播,即3*108m/s(换算后为11.8in/ns)。当电流从

PD = e r /11.8 ns/ in

TD = PD ? L

信号时延介绍

走线与信号传播 电路板走线分为带状线和微带线。

通常认为带状线环境的走线四周的材料是均匀的。实际上,我们设计时也是这样要求 厂家制作的。因此,在带状线环境的走线中,信号的传播速度就可以用如下公式进行

时延估计方法

利用EM算法实现多径时延的极大似然估计

t 的估值也会被限制在以采样周期兀为间隔的离散点上, 如果t不是Ts的整数倍,则它的准确估值只能借助于内插 才可以得到。EM算法中的迭代加上内插使的运算量加大, 必须想办法加以消除。

改进方法:利用频域数据避免内插运算,在利用频域数据 EM算法的整个处理过程中,仅仅需要增加两次(分别对发 射信号和接收信号进行)DFT运算, 不需要在每次迭代中进 行复杂的内插运算。

• 利用有效的迭代初始化过程提高收敛性能; • 利用参数顺序更新的迭代过程加快迭代收敛速度; • 自适应的改变搜索区间的设定减小搜索的运算量。

参数顺序更新可以加快迭代的收敛速度,因而总的运算 量减小了。不过存在一个缺陷,即普通EM算法中可以并行 完成的L个信号的参数估计,在这里只能够顺序进行,因而在 具有并行能力的系统中,时间上的开销增大了,这是我们为 加快迭代收敛速度所必须要牺牲的代价。

•多径时延估计

• 已知信号多径时延估计(EM算法实现ML) • 含噪参考信号多径时延估计(循环相关函数的LS法) • 未知波形信号的多径参数估计(music算法、esprit算法)

离散型的已知信号多径时延估计模型如下所示:

极大似然估计(MxaimmuLikehhoodEstimatino)是 参数估计问题的有效方法,具有近似最佳的估计性能 及稳健性。但是,鉴于多信号多参数估计问题所需多 维优化的复杂性,在多径时延估计问题中直接使用极 大似然方法显然并不可行。

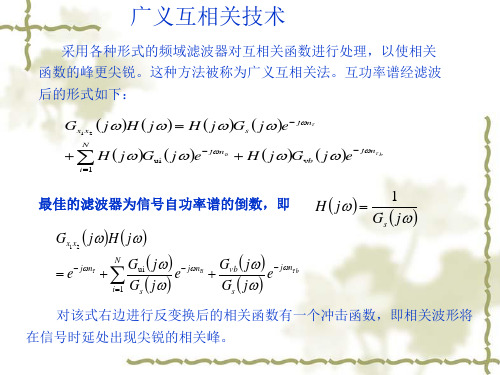

广义相位谱法是基于相位谱估计的时延估计方法中最常见 的一种算法。由相关函数时间域转换为功率谱密度函数在频率 域比较信号之间的相似性。

自适应时延估计方法

基于自适应滤波器的自适应时延估计算法,常用的是 LMSTDE(最小均方误差时延估计算法)。

PCB走线优化的走线策略(全面)

PCB Layout中的走线策略布线(Layout)是PCB设计工程师最基本的工作技能之一。

走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中是至关重要的。

下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。

主要从直角走线,差分走线,蛇形线等三个方面来阐述。

1.直角走线直角走线一般是PCB布线中要求尽量避免的情况,也几乎成为衡量布线好坏的标准之一,那么直角走线究竟会对信号传输产生多大的影响呢?从原理上说,直角走线会使传输线的线宽发生变化,造成阻抗的不连续。

其实不光是直角走线,顿角,锐角走线都可能会造成阻抗变化的情况。

直角走线的对信号的影响就是主要体现在三个方面:一是拐角可以等效为传输线上的容性负载,减缓上升时间;二是阻抗不连续会造成信号的反射;三是直角尖端产生的EMI。

传输线的直角带来的寄生电容可以由下面这个经验公式来计算:C=61W(Er)1/2/Z0在上式中,C就是指拐角的等效电容(单位:pF),W指走线的宽度(单位:inch),εr指介质的介电常数,Z0就是传输线的特征阻抗。

举个例子,对于一个4Mils的50欧姆传输线(εr为4.3)来说,一个直角带来的电容量大概为0.0101pF,进而可以估算由此引起的上升时间变化量:T10-90%=2.2*C*Z0/2 = 2.2*0.0101*50/2 = 0.556ps通过计算可以看出,直角走线带来的电容效应是极其微小的。

由于直角走线的线宽增加,该处的阻抗将减小,于是会产生一定的信号反射现象,我们可以根据传输线章节中提到的阻抗计算公式来算出线宽增加后的等效阻抗,然后根据经验公式计算反射系数:ρ=(Zs-Z0)/(Zs+Z0),一般直角走线导致的阻抗变化在7%-2020间,因而反射系数最大为0.1左右。

而且,从下图可以看到,在W/2线长的时间内传输线阻抗变化到最小,再经过W/2时间又恢复到正常的阻抗,整个发生阻抗变化的时间极短,往往在10ps之内,这样快而且微小的变化对一般的信号传输来说几乎是可以忽略的。

芯片设计中的布线与时延优化技术探讨

芯片设计中的布线与时延优化技术探讨在芯片设计中,布线与时延优化技术是至关重要的方面。

布线是将不同元件之间的连线进行有效规划和布置的过程,而时延优化技术则旨在减少电路中信号传输的时间延迟。

本文将探讨在芯片设计中布线与时延优化技术的相关问题,并介绍一些方法和策略。

一、布线技术布线技术是芯片设计中一个关键的环节,它直接影响到芯片的性能和功耗。

布线的目标是将芯片上的不同功能单元连接起来,并合理规划信号的传输路径。

在布线过程中,需要考虑以下几个因素:1.1 信号完整性:布线过程中需要确保信号能够在不损失质量和准确性的前提下传输到目标地点。

为了实现信号完整性,可以采用差分对布线技术、层次布线和电磁干扰抑制等方法。

1.2 功耗优化:布线中信号传输所需的功耗也是需要考虑的一个因素。

可以通过合理规划布线路径、减少布线层数和使用有效的供电策略等方式来降低功耗。

1.3 时延优化:布线过程中的一个重要目标是尽量缩短信号的传输时间。

通过合理选择信号路径、减少布线长度和使用先进的时延优化技术等方法可以实现时延的优化。

二、时延优化技术在芯片设计中,时延优化技术是提高芯片性能和可靠性的关键之一。

时延指的是信号从发送到接收所需的时间延迟,它直接影响着芯片的工作速度。

以下是一些常用的时延优化技术:2.1 时钟树优化:时钟树是芯片设计中常用的时钟分配网络。

通过合理布置时钟树,并采用低时延的时钟路由算法,可以减少时钟传输的延迟。

2.2 等长布线:等长布线是指对于芯片上的不同信号路径,尽量使其长度相等。

这样可以减小信号传输的延迟差异,提高芯片的工作效率。

2.3 缓冲器优化:在芯片布线中,由于信号传输的延迟增加,可能会导致信号的失真和功耗的增加。

通过合理优化缓冲器的位置和类型,可以有效降低延迟和功耗。

2.4 时钟同步优化:芯片中常常存在多个时钟域,时钟域之间的传输延迟会对芯片的性能和可靠性产生影响。

通过采用合适的时钟同步方案,可以减小时钟域之间的延迟差异,提高芯片的工作性能。

PCB传输时延计算

P C B传输时延计算------------------------------------------作者xxxx------------------------------------------日期xxxx【精品文档】电信号在PCB上的传播速度2013-10-21 15:00:25分类:IT职场电信号在真空中的传播速度是光速,3 * 10^8 m/s or11.8 inch/ns . 1 inch = 2.54cm = 1000 mil在其他的介质中,如果相对介电系数是Er ,则传播速度为 11.8 * Er^0.5。

例如,在水中,水的相对介电系数是80,所以,传播速度是真空中的1/9 ,在PCB中,FR4的相对介电系数约为4,所以,传播速度是真空中的一半,既11.8 / 4 ^0.5 = 5.9 inch/ns对于两个200M的sina wave号,如果trace的长度相差200mil,则信号从driver到达receiver的时间相差:200 / 5900 = 0.034ns;200M的信号每个周期的时间为5ns.所以,判断200mil的线长误差的依据在于这个0.034ns的时间差能否引起时序问题。

--------------------------------------------------------------------- 时间的单位换算 1秒=1000毫秒(ms) 1毫秒=1/1,000秒(s) 1秒=1,000,000 微秒(μs) 1微秒=1/1,000,000秒(s) 1秒=1,000,000,000 纳秒(ns) 1纳秒=1/1,000,000,000秒(s) 1秒=1,000,000,000,000 皮秒(ps) 1皮秒=1/1,000,000,000,000秒(s)--------------------------------------------------------------------- 信号在pcb走线上传输需要一定的时间,普通FR4板材上传输时间约为每纳秒6英寸,当然表层走线和内层走线速度稍有差别。

PCB线路良率预测方法介绍

按 照 工 厂 的 标 准 流程 制 造 测 试 板 并 提交 给 C A T * C A T分析 所 有 数 据 生 成 所 有报 告 。

图 1预 测 产 品 良率 与 导 线 长度

过程 能力 测试板设计 , 测试方法 , 数据分析技术 和数 据库相关 的知

路长 度 由于线路开路 导致的产 品部分 良率和 由于线路短路 导致 的产 品部分 良率通过公式( 4 ) 计算得到 由于线路开路和短路导致 的产品 P C Q R : 过程能力 测试板 由不同的测试模块组成 , 用于印制线路 部分 良率 板 制造过程收集数据 的测试 图形应该尽可能 的接近他们打算、 导通孔 、 孔盘 和网格尺 寸 、 对位和阻 1 0 O y , f o v , ( 4 ) 抗要求 、 层数 、 叠构 、 板厚和材料 。利用其线宽 间距模块 的测试结果 5 良率 预测 示例 可以预测线路板线路 良率。 线宽间距模块 由不 同的线宽间距 的线条 如图 1 所示 了 5 m i l 间距缺 陷密度是 3 6 1 个 缺陷每百万英 寸间 构成 , 通过测试测试点导线 的通断情况侦测线路开短路 的缺陷 。其 距 。 同样 , 在 固定 缺 陷密 度 的情 况 下 预 测 良率 随 着 间 距 长 度 增 加 而 测试结果 中的线路 良率以及缺陷密度可 以预测线路 良率 。 降低 。 基于开路 的部分 良率乘 以基于短路的部 分 良率然后再通过乘 0 0转化为百分率来估算产 品开短路联合通 过测量线宽 间距 模 缺 陷密度是指每单位数量 或者尺寸 的产 品特性发生缺 陷的数 以 1 计算 缺陷密度得到 的成功制造线路 和间距的能力 , 预测 良率表 量, 比如每 1 0 0 0英寸线路中开路发生 的次数 。 通过线路 良率计算得 块 , 示线宽间距 的质量 。图 1表述了通过开短路 的预测 良率对线 宽为 到的缺陷密度标准化了缺陷产生的概率 , 可 以用于预测产 品生产时 、 4 、 5和 6 mi l 的线路和 4 、 5 、 6 mi l 间距的 曲线 。曲线显示 了一个 固 的 良率。 公式 1 用于通过过程能力测试板 的能力数据计算线路缺 陷 3 定缺陷密度 的情况下 , 产 品良率随着线路长度增加而下降。缺陷密 皴 。 i n Y 度为 3 3 个缺 陷每百万英寸 的 6 m i l 导线预测产 品 良率 ( 开路造成 ) 0 0 、 1 0 0 0 、 1 0 0 0英 寸 线 路 的 产 品分 别 为 9 9 . 7 %, 9 6 . 8 %和 ( 1 ) 每单元 1 7 1 . 9 %。当缺 陷密度提高到如图上 5 m i l 线路所示的 1 3 3 个缺 陷每百 式中 Y = 线路 良率 , I =独立线路长度 , :线路缺陷密度 万英寸时 , 1 0 0 、 1 0 0 0 、 1 0 0 0英 寸 线路 的 预测 良率 分 别 为 9 8 . 7 %、 类似 的公式用于计算间距和导通孔 的缺陷密度。 8 7 . 5 %和 2 6 . 5 %。 作用 的预测 良率。 例如 , 一个 由 1 0 0 0 英寸 5 m i l 线路 0 0英 寸 5 m i l间 距 构 成 的 产 品 , 预 测 良 率 应 该 为 由于缺 陷密度符合泊松分布 , 因此通过缺 陷密度 以及每个单元 和 5 0. 9 68 * 0. 83 5 *1 0 0=8 0. 5 % 。 上某产品特性 的数量可 以预测有这缺陷限导致产品失效的 良率 。 由 结 束 语 线路开路 导致 的产 品失效的 良率通过公式( 2 ) 计算 随着客户对 P C B的要求 越来 越高 , 精 细线路 , 越来越 多的工厂 Y f o —e -  ̄ c L e 不清楚是否其 良率是否可以满足客户的需要 , 需付 出多大的代价才 本文介绍的良率预测方法正适 合解决这样 的问 式中 ( = =过程能力测试板测得开路缺 陷密度 , L 产品 的总线 能达到客户的要求 。

到底微带线和带状线延时上的差别有多大?

到底微带线和带状线延时上的差别有多大?

大家在对一些数据总线处理等长的时候,都知道要同组同层,除了免去过孔带来的传输延时之外,微带线和带状线由于信号传输速度的不同,同样长度的走线延时也是有差别。

我们绕等长的最终目的是为了满足时间上的等长而不是单纯走线长度上的物理等长。

到底微带线和带状线延时上的差别有多大,绕等长的时候过孔的长度要不要算进去,可能有个具体的数据会更直观点。

下面我们来将这些数据进行估算和量化。

1.微带线和带状线传输时延

PCB中微带线是指走线只有一个参考面,带状线是指走线有两个参考面。

带状线由于电磁场都被束缚在两个参考面之间的板材中,所以走线的有效介电常数为板材的介电常数。

微带线会导致部分电磁场暴露在空气中,空气的相对介电常数约为1.0006,板材如常规FR4的介电常数为4.2,那幺微带线的有效介电常数在1和4.2之间。

现在以特定的FR4板材和层叠结构来量化微带线和带状线的传输延时。

1.微带线层叠和时延。

PCB设计布线通道计算和设计规划

PCB设计布线通道计算和设计规划设计中布线通道如何计算?与设计规章存在什么样的联系?布线通道计算规章:PCB板布线通道初步估算方式:两个过孔之间布线通道:Ni=INT((Wi-2S-W1)/(W1+S1)+1)其中:Ni:相邻两过孔间布线通道数Wi:过孔边沿间距S:过孔到布线边沿间距W1:线宽S1:线间距两个过孔之间布线通道计算暗示图差分线时:W1:=2*W2+S2 通道数即为差分线通道数W2:差分线线宽S2:差分线对内线间距差分线计算通道时:将一对差分线(W2/S2)等效成一根单线(线宽为2*W2+S2)处理。

解释:50MIL格点系统,一般信号(5MIL线宽、8MIL线间距)安照2个布线通道设计,时钟信号根据1个布线通道设计,差分信号根据1对差分线通道设计。

高密区域布线规划学问:(1)建议高密BGA布线采纳特别Fanout布线方式,外围4排管脚引出通过表层Fanout,增大布线通道。

(2)全部电源,地管脚需要挺直Fanout到相应的平面层,避开引出起出100mil长线Fanout,不包含到布线层的布线通道规划。

(3)高密BGA区域布线层数确定规章如下:最少内层布线层数=INT(M/N)+1最多内层布线层数=BGA非电源地最密管脚排布层数/两过孔间布线通道数-2解释:M:除外围4层管脚外BGA 区域的非电源地布线衔接总数+前两排挺直Fanout铺张的布线通道数;N:第5排管脚Fanout环区域的布线通道总数BGA区域全部除外4层的管脚布线都需要占用第5层环形区域的布线通道,按照此区域的布线通道数和总的布线衔接数确定最少内层布线层数。

(4)按照布线瓶颈区确定PCB板布线层数,瓶颈区域PCB板最少布线层数=INT(M/N)+1解释:M:通过瓶颈区域的布线衔接数;N:瓶颈区域的布线通道数高密BGA区域布线规划需要优先举行的划分,定义的各种BUS,然后按照各种总线的分布确定布线的大致区域,最后按照各组总线的所需通道数举行具体的通道具分配和布线规划。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

信号在PCB走线中传输时延(上)来源:一博科技更新时间:2014-2-15摘要:信号在媒质中传播时,其传播速度受信号载体以及周围媒质属性决定。

在PCB(印刷电路板)中信号的传输速度就与板材DK(介电常数),信号模式,信号线与信号线间耦合以及绕线方式等有关。

随着PCB走线信号速率越来越高,对时序要求较高的源同步信号的时序裕量越来越少,因此在PCB设计阶段准确知道PCB走线对信号时延的影响变的尤为重要。

本文基于仿真分析DK,串扰,过孔,蛇形绕线等因素对信号时延的影响。

关键词:传输时延, 有效介电常数,串扰DDR 奇偶模式1.引言信号要能正常工作都必须满足一定的时序要求,随着信号速率升高,数字信号的发展经历了从配合步时钟到源同步时钟以及串行(serdes)信号。

在当今的消费类电子,通信服务器等行业,源同步和串行信号占据了很大的比重。

串行信号比如常见PCIE,SAS,SATA,QPI,SFP+,XUAI,10GBASE-KR等信号,源同步信号比如DDR信号。

串行信号在发送端将数据信号和时钟(CLK)信号通过编码方式一起发送,在接收端通过时钟数据恢复(CDR)得到数据信号和时钟信号。

由于时钟数据在同一个通道传播,串行信号对和对之间在PCB上传输延时要求较低,主要依靠锁相环(PLL)和芯片的时钟数据恢复效用。

源同步时钟主要是DDR信号,在DDR设计中,DQ(数据)信号参考DQS(数据选通)信号,CMD(命令)信号和CTL(控制)信号参考CLK(时钟)信号,由于DQ的速率是CMD&CTL信号速率2倍,所以DQ信号和DQS信号之间的传输延时要求比CMD&CTL和CLK之间的要求更高。

目前市场上主流的为DDR1/ DDR2/ DDR3。

DDR4预计在2015年将成为消费类电子的主要设计,随着DDR信号速率的不断提高,在DDR4设计中特别是DQ和DQS之间传输时延对设计者提出更高的挑战。

在PCB设计的时候为了时序的要求需要对源同步信号做一些等长,一些设计工程师忽略了这个信号等长其实是一个时延等长,或者说是一个‘时间等长’。

2.传输时延简介 Time delay又叫时延(TD),通常是指电磁信号或者光信号通过整个传输介质所用的时间。

在传输线上的时延就是指信号通过整个传输线所用的时间。

Propagation delay又叫传播延迟(PD),通常是指电磁信号或者光信号在单位长度的传输介质中传输的时间延迟,与“传播速度”成反比例(倒数)关系,单位为“Ps/inch”或“s/m”。

从定义中可以看出时延=传播延迟*传输长度(L)其中v 为传播速度,单位为inch/ps或m/sc 为真空中的光速(3X108 m/s)εr 为介电常数PD 为传播延迟,单位为Ps/inch或s/mTD 为信号通过长度为L的传输线所产生的时延L为传输线长度,单位为inch或m 从上面公式可以知道,传播延迟主要取决于介质材料的介电常数,而传播时延取决于介质材料的介电常数、传输线长度和传输线横截面的几何结构(几何结构决定电场分布,电场分布决定有效介电常数)。

严格来说,不管是延迟还是时延都取决于导体周围的有效介电常数。

在微带线中,有效介电常数受横截面的几何结构影响比较大;而串扰,其有效介电常数受奇偶模式的影响较大;不同绕线方式有效介电常数受其绕线方式的影响。

3.仿真分析过程3.1 微带线和带状线传输时延PCB中微带线是指走线只有一个参考面,如下图1;带状线是指走线有2个参考面,如下图2.带状线由于电磁场都被束缚在两个参考面之间的板材中,所以走线的有效介电常数为板材的介电常数。

微带线会导致部分电磁场暴露在空气中,空气的相对介电常数约为1.0006,板材如常规FR4的介电常数为4.2,那么微带线的有效介电常数在1和4.2之间,可以利用下面的公式计算微带线的有效介电常数【Collins,1992】:εe = (εr +1)/2 + (εr -1)/2(1+12H/W)-1/2 + F -0.217(εr -1)T/√WH 3.1F = 0.02 (εr -1)(1-W/H)2 (W/H < 1) F= 0 (W/H >1) 3.2其中,εe 为有效介电常数, εr 为电路板材料的介电常数,H为导线高于地平面的高度,W为导线宽度,T为导线厚度。

图4 微带线层叠与时延图5 带状线层叠和时延在图4和图5的层叠结构下,1000mil的走线时延差=179.729ps-147.954ps=31.775ps,可以看出这个差距是非常大的。

在做源同步的DDR同组等长时候只考虑物理等长会带来很严重的'时间不等长。

3.2 走线和过孔传输时延在PCB设计时候,经常会遇到走线换层,走线换层必须借助于过孔。

但长度相等的过孔和走线之间的时延并不相等。

过孔的时延可以用式3.3表示TD_via=√LC 3.3其中TD_via表示信号经过过孔的时延,L表示过孔的寄生电感,C表示过孔的寄生电容。

从式3.3可以看出寄生电容和寄生电感都会导致过孔的传输时延变大。

而不同过孔结构寄生参数也会发生改变。

下面通过仿真分析过孔时延和传输线时延时间的偏差。

图6 过孔结构及寄生参数如图6所示过孔结构时延可以根据式3.3计算出:TD_via=√LC=sqr(0.4021pf*1326.2pH)=23.1ps 式3.4由式3.4可以看出,结构如图6所示过孔的传输时延为23.1ps。

而对于普通FR4板材的微带线,1.6mm走线传输时延约为11ps,对于带状线约为12. 5ps。

通过计算可以看出相同长度的走线和过孔之间的时延相差是非常大的。

因此对设计工程师来讲设计的时候尽量做到以下两点:1)需要做等长的信号要尽量走同层,换层时需要注意总的长度要保持相等并且每层走线都需要等长。

2)需要等长的信号走相同走线层可以保持过孔的时延一致,从而消除过孔时延不一致带来的影响。

信号在PCB走线中传输时延(下)来源:一博科技更新时间:2014-2-193.3 串扰对信号时延的影响。

PCB板上线与线的间距很近,走线上的信号可以通过空间耦合到其相邻的一些传输线上去,这个过程就叫串扰。

串扰不仅可以影响到受害线上的电压幅值,同时还会影响到受害线上信号的传输时延。

图7 串扰拓扑图如图7串扰拓扑图所示,假设有3根相互耦合的传输线,中间的一根线(图8中D1)为受害线,两边的线(图8中D0&D2)为进攻线。

仿真中所加的激励源为图8所示,分为三种情况:1,假设两边的进攻线中没有信号,即不存在串扰,此种情况作为参考基准线(Reference);2,假设进攻线和受害线切换状态一致,此种情况为偶模(Even Mode)3,假设进攻线和受害线切换状态相反,此种情况为奇模(Odd Mode)图8 串扰仿真中激励奇偶模式空间电磁场分布(如图9&图10所示)不同,从而导致了传输线周围的有效介质电常数不同,有效介电常数的不同最终带来了在不同激励源的情况下信号传播速度不同。

图9 奇模电磁场分布图10 偶模电磁场分布仿真结果如下图11所示,其中蓝色为第一种激励所对应的参考基准线,其周围没有其它信号线的影响;红色线为第二种激励所对应的接收端波形;绿色为第三中情况所对应的接收端波形。

绿色波形最早到达接收端,而红色的波形最后到达接收端,是由于奇模的传输速度比偶模块。

图11 串扰仿真结果从上面的仿真结果可以看出信号线周围的进攻线会对信号线的传输时延到来影响,如果设计处理不当,导致传输时延偏差较大最终会导致系统工作不稳定。

在设计的时候要尽量减小这种影响,可以从以下几点考虑:1,拉大线间距。

线间距越大,相邻走线间的影响就越小,走线间距尽量满足3W原则。

2,使耦合长度尽量短。

相邻传输线平行走线长度越长串扰越大,走线时候尽量减小相邻线平行走线长度;对于相邻层走线尽量采用相邻层垂直走线。

3,走线尽量走在带状线。

微带线的串扰相对带状线较大,带状线走线可以减小串扰的影响。

4,保持完整回流平面,避免跨分割,走线和参考面尽量紧耦合。

3.4 绕线方式对信号时延的影响在PCB设计时候,有些设计人员为了满足等长要求会对走线进行绕线,很少有设计人员会考虑到不恰当的绕线也会影响传输线时延。

为了验证绕线对传输线时延的影响,我们公司信号完整性团队(SI组)设计出测试板进行实测。

如下图12所示,蛇形绕线和参考直线走在相同的走线层,两者线宽线间距以及物理长度完全相同,蛇形绕线的局部放大图如下图13所示。

图12 蛇形绕线和参考走线图13 蛇形绕线局部放大图实测结果如下图13所示,其中红色线为参考走线,蓝色的线为蛇形绕线的走线,从结果可以看出,蛇形绕线的信号传输速度会比直线参考线的速度要快,两者相差了13.89ps。

这是由于蛇形绕线靠的太近,平行的耦合长度太长,信号在蛇形绕线上的自耦合导致信号传播速度较快。

图13 实测结果通过3D电磁场仿真软件也可以看出这种蛇形绕线和直线间传输速度不同,如下图14所示:两种不同的绕线是物理等长的,可以看出下面一种绕线方式由于绕线靠的较紧,而且平行耦合长度也长,可以看出下面一种绕线方式信号传输的会快一点图14 仿真结果从上面的仿真测试可以看出,不同绕线方式对信号时延影响还是比较大的,为了减小由于绕线带来的时延的影响,可以考虑以下几点:1,在PCB设计时候尽量减少不必要的绕线,比如串行信号差分对和差分对之间没有必要做等长。

2,增大绕线间间距,尽量满足单根绕线间距大于5H(H为线到最近参考面的距离),差分绕线大于3H(H为线到最近参考面的距离)。

3,减小绕线间平行走线长度。

4.小结在PCB设计时候要将等长的设计观念逐步向等时设计转变,在对时序或者等长要求高的设计尤其需要注意串扰,绕线方式,不同层走线,过孔时延等方面对时序的影响。

丰富的SI(信号完整性)知识和正确的仿真方法可以帮助设计去评估PCB板上的传输时延,从而提高设计的质量。

我们在设计PCB板的时候经常会考虑信号线等长,如果等长做的不好,各个信号之间就会有延时,可能会造成数据采样错误等问题。

那么PCB上的延时应该怎么计算?我们经常听到的PCB表层走线比PCB内层走线的速度快为什么?首先要明确的一个问题是PCB上信号速度不是电子的运动速度。

信号在PCB信号线里是以电波的形式向前传播。

那么信号速度等于光速么?答案也是否定的。

信号速度还与不同材料的介电常数相关。

具体计算公式是V=C/Er0.5 ,其中Er是信号线周围材料的相对介电常数。

如果信号线暴露在空气中那么信号的传输速度就等于C,但是在PCB上,传输速度明显小于C。

举例,我们常见的PCB材料Fr4的介电常数在4.2-4.5左右,为了计算方便我们取4。

带入公式可以算出,Fr4材料制作的PCB板上面信号的传输速度是光速的二分之一。