利用PSoC实现频率计

单片机的频率计原理及应用

单片机的频率计原理及应用频率计是一种用于测量信号频率的仪器,它可以通过测量信号周期的时间来计算出信号的频率。

在单片机中,我们可以利用单片机的计时/计数功能来实现频率计。

频率计的原理是利用计时/计数器的工作原理。

计时/计数器是一种可编程的计数器,它可以根据我们的需要进行计数,实时显示计数结果。

在频率计中,我们可以将计时/计数器配置为计数外部时钟脉冲的脉冲数。

假设外部信号的频率为f,那么每个周期中的脉冲数为N,那么信号的周期T可以表示为T = 1/f = N*(1/计数频率),其中计数频率为计时/计数器的工作频率。

在单片机中,我们可以使用定时器/计数器(Timer/Counter)来实现频率计。

单片机中的定时器/计数器有多种工作模式,例如定时模式和计数模式。

在计数模式下,我们可以将定时器/计数器配置为对外部时钟脉冲进行计数。

定时器/计数器会记录经过的脉冲数,我们可以通过读取定时器/计数器的值来获取脉冲数N,从而计算出信号的频率。

单片机中的定时器/计数器通常有32位或16位的计数器,可以支持更大范围的计数。

当计数器溢出时,我们可以通过中断来处理计数结果,从而实时获取信号的频率。

通过频率计,我们可以测量各种信号的频率,包括脉冲信号、交流信号、数字信号等。

频率计的应用非常广泛。

在电子设备制造中,频率计可以用于生产过程中的频率测量,用于检验电路工作是否正常。

在通信工程中,频率计可以用于测量无线电信号频率,包括无线电收发信号和无线电调制信号等。

在科学实验中,频率计可以用于测量声波频率、震动频率等。

此外,频率计还可以用于音频设备中的音频频率测量,例如测量音响设备的频率响应范围。

在自动化控制系统中,频率计可以用于测量机械运动的频率,用于控制机械运动。

另外,频率计还可以用于测量电网频率,用于监控电网的稳定性。

总之,频率计是一种实用的测量仪器,通过单片机的计时/计数功能可以实现频率测量。

它可以广泛应用于电子设备制造、通信工程、科学实验、音频设备、自动化控制等领域。

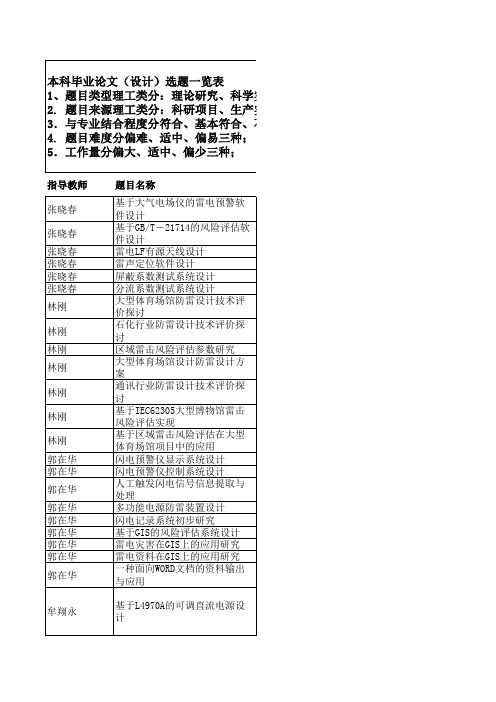

成都信息工程学院毕业课题详情

张福贵

基于ADS805E的采集卡设计 简易双通道数字示波器硬件系 统设计 简易双通道数字示波器软件设 计 基于红外探测及超声波报警系 统设计——硬件电路设计 基于红外探测及超声波报警系 统设计——软件系统设计 基于SBDART的辐亮度分析

张福贵 张福贵 张福贵 张福贵

丁继烈

丁继烈

气溶胶对卫星遥感辐亮度的影 响

樊昌元

樊昌元

高炮作业数据采集器手持终端 软件设计

樊昌元

高炮作业数据无线传输电路设 计与实现

樊昌元

高炮作业数据采集器电源充电 电路设计

樊昌元

增量编码器角度测量的倍频电 路设计

樊昌元

高炮作业方位角测量模拟实验 平台设计 红外温度测量电路设计 LPC—10低码率语音声码器的研 究与仿真 7kHz宽带语音子带编码算法的 研究与仿真 基于倒谱的语音信号特性参数 提取算法设计与实现

胡仕兵 胡仕兵

李运洪

李运洪 蒋娟萍 蒋娟萍 蒋娟萍 蒋娟萍 卢会国 卢会国 卢会国 卢会国 卢会国 卢会国

卢会国

王旭

对C波段天气雷达反射率进行衰 减订正的软件设计

王旭

对X波段双偏振天气雷达反射 率进行衰减订正的软件设计

王旭

一种改进的双重频退速度模糊 算法的软件实现

王旭

毫米波天气雷达RHI退速度模糊 算法的软件实现

马尚昌

三种红外地表温度传感器性能 分析

马尚昌

基于ZigBee和光纤的双通信控 制系统硬件设计

马尚昌

基于ZigBee和光纤的双通信控 制系统软件设计

马尚昌

太阳光模拟器设计

马尚昌

光电隔离型接口转换模块设计

马尚昌

以太网光纤收发模块设计

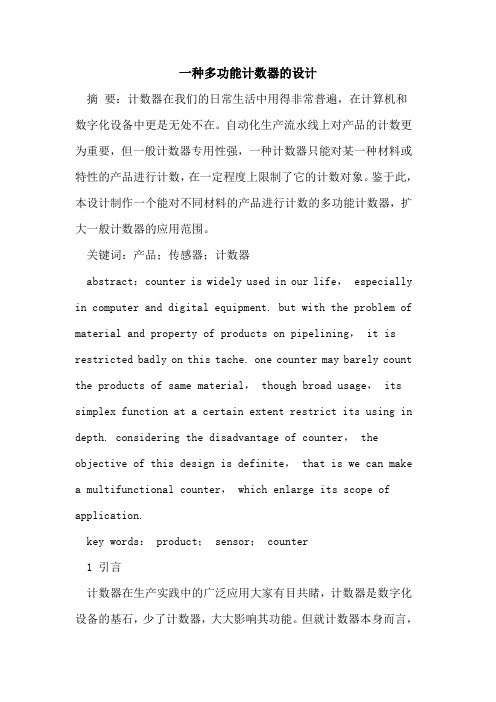

一种多功能计数器的设计

一种多功能计数器的设计摘要:计数器在我们的日常生活中用得非常普遍,在计算机和数字化设备中更是无处不在。

自动化生产流水线上对产品的计数更为重要,但一般计数器专用性强,一种计数器只能对某一种材料或特性的产品进行计数,在一定程度上限制了它的计数对象。

鉴于此,本设计制作一个能对不同材料的产品进行计数的多功能计数器,扩大一般计数器的应用范围。

关键词:产品;传感器;计数器abstract:counter is widely used in our life, especially in computer and digital equipment. but with the problem of material and property of products on pipelining, it is restricted badly on this tache. one counter may barely count the products of same material, though broad usage, its simplex function at a certain extent restrict its using in depth. considering the disadvantage of counter, the objective of this design is definite, that is we can make a multifunctional counter, which enlarge its scope of application.key words: product; sensor; counter1 引言计数器在生产实践中的广泛应用大家有目共睹,计数器是数字化设备的基石,少了计数器,大大影响其功能。

但就计数器本身而言,它的功能单一,限制了它的应用范围,因为它就只拥有一个计数功能。

单片机频率计原理

单片机频率计原理单片机频率计是一种利用单片机进行频率测量的设备。

其原理是通过测量输入信号的周期或频率来计算频率值。

单片机频率计的原理可以简单分为两个主要步骤:信号捕获和频率计算。

首先,信号捕获阶段,单片机需要从外部接收输入信号。

通常情况下,输入信号会经过一个条件放大器,然后进入单片机的输入引脚。

为了确保精确度,输入信号通常需要经过一个低通滤波器,以去除高频噪声。

一旦输入信号进入单片机,接下来就是频率计算阶段。

单片机通过计算输入信号的周期或频率,得出频率值。

常见的计算方法有两种:使用计数器和使用定时器。

使用计数器的方法是通过使用单片机的计数器来测量输入信号的周期或频率。

计数器接收到输入信号后开始计数,直到计数值达到某个预设值或经过一个特定时间长度。

然后,计数器的值将被读取并转换为频率值。

由于计数器的位数有限,所以测量范围也是有限的。

使用定时器的方法是利用单片机的定时器来测量输入信号的周期或频率。

定时器会根据输入信号的上升沿或下降沿来开始和停止计时。

通过测量定时器的值,可以计算出输入信号的周期或频率。

相比于计数器方法,定时器方法相对更精确,也更适合测量高频信号。

无论是计数器方法还是定时器方法,最终都需要将计数器或定时器的值进行一系列的转换以得到最终的频率值。

转换方式可以通过公式计算,也可以通过查表的方式来获得。

在转换过程中,需要考虑到单片机的时钟频率和计数器或定时器的分辨率等因素,以确保测量结果的准确性。

此外,为了提高测量的稳定性和准确性,单片机频率计通常还会采用一些增强技术。

例如,可以使用外部参考时钟来优化计时精度。

还可以进行信号预处理,如去除噪声和滤波等,以提高测量信号的质量。

总结起来,单片机频率计通过测量输入信号的周期或频率来计算频率值。

其中,信号捕获阶段主要是对输入信号进行处理,而频率计算阶段则是通过计数器或定时器来测量信号的周期或频率,并将其转换为最终的频率值。

通过合理的设计和优化,单片机频率计可以实现准确、稳定和高精度的频率测量功能。

频率计的制作实验报告

频率计的制作实验报告实验目的:本实验的目的是通过制作一个简单的频率计,了解频率计的工作原理以及实际应用。

实验仪器与材料:1. 模块化电子实验箱2. 函数信号发生器3. 示波器4. 电压表5. 电阻、电容等基本元件实验原理:频率计是用于测量信号频率的一种仪器。

其基本原理是利用周期性信号的周期长度与频率之间的倒数关系,通过计算周期长度来确定信号的频率。

实验步骤:第一步:搭建电路1. 将函数信号发生器的输出接入电路板上的输入端,作为输入信号源。

2. 将电路板上的元件按照电路图连接,包括电容、电阻等。

确保电路连接正确。

第二步:调试电路1. 将函数信号发生器的频率设置为一个已知的数值,例如1000Hz。

2. 使用示波器测量电路输出端信号的周期长度。

3. 使用计算器计算出信号的频率。

4. 调整电路参数,直到测量到的频率与设定的频率相等。

第三步:验证测量准确性1. 将函数信号发生器的频率调整到其他已知值,例如2000Hz。

2. 重复上述步骤,测量并计算信号的频率。

3. 比较测量到的频率与设定的频率,验证测量准确性。

实验结果与分析:通过实验,我们成功制作了一个简单的频率计。

在调试电路的过程中,我们可以通过测量输出信号的周期长度,并利用频率的倒数与周期长度的关系计算出信号的频率。

通过与设定的频率进行比较,验证了测量的准确性。

实验中可能存在的误差主要来自于电路元件的稳定性以及测量设备的精度。

为了提高测量准确性,可以选择更稳定的元件,并使用更精确的测量设备。

实验结论:本实验通过制作一个简单的频率计,深入了解了频率计的工作原理和实际应用。

通过测量信号的周期长度并计算出频率,我们可以准确地测量信号的频率。

实验结果验证了测量的准确性,并提出了进一步提高准确性的建议。

频率计在电子测量中具有重要的应用价值,可以广泛应用于通信、电子设备维修等领域。

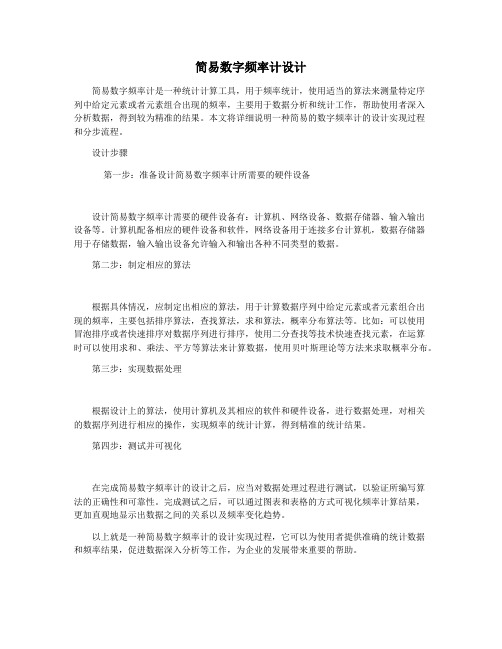

简易数字频率计设计

简易数字频率计设计简易数字频率计是一种统计计算工具,用于频率统计,使用适当的算法来测量特定序列中给定元素或者元素组合出现的频率,主要用于数据分析和统计工作,帮助使用者深入分析数据,得到较为精准的结果。

本文将详细说明一种简易的数字频率计的设计实现过程和分步流程。

设计步骤第一步:准备设计简易数字频率计所需要的硬件设备设计简易数字频率计需要的硬件设备有:计算机、网络设备、数据存储器、输入输出设备等。

计算机配备相应的硬件设备和软件,网络设备用于连接多台计算机,数据存储器用于存储数据,输入输出设备允许输入和输出各种不同类型的数据。

第二步:制定相应的算法根据具体情况,应制定出相应的算法,用于计算数据序列中给定元素或者元素组合出现的频率,主要包括排序算法,查找算法,求和算法,概率分布算法等。

比如:可以使用冒泡排序或者快速排序对数据序列进行排序,使用二分查找等技术快速查找元素,在运算时可以使用求和、乘法、平方等算法来计算数据,使用贝叶斯理论等方法来求取概率分布。

第三步:实现数据处理根据设计上的算法,使用计算机及其相应的软件和硬件设备,进行数据处理,对相关的数据序列进行相应的操作,实现频率的统计计算,得到精准的统计结果。

第四步:测试并可视化在完成简易数字频率计的设计之后,应当对数据处理过程进行测试,以验证所编写算法的正确性和可靠性。

完成测试之后,可以通过图表和表格的方式可视化频率计算结果,更加直观地显示出数据之间的关系以及频率变化趋势。

以上就是一种简易数字频率计的设计实现过程,它可以为使用者提供准确的统计数据和频率结果,促进数据深入分析等工作,为企业的发展带来重要的帮助。

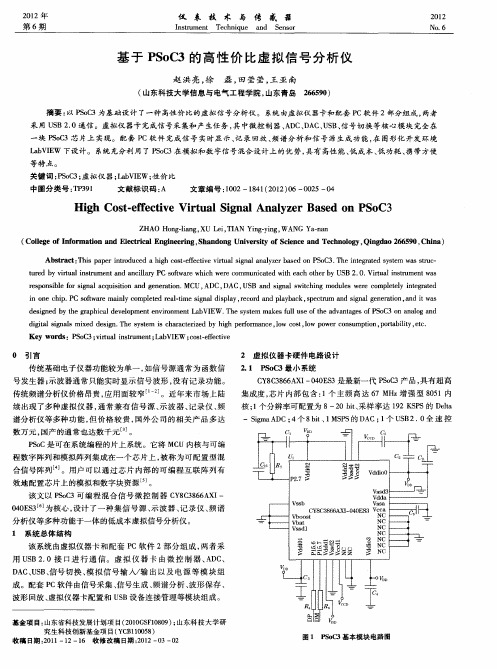

PSOC实现电机转速的检测与控制

PSOC实现电机转速的检测与控制作者:邓燕雯李世涛来源:《中国新技术新产品》2013年第15期摘要:超声波电动机是近年来发展起来的一种新型电机,它的发展和应用离不开超声波电动机的驱动控制技术,并且在很大程度上驱动器的性能决定了超声波电动机的性能。

PSOC (Programmable System-on-Chip)是一款单片片上功率系统,包含丰富的可编程模拟模块,还有专为触摸设计的CapSense模块,内置微处理器和数字模拟外设,是具有真正混合信号处理能力的可编程片上系统。

本文主要介绍了PSOC技术在行波型旋转超声波电动机驱动的直线位移机构步进运动控制系统中的应用。

关键词:PSOC;电机转速;检测与控制中图分类号:F40 文献标识码:A1概述超声波电机是利用压电陶瓷的逆压电效应,把电能转换成弹性体的超声振动,通过摩擦偶合作用获得运动和力(矩)的一款发动机。

由于航空航天器往往处在高真空、极端温度、强辐射等恶劣条件中,且对系统重量要求严苛,而使超声马达成为驱动器的最佳选择,所以超声波电动机在航空航天领域得到广泛的应用。

本文基于行波型旋转超声波电动机设计了一种直线位移机构,想要实现其步进运动控制。

以上功能的实现依托于一款功能强大、高集成度的微处理器,即为PSOC。

2 超声波电动机直线位移机构该机构通过滚珠丝杆,将超声波电动机生成的旋转运动转变为顶杆的直线运动。

如图1所示,该直线位移机构的组成元件为螺母导向座、平键、滚珠丝杠与顶杆,最后是超声波电动机。

将螺母导向座安装在超声波电动机上,超声波电动机输出轴与滚珠丝杠轴由轴销连接,导向座内壁有两个键槽,分别安装了平键,通过平键将丝杠螺母定位在螺母导向座里,由小螺钉将顶杆定在丝杠螺母之上。

通过轴销,电动机输出轴驱动丝杠轴而——旋转,且由平键定位,沿着螺母导向座的轴向方向,滚珠丝杠螺母成直线运动,最后,通过滚珠丝杠螺母,顶杆做往复直线运动。

3 控制系统工作原理如图2所示是早期的超声波电动机控制系统原理框图。

利用PIC单片机CCP模块设计简易数字频率计的C语言程序

第 10章 利用 CCP 模块设计频率计#include <math.h>table[11]={0xc0 ,0xf9,0xa4,0xb0,0x99,0x92,0x82,0XD8 ,0x80,0x90,0xFF} ;//不带小数点的显示段码表const char table0[11]={0X40 ,0X79,0X24,0X30,0X19,0X12,0X02,0X78,0X00, 0X1 0 ,0xFF} ;//带小数点的显示段码表10.5 程序设计 10.5.4 #includ e #includ e 程序清单 <pic.h><stdio.h> //本程序利用 CCP1模块实现一个“简易数字频率计”的功能const charint cp1z[11];cp1 y1;unsignedcharcp1e[2];bank3 union {int //定义一个数组,用于存放各次的捕捉值 }cp1u ;unsigned unsigned unsigned char COUNTW ,COUNT ;char COUNTER , data ,k ;char FLAG @ 0XEF ; //定义一个共用体 //测量脉冲个数寄存器#define FLAGIT(adr ,bit) ((unsigned)(&adr)*8+(bit)) //绝对寻址位操作指令 staticbit FLAG1staticbit FLAG2staticbit FLAG3unsignedintdouble@ FLAGIT(FLAG , @ FLAGIT(FLAG , @ FLAGIT(FLAG , char s[4] ; T5 ,uo ; RE5; puad5; 0); 1); 2); //定义一个显示缓冲数组 double//spi 方式显示初始化子程序void SPIINIT(){PIR1=0;SSPCON=0x30;SSPSTAT=0xC0;〃设置SPI 的控制方式,允许SSP 方式,并且时钟下降沿发送,与"74HC595,当其 //SCLk 从低到高跳变时,串行输入寄存器 "的特点相对应TRISC=0xD7 ; //SDO 引脚为输出,SCK 引脚为输出 TRISA5=0; //RA5 引脚设置为输出,以输出显示锁存信号 FLAG1=0 ;FLAG2=0 ;FLAG3=0 ;COUNTER=0X01 ;}//CCP 模块工作于捕捉方式初始化子程序void ccpint( ){CCP1CON=0X05; T1CON=0X00 ; PEIE=1; CCP1IE=1; TRISC2=1; }//系统其它部分初始化子程序//为保证测试精度,测试 5 个脉冲的参数后//求平均值,每个脉冲都要捕捉其上升、下降沿,//故需要有 11 次中断TRISB1=0;TRISB2=0;TRISB4=1;TRISB5=1; RB1=0;RB2=0; }//SPI 传送数据子程序{SSPBUF=data ; do { }while(SSPIF==0) ;//首先设置 CCP1 捕捉每个脉冲的上升沿 //关闭 TMR1 震荡器//外围中断允许 (此时总中断关闭 ) //允许 CCP1 中断//设置 RC2 为输入void initial( ){COUNT=0X0B ; //设置与键盘有关的各口的输入、输出方式 //建立键盘扫描的初始条件void SPILED(data)//启动发送SSPIF=0;} //显示子程序,显示 4 位数 void display( ){RA5=0 ; //准备锁存for(COUNTW=0 ;COUNTW<4 ; COUNTW++){ data=s[COUNTW] ; data=data&0x0F ;if(COUNTW==k) data=tableO[data]; 〃第二位需要显示小数点 else data=table[data];SPILED(data); }for(COUNTW=0 ; COUNTW<4 ; COUNTW++){ data=0xFF ; SPILED(data); }RA5=1; } //键盘扫描子程序 void keyscan( ) {if((RB4==0)||(RB5==0)) else FLAG1 = 0 ;}//键服务子程序{ PORTB=0XFD ;if(RB5==0) data=0X01;if(RB4==0) data=0X03;PORTB=0XFB ;if(RB5==0) data=0X02;if(RB4==0) data=0X04; PORTB=0X00; if(data==0x01) { COUNTER=COUNTER+1 ; if(COUNTER>4)COUNTER=0x01 ; 〃若COUNTER 超过 4,则又从 1 计起void keyserve()//发送显示段码//连续发送 4个 DARK ,使显示好看一些 //最后给一个锁存信号,代表显示任务完成 FLAG1=1 ;//若有键按下,则建立标志 FLAG1//若无键按下,则清除标志 FLAG1//以上确定是哪个键按下//恢复 PORTB 的值//若按下 S9 键,则 COUNTER 加 1} if(data==0x02) { COUNTER=COUNTER-1 ; //若按下 S11 键,则 COUNTER 减 1 if(C0UNTER<1) COUNTER=0x04 ; 〃若 COUNTER 小于 1, } if(data==0x03) FLAG2=1 ; if(data==0x04) FLAG2=0 ; } //中断服务程序 void interrupt cp1int(void) {CCP1IF=0; cp1u.cp1e[0]=CCPR1L ; cp1u.cp1e[1]=CCPR1H ; cp1z[data]=cp1u.y1;CCP 1CON=CCPICONTOXOI ;data++;COUNT--;} //周期处理子程序//若按下 S10 键,则建立标志 //若按下 S12 键,则清除标志 //清除中断标志 则又循环从 4 计起 FLAG2 FLAG2 //存储 1 次捕捉值 //把 CCP1 模块改变成捕捉相反的脉冲沿 void PERIOD( ){T5=cp1z[1O]-cp1z[O] ;RE5=(double)T5;RE5=RE5/5;}//频率处理子程序 //求得 5 个周期的值 //强制转换成双精度数 〃求得平均周期,单位为卩s void FREQUENCY( ) {PERIOD( );RE5=1OOOOOO/RE5;//先求周期 //周期值求倒数,再乘以 1 000 000,得频率, //单位为 HZ }//脉宽处理子程序void PULSE( ) {int pu ;for(data=0, puad5=0;data<=9;data++) {pu=cp1z[data+1]-cp1z[data];puad5=(double)pu+puad5;data=data+2;}RE5=puad5/5;}//占空比处理子程序//求得5 个脉宽的和值//求得平均脉宽void OCCUPATIONAL( ) {PULSE( );puad5=RE5;PERIOD();RE5=puad5/RE5;} //主程序//先求脉宽//暂存脉宽值//再求周期//求得占空比main( ) {SPIINIT( ) ;while(1) { ccpint();initial() ;if(FLAG2==0) { s[0]=COUNTER ;s[1]=0X0A ;s[2]=0X0A ;s[3]=0X0A ;} display( );keyscan();data=0x00;TMR1H=0 ;TMR1L=0 ;CCP1IF=0;//SPI 方式显示初始化//CCP 模块工作于捕捉方式初始化//系统其它部分初始化//第一个存储COUNTER 的值//后面的LED 将显示"DARK"//调用显示子程序//键盘扫描//存储数组指针赋初值ei( );TMR1ON=1 ;while(1){if(COUNT==0)break ;//定时器1清0//清除CCP1 的中断标志,以免中断一打开就进入//中断//中断允许//定时器1 开//等待中断次数结束//禁止中断//关闭定时器//键盘扫描//若确实有键按下,则调用键服务程序 //如果没有按下确定键,则终止此次循环, //继续进行测量 //如果按下了确定键,则进行下面的数值转换和显示工作 if(COUNTER==0x01) FREQUENCY() ; //COUNTER=1 ,则需要进行频率处理 if(COUNTER==0x02) PERIOD() ;//COUNTER=2 ,则需要进行周期处理 if(C0UNTER==0x03) OCC UP A TIONAL() ; //COUNTER=3,则需要进行占空比处理 if(COUNTER==0x04) PULSE() ;k=5;if(RE5<1){RE5=RE5*1000;k=0x00;if(RE5<10){RE5=RE5*1000;k=0x00; if(RE5<100){RE5=RE5*100;k=0x01 ;if(RE5<1000){RE5=RE5*10;k=0x02;RE5=RE5;uo=(int)RE5;sprintf(s , "%4d" , uo);display(); } di(); TMR1ON=0 ; keyscan(); if(FLAG1==1) keyserve() ; if(FLAG2==0) continue//COUNTER=4 ,则需要进行脉宽处理 } else } else } else } else〃若RE5<10,则乘以1 000,保证小数点的精度 〃若RE5<100,则乘以100,保证小数点的精度 〃若RE5<1000,则乘以10,保证小数点的精度 〃把需要显示的数据转换成 4位ASII 码,且放入数//组 S 中〃若RE5<1,则乘以1 000,保证小数点的精度。

数字频率计的设计实验报告

数字频率计的设计实验报告实验名称:数字频率计的设计实验日期:2021年7月1日实验目的:设计并实现一个基于计数器的数字频率计,使用计数器测量输入信号的频率,并将结果显示在数码管上。

实验器材:FPGA开发板、数字频率计模块、计数器模块、数码管模块。

实验原理:1. 计数器模块设计一个计数器模块,用于计数示波器输入脉冲信号的时间。

计数器的计数时间可以根据需要进行调整。

2. 数字频率计模块设计一个数字频率计模块,用于将计数器的计数时间转换为输入信号的频率。

通过计算计数器的计数值来计算频率,并将结果显示在数码管上。

3. 数码管模块设计一个数码管模块,用于将数字频率计模块计算出的频率值转换为可以在数码管上显示的数码。

实验步骤:1. 搭建实验电路将FPGA开发板连接到计数器模块、数字频率计模块和数码管模块。

2. 编写Verilog代码根据上述原理,编写计数器模块、数字频率计模块和数码管模块的Verilog代码。

3. 编译代码并下载到FPGA开发板使用Xilinx Vivado软件将Verilog代码编译成比特流文件,并将比特流文件下载到FPGA开发板中。

4. 测试实验将示波器的输出信号连接到数字频率计的输入端,并将数字频率计连接到数码管。

通过计算数字频率计的输出,验证数字频率计的测量准确性。

实验结果:经过测试,数字频率计的测量准确度在实验误差范围内。

输入不同频率的信号时,数码管能够正确显示频率值。

实验总结:通过本次实验,成功设计并实现了一个基于计数器的数字频率计。

该实验不仅巩固了计数器、数码管等模块的设计知识,也提高了学生的Verilog编程能力。

在实验中,学生还学习了如何使用FPGA开发板进行数字电路实验,以及测试和验证数字电路的方法和技巧。

基于PSoC3的高性价比虚拟信号分析仪

相加 ) 以满足 P o 3芯片 I0输 入电压范围的要求 。2个高速 , SC /

运算放大器 O 3 G构 建了一个 截止 频率 为 2 H 、 P7 0k z 四阶有 源抗 混叠滤波器 , 用来 完成输入通道的滤波。

23 输 出通 道 电 路 .

图 3为一路 输 出通道 电路 图 , 他 3路 输 出通 道完 全 相 其

ZH AO n -ing, Ho g la XU i TI Le , AN n — i g, ANG — a Yi g y n W Ya n n

( l g f nomaina dEeti l n ier g S a d n nvri f c n ea dT cn l y Q n d o2 6 9 , hn ) Co eeo fr t n l r a gn ei ,h n o gU ies yo i c n eh oo , ig a 65 0 C ia l I o c c E n t Se g

压幅值范 围为 一 5 2 0~+20 V; 二波段 , 对输 入信 号进 行 5 第 不 任何增益变换 , 测量 电压 幅值 范 围为 一25+2 5V; 三波段 , . . 第 利用仪表放大器 A 6 0对输入信号增益进行 10倍放大 , D2 0 可细 致观 察 幅值 范 围 为 一2 5~ +2 V微 弱 电压 信 号 。双 运 放 5m L 33 F 5 D构建 的电压缓 冲器 和极性 变换 电路 , 来提 高输 入阻 用 抗 和将输 入 的双 极性信号 变为单 极性信号 ( . V基准 电压 与2 5

一

块 P o 3芯 片上 实现。配套 P SC c软件 完成信 号 实时显示 、 录回放 、 记 频谱 分析和信 号源生 成功能 , 图形 化开发环 境 在

基于cpld的简易数字频率计的设计

基于cpld的简易数字频率计的设计

基于CPLD的简易数字频率计的设计如下:

首先,将CPLD作为主控芯片,实现信号的采集、处理和控制。

通过输入的信号,经过滤波器去除噪音和干扰,然后使用计数器模块对输入信号的频率进行测量。

计数器模块将信号的周期转换成相应的脉冲数,再通过单片机进行数据处理,计算出信号的频率。

其次,利用单片机进行数据处理和显示。

单片机通过接收计数器模块的脉冲数,根据测量公式计算出信号的频率,并将结果显示在LCD屏幕上。

同时,单片机还负责控制CPLD的工作流程,实现整个系统的协调工作。

最后,通过仿真和测试验证设计的正确性和可行性。

测试结果表明,该数字频率计具有测量精度高、抗干扰能力强、稳定性好等优点,可以广泛应用于各种需要测量频率的场合。

基于CPLD的简易数字频率计的设计方法包括硬件设计和软件设计两部分。

硬件设计主要是利用CPLD和单片机等芯片进行电路设计和搭建;软件设计主要是利用CPLD编程语言和单片机编程语言进行程序编写和调试。

在实际应用中,需要根据具体需求和条件进行选择和调整。

频率计资料

频率计频率计是一种用于测量信号频率的仪器,广泛应用于各种领域,包括电子、通信、电力等。

频率计的原理是利用输入信号的周期或脉冲数来计算其频率,从而实现频率测量。

本文将介绍频率计的工作原理、分类、应用及未来发展方向。

工作原理频率计主要通过计算输入信号的周期或脉冲数来确定其频率。

一般来说,频率计可以分为两种类型:数字频率计和模拟频率计。

数字频率计通过将输入信号转换为数字形式,并利用计数器来计算周期或脉冲数。

随着技术的进步,数字频率计在精度和稳定性方面有了显著提高,逐渐成为主流。

模拟频率计则通过比较输入信号与参考信号,利用锁相环等电路来测量频率。

尽管模拟频率计在某些特定应用中仍具有优势,但受限于精度和稳定性较差,逐渐被数字频率计所替代。

分类根据测量范围和精度的不同,频率计可以分为基本频率计和精密频率计。

基本频率计通常用于测量工程中的常用频率范围,如电力系统中的50Hz/60Hz,通信系统中的几百kHz至几GHz等。

这类频率计具有成本低、易操作等特点,适用于大多数应用场景。

精密频率计则用于对频率要求更高的领域,如科学研究、航空航天等。

这类频率计具有更高的精度、稳定性和抗干扰能力,在特定场合中得到广泛应用。

应用频率计作为一种关键的测量仪器,在各个行业都有着重要的应用。

在电力系统中,频率计用于监测电网频率的稳定性,保障电网运行的安全可靠。

在通信系统中,频率计用于测量无线信号的频率,确保通信系统正常工作。

在科学研究中,频率计用于实验室中各种信号的频率测量,为科学家们提供准确的数据支持。

未来发展随着科学技术的不断进步,频率计也在不断发展和完善。

未来,随着5G技术的广泛推广,对高频率、高精度频率计的需求将进一步增加,频率计将朝着更加智能、精准、高效的方向发展。

另外,随着人工智能技术的不断成熟,频率计的自动化、智能化程度也将得到提升,从而进一步提高频率测量的精度和效率。

总的来说,频率计作为一种重要的测量仪器,将在未来的科技发展中继续发挥重要作用,并不断适应各种新的应用场景,为人类的科学研究和生产生活带来更多的便利和效益。

如何设计一个简单的频率计

如何设计一个简单的频率计频率计是一种用于测量信号频率的设备,广泛应用于电子、通信、自动化等领域。

本文将介绍如何设计一个简单的频率计,并提供相关原理和步骤。

一、简介频率计是一种测量频率的仪器。

它可以通过测量信号周期的时间来计算频率。

频率计可以根据测量的频率范围和精度要求,选择不同的设计方案。

下面将介绍一种简单的频率计设计。

二、设计原理该频率计设计基于计数器原理。

其思想是通过计数已知时间内信号周期的脉冲数来确定频率。

三、所需元器件1. 计数器芯片:选择适合频率范围的计数器芯片。

2. 晶振:提供稳定的时钟信号作为计数器的时基。

3. 预处理电路:用于处理输入信号,确保其满足计数器的输入要求。

四、设计步骤1. 确定测量范围和精度要求:根据应用需求确定频率计所需要测量的频率范围和精度要求,选择合适的计数器芯片。

2. 选择计数器芯片和晶振:根据测量范围和精度要求,选择适合的计数器芯片和晶振。

计数器芯片的型号选择要能满足测量范围,并具有足够的计数位数。

晶振的频率要足够稳定。

3. 设计输入信号预处理电路:根据计数器芯片的输入要求,设计合适的输入信号预处理电路。

例如,如果输入信号幅值过大或过小,需要进行合适的电平转换或调整。

五、连接设计1. 将输入信号接入预处理电路,确保信号满足计数器芯片的输入要求。

2. 将预处理后的信号接入计数器芯片的计数端。

3. 将晶振连接至计数器芯片的时钟输入端。

4. 连接供电电源,确保设计正常工作。

六、测试与调试1. 给设计供电,确保所有连接正确。

2. 输入已知频率的信号,观察频率计是否能准确测量。

3. 如果测量结果不准确,检查元器件连接是否正确、晶振频率是否稳定等。

4. 根据实际情况调整设计参数,直至测量结果满足要求。

七、注意事项1. 设计中要注意信号的幅值范围和频率范围。

2. 选择合适的计数器芯片和晶振,以保证测量精度和稳定性。

3. 调试时要注意设计的连通性和元器件的正确连接。

八、总结设计一个简单的频率计需要确定测量范围和精度要求,选择适合的计数器芯片和晶振,并设计合适的输入信号预处理电路。

基于FPGA的简易数字频率计

基于FPGA的简易数字频率计第一篇:基于FPGA的简易数字频率计EDA 简易数字频计设计性实验 2008112020327 ** 电子信息科学与技术物电电工电子中心2009年5月绘制2008.6.10 湖北师范学院电工电子实验教学省级示范中心电子版实验报告简易数字频率计设计一.任务解析通过对选择题的分析,认为该简易数字频率计应该能达到以下要求:1.准确测出所给的方波信号的频率(1HZ以上的信号)。

2.在显示环节上,应能实现高位清零功能。

3.另外还有一个总的清零按键。

二.方案论证本实验中所做的频率计的原理图如上图所示。

即在一个1HZ时钟信号的控制下,在每个时钟的上升沿将计数器的数据送到缓冲器中保存起来,再送数码管中显示出来。

第2页,共11页湖北师范学院电工电子实验教学省级示范中心电子版实验报告在本实验中,用到过几中不同的方案,主要是在1HZ时钟信号的选择和计数器清零环节上:1.在实验设计过程中,考滤到两种1HZ时钟信号其波形如下图所对于上术的两种波形,可以调整各项参数来产生两种1HZ时钟信号。

最后通过实验的验证发现第二种波形对于控制缓冲器获得数据和控制计数器清零更易实现。

并且,用第二种波形做为时钟信号,可以在很短的高电平时间内对计数器清零,在低电平时间内让计数器计数,从面提高测量的精度。

而用第一种波形则不易实现这个过程。

2.在计数器的清零过程中,也有两个方案,分别是能通过缓冲器反回一个清零信号,另一个是在时钟的控制下进行清零。

最终通过实验发现,用时钟进行清零更易实现。

因为如果用缓冲器反回一个清零信号,有一个清零信号归位问题,即当缓冲器反回一个低电平清零信号时,计数器实现清零,但不好控制让缓器冲的清零信号又回到高电平,否则计数器就一直处于清零状态面不能正常计数了。

三.实验步骤通过上分析后,实验分为以下几步:1.1HZ时钟信号的产生(产生该信号的模块如下):module ones(clk,clkout);input clk;output clkout;parameter parameter N=24000000;n=24;第3页,共11页湖北师范学院电工电子实验教学省级示范中心电子版实验报告reg [n:0]cnt;reg clkout;always @(posedge clk)begin if(cnt==N)else end endmodule begin cnt=0;clkout=1;clkout=0;endend begin cnt=cnt+1;最终产生的信号的波形:2.计数模块。

频率计的发展简介

频率计的发展简介频率计是一种用于测量信号频率的仪器。

它广泛应用于电子、通信、无线电、自动化控制等领域。

本文将对频率计的发展历程进行简要介绍。

一、频率计的起源频率计的起源可以追溯到19世纪末。

当时,无线电通信技术刚刚兴起,人们迫切需要一种能够准确测量信号频率的仪器。

最早的频率计是基于机械振荡器的,通过机械振荡器的频率与待测信号频率进行比较来实现测量。

二、频率计的发展过程1. 早期机械频率计早期的频率计主要采用机械振荡器和机械计数器的组合。

机械振荡器通过机械共振实现稳定的振荡频率,机械计数器则通过机械传动实现频率计数。

这种频率计具有测量范围窄、精度低的特点,但在当时仍然是一种重要的测量工具。

2. 电子频率计的浮现20世纪初,随着电子技术的发展,电子频率计开始浮现。

电子频率计利用电子元件的特性来实现频率测量,具有测量范围广、精度高、稳定性好的优点。

电子频率计的浮现极大地提高了频率测量的准确性和可靠性。

3. 数字频率计的应用随着计算机技术的发展,数字频率计逐渐取代了传统的摹拟频率计。

数字频率计利用数字信号处理技术对输入信号进行采样和处理,通过数学算法计算出信号的频率。

数字频率计具有测量速度快、精度高、灵便性强的特点,广泛应用于科研、工业生产等领域。

4. 频率计的功能扩展随着科技的进步,频率计的功能也得到了不断扩展。

现代频率计不仅可以测量信号的频率,还可以测量相位、脉宽、占空比等参数。

一些高级频率计还具备频谱分析、信号发生器、计时功能等,满足了不同领域对频率测量的需求。

三、频率计的应用领域频率计广泛应用于电子、通信、无线电、自动化控制等领域。

在电子领域,频率计常用于测量电路中的振荡频率、时钟频率等。

在通信领域,频率计用于测量无线电信号的频率、调制频率等。

在自动化控制领域,频率计用于测量机电转速、控制系统的频率响应等。

四、频率计的发展趋势随着科技的不断进步,频率计的发展也呈现出以下几个趋势:1. 小型化:随着集成电路技术的进步,频率计体积越来越小,便于携带和使用。

第10章 利用CCP模块设计频率计

PIC单片机实验室

北邮世纪学院电子与自动化系

2

CCP1、CCP2

• 内置了两个CCP模块,CCP1\CCP2,这两个模块在 使用上,其动作方式与功能很相近,引脚如图所示: RC2\RC1

PIC单片机实验室

北邮世纪学院电子与自动化系

3

捕捉、比较、PWM

1、捕捉指的是侦测引脚上输入信号的状态,当信号的变 化符合预先设定的条件(上升沿或下降沿),产生中断, 并记录当前的定时器值。与TMR1配合,是16位的。 • 2、比较是将事先设定好的值与定时器的值相互比较,一 旦两个值相等,就产生中断并驱动事先设定好的动作。与 TMR1配合,是16位的。

PIC单片机实验室

北邮世纪学院电子与自动化系

17

10.4 设计与测量原理

t1 时 刻 捕 捉 T M R 1 1

t1

t2

t3

t3 时 刻 捕 捉 T M R 1 3

t2 捕 捉 T M R 1 2

t1时刻以前,把CCP1设置成捕捉上升沿;当上升沿到来时,CCP中断, 捕捉此时TMR1寄存器中16位的值TMR11, 把CCP1再设置成捕捉下降沿,当t2下降沿到来时,CCP中断,捕捉此时 TMR1寄存器中16位的值TMR12, 把CCP1再设置成捕捉上升沿,当t3时刻下降沿到来时,CCP中断,捕捉 此时TMR1寄存器中16位的值TMR13。 则: 信号的周期T=TMR13—TMR11 us 脉冲宽度Tp=TMR12—TMR11 us 信号的频率f= 1/T 占空比D=Tp/T *100%

PIC单片机实验室

北邮世纪学院电子与自动化系

18

如何提高测量频率

• 特别注意: • 2次中断的时间间隔必须大于一次中断服务的执行时间; • 本题需要测量的最高频率为1000HZ,周期时1000us,且占 空比的变化范围是10%--90%,则高电平持续的最短时间 100us 是:100us。可以由充分的中断服务时间。 • 如果实际应用中发现两次捕捉中断的时间间隔小于中断服 务时间,则可以设置CCP1CON的值,时ccp模块每4个脉 冲上升沿捕捉1次,或16个脉冲捕捉一次 • 要么把被测信号进行分频。

基于DSP的简易数字频率计

基于DSP的简易数字频率计* 本作品获得2008年德州仪器(TI) C2000 DSP大奖赛命题组一等奖,并得到合肥工业大学2008年大学生创新性实验计划项目的资助作品的意义与概况随着微电子技术和计算机技术的飞速发展, 各种电子测量仪器在原理、功能、精度及自动化水平等方面都发生了巨大的变化, 特别是DSP技术诞生以后,电子测量技术更是迈进了一个全新的时代。

近年来,DSP逐渐成为各种电子器件的基础器件,逐渐成为21世纪最具发展潜力的朝阳行业,甚至被誉为信息化数字化时代革命旗手。

在电子测量技术中,频率是最基本的参数之一,它与许多电参量和非电量的测量都有着十分密切的关系。

例如,许多传感器就是将一些非电量转换成频率来进行测量的,因此频率的测量就显得更为重要。

数字频率计是用数字来显示被测信号频率的仪器,被测信号可以是正弦波、方波或其它周期性变化的信号。

数字频率计广泛采用了高速集成电路和大规模集成电路,使得仪器的体积更小、耗电更少、精度和可靠性更高。

而传统的频率计测量误差较大,范围也较窄,因此逐渐被新型的数字频率计所代替。

基于DSP的等精度频率计以其测量准确、精度高、方便、价格便宜等优势将得到广泛的应用。

我们设计的简易数字频率计在未采用任何门控器件控制的情况下,在很宽的范围内实现了等精度频率测量,0.5Hz~10MHz的范围内测量方波的最大相对误差小于2e-6,测量正弦波的最大相对误差小于3.5e-5;结果通过RS232通讯显示在计算机上,可以很方便地监测数据。

方案设计总体介绍传统的等精度测频法使用门控器件产生门控信号,从而实现实际门闸信号与被测信号同步,消除对被测信号计数产生的一个脉冲的误差,其原理图如图1所示。

图1 传统的等精度测量原理由硬件控制计数的门闸时间,当预置们信号(即定闸门信号)为高电平时,基准信号计数器CNT1和被测信号计数器CNT2并不启动,而是等被测信号的上升沿来到时才同时开始计数;当预置们信号为低电平时,两个计数器并不马上关闭,同样要等到被测信号上升沿来到后再关闭;于是,实际闸门时间就是被测信号周期的整数倍,从而实现了闸门与被测信号的同步。

基于等精度测量与spi传输协议的简易频率计

电子系统设计综合报告选题: 简易频率计成员:学号:专业: 电子信息科学与技术时间: 2014.7.23目录一绪论-------------------------------------------------------------------------- 41.1测量原理-------------------------------------------------------------------- 41.1.1等精度测量--------------------------------------------------------- 41.1.2SPI协议-------------------------------------------------------------- 41.2系统指标-------------------------------------------------------------------- 5 二硬件电路-------------------------------------------------------------------------- 62.1 系统设计-------------------------------------------------------------------- 62.2 FPGA逻辑模块------------------------------------------------------------- 62.3 单片机数据接收模块---------------------------------------------------- 72.4 波形变换电路-------------------------------------------------------------- 7 三软件设计-------------------------------------------------------------------------- 93.1 编译环境--------------------------------------------------------------------- 93.2 VHDL语言-------------------------------------------------------------------- 93.3 FPGA顶层设计------------------------------------------------------------- 93.4 FPGA仿真波形-------------------------------------------------------------123.5 ATmega16单片机编程---------------------------------------------------13 四系统测试-------------------------------------------------------------------------154.1 等精度测量理论分析---------------------------------------------------154.2 实验测量数据-------------------------------------------------------------15 五结束语---------------------------------------------------------------------------16摘要本设计利用FPGA进行测频计数, 单片机实施控制实现频率计的设计过程.该频率计利用等精度的设计方法, 克服了基于传统测频原理的频率计的测量精度随被测信号频率的下降而降低的缺点. 等精度的测量方法不但具有较高的测量精度,而且在整个频率区域保持恒定的测试精度.设计中用一块FPGA芯片(型号为CycloneⅡ的EP2C5T144C8N)完成各种时序逻辑控制,计数功能. 在QuartusⅡ平台上,用VHDL语言编程完成了FPGA的软件设计,编译,调试,下载. 使用Modelsim软件对程序进行仿真与时序及信号的分析.用ATmega16单片机作为系统的主控部件,实现整个电路的测试信号接收,数据运算处理和显示输出. 系统将单片机的控制灵活性及FPGA芯片的现场可编程性相结合, 不但大大缩短了开发研制周期, 而且使本系统具有结构紧凑, 可靠性高, 测频范围宽, 精度高等优点.关键字: FPGA, ATmega16, VHDL, 等精度测量, spi总线协议一 绪论1.1 测量原理1.1.1 等精度测量等精度测量原理用以下结构图进行说明:图1-1 等精度测量频率计结构图如结构图所示, 计数器A, 计数器B 分别用于记录待测信号fx 与基准时钟信号clk 的高低电平跳变次数, 门限信号与待测信号fx 通过D 触发器分别通过计数器A,B, 以达到clk 与fx 在相同时间开始计数的目的,门限信号可设定计数器的计数时间, 为1s~10s.当待测信号频率较低时, 应适当地上调门限信号的持续时间, 以增加fx 的计数次数, 提高精确度.当一次计数完毕后, 依次将计数器A,B 数据存入64位寄存器内,待传送至单片机进行数据处理.假定计数器A 在门限时间内计数为NA, 计数器B 技术为NB,已知基准时间信号的频率为fclk,则待测信号fx 频率为 fx=(NA/NB)*fclk,由于NB 十分大,因此误差很小, 消除了直接测量法的±1误差问题.1.1.2 SPI 协议SPI, 是英语Serial Peripheral Interface 的缩写, 顾名思义就是串行外围设备接口.SPI,是一种高速的, 全双工, 同步的通信总线, 并且在芯片的管脚上只占用四根线, 节约了芯片的管脚, 同时为PCB 的布局上节省空间, 提供方便,正是出于这种简单易用的特性, 现在越来越多的芯片集成了这种通信协议.SPI 是一个环形总线结构,由ss, sck, mosi, miso 构成,其时序其实很简单,主要是在sck 的控制下, 两个双向移位寄存器进行数据交换.当主从机之间进行单向传输时, 以主机向从机传输为例, 只需使用ss, sck, mosi 三根总线.64位寄存器D 触发器1s~10s 可调门限信号待测信号fxFPGA 分频产生10MHZ 基准时钟信号32位计数器A32位计数器B(1)mosi 主设备数据输出;(2)miso 主设备数据输入;(3)sck 同步时钟信号;(4)ss 从设备使能信号.ss为使能信号, 只有当ss有效时, 才可以实现双机通信. 当ss为有效信号时(高低电平由用户及硬件决定), 通信由sck, mosi, miso进行, mosi与miso根据sck提供的时钟脉冲进行数据传输, 数据输出通过mosi传输, 数据在时钟的上升沿或下降沿跳变, 在紧接着的下降沿或上升沿将数据读入8位移位寄存器, 完成一位数据的传输, 经过8个sck时钟脉冲后完成8位数据的的读取, 此时令ss使能信号无效, 接收机将不再读取信号, 至此完成一次数据的传输.图1-2 spi串行传输数据波形示例图1-2中, sck卫同步时钟, mosi为主机向从机发送数据, 使能信号为ssmark, 高电平有效, 当sck到达上升沿, 从机进行数据的读取, 读取结果为8位2进制数00110001.引脚SPI主机SPI从机MOSI 用户定义输入用户定义输入MISO 输入用户定义输入用户定义SCK 用户定义输入用户定义输入SS 用户定义输入用户定义输入1.2系统指标(1)在0.1Hz~10MHz 测试误差0.01%(最大闸门时间≤10s)条件下,进行大信号(信号幅度:0.5V~5V)的频率测量. 十进制数字显示,显示刷新时间1~10 秒连续可调.(2)在1Hz~1MHz 范围内及测试误差≤0.1%的条件下,进行小信号的频率测量.二硬件电路2.1 系统设计等精度测量频率计涉及加,减,乘,除运算,由于运算量大考虑到资源的消耗,本设计使用单片机与FPGA相结合的方案, 系统结构图如下所示, FPGA进行测频计数,单片机进行运算以及显示.图2-1 系统总体结构图系统主要部分功能如下:1.波形变换电路: 将输入信号转换成FPGA能够正确识别的信号;2.FPGA: 作为SPI主机对待测信号与基准时钟进行计数,使用3个IO口分别输出使能信号ss, 同步时钟sck以及存有计数器A, B数值的64位数, 进行SPI数据发送;3.ATmega16单片机: 作为SPI从机, 利用引脚PB7,PB5,PB4的第二功能, 对sck,mosi, ss进行接入, 实现数据传送, 接收到的前32位数与后32位数分别保存, 计算两者比值, 再与基准频率10mhz相乘的测得频率. 再通过其他引脚连接1602显示器, 将测得频率显示在1602显示器上.2.2 FPGA逻辑模块FPGA数据流图如下:图2-2 数据流图信号输入整形放大电路FPGA测频计数ATmega16单片机进行数据处理1602显示器数码管显示门限信号时间门限时间设定按键图中SS0, sck, mosi分别输出使能信号, 同步时钟信号以及计数数据,它们分别于AVR单片机的PB4, PB7, PB5口相连, 进行SPI单向数据传输.2.3 单片机数据接收模块ATmega16是基于增强的AVR RISC结构的低功耗8 位CMOS微控制器. 由于其先进的指令集以及单时钟周期指令执行时间,ATmega16 的数据吞吐率高达 1 MIPS/MHz,从而可以缓减系统在功耗和处理速度之间的矛盾.ATmega16具有32 个可编程的I/O 口, 其封装包括40引脚PDIP 封装, 44 引脚TQFP 封装, 与44 引脚MLF 封装, 本设计使用了40引脚的PDIP封装, 其引脚图如下.图2-3 ATmega16封装本设计使用了端口B的PB7, PB5, PB4引脚的第二功能, 使ATmega16作为SPI 数据传输中的从机,读取来自FPGA传送的计数数据.2.4 波形变换电路频率计的前置放大电路使用了TI的OPA 690高速运放构成反向比例放大电路对输入信号进行放大,输入端加入电阻电容,滤去杂波. 放大后通过74ls14施密特触发器对波形进行整形,其原理图及PCB图如下.图2-4 放大整形电路原理图图2-5 pcb图三软件设计3.1编译环境本设计FPGA部分使用QUARTUS II 进行程序的编写与烧录, 使用Modelsim 对编写程序进行信号波形的仿真与校对; AVR单片机C语言编程使用ICCV7 FOR AVR , 在线调试使用了AVR Studio.3.2VHDL语言VHDL语言是一种用于电路设计的高级语言. 它在80年代的后期出现. 最初是由美国国防部开发出来供美军用来提高设计的可靠性和缩减开发周期的一种使用范围较小的设计语言 .VHDL翻译成中文就是超高速集成电路硬件描述语言,主要是应用在数字电路的设计中. 它在中国的应用多数是用在FPGA/CPLD/EPLD的设计中. 当然在一些实力较为雄厚的单位,它也被用来设计ASIC.VHDL主要用于描述数字系统的结构,行为,功能和接口. 除了含有许多具有硬件特征的语句外,VHDL的语言形式, 描述风格以及语法是十分类似于一般的计算机高级语言. VHDL的程序结构特点是将一项工程设计,或称为设计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可视部分,及端口)和内部(或称不可视部分),既涉及实体的内部功能和算法完成部分. 在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体. 这种将设计实体分成内外部分的概念是VHDL系统设计的基本点.3.3FPGA顶层设计门限信号时间的设定与显示产生门限信号的描述SPI数据传输同步时钟SCK10mhz基准时钟clk, D触发器, 计数器A, B的描述64位寄存器64~33位保存计数器A数值,32~1位保存计数器B数值,其描述如下寄存器中的数据分8次在不同时刻从高位到低位依次从MOSI发送数据, 每次8位3.4FPGA输出波形仿真为验证程序的正确性, 我们使用Modelsim对程序进行了仿真, 设定待测信号为fx, 频率为2khz.其仿真信号波形如下.图3-1 SPI数据发送波形分析:波形图中, clk为基准时钟, 大小为10mhz, fx为2khz待测信号, sck为SPI 数据传输同步时钟, mosi向AVR单片机数据, SS0为使能信号, 低电平有效.取第二段发送数据分析, 当SS0低电平, 从第一个SCK时钟开始, 单片机在SCK时钟的上升沿从mosi上采数据, 每次1位, 直到8位数据采集完毕, 图3-1中采集数据为00110001, 64位寄存器DataBase中第56~49位数据为00110001, 数据传输正确.下面验证计数器结果的正确性:DataBase中, 64~33位保存着计数器A数值, 32~1位保存着计数器B数值. DataBase数值大小为00000001 00110001 00101101 0000000000000000 00000000 00001111 10100000, 设NA为64~33位32位数, NB为32~1位32位数, 转换为十进制大小NA=20000000, NB=4000, 2khz, 大小与fx相等, 仿真结果正确.3.5ATmega16单片机编程在本设计中, ATmega16用于完成数据的接收, 运算以及显示输出. 由于ATmega16端口B的PB7, PB5, PB4的第二功能为SPI传输的时钟sck, 数据传输mosi以及传输使能, 因此用于SPI从机接收十分便捷, 只须配置SPI控制寄存器SPCR的使能SPE位为1即可.当使能信号SS低电平, 单片机在每个同步时钟的上升沿(默认使用SPI模式0)读取数据, 存至SPI移位寄存器中SPDR中, 当数据发送完毕SPI状态寄存器SPSR的SPI中断标志位SPIF将置1, 故可用SPIF位判断一次传输数据是否完成, 程序流程图见图3-6.图3-2 端口B的第二功能图3-3 SPCR寄存器图3-4 SPDR寄存器图3-5 SPSR寄存器开始1602初始化, SPCR的SPE位置1读数据读取完毕?计算频率计算完毕显示输出图3-6 程序流程图四系统测试4.1 等精度测量理论分析本系统的测频公式为:Fx = ( Fs×Nx ) / Ns[8]其误差分析如下:设所测频率值为Fx,其真实值为Fxe,标准频率为Fs. 在一次测量中,由于Fx 计数的起停时间都是由该信号的上跳沿触发的,在Tpr时间内Fx的计数Nx无误差;此时内的计数Ns最多相差一个脉冲,即|⊿Ns|≤1则:Fx/Nx=Fs/NsFxe/Nx=Fs/(Ns+⊿Ns)由此推得:Fx=(Fs/Ns)×NxFxe=[Fs/(Ns+⊿Ns)] ×Nx根据相对误差公式有:⊿Fxe/Fxe=|Fxe-Fx|/Fxe可以得:⊿Fxe/Fxe=|⊿Ns|/Ns∵|⊿Ns|≤1 ∴|⊿Ns|/Ns≤1/Ns即相对误差⊿Fxe/Fxe≤1/Ns又Ns=Tpr×Fs由此可知:(1)相对测量误差与频率无关;(2)增大Tpr或提高Fs,可以增大Ns,减少测量误差,提高测量精度;(3)本测频系统的测量精度与预置门宽度和标准频率有关,与被测信号的频率无关.4.2 实验测试数据实际频率测试频率门限时间误差0.5hz 0.49hz 2s 2%1hz 0.99hz 1s 1%10hz 9.99hz 1s 0.1%50hz 49.99hz 1s 0.02%100hz 99.99hz 1s 0.01%1khz 999.99hz 1s 0.001%5khz 4999.95hz 8s 0.001%50khz 49999.11hz 8s 0.00178%500khz 499989.90hz 10s 0.00202%1mhz 999981.31hz 10s 0.001869%5mhz 4999989.50hz 10s 0.00021%由于在单片机程序中显示部分仅显示出小数后两位, 因此测得频率误差较大, 实际情况应比测得值小, 随待测信号频率的增加, 测得频率的误差减小, 满足指标.五结束语本设计综合使用QUARTUS II, ICCR7 FOR AVR, Altium Designer, ModeSim, Multisim等EDA软件进行综合的软硬件设计与仿真调试, 各项功能基本上达到了系统指标, 但由于硬件设计上的经验和储备知识的不足, 对正弦波, 三角波等信号的测频上限不尽人意, 日后必定加以练习, 查漏补缺.简易频率计实物图。

基于PSoC芯片的两路高精度频率测量系统设计

基于PSoC芯片的两路高精度频率测量系统设计赵浩;吴斌【期刊名称】《电子设计工程》【年(卷),期】2014(000)015【摘要】In order to improve measure accuracy and broaden the frequency range, a frequency measure system of two-channel signal based on PSoC is proposed. The core processing unit of this system is CY8C29666. Based on the synchronous multi-cycle frequency measurement, and combined with the advantages of high integration, resourceful, flexible configuration and anti-jamming stability PSoC chips, the system performed high accuracy frequency measure of two-channel signal between 0.1 Hz~10M Hz. Based on the results, the measure accuracy is analyzed.%针对在脉冲频率测量中,测量精度低、频率范围窄等问题,提出了一种基于PSoC芯片的两路信号频率测量系统。

采用PSoC芯片CY8C29666作为系统核心,以改进的多周期同步测频法为理论基础,结合PSoC芯片集成度高、系统资源丰富、配置灵活、稳定抗干扰的优点,实现了对0.1 Hz~10 MHz之间两路信号频率的高精度测量,并结合实验结果进行了精度分析。

【总页数】3页(P174-176)【作者】赵浩;吴斌【作者单位】西北机电工程研究所陕西咸阳 712099;西北机电工程研究所陕西咸阳 712099【正文语种】中文【中图分类】TM935.1【相关文献】1.基于PSoC+CPLD的高精度位置伺服控制系统设计 [J], 张世文;2.高精度频率测量系统设计与实现 [J], 王勋3.CY8C29666芯片的高精度频率测量系统设计 [J], 赵浩;纪平鑫;周加永;李会营;吕启元4.基于DSP和CPLD的高精度频率测量系统设计 [J], 席鹏;李军;於二军5.基于IEEE1588时间同步的分布式桥梁健康监测系统基于BQ76pl455高精度电压采集芯片的储能电池管理系统设计 [J], 李雄伟;季钰林;谢伊亮;陈永强;李英祥因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

以通过软件设 计直接 用十进制 数字显示 被测信 号频率 。

输入 l

— — —

_ .

2 系统 总体构

频率计工作时 , 先要产生一个计数允许信号, 即 闸门信号, 闸门信号高电平的宽度为单位时间 , 例如

文章 编 号 :17 —72 2 0 )60 2 —4 6 114 (0 80 —6 20

利 用 P o 实 现 频 率 计 SC

李 玉 丽 , 徐 家 品, 张俊 霞

( 四川 大学 电子信 息 学院 , 四川 成都 60 6 ) 104

摘要 : 频率计 的设计以 P _ C 82 462 P XI S, Y C 9 6 —4 V 为核心 , C 由内部模块与外部 电路 的组合 成其硬件 电路 , 软件 设计采用 C语言 。设计包括信号处理 、 定时器计数及数据显示 3个 主要部分 , 以实现对信号频率 的测 定。由于 可 设计 中采用了分频 , 而且在 P 【 S) C中定时器最 多可 以达 3 2位 , 以频率范围比 8位的单片定时器测得要广。 所

第2 3卷第 6期

20 0 8年 l 2月

成

都

信

息

工

程

学

院

学

报

Vo .3 No. 12 6

De e.2 0 08

J OUR L 0F C N DU NI R I 0 MA ON T C 0L Y NA HE G U VE S TY 0F I NF R TI E HN oG

电路 ; 活的片上存储 器 ,K字节 Fah程序存储 ,0 0 0次擦写 ,5 字 节 S A 数据存 储 _ ; 灵 4 l s 5 ,0 26 R M J 可编程 的引脚配

置, 所有 的 G I 5 PO 2mA驱动 , 上拉 、 下拉 、 高阻 、 强力及 开路驱动模 式 ; 它 系统资 源 , 门狗 和 睡眠定 时器 等 ; 其 看 完 善的开 发工具 , 费的开放软 件 P o ei e, 免 S CD s nr利用 IE C b( g C — ue在线仿真 器 ) 实现 在线仿真 和调试 。 该 系列单 片机 与传统单 片机 的根 本 区别在 于 内部 集成 了可 配置性 编程 的数字 模块 和模 拟模 块 , 开发者 可 以 根据不 同设计 要求调 用相应 的数字模 块和模拟模 块 , 成芯 片 内部 的功 能设计 ; 完 实现使用 一块 芯片就 可以配置成 具有多种不 同外 围元 器件 的微 控制器 , 建立一 种可配置 嵌入式 微控制器 ; 以实 现从确定 系统 功能开始 , 用 到软件 /

信号预 处理 卜 定时计数 器T —— 1 信号预 处理 卜— 定时计数 器T .— - 2

图 1 系统总体框架图

输入2

1 或 1s s 0。在闸门信号有效的时间内对待测信号进行计数 , 从而可以得到信号频率。 系统总体结构如图 l 所示 , 系统中信号的核心处理部分是 P o Y C 96 — P X , SCC 8 2462 V I利用其 内部 的定时计 4 数器在闸门信号有效的时间内对待测信号进行计数 , 而后输 出信号的频率数值。首先设定全局参数和定时器的

关 键 词 : S S 定 时 器 ; 形 ; 频 PO ; 整 分 文献标识码 : A 中图 分类 号 : TM9 5 1 3 3 .3

频率计是一种常用的测量仪器 , 通过对单位时间内的信号脉冲进行计数, 从而测量 出信号的频率。频率计 的应用 范围很广 , 不仅应用 于一般 的简单仪器 测量 , 且还 广泛 应用 于教学 、 而 科研 、 高精 度仪 器测 量 、 工业 控制 等

其它领 域。

1 频 率计 的核 心器 件 P o Y8 2 4 62 P I S C C C 9 6 .4 VX

Po SC是 美 国 C pesMio yt yrs c S s ms公 司 推 出 的 功 能 强 大 的 8位 可 配 置 的 嵌 入 式 单 片 机 。P o r e SC C 82X Y C 9 XX系列 可编程 片上系统具 有一个 高速 内核 、l h快 速闪存 和 S Fa s

用 的数 字模 块和模 拟模块 。

数 据 内存 , 以及 设计 者可 配置 使

P O 主要 特 点 有 : 能强 大 的 8位 哈 佛 结 构 的处 理 器 , C处 理 器 的时 钟 频 率 可 以从 9 .k ~2 SC的 功 M8 37 Hz 4 MH , 大的频率 范 围可以使 M8 z如此 C适应 于不 同的应 用需 求 , 支持 的指 令集 也非 常丰 富 ; 先进 的 外 围电路 , 4列 模拟模块最 多可 以有 1 2个模 拟模块 , 以提供 多至 1 可 4位 A DC、 多至 l 位 D C、 4 A 可编程放 大器 、 可编程 滤波器和 比较器 , 模块列 包含一 个 B类型 的连续 时钟模 块 、 每个 一个 C类 型的开关 电容模 块 (C 和一 个 D类 型 的开关 电 S) 容模块 (C)1 数字模块 提供 8 2位定 时器 、 数器 和 P S ,6个 —3 计 WM 、 至所有 G I 可连 PD引脚 , 可组合成 复杂 的外围

参数, 可以选择好定时器的时钟 、 触发方式以及定时 , 将两个定时器的定时设置成相同的 , 测定该时间内信号的脉

收稿 日期 :0 80 —8 修订 1期 :0 80 —2 2 0 61 ; 3 2 0—90

第 6期

李 玉丽等 : 用 P o 利 S C实现频 率计

63 2

冲个数 , 么 F=N/ T )( 那 ( o F表示 频率 , 表示 测 得 的数值 , 定时 器的定 时 )当然 我们 在计 算 信号 的频 率 时 N , 还要把分频考虑在内, 可以通过对软件代码的设计 , 直接算 出信号的频率 , 然后将该频率数值输 出显示在 L D E 上 。采用 串行 的数 据传输 方式 , 以减少 IO 口的 占用 比例 , 可 / 留有 一定 的空 间 。为 了精 确起 见 可 以多次 测 量数 值, 求其平 均值作 为最终 测量 结果 。