chapter7 一阶数字锁相环

锁相环基本原理

锁相环基本原理

锁相环(Phase Locked Loop,PLL)是一种常用的电子电路,可以用来解决信号同步和频率合成等问题。

它的基本原理是通过比较两个信号的相位差,通过反馈调节使得相位差保持在一个稳定的值,从而达到信号同步的目的。

锁相环的基本组成部分包括相位检测器、低通滤波器、振荡器和分频器等。

其中,相位检测器是锁相环的核心部件,它的作用是将输入信号和反馈信号进行比较,得到相位差信号。

常用的相位检测器有边沿检测器、乘积检测器和采样保持器等。

在锁相环的工作过程中,输入信号经过相位检测器与反馈信号进行比较,产生相位差信号,经过低通滤波器进行滤波处理,然后输出给振荡器进行调节,从而使得振荡器的输出信号与输入信号达到同步。

如果输入信号的频率发生变化,相位差信号也会随之变化,这时锁相环会通过反馈调节振荡器的输出频率,使得相位差保持在一个稳定的值。

锁相环在实际应用中具有广泛的用途,如在通信系统中用于时钟恢复和信号重构,可以提高信号质量和传输距离;在计算机系统中用于时钟同步和频率合成,可以提高计算机的稳定性和性能;在音频系统中用于音频合成和去噪,可以提高音质和降低噪声等。

锁相环作为一种常用的电子电路,其基本原理是通过比较两个信号的相位差,通过反馈调节使得相位差保持在一个稳定的值,从而达到信号同步的目的。

它在实际应用中具有广泛的用途,可以提高系统的稳定性和性能,提高信号质量和传输距离,降低噪声等。

数字锁相环matlab

数字锁相环matlab摘要:1.数字锁相环的概述2.Matlab 在数字锁相环中的应用3.数字锁相环的实现方法4.结论正文:1.数字锁相环的概述数字锁相环(Digital Phase-Locked Loop,简称DPLL)是一种数字信号处理技术,用于在数字通信系统中实现信号同步。

在数字通信系统中,信号的同步至关重要,因为只有实现信号同步,才能确保接收端正确地解调出原始信号。

数字锁相环通过比较接收信号与本地生成的信号,并根据两者之间的相位差来调整本地信号的相位,从而实现信号的同步。

2.Matlab 在数字锁相环中的应用MATLAB 是一种广泛应用于信号处理和通信系统的软件工具,它可以方便地实现数字锁相环的模型和算法。

使用MATLAB 可以搭建数字锁相环的仿真模型,对锁相环的性能进行分析和评估,以及对锁相环的算法进行优化。

此外,MATLAB 还提供了丰富的通信系统工具箱,如通信系统工具箱、信号处理工具箱等,为数字锁相环的设计和分析提供了强大的支持。

3.数字锁相环的实现方法数字锁相环的实现方法主要包括以下几种:(1)基于滤波器的实现方法:该方法通过设计一个滤波器,使得滤波器的传递函数与输入信号的相位相关,从而实现信号的同步。

(2)基于频率检测的实现方法:该方法通过检测输入信号的频率,并将其与本地信号的频率进行比较,从而实现信号的同步。

(3)基于相位检测的实现方法:该方法通过检测输入信号与本地信号之间的相位差,并根据相位差来调整本地信号的相位,从而实现信号的同步。

(4)基于最大似然估计的实现方法:该方法通过计算输入信号与本地信号之间的最大似然估计,从而实现信号的同步。

4.结论数字锁相环是一种重要的信号处理技术,广泛应用于数字通信系统中。

MATLAB 作为一种强大的信号处理工具,可以方便地实现数字锁相环的模型和算法。

数字锁相环的实现方法有多种,每种方法都有其独特的优点和适用场景。

数字锁相环基础知识

数字锁相环基础知识数字锁相环(Digital Phase-Locked Loop,简称DPLL)是一种广泛应用于通信系统、数字信号处理和时钟同步等领域的数字电路技术。

它通过对输入信号进行数字化处理,实现锁定输入信号的相位和频率,从而实现信号的同步和解调。

数字锁相环的基本原理是将输入信号与本地参考信号进行比较,通过调整本地参考信号的相位和频率,使得输入信号与本地参考信号保持同步。

为了实现这一目标,数字锁相环通常由相位检测器、数字控制环路滤波器、数字控制振荡器和数字控制频率合成器等组成。

相位检测器负责测量输入信号和本地参考信号之间的相位差。

常见的相位检测器有边沿检测器和乘法器相位检测器等。

边沿检测器通过测量输入信号和本地参考信号之间的边沿时间差来计算相位差;乘法器相位检测器通过将输入信号和本地参考信号相乘,得到一个与相位差成正比的输出。

接着,数字控制环路滤波器对相位差进行滤波处理,以获得平滑的控制信号。

常见的数字控制环路滤波器有积分环路滤波器和二阶锁相环滤波器等。

积分环路滤波器通过积分相位差来获得控制信号;二阶锁相环滤波器通过对相位差进行二阶滤波,提高了系统的稳定性和抗干扰能力。

然后,数字控制振荡器根据控制信号调整本地参考信号的相位和频率。

数字控制振荡器通常由数字控制调节器和数字控制振荡器组成。

数字控制调节器根据控制信号调节数字控制振荡器的频率,从而实现对本地参考信号频率的精确控制。

数字控制频率合成器根据数字控制振荡器的输出信号生成输出信号。

数字控制频率合成器通常由数字控制振荡器和数字控制调制器组成。

数字控制振荡器通过输出参考信号的频率来控制数字控制调制器的频率,从而实现对输出信号频率的精确合成。

数字锁相环具有很多优点。

首先,它可以实现高精度的相位和频率锁定,对于要求高精度同步的应用非常有用。

其次,数字锁相环具有较高的稳定性和抗干扰能力,可以有效抑制噪声和干扰信号。

此外,数字锁相环还具有灵活性强、可编程性好等特点,可以根据不同的应用需求进行灵活配置和调整。

锁相环基本概念PPT课件

ui(t)

PD ud(t) LF

uc(t) VCO

uo(t)

uf(t)

PLL

图1.2.1 基本锁相环组成

实际使用的锁相环还可能包含放大器、混频器、分 频器、滤波器等部件,但这些部件不影响锁相环的工 作原理,可不予考虑。

u(t) VCO

uf(t)

PLL

uo(t)

图1.2.1 基本锁相环组成

ui(t)

PD

ud(t) LF

uc(t) VCO

uo(t)

uf(t)

PLL

图1.2.1 基本锁相环组成

在锁相环中,PD是控制器,VCO是控制对象,LF是校 正网络,基本锁相环中反馈网络的传递函数为1。反 馈网络的传递函数为1 的环路称为单位反馈环,它的 反馈信号等于输出信号,反馈量等于输出量。在本 书中,无特殊说明的锁相环皆是单位反馈环。

由图可见,锁相环是一个反馈系统(闭环控制系统) 。 基本锁相环是一个全反馈系统,因为uf(t)=uo(t) 。

PD对输入信号ui(t)和反馈信号uf(t)的相位作比较, 其输出信号可表示为

ud(t)=f[θe(t)]

(1.2.1)

式中θe(t)是输入信号和反馈信号的相位差,f[·]表 示运算关系。

2021/6/19

12

LF是一个线性低通网络,用来滤除ud(t)中的高频成分 和调整环路参数,它对环路的性能指标有重要影响。 它的输出uc(t)被用来控制VCO的频率和相位。常 称ud(t)为误差信号,uc(t)为控制信号,它们之间的关 系为 uc(t)=F(p)ud(t)…(1.2.2)

式中p为微分算子,F(p)为LF的传输算子。

到70年代,随着集成电路技术的发展,逐渐出现了集成 的环路部件、通用单片集成锁相环路以及多种专用 集成锁相环路,这就为锁相技术在更广泛的领域应用 提供了条件,从而使锁相技术得到了广泛的应用。

数字锁相环实验报告

本科实验报告实验名称:数字锁相环实验四、实验内容准备工作:将调制方式设在BPSK方式,用函数信号发生器产生一个64KHz的TTL信号送入数字数字信号测试端口J007(实验箱左端)。

1.锁定状态测量用示波器同时测量TPMZ03、TPMZ02的相位关系,测量时用TPMZ03同步;在理论上,环路锁定时该两信号应为上升沿对齐。

2.数字锁相环的相位抖动特性测量数字锁相环在锁定时,输出信号存在相位抖动是数字锁相环的固有特征。

测量时,以TPMZ03为示波器的同步信号,用示波器测量TPMZ02,仔细调整示波器时基,使示波器刚好容纳TPMZ02的一个半周期,观察其上升沿。

可以观察到其上升较粗(抖动),其宽度与TPMZ02周期的比值的一半即为数字锁相环的时钟抖动。

3.锁定频率测量和分频比计算将函数信号发生器设置在记数状态(频率计)。

参见数字锁相环的结构如图3.2.1数字锁相环的结构,测量各点频率。

记录测量结果,计算分频比。

TPMZ01 TPMZ02TPMZ03 TPMZ04TPMZ054.锁定过程观测(1)用示波器同时观测TPMZ03、TPMZ02的相位关系,测量时用TPMZ03同步;复位通信原理综合实验系统,则FPGA进行初始化,数字锁相环进行重锁状态。

此时,观察它们的变化过程(锁相过程)。

(2)用示波器测量TPMZ05波形,复位通信原理综合实验系统,观察调整的变化过程。

5.同步带测量(1)用函数信号发生器产生一个64KHz的TTL信号送入数字信号测试端口J007。

用示波器同时测量TPMZ03、TPMZ02的相位关系,测量时用TPMZ03同步;正常时环路锁定,该两信号应为上升沿对齐。

(2)缓慢增加函数信号发生器输出频率,直至TPMZ03、TPMZ02两点波形失步,记录下失步前的频率。

(3)调整函数信号发生器频率,使环路锁定。

缓慢降低函数信号发生器输出频率,直至TPMZ03、TPMZ02两点波形失步,记录下失步前的频率。

数字锁相环介绍

数字锁相环试验讲义一、锁相环的分类模拟、数字如何定义?何谓数字锁相环。

是指对模拟信号进行采样量化之后(数字化)的“数字信号”的处理中应用的锁相环,还是指的对真正的“数字信号”如时钟波形进行锁定的锁相环?二、数字锁相环的实际应用欲成其事,先明其义。

现代数字系统设计中,锁相环有什么样的作用。

1)在ASIC设计中的应用。

主要应用领域:窄带跟踪接收;锁相鉴频;载波恢复;频率合成。

例一:为了达到ASIC设计对时钟的要求,许多工程师都在他们的设计中加入了锁相环(PLL)。

PLL有很多理想的特性,例如可以倍频、纠正时钟信号的占空比以及消除时钟在分布中产生的延迟等。

这些特性使设计者们可以将价格便宜的低频晶振置于芯片外作为时钟源,然后通过在芯片中对该低频时钟源产生的信号进行倍频来得到任意更高频率的内部时钟信号。

同时,通过加入PLL,设计者还可以将建立-保持时间窗与芯片时钟源的边沿对齐,并以此来控制建立-保持时间窗和输入时钟源与输出信号之间的延迟。

2)在信号源产生方面的应用例二:由于无线电通信技术的迅速发展,对振荡信号源的要求也在不断提高。

不但要求它的频率稳定度和准确度高,而且要求能方便地改换频率。

实现频率合成有多种方法,但基本上可以归纳为直接合成法与间接合成法(锁相环路)两大类。

3)无线通信领域的实际应用例三:GSM手机的频率系统包括参考频率锁相环,射频本振锁相环、中频本振锁相环。

广义的数字锁相环包括扩频通信中的码跟踪。

三、数字锁相环的基本原理一般数字锁相环路的组成与模拟锁相环路相同,即也是由相位检波器、环路滤波器和本地振荡器等基本部件构成,但这些部件全部采用数字电路。

具体来说数字锁相环由:数字鉴相器、数字环路滤波器、NCO和分频器组成。

四、实际应用中的数字锁相环的实现方法PLL的结构和功能看起来十分简单,但实际上却非常复杂,因而即使是最好的电路设计者也很难十分顺利地完成PLL的设计。

在实际应用中,针对数字信号或数字时钟的特点,数字锁相环多采用超前滞后型吞吐脉冲的锁相环路来实现。

锁相环工作原理

锁相环工作原理锁相环(Phase-Locked Loop,简称PLL)是一种常用的电子系统控制技术,用于实现频率合成、频率调整、时钟恢复等功能。

它可以将输入信号的频率和相位与参考信号进行比较,并通过调节输出信号的频率和相位来使两者保持同步。

锁相环广泛应用于通信系统、数字信号处理、时钟同步、频率合成等领域。

锁相环主要由相位比较器、低通滤波器、电压控制振荡器(Voltage Controlled Oscillator,简称VCO)和分频器组成。

1. 相位比较器(Phase Comparator):相位比较器是锁相环的核心部件之一,它用于比较输入信号和参考信号的相位差。

常见的相位比较器有边沿比较器、乘法器、延迟锁定环等。

相位比较器的输出信号表示相位差的大小和方向。

2. 低通滤波器(Low Pass Filter):相位比较器的输出信号经过低通滤波器进行滤波处理,去除高频噪声和干扰,得到平滑的控制电压。

3. 电压控制振荡器(Voltage Controlled Oscillator,VCO):VCO是锁相环的另一个核心部件,它根据控制电压的大小和极性来调节输出信号的频率和相位。

VCO的输出信号经过分频器反馈给相位比较器进行相位比较。

4. 分频器(Divider):分频器用于将VCO的输出信号进行分频,得到参考信号。

分频器通常采用可编程分频器,可以根据需要进行分频比的设置。

锁相环的工作原理如下:1. 初始化:锁相环开始工作时,需要进行初始化设置。

初始化包括设置参考信号的频率、相位和幅度,以及设置VCO的初始频率。

2. 相位比较:相位比较器将输入信号和参考信号进行相位比较,得到相位差的大小和方向。

3. 低通滤波:相位比较器的输出信号经过低通滤波器进行滤波处理,得到平滑的控制电压。

4. 控制VCO:控制电压作用下,VCO的频率和相位发生变化。

如果相位差为正,则VCO的频率增加;如果相位差为负,则VCO的频率减小。

实验一 一阶锁相环

锁相与频率合成专业班级: _ ____实验名称:一阶锁相环 _学生姓名: aikundehcong _ 学号:_ _任课老师: _2013 年 6月 8 日实验一 一阶锁相环一、实验目的了解通信系统中锁相环的建立与仿真二、实验内容1、建立一个采用乘法器作为鉴相器的一阶锁相环。

三、实验原理:1、一阶锁相环VCOVCO 的振荡频率为100Hz ,控制灵敏度为kc=10Hz/V ,VCO 输出信号振幅为1V ,输入正弦信号振幅为1V 。

设输入信号为()cos(2())r t ft t πφ=+,VCO 输出信号为ˆ()sin(2())s t ft t πφ=+,则乘法鉴相器输出(滤除2倍频分量后)直接用来作为VCO 的控制信号()v t ,即1ˆ()sin()2v t φφ=-显然,()[0.5,...0.5]v t ∈-。

VCO 的最大控制频偏为max[()]5c f k v t Hz ∆==因此,VCO 的振荡频率范围是95~105Hz ,如果输入信号频率超过该范围,锁相环将不能跟踪。

上图中,系统仿真步进设置为0.0001s ,这样,在100Hz 波形的一个周期中采样点数可达到100点。

显示波形很光滑。

四、实验步骤:1、根据实验原理图在matlab的simulink上画出模块。

2、VCO的振荡频率设为100Hz,控制灵敏度为kc=10Hz/V,VCO输出信号振幅为1V。

3、将步进设为0.0001s(注意:vco、零阶保持器Zero-Order Hold以及乘法器的sample time都应设置为0.0001s)。

4、将信号发生器(signal generator)的频率设为100Hz,观察和对比示波器显示的三个波形。

5、将信号发生器(signal generator)的频率设为110Hz,观察和对比示波器显示的三个波形。

6、将信号发生器(signal generator)的频率设为90Hz,观察和对比示波器显示的三个波形。

chapter7 一阶数字锁相环 电子科技大学(经典)

当:①某一路的N计数器在M计数器的计数值满的同时或之前计数值 满,则相应地输出一个“提前”或“退后”脉冲,并使得所有的计数 器复 位; ②M计数器在N计数器的计数值满之前计数值满,则输出一个复

位信号,此时无“提前”或“退后”脉冲输出

在环路中相位差很小或输入信噪比很低时,环路中的超前或滞后

脉冲主要是由噪声所致,超前脉冲数与滞后脉冲数几乎相同且分布比

常用的序列滤波器有两种:

(1) “N先于M”序列滤波器 (2) “随机徘徊”序列滤波器

(1)

“N先于M”序列滤波器

N 寄存器

超前 脉冲 滞后 脉冲

提前脉冲

+

M 寄存器 N 寄存器

+

复 位

推后脉冲

工作原理 鉴相器输出的超前或滞后脉冲分别送入两个N计数存储器中 进行计数,它们的和脉冲送入M计数存储器进行计数,计数值N和M 满足: N < M < 2N

分频器

标准频率源输出频率相同但相差为π的两路标准频率信号,

0相位的频率信号用于通常的计数和减脉冲,π相位的频率信号 用于加脉冲

工作过程的图形描述

0相位频 率信号 0 π 相位频 率信号 0 无控制 输出信号 1 插入提前 脉冲 T0 2 3 4 5 6 7 5 10 15 20 25 30 5 10 15 20 25 30

T0

输入 信号 t

反馈 信号 t

RS触发 器输出

e

t

对应的鉴相特性如教材P181图7-2所示

3. 奈奎斯特速率型数字鉴相器

又称为取样鉴相器,其名称来源于奈奎斯特定理 奈奎斯特速率型数字鉴相器的特点:

• 输入信号和本地参考信号使用相同频率进行取样处理,处

理过程中取样速率不变

数字锁相环的工作原理

数字锁相环的工作原理数字锁相环啊,可是个超有趣又很有技术含量的东西呢。

数字锁相环主要由鉴相器、环路滤波器和数控振荡器这几个部分组成。

鉴相器啊,它的作用可大了。

它是用来比较输入信号和数控振荡器输出信号的相位差的。

你想啊,就好像是在给两个小伙伴做比较,看看他们在相位这个方面到底有多少不一样的地方呢。

当输入信号和数控振荡器的输出信号进来之后啊,鉴相器就会根据它们的相位关系产生一个误差信号。

这个误差信号可就像是一个小提示,告诉整个系统啊,这两个信号在相位上有点偏差了呢。

接着就是环路滤波器啦。

环路滤波器拿到鉴相器给出的误差信号后啊,就开始对这个信号进行处理。

它可不是简单地把这个信号直接传递下去哦,而是会按照一定的规则对这个信号进行滤波啊。

这就好比是把一些不需要的杂质给去掉,只留下对调整有用的信息。

经过环路滤波器处理后的信号就变得更加纯净、更加适合用来做后续的操作啦。

最后就是数控振荡器啦。

数控振荡器在收到环路滤波器处理后的信号之后啊,就会根据这个信号来调整自己的输出频率和相位呢。

它就像是一个很听话的小助手,根据得到的指令来改变自己的输出,目的就是要让自己输出的信号和输入信号在相位上尽可能地接近。

这样不断地调整、比较、再调整的过程啊,就使得整个数字锁相环能够稳定地工作啦。

在整个数字锁相环的工作过程中啊,这几个部分相互配合、相互影响。

鉴相器不停地检测相位差,环路滤波器不断地优化误差信号,数控振荡器持续地调整输出,这样的一个循环往复的过程啊,就使得数字锁相环能够实现对输入信号的相位锁定。

比如说在通信系统中啊,数字锁相环就可以用来从接收到的信号中提取时钟信号。

这多厉害呀,它就像是一个精准的小工匠,能够在众多的信号当中找到自己想要的时钟信号,为通信系统的正常运行提供了很大的保障呢。

而且啊,数字锁相环在很多其他的领域也有广泛的应用,像在雷达系统中可以用来进行信号的处理和跟踪,在音频处理中也能够起到稳定频率等重要的作用。

数字锁相环原理

数字锁相环原理数字锁相环(Digital Phase-Locked Loop,简称数字PLL)是一种广泛应用于通信、控制系统中的数字信号处理器。

它可以实现信号的频率和相位同步,对于数字通信系统中的时钟恢复、频率合成、信号解调等功能起着至关重要的作用。

本文将介绍数字锁相环的基本原理及其在通信系统中的应用。

数字锁相环由相位比较器、数字控制振荡器(DCO)、数字滤波器和锁定检测器组成。

其中,相位比较器用于比较输入信号和反馈信号的相位差,产生一个误差信号;数字控制振荡器根据误差信号调整输出频率;数字滤波器用于滤除噪声和抖动;锁定检测器用于检测数字锁相环是否已经锁定。

数字锁相环的工作原理可以简单描述为,首先,输入信号经过频率除法器和相位频率检测器,产生一个误差信号;然后,误差信号经过数字滤波器滤除噪声,再经过数字控制振荡器产生输出信号;最后,输出信号经过反馈回到相位比较器,形成闭环控制。

在闭环控制下,数字锁相环可以实现输入信号和输出信号的频率和相位同步。

数字锁相环在通信系统中有着广泛的应用。

在数字调制解调中,数字锁相环可以实现信号的时钟恢复和频率合成,保证接收端对发送端信号的准确解调;在频率合成器中,数字锁相环可以实现高稳定性的频率合成,满足通信系统对频率精度的要求;在通信系统中,数字锁相环还可以用于时钟同步和信号重构等功能。

总之,数字锁相环作为一种重要的数字信号处理器,在通信系统中有着广泛的应用。

它通过闭环控制实现输入信号和输出信号的频率和相位同步,保证了通信系统的稳定性和可靠性。

随着通信技术的不断发展,数字锁相环的应用范围将会更加广泛,对于提高通信系统的性能起着至关重要的作用。

通过本文的介绍,相信读者对数字锁相环的原理及其在通信系统中的应用有了更深入的了解。

数字锁相环作为一种重要的数字信号处理器,其原理简单而又实用,对于提高通信系统的性能有着重要的意义。

希望本文能对读者有所帮助,谢谢阅读!。

第7章数字锁相环

《锁相技术》

第7章 数字锁相环

3.过零检测式数字锁相环(ZC-DPLL)环路用本地受 控时钟脉冲对输入信号的过零点抽样,非零的实际抽 样值大小就反映着相位误差,用该相位误差来调节本 地时钟信号的相位。

2 (rad )

(7-2)

N

《锁相技术》

第7章 数字锁相环

所以N是表示2π弧度内相位受控变化大小的一个量, 也叫做模2π内状态数。这就是说,数字压控振荡器输出 脉冲的瞬时相位θo(k),在2π弧度内只能以Δ或其倍数离 散地变化。显然,在这里To/N=Tc,Tc为信号钟的周期。因 此有

N To Tc

《锁相技术》

第7章 数字锁相环 《锁相技术》

第7章 数字锁相环

由于鉴相器输出是二值脉冲,常后接一种序列滤波 器来平滑其中的起伏,消除噪声起伏造成的环路误动作 比较方便。有两种形式序列滤波器,一种叫“N先于M” 滤波器。如图7-9所示;另一种叫“随机徘徊”滤波器, 如图7-10所示。

《锁相技术》

第7章 数字锁相环

第7章 数字锁相环

(3) 过零取样鉴相器。这种鉴相器有两种形式,一 种是正过零点取样,如图7-5所示。这种正过零点取样 鉴相器是所有数字鉴相器中最简单的,而且易于实现。 另一种则在正负过零点都取样,如图7-6所示。

《锁相技术》

第7章 数字锁相环

图7-4 用于FM解调的NR-DPLL组成方案 《锁相技术》

《锁相技术》

第7章 数字锁相环

《锁相技术》

图7-7 简单二元鉴相器

数字锁相环原理应用

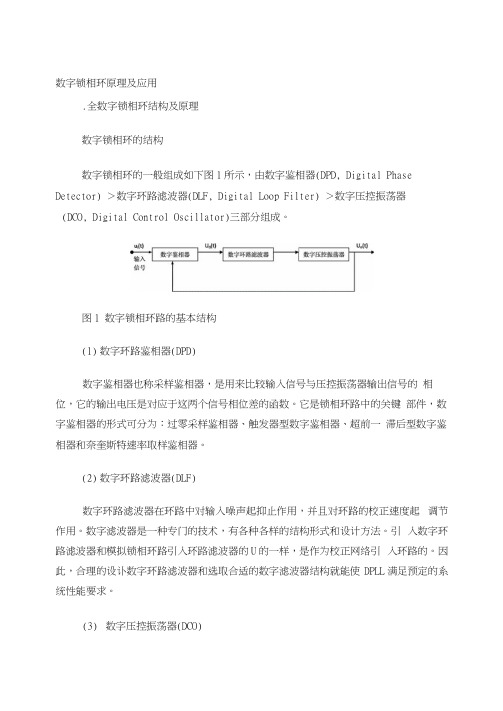

数字锁相环原理及应用.全数字锁相环结构及原理数字锁相环的结构数字锁相环的一般组成如下图1所示,由数字鉴相器(DPD, Digital Phase Detector) >数字环路滤波器(DLF, Digital Loop Filter) >数字压控振荡器(DCO, Digital Control Oscillator)三部分组成。

图1 数字锁相环路的基本结构(1)数字环路鉴相器(DPD)数字鉴相器也称采样鉴相器,是用来比较输入信号与压控振荡器输出信号的相位,它的输出电压是对应于这两个信号相位差的函数。

它是锁相环路中的关键部件,数字鉴相器的形式可分为:过零采样鉴相器、触发器型数字鉴相器、超前一滞后型数字鉴相器和奈奎斯特速率取样鉴相器。

(2)数字环路滤波器(DLF)数字环路滤波器在环路中对输入噪声起抑止作用,并且对环路的校正速度起调节作用。

数字滤波器是一种专门的技术,有各种各样的结构形式和设计方法。

引入数字环路滤波器和模拟锁相环路引入环路滤波器的U的一样,是作为校正网络引入环路的。

因此,合理的设讣数字环路滤波器和选取合适的数字滤波器结构就能使 DPLL满足预定的系统性能要求。

(3)数字压控振荡器(DCO)数控振荡器,乂称为数字钟。

它在数字环路中所处的地位相当于模拟锁相环中的压控振荡器(VCO)。

但是,它的输出是一个脉冲序列,而该输出脉冲序列的周期受数字环路滤波器送来的校正信号的控制。

其控制特点是:前一采样时刻得到的校正信号将改变下一个采样时刻的脉冲时间位置。

全数字锁相环工作原理全数字锁相环的基本工作过程如下:(1)设输入信号Ui(t)和本振信号(数字压控振荡器输出信号)uo(t)分别是正弦和余弦信号,他们在数字鉴相器内进行比较,数字鉴相器的输出是一个与两者间的相位差成比例的电压ud(t)。

(2)数字环路滤波器除数字鉴相器输出中的高频分量,然后把输出电压uc(t) 加到数字压控振荡器的输出端,数字压控振荡器的本振信号频率随着输入电圧的变化而变化。

数字锁相环设计

引言锁相的概念是在19世纪30年代提出的,而且很快在电子学和通信领域中获得广泛应用。

尽管基本锁相环的从开始出现几乎保持原样,但是使用不同的技术制作及满足不同的应用要求,锁相环的实现对于特定的设计还是蛮大的挑战。

锁相环在通信、雷达、测量和自动化控制等领域应用极为广泛,已经成为各种电子设备中必不可少的基本部件。

随着电子技术向数字化方向发展,需要采用数字方式实现信号的锁相处理。

锁相环技术在众多领域得到了广泛的应用。

如信号处理,调制解调,时钟同步,倍频,频率综合等都应用到了锁相环技术。

传统的锁相环由模拟电路实现,而全数字锁相环(DPLL)与传统的模拟电路实现的锁相环相比,具有精度高且不受温度和电压影响,环路带宽和中心频率编程可调,易于构建高阶锁相环等优点,并且应用在数字系统中时,不需A/D及D/A转换。

随着通讯技术、集成电路技术的飞速发展和系统芯片(SoC)的深入研究,全数字锁相环必然会在其中得到更为广泛的应用。

因此,对全数字锁相环的研究和应用得到了越来越多的关注。

传统的数字锁相环系统是希望通过采用具有低通特性的环路滤波器,获得稳定的振荡控制数据。

对于高阶全数字锁相环,其数字滤波器常常采用基于DSP 的运算电路。

这种结构的锁相环,当环路带宽很窄时,环路滤波器的实现将需要很大的电路量,这给专用集成电路的应用和片上系统SOC(system on chip)的设计带来一定困难。

另一种类型的全数字锁相环是采用脉冲序列低通滤波计数电路作为环路滤波器,如随机徘徊序列滤波器、先N后M序列滤波器等。

这些电路通过对鉴相模块产生的相位误差脉冲进行计数运算,获得可控振荡器模块的振荡控制参数。

由于脉冲序列低通滤波计数方法是一个比较复杂的非线性处理过程,难以进行线性近似,因此,无法采用系统传递函数的分析方法确定锁相环的设计参数。

不能实现对高阶数字锁相环性能指标的解藕控制和分析,无法满足较高的应用需求。

由于数字电子技术的迅速发展,尤其是数字计算和信号处理技术在多媒体、自动化、仪器仪表、通讯等领域的广泛应用,用数字电路处理模拟信号的情况日益普遍。

全数字锁相环结构及工作原理

DPLL结构及工作原理一阶DPLL的基本结构如图1所示。

主要由鉴相器、K变模可逆计数器、脉冲加减电路和除N计数器四部分构成。

K变模计数器和脉冲加减电路的时钟分别为Mfc和2Nfc。

这里fc是环路中心频率,一般情况下M和N都是2的整数幂。

本设计中两个时钟使用相同的系统时钟信号。

图1 数字锁相环基本结构图鉴相器常用的鉴相器有两种类型:异或门(XOR)鉴相器和边沿控制鉴相器(ECPD),本设计中采用异或门(XOR)鉴相器。

异或门鉴相器比较输入信号Fin相位和输出信号Fout相位之间的相位差Фe=Фin-Фout,并输出误差信号Se作为K变模可逆计数器的计数方向信号。

环路锁定时,Se为一占空比50%的方波,此时的绝对相为差为90°。

因此异或门鉴相器相位差极限为±90°。

异或门鉴相器工作波形如图2所示。

图2 异或门鉴相器在环路锁定及极限相位差下的波形K变模可逆计数器K变模可逆计数器消除了鉴相器输出的相位差信号Se中的高频成分,保证环路的性能稳定。

K变模可逆计数器根据相差信号Se来进行加减运算。

当Se为低电平时,计数器进行加运算,如果相加的结果达到预设的模值,则输出一个进位脉冲信号CARRY给脉冲加减电路;当Se为高电平时,计数器进行减运算,如果结果为零,则输出一个借位脉冲信号BORROW给脉冲加减电路。

脉冲加减电路脉冲加减电路实现了对输入信号频率和相位的跟踪和调整,最终使输出信号锁定在输入信号的频率和信号上,工作波形如图3所示。

图3 脉冲加减电路工作波形除N计数器除N计数器对脉冲加减电路的输出IDOUT再进行N分频,得到整个环路的输出信号Fout。

同时,因为fc=IDCLOCK/2N,因此通过改变分频值N可以得到不同的环路中心频率fc。

DPLL部件的设计实现了解了DPLL的工作原理,我们就可以据此对DPLL的各部件进行设计。

DPLL 的四个主要部件中,异或门鉴相器和除N计数器的设计比较简单:异或门鉴相器就是一个异或门;除N计数器则是一个简单的N分频器。

锁相环

设计目的

设计一个全数字锁相环路,通过它从19.2k的信号 中提取同步信号。 本地源时钟为11.0592MHz。

完成步骤

1. 阅读相关资料,了解锁相环的相关知识 2. 设计数字锁相环 3. 完成了锁相环的仿真、测试工作

4. 电路调试

锁相环分类

一类是环路中误差信号去连续地调整位同步信号的 相位,这一类属于模拟锁相法

控制器: 包括图中的扣除门(常开)、附加门(常闭) 和“或门”, 它根据比相器输出的控制脉冲(“超 前脉冲”或“滞后脉冲”)对信号钟输出的序列实施 扣除(或添加)脉冲。

数字锁相环基本原理

分频器:是一个计数器,每当控制器输出n个脉冲时, 它就输出一个脉冲。控制器与分频器的共同作用的结 果就调整了加至比相器的位同步信号的相位。这种相 位前、后移的调整量取决于信号钟的周期,每次的时 间 阶 跃 量 为 T0 , 相 应 的 相 位 最 小 调 整 量 为 Δ =2π T0/T=2π /n。

数字锁相环硬件实现- N先于M 数 字 滤 波 器

N先于M滤波器包括一个计超前脉冲数和一个计滞后脉冲数的N计数器,超前脉 冲与滞后脉冲还通过或门加于一M计数器

选择N<M<2N, 无论哪个计数器计满, 都会使所有计数器重新置“0”。

数字锁相环硬件实现- N先于M 数 字 滤 波 器

当鉴相器送出超前脉冲或滞后脉冲时,滤波器并不马上将它送 去进行相位调整, 而是分别对输入的超前脉冲(或滞后脉冲) 进行计数。 如果两个N计数器中的一个,在M计数器计满的同时或未计满前 就计满了,则滤波器就输出一个“减脉冲”(或“加脉冲”) 控制信号去进行相位调整, 同时将三个计数器都置“0”(即复 位),准备再对后面的输入脉冲进行处理。 如果是由于干扰的作用,使鉴相器输出零星的超前或滞后脉冲, 而且这两种脉冲随机出现,那么,当两个N计数器的任何一个都 未计满时,M计数器就很可能已经计满了,并将三个计数器又置 “0”,因此滤波器没有输出,这样就消除了随机干扰对同步信 号相位的调整。

锁相环理论讲解

锁相环的理论锁相环作为一个系统,主要包含三个基本模块:鉴相器(Phase Detector :PD)、低通滤波器(LowPass Filter :LPF),亦即环路滤波器(L00P Filter :LF ),和压控振荡器(V oltage Controlled Oscillator :VCO )。

这三个基本模块组成的锁相环为基本锁相环,亦即线形锁相环(LPLL),如图2.1所示。

图2.1锁相环原理图当锁相环开始工作时,输入参考信号的频率1f 与压控振荡器的固有振荡频率o f 总是不相同的,即1o f f f ∆=-,这一固有频率差1o f f f ∆=-必然引起它们之间的相位差不断变化,并不断跨越2π角。

由于鉴相器特性是以相位差2π为周期的,因此鉴相器输出的误差电压总是在某一范围内摆动。

这个误差电压通过环路滤波器变成控制电压加到压控振荡器上,使压控振荡器的频率o f 趋向于参考信号的频率i f ,直到压控振荡器的频率变化到与输入参考信号的频率相等,并满足一定条件,环路就在这个频率上稳定下来。

两个频率之间的相位差不随时间变化而是一个恒定的常数,这时环路就进入“锁定”状态。

当环路已处于锁定状态时,如果输入参考信号的频率和相位发生变化,通过环路的控制作用,压控振荡器的频率和相位能不断跟踪输入参考信号频率的变化而变化,使环路重新进入锁定状态,这种动态过程称为环路的“跟踪”过程。

而环路不处于锁定和跟踪状态,这个动态过程称为“失锁”过程。

从上述分析可知,鉴相器有两个主要功能:一个是频率牵引,另一个是相位锁定。

实际中使用的锁相环系统还包括放大器、分频器、混频器等模块,但是这些附加的模块不会影响锁相环的基本工作原理,可以忽略。

2.1 锁相环的工作原理锁相环作为一个系统,主要包含三个基本模块:鉴相器【4】、低通滤波器,亦即环路滤波器,和压控振荡器。

在本节首先分析鉴相器、环路滤波器和压控振荡器.2.1.1 鉴相器锁相环中的鉴相器(PD )通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图示:()O U t ()i U t ()D U t图2.2 模拟鉴相器电路 鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:()sin[()]i m i i u t U t ωθ=+ (2.1)()sin[()]o om o o u t U t ωθ=+ (2.2)式中的O ω为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

当:①某一路的N计数器在M计数器的计数值满的同时或之前计数值 满,则相应地输出一个“提前”或“退后”脉冲,并使得所有的计数 器复 位; ②M计数器在N计数器的计数值满之前计数值满,则输出一个复

位信号,此时无“提前”或“退后”脉冲输出

在环路中相位差很小或输入信噪比很低时,环路中的超前或滞后

脉冲主要是由噪声所致,超前脉冲数与滞后脉冲数几乎相同且分布比

u1(t) u1(t) ud(t) ud(t) u2(t) u2(t)

当0<θe<π 时,输入输出波形如下所示

u1(t)

e

u2(t)

T0

ud(t)

T0/2

此时鉴相器输出的平均电压为

ud

1

e

U d d

0

Ud

(0 e ) e

当π <θe<2π 时,输入输出波形如下所示

∵ To/N = Tc

∴ 由此可知: N = To / Tc = fc / fo

①环路的工作频率越高,标准频率源所需要的频率越高,因此

数字环在高频时难实现 ②工作频率与标准频率的差别越大,控制精度越高,稳态相差

越小

另一种DCO的实现方案为

提前脉冲 输入

推后脉冲 输入

0

常 开

标准 频率源

π

+

常 闭

m

常用的序列滤波器有两种:

(1) “N先于M”序列滤波器 (2) “随机徘徊”序列滤波器

(1)

“N先于M”序列滤波器

N 寄存器

超前 脉冲 滞后 脉冲

提前脉冲

+

M 寄存器 N 寄存器

+

复 位

推后脉冲

工作原理 鉴相器输出的超前或滞后脉冲分别送入两个N计数存储器中 进行计数,它们的和脉冲送入M计数存储器进行计数,计数值N和M 满足: N < M < 2N

计数器

比较器

控制电压 E0+yk

受控输出

基本组成包括:固定频率源、计数器与比较器 设标准频率源的输出频率:fc = mfo 对于第k个取样周期Tk,有 Tk= To ± To/N·k-1 y

可见,受控时Tk以±n·o/N相对于To作阶跃式的改变 T

与最小周期变化量相对应的最小相位变化量

Δ = 2 / N 称N为2周期内的状态数

5. 超前滞后型数字鉴相器

采用二元鉴相器,对应相差的大小输出超前指示信

号或滞后指示信号,以控制本地参考信号的相位的变化

一般情况下有:

θe>0,本地参考信号落后,发超前脉冲

θe<0,本地参考信号超前,发滞后脉冲

典型的二元鉴相器用同相与中相积分来实现:

同相积分器的积分区间与每个输入码元区间重合 中相积分器的积分区间跨在两个码元区间之间

u1(t)

e

u2(t)

T0

ud(t)

T0/2

此时鉴相器输出的平均电压为

ud

1

2 e

U d d U d (2 e( e 2) )

0

综上,有鉴相特性

ud

Ud -2π

-π

0

π

2π

θ e

可见,异或门鉴相电路具有三角形鉴相特性,其鉴相特性的斜率为

Kd = ± Ud / π

较均匀,因此,序列滤波器可提供较好的抗噪能力

(2)

“随机徘徊”序列滤波器

工作原理 与“N先于M”序列滤波器的思想一致,只是使用可 逆 计数器来实现,一般情况下超前脉冲使计数器上行计数,滞后 脉冲使计数器下行计数。当计数值达+N时,输出“提前”脉冲;

当计数值达-N时,输出“退后”脉冲

可见,在环路的捕获过程中,序列滤波器可能会影响系统 的捕获速度,但序列滤波器对同步以后的抗噪性能有很大的帮助 通常,由于序列滤波器的目的不是对误差信号做数字处理, 仅仅用于对噪声所可能引起的误动作的控制,因此一般认为它

T0

输入 信号 t

反馈 信号 t

RS触发 器输出

e

t

对应的鉴相特性如教材P181图7-2所示

3. 奈奎斯特速率型数字鉴相器

又称为取样鉴相器,其名称来源于奈奎斯特定理 奈奎斯特速率型数字鉴相器的特点:

• 输入信号和本地参考信号使用相同频率进行取样处理,处

理过程中取样速率不变

• 取样脉冲的速率根据前置的带通滤波器而定,要求满足奈

t t t

t

相位提前 输出信号 1 扣除推后 脉冲 TO m 2 3 4 5 6 7 8

t

t

相位推后 输出信号 1 TO m 2 3 4 5 6

t

五 一阶DPLL的工作原理

一种采用超前滞后型数字鉴相器的一阶环如下:

清零输入 取样脉冲 形成 b & d A Q Q Q Q 常开 1 0 标准 频率源 π 加/减控制器 A:超前触发器 B:滞后触发器

第七章 一阶DPLL分析

一 全数字环的一般构成与分类

全数字环的基本组成:

① 数字鉴相器

② 数字环路滤波器 ③ 数控振荡器DCO/NCO 与模拟环不同,对全数字锁相环,对环路性能影响最大的是数字 鉴相器的性能,因此多以鉴相器的实现方式来对数字锁相环进行分类

常用的DPLL的分类: ① 触发器型数字锁相环(FF-DPLL) ② 奈奎斯特型数字锁相环(NR-DPLL)

数字滤波器有以下的一些缺点: 器的频率

③ 设计和实现较复杂,不适用于较简单的系统

在非实时处理和模拟实验时,数字滤波器可用软件实现; 在进行实时处理时,一般采用数字硬件实现

四 数控振荡器DCO

一种实现方案如下图所示

复位脉冲

标准 频率源

③ 同相积分的结果可以判断相邻码元的变化趋势 综上可推出逻辑运算单元的真值表 同相支路(状态检测) +1 +1 中相支路 (相差检测) -1 0 超前 滞后 同步 -1 滞后 超前 同步 0 - - X

对二元鉴相器,其输出为二值脉冲,在噪声的干扰下,比较 容易出现误动作,因此需要采用序列滤波器,通过对鉴相器输出 的超前或滞后脉冲进行累加计数,来平滑其中的起伏,以减少误 动作,提高同步系统的可靠性和抗干扰性

•

中相积分

A

1

0

1

t0

-A T

积分结果为正,指示取样脉冲超前

A

0

1

0

t0

-A T

积分结果为负,但取样脉冲超前

•

同相积分

A

1

0

1

-A

相邻码元的积分结果为正负,指示当前码元正负

1 0 1

A

-A

相邻码元的积分结果为负正,指示当前码元负正

由以上的分析知: ① 中相积分的大小可反映相差的大小

② 中相积分的结果不能确定相位的超前或滞后关系

零输入端控制)

不是环路滤波器,并且它是无惰性的,不影响环路的阶数

三 数字环路滤波器

数字环路滤波器的作用与模拟环中的相同,都是对误差信号中 的噪声及高频分量进行抑制,并因此影响系统的校正速度与校正精 度 数字滤波器具有以下的一些优点: ① 抗干扰能力强,不怕电磁感应 ② 无阻抗匹配问题

③ 可以工作在很低的频率

④ 可通过编程调节其参数,有较大的灵活性 ⑤ 可以提供很高的处理精度

③ 过零检测式数字锁相环(ZC-DPLL)

④ 超前滞后型数字锁相环(LL-DPLL)

其中:第① 、③ 、④类属于非均匀采样的形式

第②类属于均匀采样的形式

数字锁相环实际上是根据输入与输出的相位差关系,对输出相

位进行量化调整,以实现跟踪的闭环控制系统

二 数字鉴相器

1. 异或门型数字鉴相器

常见的两种由4个与非门组成的异或门电路如下图所示

Δ = 2· / m;反之,输出相位推后Δ。这样,不管起始频差为多 S 少,经过一段时间的调整后, 2都将围绕1前后跳跃,环路处于

锁定状态,存在稳定的相差

可知,分频数m和每次加减脉冲数S(又称为校正步数)是影响 跟踪性能的两个重要参数,m的典型值为64,通常在锁定状态下

取S=1,在捕获状态下,为减小捕获时间而取S >1(S的大小由清

a

& 二进制鉴相器 c c

e

B

m分频

1

常闭 1

设输入信号及输出反馈信号都是对称方波,则环路工作过程可 用图形描述为

a b c c d e

a b c c d e

e >0

e <0

跟踪原理: 设第k个取样时刻的相位差e (k) = 1 (k) -2 (k) >0,则二元

鉴相器输出Vd(k)=1,控制加S个脉冲,从而输出相位提前

2. 触发器型数字鉴相器

通常采用RS触发器,输入信号的上升沿使触发器输出为高电平, 反馈信号的上升沿使触发器输出为低电平,于是输出高电平的持续 时间反映了相位差信息。此方法的最简单的实现形式如下

输入信号

正向 过零检测 正向 过零检测

S

Q

本地参考 信号

R

触发器型鉴相器, 在0<θe<π时,典型的输入输出波形如下:

分频器

标准频率源输出频率相同但相差为π的两路标准频率信号,

0相位的频率信号用于通常的计数和减脉冲,π相位的频率信号 用于加脉冲

工作过程的图形描述

0相位频 率信号 0 π 相位频 率信号 0 无控制 输出信号 1 插入提前 脉冲 T0 2 3 4 5 6 7 5 10 15 20 25 30 5 10 15 20 25 30

奎斯特定理以保留信号的完整频谱

• 数字乘法器进行按时间点相乘的数字运算

4. 过零取样数字鉴相器 • 正向过零点取样: 以本地参考信号的正向过零点对输入信

号进行取样,根据取样值的大小改变本地参考信号的相位 • 过零点取样: 在本地参考信号的正向和反向过零点都对输 入信号进行取样处理的方法