第五章 IO端口

第五章GPIO和中断

对C口的6个GPIO管脚进行操作,设计花 样流水灯

#include "stm32f10x.h“ #define LED_ALL GPIO_Pin_0| GPIO_Pin_1| GPIO_Pin_2| GPIO_Pin_3| GPIO_Pin_4| GPIO_Pin_5 int main(void) { unsigned char j=0; chLsd=0xFF;

对于双向复用功能,端口位必须配置复用功能 输出模式(推挽或开漏)。

如果把端口配置成复用输出功能,则引脚和输出寄 存器断开,并和片上外设的输出信号连接。

如果软件把一个GPIO脚配置成复用输出功能,但是 外设没有被激活,它的输出将不确定。

模拟输入配置

GPIO寄存器的操作

SM32F10X硬件文档.PDF

GPIO_Mode值

例如:IO配置

GPIO_Mode_AIN = 0x0, 模拟输入 GPIO_Mode_IN_FLOATING = 0x04, 浮空输入 GPIO_Mode_Out_OD = 0x14, 表示配置相应管脚为GPIO开漏输出(真双向IO) GPIO_Mode_Out_PP = 0x10, 通用推挽输出模式 GPIO_Mode_AF_OD = 0x1C, 表示配置相应管脚为复用功能的开漏输出 GPIO_Mode_AF_PP = 0x18 复用功能的推挽输出模式

GPIOx_BSRR和GPIOx_BRR寄存器允许 对任何GPIO寄存器的读/更改的独立访问

端口位配置表

I/O端口位输出配置

复用功能配置

复用功能

对于复用的输入功能,端口必须配置成输入模 式(浮空、上拉或下拉)且输入引脚必须由外部 驱动

对于复用输出功能,端口必须配置成复用功能 输出模式(推挽或开漏)。

精选设备管理IO设备

第五章 设 备 管 理

3) 这种分类方式可将I/O (1) 独占设备。 (2) (2) 共享设备。 (3) (3) 虚拟设备。

第五章 设 备 管 理

2. 设备与控制器之间的接口

至设备 控制器

数据信号线 状态信号线

控制信号线

I/O设 备 缓冲 转换器

控制逻辑

信号 数据

图 5-1 设备与控制器间的接口

第五章 设 备 管 理

5.1.2 设备控制器

1. 设备控制器的基本功能 1) 接收和识别命令 2) 2) 数据交换 3) 3) 标识和报告设备的状态 4) 4) 地址识别 5) 5) 数据缓冲 6) 6) 差错控制

第五章 设 备 管 理

2. 设备控制器的组成

CPU与 控 制 器 接 口

数据线

地址线 控制线

T3(缓 冲 3)

T4(缓 冲 4)

(b)

M1

M2

M3

M4

C1

C2

C3

C4

(2) 内存地址寄存器MAR。在输入时,它存放把数据从 设备传送到内存的起始目标地址;在输出时,它存放由内存 到设备的内存源地址。

(3) 数据寄存器DR。用于暂存从设备到内存,或从内存 到设备的数据。

(4) 数据计数器DC。 存放本次CPU要读或写的字(节)数。

第五章 设 备 管 理

3. DMA工作过程 设置AR和DC初值

一是其指令类型单一,这是由于通道硬件比较简单, 其所能执行的命令,主要局限于与I/O操作有关的指令; 再 就是通道没有自己的内存,通道所执行的通道程序是放在主 机的内存中的, 换言之,是通道与CPU共享内存。

第五章 设 备 管 理

2. 通道类型 1) 字节多路通道(Byte Multiplexor Channel)

输入输出接口

六.8086输入/输出指令

1. 输入指令

IN AL, PORT

IN AX, PORT

IN AL, DX

IN AX, DX

2. 输出指令

OUT PORT, AL

OUT PORT, AX

OUT DX, AL

OUT DX, AX

计算机原理讲义

CPU与外设的连接

第5.2节 CPU与外设的连接

一.CPU与外设的一般接口电路

接口功能

D15~D0 A15~A0

A0 BHE IOR IOW

三.接口的功能

数据口 状态口 控制口

I/O装置

➢ 数据缓冲:外设数据输入到总线时需要缓冲。 ➢ 数据锁存:总线数据输出到外设时的锁存,解决CPU

与外设速度不匹配问题。 ➢ 传输控制命令和状态信息:计算机与外设有时需使用

硬件握手。例如:计算机利用查询输出到打印机。 ➢ 信息转换:串并转换、数模转换、电平格式转换

(START)、停止(STOP)或数据的选通(STB)等, 具体由外设的要求而定。 ③ 状态口 ✓ CPU通过状态口了解外设状态。如:

输入外设是否准备好(READY) 转换是否结束(EOC) 输出装置是否忙(BUSY) ✓ 控制信息和状态信息一般也由数据总线传送。

计算机原理讲义

CPU与外设的数据传送方式

D15~D0

A15~A0 A0

BHE IOR IOW

(一)端口

数据口 状态口 控制口

I/O装置

① 数据口:用于完成数据的输入或输出。包括:

✓ 数字量 如用ASCII码表示的数和字符 ✓ 模拟量 如经DAC转换输出的电流 ✓ 开关量 如以一位二进制表示的量

计算机原理讲义

CPU与外设的连接

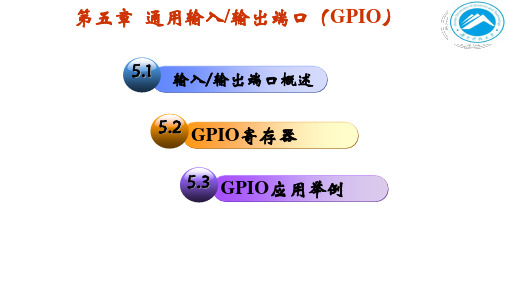

第五章 IO端口、输入捕捉

• 图5-2: 共用的端口结构框图

• 5.3.1 I/O 与多个外设复用

• 对于有些dsPIC30F 器件,尤其是那些带有少量 I/O 引脚数较少的器件,其每个I/O 引脚可能要 复用多种外设功能。图5-2 所示为两个外设与同 一个I/O 引脚复用的示例。

• 和TRISx 寄存器以及该端口引脚将读作0

5.3 外设复用

• 当某个外设使能时,与其相关的引脚将被禁止作为通 用I/O 引脚使用。可以通过输入数据路径读该I/O 引脚, 但该I/O 端口位的输出驱动器将被禁止。

• 与另一个外设共用一个引脚的I/O 端口总是服从于该外 设。外设的输出缓冲器数据和控制信号提供给一对多 路开关。该多路开关选择是外设还是相关的端口拥有 输出数据的所有权以及I/O 引脚的控制信号。图11-2 显示了端口如何与其他外设共用,以及与外设连接的 相关I/O 引脚。

• 参照图5-2,外设多路开关的结构将决定外设输 入引脚是否可以通过使用PORT 寄存器用软件控 制。

• 当图中所示的概念化的外设在功能被使能时,会断开 I/O 引脚与端口数据的连接。一般而言,下列外设允许 通过PORT 寄存器手动控制它们的输入引脚:

• 外部中断引脚 • 定时器时钟输入引脚 • 输入捕捉引脚 • PWM 故障引脚 • 大多数串行通信外设在使能时,将完全控作0 • bit 13 ICSIDL:输入捕捉模块在空闲时停止控制位 • 1 = 输入捕捉模块在CPU 空闲模式将停止 • 0 = 输入捕捉模块在CPU 空闲模式将继续工作 • bit 12-8 未用:读作0 • bit 7 ICTMR:输入捕捉定时器选择位 • 1 = 捕捉事件时捕捉TMR2 的内容 • 0 = 捕捉事件时捕捉TMR3 的内容 • 注: 可供选择的定时器可能会和上述不同。 更多详细

第五章(8259)

采用I/O独立编址方式(但地址线与存储器共用) 地址线上的地址信号用 IO/M来区分:

IO/M=1 时为I/O地址

I/O操作只使用20根地址线中的16根: A15 ~ A0 可寻址的I/O端口数为64K(65536)个 I/O地址范围为0~FFFFH IBM PC只使用了1024个I/O地址(0~3FFH)

符号 ’0’ ’1’ ’2’ ’3’ ’4’ ’5’ ’6’ ’7’

应用例子:发光二极管接口

+5V

D0 | D7 Q0

D0~D7

A0~A15 M/IO

译 码 器

. . .

Q7

=1 . . . =1

R

. . .

. . .

R

CP

WR

74LS373

I/O接口综合应用例

根据开关状态在7段数码管上显示数字或符号 设输出接口的地址为F0H

设输入接口地址为F1H

当开关的状态分别为0000~1111时,在7段数 码管上对应显示’0’和内存地址空间相互独立。 优点:内存地址空间不受I/O编址的影响 缺点:I/O指令功能较弱,使用不同的读写控制 信号

内存地址空间 I/O地址空间 0000H FFFFH

内存空间 (1MB)

00000H

I/O空间 (64KB)

FFFFFH

8088/8086 CPU的I/O编址方式

第5章 数字量输入输出

5.1 概述 1.I/O信号形式 通常有以下4种类型: (1) 数字量: 二进制形式的数据,最小单位为 “位”(bit),8位称为一个字节(BYTE)。 (2) 模拟量: (3) 开关量: 用一位二进制数表示。 (4) 脉冲量:

计算机控制(第五章开关IO电机控制步进电机)

(七)电磁阀接口技术 电磁阀对气体、液体管道的开关进行控制。广泛应用于液 压机械、空调系统、热水器、自动机床等系统中。 电磁阀可分为交流和直流两类,根据其阀位和通道数目有 两位三通、两位四通、三位四通等。 下图为电磁阀的结构原理图。

交流电电磁阀常要使用双向可控硅驱动或用一个直流继 电器作为中间继电器控制。

下图为交流电磁阀的接口电路。MOC3041为光电耦合 器,用于触发双向晶闸管KS,以及隔离单片机和电磁阀系统。

(八)报警程序的设计

常用的报警方式有: 1、 声语言报警:电铃,电笛,频率可调的蜂鸣震 荡音响,集成电子音乐芯片,语音芯片等。 2、 显示报警:LED指示灯,闪烁的白炽电灯, LED、LCD数码管,LED、LCD图形显示器,CRT 显示器等。 3、 图形、声音的混合报警。

三、电机控制接口技术

电动机的应用非常广泛。电机分为动力电机和控制电机。 现代化生产对电机的性能要求越来越高:精度、速度、带 负载能力、灵活性、智能化等。 电机的控制用自动化控制设备,朝向集成化、微型化、智 能化方向发展。微机和单片机使电机控制产生革命性的飞跃。目 前已研制出了许多微机或单片机控制电机的系统及专用控制板。 不远的将来,智能化调速系统、电机一体化等会广泛应用。 (一)小功率直流电机调速原理 小功率直流电机的调速可通过控制电枢平均电压来实现。 用微机或单片机控制,通过改变电枢电压接通时间与通电周期的 比值(即占空比)来控制电机速度——此即脉冲宽度调制PWM。 电机转速由电枢电压Ua决定, Ua越大,电机转速越高。 电机通电时速度增加,断电时速度逐渐减小,控制通、断时间比 即可控制电机转速。 设电机全通电时的转速为Vmax,占空比为D=t1/T,则电机的 平均速度为:Vd=Vmax×D (近似的线性关系)

第5章 IO接口电路的设计

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 0 0

0 1 1 1 0 0

1 0 1 1 1 0 1 1 1

x x x x x x

x x x x x x x x x

C018~C01F C020~C027

C028~C02F C030~C037 C038~C03F

1 1 1

1 1 1

0 0 0

0 0 0

0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 0 0

0 0 0 0 0 1 0 1 0

x x x x x x x x x

C000~C007 C008~C00F C010~C017

1 1

1 1 1

1 1

1 1 1

0 0

0 0 0

0 0

0 0 0

0 0 0 0

开始 初始化 读入状态

N

数据准备好

Y

输入数→CPU

数→内存缓冲区

N Y

传送完? 结束

9

例5-4

查询式输出方式的接口电路

输出 /ACK 设备

数 据 锁存器 (8位) R C

选通 信号 +5V

D7~D0 /WR(写数据) 2 /CS2 /CS1 1

I/O 译码

M//IO A15~A0

Q

D

D触发器

/RD(读状态) D1(数据总线)

10

设:状态口的地址为P_S2,输出口地址 为P_OUT,传送数据的总字节为C_2, 则查询方式输出数据的程序段为: MOV CX,C_2 READ_S2:IN AL,P_S2 TEST AL,02H JZ READ_S2 MOV AL,输出数据 OUT P_OUT,AL LOOP READ_S2 ……

单片机原理及接口技术第5章 IO口应用-显示与开关键盘输入

图5-1

发光二极管与单片机并行口的连接

5

如果端口引脚为低电平,能使灌电流Id从单片机的外部流入内部,则将

大大增加流过的灌电流值,如图5-1(b)所示。所以,AT89S51单片机任 何一个端口要想获得较大的驱动能力,要采用低电平输出。 如果一定要高电平驱动,可在单片机与发光二极管之间加驱动电路,如 74LS04、74LS244等。 5.1.2 单片机I/O端口控制发光二极管的编程 发光二极管与单片机的I/O端口的连接,如图5-1(b)所示。如要点亮 某发光二极管,只需该I/O端口位写入“0”即可。下面通过一个例子介绍如

21

图5-6 4位LED静态显示的示意图

示字符。这样在同一时间,每一位显示的字符可以各不相同。但是,静态

显示方式占用I/O口线较多。 对于图5-6所示电路,要占用4个8位I/O口(或锁存器)。如果数码管 数目增多,则还需要增加I/O口的数目。在实际的系统设计中,如果显示位 数较少,可采用静态显示方式。但显示位数较多时,为了降低成本,一般 采用动态显示方式。 2. 动态扫描显示方式 显示位数较多时,静态显示所占用的I/O口多,为节省I/O口与驱动电路

单片机控制的8位I/O口锁存器输出相连。如果送往各个LED数码管所显示字 符的段码一经确定,则相应I/O口锁存器锁存的段码输出将维持不变,直到

送入下一个显示字符的段码。因此,静态显示方式的显示无闪烁,亮度较

高,软件控制比较容易。 图5-6所示为4位LED数码管静态显示电路,各个数码管可独立显示,

只要向控制各位I/O口锁存器写入相应的显示段码,该位就能保持相应的显

闭合时,P3.0引脚为低电平。单片机对开关状态的检测是由程序检测

10

图5-3

开关、LED发光二极管与P1口的连接

单片机IO端口工作原理

单片机IO端口工作原理在单片机内部,每一个IO端口都对应着一个寄存器,该寄存器称为IO口寄存器,用于控制该IO端口的输入输出状态。

IO口寄存器通常是一个8位或16位的寄存器,每一位对应一个IO端口。

单片机的IO端口工作原理如下:1.输入方式:当一些端口被设置为输入模式时,它可以接收外部信号。

在输入模式下,该端口的电平状态可以被单片机读取到。

通常通过设置IO口寄存器的相应位来控制端口的输入模式。

在输入模式下,可以通过查询或中断方式读取IO端口的状态。

2.输出方式:当一些端口被设置为输出模式时,它可以向外部设备发送信号。

在输出模式下,可以通过设置IO口寄存器相应位的值来控制端口的输出电平状态。

高电平和低电平对应着不同的输出状态,可以通过操作寄存器来改变IO端口的电平状态。

3.端口模式设置:针对每一个IO端口,单片机提供了相应的寄存器来设置其工作模式。

通常包括输入模式、输出模式、上拉模式和下拉模式等。

输入模式和输出模式可以通过设置IO口寄存器的相应位来实现,上拉模式和下拉模式则需要通过设置其他寄存器或器件来实现。

4.状态改变:在一些情况下,IO端口的状态可能发生改变,如按键按下、外部信号触发等。

这时候可以通过查询或中断的方式来获取IO端口的状态变化,然后进行相应的处理。

5.外部设备连接:IO端口通常通过引脚连接到外部设备,如按键、LED灯、LCD显示屏、电机等。

通过IO端口的输出控制可以实现对外部设备的控制,通过IO端口的输入可以获取外部设备的状态。

总之,单片机IO端口通过IO口寄存器进行控制,可以实现与外部设备的信息交换和控制。

通过设置端口的输入输出模式,可以实现数据的输入和输出。

通过查询或中断的方式,可以实时获取IO端口的状态变化。

通过连接外部设备,可以实现对其控制和监测。

第5章.IO接口WY001

5.3.2.程序查询式控制

一. 特点:

I/O操作总是由MPU通过程序查询外设的 状态来启动,即总是MPU主动,I/O被动。

二. 硬件接口结构 输入接口 输出接口

1.输入接口硬件结构

数 据 输 入 设 备

&

Pd

数据 锁存

三态缓冲 器(8位)

DB

Di

输入状态信息

N AB MPU

选 通

> D

R Q

三态缓冲 器(1位)

READY (状态 信息)

Ps

地 址 译 码

IOR

数据就绪?

Y

输入数据 状态位复位

+5V

准备就绪 触发器

&

(a) 硬件结构

(b) 工作流程

输入外设发选通信号锁存数据。Q = 1, READY =1 读状态标志,Ps有效,READY = 1,数据准备就绪; 执行IN 命令,Pd有效, 并使触发器复位

I/O地址译码例

地址范围:

A11

A0

××××001011110000 ××××001011110011

任意状态

片内地址

图中不接入

I/O地址译码例

译码电路图:

A1 A11 A10 A18 A3 A2 A9 A7 A4 ┇ A0

接口芯片

≥1 &

CE

2. 关于Intel系列MPU的I/O编址方式说明:

D7-D0 D7-D0 Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0 D7 D6 D5 D4 D3 D2 D1 D0

D5

IOW

A9 | A3

A15 | A10 A2 A1 A0

第五章 P1、P2、P3

内部总线 写锁存器

D 锁存器 CL

Q Q MUX

引脚

读引脚

P3口

P3口作为通用I/O口使用时是准双向口,工作原理与P1、 P2类似,此时选择输出功能端置“1” 。 P3口输入时,端口锁存器应置“1”。 P3口作为第二功能口使用时,该位的端口锁存器应置 “1”。

Vcc 读锁存器 选择输出功能 内部上拉电阻 引脚 内部总线 写锁存器 D 锁存器 CL Q Q

第五章

并行I/O口

1、P0口:地址/数据总线+准双向IO 2、P1口:准双向IO

3、P2口:高8位地址总线+准双向IO

4、P3口:第二功能(控制总线)+准双向IO

P0口

P0口每位I/O包含一个输出锁存器、一个MUX、两个三 态缓冲器、一个输出控制电路和一个FET推挽输出驱动电路。 P0口既可以作为通用I/O口,又可以作为地址/数据总线。

读引脚

第二输入功能

P3口的第2功能

端口引脚

P3.0 P3.1 P3.2 P3.3 P3.4 P3.5

第二功能

RXD(串行输入口) TXD(串行输出口) (外部中断0输入线,负跳变) (外部中断1输入线,负跳变) T0(定时器0外部输入) T1(定时器1外部输入) (外部数据存储器写选通信号输出 ) (外部数据存储器读选通信号输出)

P3.6 P3.7

举例:用4个发光二极管对应显示4个开关的 开合状态。如P1.0合则P1.4亮。

ORG 0000H AJMP MAIN ORG 0100H MAIN:ORL A,#0FH MOV P1,A MOV A,P1 SWAP A MOV P1,A SJMP MAIN

MCS-51 P1.7 P1.6 P1.5 P1.4 P1.3 P1.2 P1.1 P1.0

微机原理 第五章 IO接口

控 制 逻 辑

8 8

IOR IOW

I/O 端口 (256个) 个

(3)使用专用I/O指令和 (3)使用专用I/O指令和 使用专用I/O 存储器访问指令有明显 区别, 区别,可使编制的程序 清晰易懂,便于检查. 清晰易懂,便于检查.

隔离I/O I/O方式 5.2.2 隔离I/O方式

5-16

2.缺点: 2.缺点: 缺点

AB 存储器 存 储 空 间 DB MPU

读 /写 I/O 端口 RD 源自R 控制 逻辑控制5.2.1 存储器映象方式

5-12

1.优点: 1.优点: 优点

AB 存储器 存 储 空 间 DB MPU

读 /写 I/O 端口 RD WR 控制 逻辑

控制

I/O操作与存储器操作完 (1) I/O操作与存储器操作完 全相同,无需使用专用I/O指 全相同,无需使用专用I/O指 I/O 令,而存储器操作指令及其寻 址方式非常丰富,从而使I/O 址方式非常丰富,从而使I/O 功能增强,编程方便,灵活. 功能增强,编程方便,灵活. I/O端口数目 端口数目( (2) I/O端口数目(即外设数 只受总存储容量的限制, 目)只受总存储容量的限制,大 大增加了系统的吞吐率. 大增加了系统的吞吐率. (3) 使微机系统的读写控制 逻辑简单. 逻辑简单.

存储器 (1MB)

控制

MEMR MEMW

控 制 逻 辑

8 8

IOR IOW

有两个地址空间, 有两个地址空间, 使用不同的读写 MPU 使用不同的读写 控制信号访问存储器 I/O端口 端口. 和I/O端口. MPU访问I/O端口必 访问I/O MPU访问I/O端口必 须采用专用I/O指令. 须采用专用I/O指令. I/O指令

第五章通用和复用功能IO口

第五章通用和复用功能IO口1.引言通用和复用功能IO口是现代数字电路设计中的重要组成部分。

它们允许电路与外部设备进行通信和控制,实现数据的输入、输出和处理。

在本章中,我们将介绍通用和复用功能IO口的基本原理和应用。

通用功能IO口是一种通用的输入/输出接口,可以通过软件来配置不同的功能。

它可以被用作输入口,用来读取外部设备的状态;也可以被用作输出口,用来控制外部设备的运行。

通用功能IO口通常由一组引脚组成,每个引脚都可以配置为不同的功能。

通过编程的方式,我们可以根据需要来选择引脚的功能,并进行相应的输入和输出操作。

复用功能IO口是一种多功能的输入/输出接口,可以通过硬件设置来选择不同的功能。

它通常由一个多路器和多个外设模块组成。

多路器的作用是选择不同的外设模块进行连接,从而实现不同的输入和输出功能。

使用复用功能IO口,可以有效地减少芯片上的引脚数量,提高系统的可扩展性和灵活性。

4.通用功能IO口的应用通用功能IO口广泛应用于各种数字电路设计中。

它可以连接各种外设设备,如按钮、开关、传感器、LED灯等。

通过编程的方式,我们可以读取外设的状态,并根据需要来控制外设的运行。

通用功能IO口还可以连接到其他数字电路中,实现数据的输入、输出和处理。

例如,它可以与存储器、处理器、通信接口等进行连接,实现数据的存储、处理和传输。

5.复用功能IO口的应用复用功能IO口广泛应用于嵌入式系统和通信系统中。

它可以连接各种外设设备,如显示器、触摸屏、以太网接口、USB接口等。

通过硬件设置,我们可以选择不同的外设模块进行连接,并根据需要来实现不同的输入和输出功能。

复用功能IO口还可以连接到其他模块中,实现数据的传输和处理。

例如,它可以与显示模块、通信模块等进行连接,实现图形的显示、数据的传输等。

6.小结通用和复用功能IO口是现代数字电路设计中的重要组成部分。

它们允许电路与外部设备进行通信和控制,实现数据的输入、输出和处理。

通过软件和硬件的配置,我们可以选择引脚的功能,并进行相应的输入和输出操作。

第05章IO接口

举例

IN AL, 60H ;8位输 入指令 IN AX, 78H ;16位输 入指令 MOV DX, 312H ;端口 地址送DX IN AX, DX ;16位间 接输入指令

功能

把指定端口中 的数据读入AL 或AX中

IN ACC, DX

AL/AX ← (DX)

OUT ACC OUT ACC

PORT, DX,

图5-4 输出锁存电路

简单的输入/输出接口(图5-5)

• • 把地址译码、数据锁存与缓冲、状态寄存器、命令寄 存器各个电路组合起来,构成简单输入/输出接口 接口连接的信号: – 与系统总线连接:

地址总线A0~A15 数据总线D0~D7 控制总线M/IO#、RD# 、WR# (最小模式时)或 IOWC#、IORC#(最大模式时)相连接

高电平(无效):缓冲器输出端呈高阻态。 低电平(有效,端口被选中 ):已锁存的数据通过 74LS244送往系统数据总线,被CPU所接收。

图5-3 输入设备接口的数据锁存和缓冲电路

数据(命令)输出端口:

•

CPU送往外设的数据或命令,应由接口进行锁存, 以便使外设有充分的时间接收和处理。

第五章 通用输入输出端口(GPIO)

0x0000 70C1 1

GPAQUAL 0x0000 70C2 1

GPBMUX

0x0000 70C4 1

GPBDIR

0x0000 70C5 1

GPBQUAL 0x0000 70C6 1

GPDMUX

0x0000 70CC 1

GPDDIR

0x0000 70CD 1

GPDQUAL 0x0000 70CE 1

while(1) {

GpioDataRegs.GPASET.all =0xAAAA; GpioDataRegs.GPACLEAR.all =0x5555; delay_loop(); GpioDataRegs.GPACLEAR.all =0xAAAA; GpioDataRegs.GPASET.all =0x5555;

while(1)

{ GpioDataRegs.GPADAT.all =0xAAAA; delay_loop();

GpioDataRegs.GPADAT.all delay_loop(); } }

=0x5555;

使用SET/CLEAR寄存器反转触发I/O引脚

void Gpio_example2(void) {

端口设置

void Gpio_select(void)

{

Uint16 var1;

Uint16 var2;

Uint16 var3;

var1= 0x0000;

// sets GPIO Muxs as I/Os

var2= 0xFFFF;

// sets GPIO DIR as outputs

var3= 0x0000;

//所有中断,标志清零。

IER = 0x0000; //关闭CPU中断,清除所有CPU中断标志;

第五章并行输入输出接口

图5.5 无条件传送方式

例1:一个采用无条件传送的数据采集系统

图5.6 无条件输入的数据采集系统

这是一个16位精度的数据采集系统。被采集的8个模拟 量,由继电器绕组P0、P1、…、P7分别控制触点K0、K1 、 …、K7逐个接通。每次采样转换成16位BCD码,高8 位和低8位通过两个端口(端口地址为11H和10H)输入 到计算机。CPU通过端口20H输出控制信号,以控制继电 器的吸合,实现采集不同通道的模拟量。 采集过程如下: (1)先断开所有的继电器触点,不采集数据; (2)延迟一段时间后,使K0闭合,采集第1个通道的模 拟量,并保持一段时间,以使数字电压表将模拟电压转 换为16位BCD码; (3)分别将高8位与低8位BCD码存入内存,并转存到 DSTOR开始的数据区; (4)利用移位与循环实现8个模拟量的依次采集和存储。

3、开关式可选择译码电路

如果用户希望译码器能适应不同的地址分配场合,则 可采用开关式地址可选择译码电路,如图5.4所示。电路 用DIP开关选择地址,并使用了一片74LS688八位数据比 较器。当输入端P0-P7的地址与设置端Q0-Q7的状态一致 时,输出P=Q 为低,其输出控制地址译码芯片74LS138的 译码。图中,上面一片74LS138产生读端口地址,下面一 片74LS138产生写端口地址,这样使8个口地址作16个口 地址用。此电路必须A9=1,AEN=0时才能有效译码。( AEN=0是CPU控制总线, AEN=1时DMA控制总线)。

IO端口原理

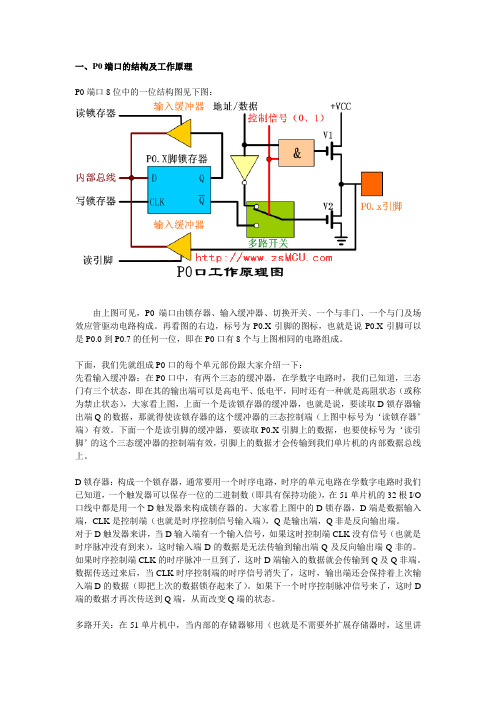

一、P0端口的结构及工作原理P0端口8位中的一位结构图见下图:由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成。

再看图的右边,标号为P0.X引脚的图标,也就是说P0.X引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

下面,我们先就组成P0口的每个单元部份跟大家介绍一下:先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上图,上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为‘读锁存器’端)有效。

下面一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O 口线中都是用一个D触发器来构成锁存器的。

大家看上图中的D锁存器,D端是数据输入端,CLK是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CLK没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q非的。

如果时序控制端CLK的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CLK时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D 端的数据才再次传送到Q端,从而改变Q端的状态。

多路开关:在51单片机中,当内部的存储器够用(也就是不需要外扩展存储器时,这里讲的存储器包括数据存储器及程序存储器)时,P0口可以作为通用的输入输出端口(即I/O)使用,对于8031(内部没有ROM)的单片机或者编写的程序超过了单片机内部的存储器容量,需要外扩存储器时,P0口就作为‘地址/数据’总线使用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

例:使用RB口控制G6区的8个指示灯,循 环移位点亮,瞬间只有一个灯亮。发光二 极管点亮

共阳极

输入输出端口

功能:MCU与外界交换信息的通道。 引脚的复用功能:

– 通用I/O – 支持外部设备

I/O端口的功能:

– 并行I/O端口 – 模拟端口引脚配置 – 输入电平变化中断模式

相关的I/O端口引脚: RB0~RB15 RC12~RC15 RD0~RD11 RE0~RE7 RF0~RF6 RG2~RG9

休眠和空闲模式下的CN 工作

CN 模块在休眠或空闲模式下继续工作。

– 如果使能的CN 引脚中的一个改变了状态, CNIF (IFS1<3>)状态位将被置1。 – 如果CNIE 位(IEC1<3>)被置1,则器件将从休眠或 空闲模式唤醒并恢复工作。

如果为CN 中断分配的优先级等于或低于当前 CPU 的优先级,则器件会紧随SLEEP 或IDLE 指 令后的那条指令继续执行。 如果为CN 中断分配的优先级高于当前CPU 的优 先级,则器件将从CN 中断向量地址继续执行。

变化通知(CN)引脚

CN 配置和操作

CN 引脚配置如下: 1. 通过将TRISx 寄存器中的相关位置1,确保CN 引脚配置为数字输 入引脚。 2. 通过将CNEN1 和CNEN2 寄存器中的相应位置1,允许所选的CN 引脚中断。 3. 通过将CNPU1 和CNPU2 寄存器中的相应位置1,打开所选的CN 引脚的弱上拉器件(如果需要)。 4. 清零CNIF (IFS1<3>)中断标志。 5. 使用CNIP<2:0> 控制位(IPC4<14:12>)为CN 中断选择所需的中 断优先级。 6. 使用CNIE (IEC1<3>)控制位允许CN 中断。 当CN 中断发生时,用户应读取与该CN 引脚相关的PORT 寄存器。 这样做将清除引脚电平不匹配条件,并设置CN 逻辑电路以检测下一 次引脚电平变化。可以将当前的端口值与上一次CN 中断时得到的端 口读出值比较,来确定发生过变化的引脚。

模拟端口

AD1PCFG 和TRIS 寄存器控制A/D 端口引脚的操 作。若希望端口引脚为模拟输入引脚,则必须将 相应的TRIS 位置1 (输入)。如果将TRIS 位清 零(输出),则该引脚的数字输出电平(VOH 或 VOL)将被转换。 读取PORT 寄存器时,所有配置为模拟输入通道 的引脚均读为0 (低电平)。配置为数字输入的 引脚不对模拟输入信号进行转换。

;Turn LED @ PORTA bit 0 ON ;Turn LED @ PORTA bit 1 ON

RMW 问题的解决方法

对LAT寄存器使用R-M-W 指令:

– BSF LATA,#0 – BSF LATA,#1

LAT 寄存器

与I/O 引脚相关的LALAT 寄存器之间的差异可以归纳如下:

IO口的外设复用

复用数字输入外设 外设不控制TRISx 寄存器。 PORTx寄存器可以读取引脚值。 PORTx数据输入路径不受影响。 外设输入路径使用特殊输入缓冲器,与IO 输入路径相互独立

变化通知(CN)引脚

电平变化通知(Change Notification,CN) 引脚使PIC24F 器件能够向处理器发出中断 请求,以响应所选择的输入引脚上的状态 变化。 可以选择(使能)最多24 个输入引脚来产 生CN 中断。 可用的CN 输入引脚总数取决于所选的 PIC24F 器件。具体查看引脚图

IO口的外设复用

下列外设允许通过PORT 寄存器手动控制它们的输入引脚:

– – – – 外部中断引脚 定时器时钟输入引脚 输入捕捉引脚 PWM故障引脚

大多数串行通信外设在使能时,将完全控制I/O 引脚,因此不 能通过相应的PORT 寄存器影响与该外设相关的输入引脚。 这些外设如下:

– – – – – SPI I2C DCI UART CAN

PORTx Function PINs

Drive Logic

Interfacing to 5V devices

5V tolerant input and Open drain configuration simplifies 5V interface

Interfacing to 5V devices

通用I/O

所有端口都为施密特触发输入,提高了抗噪声能力。

I/O 端口控制寄存器

有4 个与该端口操作直接相关的寄存器:

– TRISx: 数据方向寄存器 – PORTx:I/O 端口寄存器 – LATx: I/O 锁存寄存器 – ODCx: I/O 开漏控制寄存器

注:

– 器件上的每个I/O 引脚在TRIS、PORT、LAT 和ODC 寄存器中都分别有一个相关的位。 – 其中字母“x”表示特定的I/O 端口:

ODC 寄存器

每个I/O 引脚都可以单独配置为正常数字输 出( ODC 位为1)或开漏输出( ODC 位 为0 )。 ODC 位仅对输出引脚有效。 复位后, ODCx 寄存器的所有位的状态被 设置为0。

I/O 的开漏输出

15 7 6 5 4 3 2 1 0

0

0

0

1 0

0

0

0

0

0

ODCx

OD

CN 控制寄存器

有4 个与CN 模块相关的控制寄存器。

– CNEN1 和CNEN2 寄存器包含CNxIE 控制位, 其中“x”表示CN 输入引脚的编号。要让某个 CN 输入引脚中断CPU,必须将其CNxIE 位置 1。 – CNPU1 和CNPU2 寄存器包含CNxPUE 控制 位。每个CN 引脚连接一个弱上拉器件,该器 件可以通CNxPUE 控制位使能或禁止。 – 弱上拉器件充当连接到该引脚的电流源,并且 当连接了按钮或键盘设备时,有了该器件即可 不需要外部电阻。

端口可当作寄存器来访问(读入或写出) 每个端口的每个引脚可分别设置为输入(1) 或输出(0) 复位后,所有端口引脚都被定义为输入。

15 7 6 5 4 3 2 1 0

1

1

1

0 1

1

0 1

1

1

1 0

TRISA

I

I

I

I O

I

O I

I

I

O I

PORTA

引脚

数字 I/O 口 – 16-位

BSET PORTA,#0 BSET PORTA,#1

Interfacing to low impedence 5V load with open drain feature

5V 5V

PIC24FJxxxx

PIC24FJxxxx

Logic low

Load on

Logic high

Load Off

IO口的外设复用

许多引脚还支持一个或多个外设模块。当 配置为操作外设时,引脚不能用作通用输 入或输出。

– – – – 写PORTx 寄存器就是将数据值写入该端口锁存器。 PORTx 写LATx 寄存器就是将数据值写入该端口锁存器。 读PORTx 寄存器就是读取I/O 引脚上的数据值。 读LATx 寄存器就是读取保存在该端口锁存器中的数据 值。

PORT 寄存器

– 通过PORTx寄存器访问I/O引脚上的数据。 – 读PORTx寄存器是读取I/O引脚上的值; – 写PORTx寄存器是将值写入端口数据锁存器。 – 注意都是读-修改-写操作指令。如BSET 和 BCLR,