ATMEGA16的IO端口

Atmegal16单片机寄存器

ATMEGAL16二、寄存器(1)I: 全局中断使能I=1:允许全局中断C=0:禁止全局中断(2)T:位复制存储将寄存器某一位复制到T,或将T复制到寄存器某一位(3)H:半进位标志位H=1:低4位向高4位有进位H=0:低4位向高4位无进位(4)S:符号位S=N异或V(5)V:2进制补码溢出标志V=1:2进制补码有溢出V=0:2进制补码无溢出(6)N:负数标志位N=1:结果是负数N=0:结果是正数(7)Z:零标志Z=1:结果是零Z=0:结果不是零(二、三)SPH,SPL:堆栈指针堆栈区的初地址,SPL是低8位,SPH是高8位(1)SE:睡眠使能SE=1:使能睡眠模式SE=0:禁止睡眠模式SRE:外部扩展使能(2)SM2,SM1,SM0:睡眠模式选择JTD=1:JTAG测试使能JTD=0:禁止JTAG测试(2)ISC2:外中断2触发方式ISC2=1:上升沿中断ISC2=0:下降沿中断(3)JTRF:JTAG测试复位标志JTRF=1:JTAG复位JTRF=0:JTAG没复位(4)WDRF:看门狗复位标志WDRF=1:看门狗复位WDRF=0:看门狗没复位(5)BORF:掉电检测复位标志BORF=1:掉电检测复位BORF=0:没掉电(6)EXTRF:外部引脚复位标志EXTRF=1:外部引脚复位EXTRF=0:外部引脚没复位(7)PORF:上电复位标志PORF=1:上电复位PORF=0:没上电复位(六)SFIOR:特殊功能(2)ACME:模拟比较器多路复用器使用标志ACME=1:ADC多路复用器为模拟比较器选择负极输入ACME=0:AN1连接到比较器负极(3)PUD:禁止上拉电阻PUT=1:禁止上拉电阻PUT=0:允许上拉电阻(4)PSR2:T/C2预分频复位PSR2=1:T/C0预分频复位PSR2=0:不操作(5)PSR10:T/C1或0预分频复位PSR10=1:T/C1或0预分频复位PSR10=0:不操作(七、八)EEARH ,EEARL:EEPROM地址EEARH是高地址,EEARL是低地址(九)EEDR:EEPROM读写的数据EERIE=1:允许EEPROM中断EERIE=0:禁止EEPROM中断(2)EEMWE:EEPROM写使能EEMWE=1:允许EEPROM写EEMWE=0:禁止EEPROM写(3)EEWE:写EEPROMEEWE=1:写EEPROMEEWE=0:无操作(4)EERE:读EEPROMEERE=1:读EEPROMEERE=0:无操作当PORTnn置位时是高电平。

AVR单片机项目4 ATmega16单片机IO接口应用

二、I/O接口的寄存器

在GCCAVR C环境中,头文件“io.h”中定义了许多用于控 制I/O接口输入/出操作的宏,这些宏与I/O寄存器同名,通 过这些宏可以控制A、B、C、D接口的输入输出操作。 当A、B、C、D接口用于数据I/O口时,通过DDRx、 PORTx和PINx三个宏控制接口的输入与输出(其中x为A、B、 C或D)。例如: ①DDRA为A口数据方向寄存器,用来定义A口的通讯方 向(输入/输出); ②PORTA为A口数据寄存器,用来输出数据(输入时, PORTX为高,打开上拉电阻);当PORTx=1时,I/O引脚高 电平,可提供输出20mA电流;当PORTx=0时,I/O引脚低电 平,可吸纳20mA电流。因此,AVR的I/O在输出方式下提供 了比较大驱动能力,可以直接驱动LED等小功率外围器件。 ③PINA用来读取A口数据(只读)。

位

复位值

0

0

0

0

0

0

0

0

二、I/O接口的寄存器

端口输入寄存器:PINX(PINA)-----只读

PINA.7 PINA.6 PINA.5 PINA.4 PINA.3 PINA.2 PINA.1 PINA.0 N/A N/A N/A N/A N/A N/A N/A N/A

位 复位值

特殊功能寄存器:SFIOR

《单片机应用技术》

项目四 ATmega6单片机I/O口应用

任务一 项目知识点学习 任务二 LED闪烁灯控制 任务三 LED开关灯控制 任务四 汽车转向灯控制 任务五 霓虹灯控制 任务六 继电器控制照明设备

【知识目标】

1. 2.

3.

了解LED发光二极管的驱动控制方法 了解ATmega16单片机数字I/O口的结构 了解ATmega16单片机数字I/O口的相关寄 存器功能

ATmega16单片机小系统板简介

1.概述本单片机小系统板为一单元实验板,使用一颗基于A VR构架的A Tmega16单片机。

A Tmega16有16KB的程序存储空间,1KB内部SRAM,512B内置EEPROM。

外部共有32个GPIO,一路USART,一路主从SPI,一路I2C,两个8位定时器,一个16位定时器,4通道PWM输出,8路10位AD输入。

还有各种丰富的管脚中断和不同的时钟可供使用。

2.硬件说明1.本单片机小系统板的电源输入电压为DC 2.7--5V,科创课程实验建议使用DC 5V。

2.小系统板上的P1为下载口,可供程序烧录、eeprom数据读写、熔断丝设置。

3.小系统板上的接插件PB、PC、PD分别对应A Tmega16芯片引脚的PB、PC、PD口。

PB、PC、PD口是八位数据端口,可作为通用IO口,也可用作第二功能使用,具体请参见datasheet的相关部分。

4.小系统板上的接插件PA的1-5脚分别连接A Tmega16芯片PA口的PA0-PA4,PA0-PA4是AD转换的模拟电压输入端口,也可作为通用IO口使用。

5.小系统板上的接插件PA的9脚连接A Tmega16芯片的V ref ,10脚接地。

A Tmega16有一个标称值为2.56V的内部基准源,每颗芯片的实际值会有所不同。

6.A Tmega16 PA口的PA5-PA7作为串行数据输出到小系统板上的74HC595上,有二片74HC595驱动4位数码管和4个LED灯。

小系统板上的P2作为串行数据输出总线,可级联74HC595。

7.小系统板上的四个按钮SW1-4分别连接在A Tmega16芯片PC4-7。

按钮RST为复位键。

3.开发环境推荐的入门开发环境为A VR studio 4 + WinA VR,即使用Atmel的免费IDE A VR studio 4和基于gcc的WinA VR编译器。

软件安装这两个软件的安装非常简单,双击之后一路回车即可。

官方下载地址:A VR studio 4:/dyn/products/tools_card.asp?tool_id=2725WinA VR:/projects/winavr/files/课程FTP://202.120.39.248也会提供软件包。

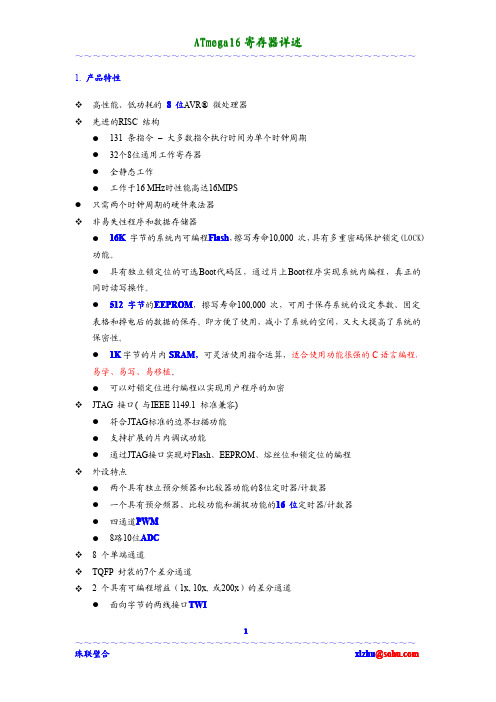

ATmega16寄存器详述

5

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ @ 珠联璧合 xlzhu xlzhu@

ega1 6 寄存器详述 ATm ATmega1 ega16

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

表2 端口引脚配置 DDRXn 0 0 0 1 1 PORTXn 0 1 1 0 1 PUD × 0 1 × × I/O 输入 输入 输入 输出 输出 上拉电阻 否 是 否 否 否 说明 I/O 三态输入 I/O 口带上拉电阻输入 高阻态 推免0输出 推免1输出

点,可直接驱动LED、SSR或继电器。 � � 40引脚PDIP封装,44引脚TQFP 封装,与44引脚MLF封装。

工作电压 � � ATmega16L:2.7 - 5.5V ATmega16:4.5 - 5.5V

�

速度等级 � � 0 ~8 MHz ATmega16L 0 ~16 MHz ATmega16

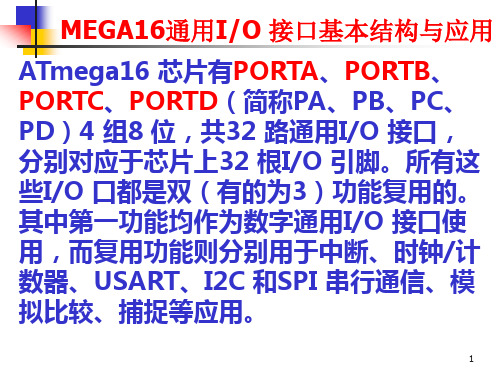

3. I/O 端口 3.1 I/O 端口特性 � � � � 共有PA~PD四组通用I/O口,每组I/O都是8位寄存器。 作为通用数字I/O 使用时,所有AVR I/O 端口都具有真正的读-修改-写功能。 输出缓冲器具有对称的驱动能力,可以输出或吸收大电流,直接驱动LED。 所有的端口引脚都具有与电压无关的上拉电阻。并有保护二极管与VCC 和地相连。

◎输入引脚地址 PINA

BIT PINA 读/写 初始值 7 PINA7 R N/A 6 PINA6 R N/A 5 PINA5 R N/A 4 PINA4 R N/A 3 PINA3 R N/A 2 PINA2 R N/A 1 PINA1 R N/A 0 PINA0 R N/A

5 PB 口寄存器 3. 3.5 ◎数据方向寄存器 DDRB

ATmega16_00硬件系统基本I0口使用

时钟源

ATmega16芯片有如下几种通过Flash熔丝位进行选 择的时钟源。时钟输入到AVR时钟发生器,再分配到相 应的模块。 •缺省时钟 器件出厂时缺省设置的时钟源是1 MHz 的内部RC振 荡器,启动时间为最长。这种设置保证用户可以通过 ISP 或并行编程器得到所需的时钟源。 •晶体振荡 XTAL1 与XTAL2 分别为用作片内振荡器的反向放大 器的输入和输出,这个振荡器可以使用石英晶体,也可 以使用陶瓷谐振器。

主要构成:

AVR CPU部分 程序存储器Flash 数据存储器SRAM和EEPROM 各种功能的外围接口,IO口,以及与他们 相关的数据、控制、状态寄存器等

8位数据总线

Flash程序 存储器

程序计数器

状态和控制

指令寄存器

32× 8 通用寄存器

中断单元 SPI单元 看门狗定时器

指令译码器

2个带预分频器、具有比较、PWM功能的8位定时器/ 计数器 1个带预分频器、具有比较、捕获和PWM功能 的16位定时器/计数器 1个具有独立振荡器的异步实时时钟(RTC) 4个PWM通道 8通道10位ADC 1个I2C的串行口 1个可编程的串行USART接口 1个主/从收/发的SPI同步串行接口 带片内RC振荡器的可编程看门狗定时器WDT 片内模拟比较器

//将端口A的第七位翻转 //将局部变量的第七位翻转 //将全局变量的第七位翻转

位操作

“按位与”用于检查某一位或某几位是否为1 #include<iom16v.h> #include<macros.h> unsigned char gtmpA void main() { unsigned char tmpB; while(tmpB&0x80) //查询局部变量第七位是否为“1” { //查询PA.7是否为“1” if(PINA&0x80) PORTA &=~0x80; //关闭A端口第七位 else …… } }

ATmega16单片机端口讲解新

软件消抖 如果按键较多,常用软件方法去抖,即检测出键闭

合后执行一个延时程序,5ms~10ms的延时,让前沿抖动 消失后再一次检测键的状态,如果仍保持闭合状态电平, 则确认为真正有键按下。

图2-13 按键消抖

3、软件算法设计——查询法

2 U9

74HC164

8

dp g f e d c b a

13 12 11 10 6 5 4 3 1

2 U10

74HC164

8

L4 R45~52

dp g f e d c b a

13 12 11 10 6 5 4 3 1

2 U11

74HC164

8

GND GND 168 GND 28 GND 39

图2-12 硬件设计

数码管的字型码——共阴极:

7பைடு நூலகம்ls164引脚图和真值 表:

A1 A2 QA QB QC QD GND

1

14

2

13

3

12

4

11

5

10

6

9

7

8

2-9 引脚图

VCC QH QG QF QE RESET CLOCK

2-10 真值表

TTL电平和CMOS电平的区 别:

TTL CMOS

VOH ≥2.4V VOL ≤0.4V

按键消抖程序:

if(!AJ1) {

__delay_cycles(80000);//延时10ms消抖 if(!AJ1) //确认有键按下

{ while(!AJ1);//等待按键释放

}

}

ATmega16的中断源:

atmega16存器介绍

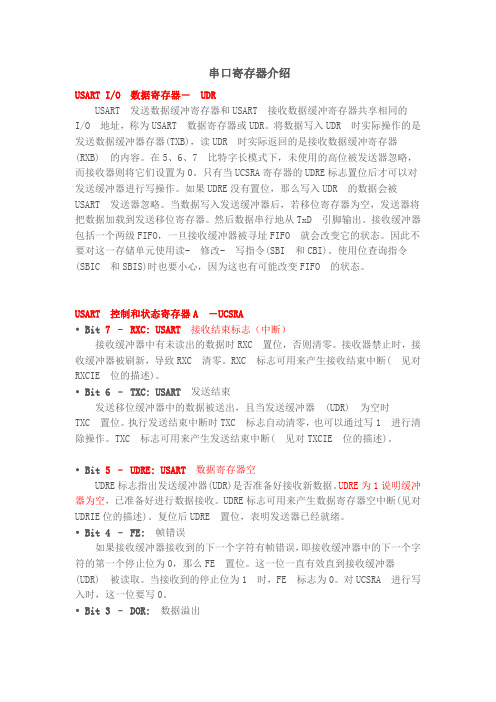

串口寄存器介绍USART I/O 数据寄存器- UDRUSART 发送数据缓冲寄存器和USART 接收数据缓冲寄存器共享相同的I/O 地址,称为USART 数据寄存器或UDR。

将数据写入UDR 时实际操作的是发送数据缓冲器存器(TXB),读UDR 时实际返回的是接收数据缓冲寄存器(RXB) 的内容。

在5、6、7 比特字长模式下,未使用的高位被发送器忽略,而接收器则将它们设置为0。

只有当UCSRA寄存器的UDRE标志置位后才可以对发送缓冲器进行写操作。

如果UDRE没有置位,那么写入UDR 的数据会被USART 发送器忽略。

当数据写入发送缓冲器后,若移位寄存器为空,发送器将把数据加载到发送移位寄存器。

然后数据串行地从TxD 引脚输出。

接收缓冲器包括一个两级FIFO,一旦接收缓冲器被寻址FIFO 就会改变它的状态。

因此不要对这一存储单元使用读- 修改- 写指令(SBI 和CBI)。

使用位查询指令(SBIC 和SBIS)时也要小心,因为这也有可能改变FIFO 的状态。

USART 控制和状态寄存器A -UCSRA• Bit 7 – RXC: USART 接收结束标志(中断)接收缓冲器中有未读出的数据时RXC 置位,否则清零。

接收器禁止时,接收缓冲器被刷新,导致RXC 清零。

RXC 标志可用来产生接收结束中断( 见对RXCIE 位的描述)。

• Bit 6 – TXC: USART 发送结束发送移位缓冲器中的数据被送出,且当发送缓冲器 (UDR) 为空时TXC 置位。

执行发送结束中断时TXC 标志自动清零,也可以通过写1 进行清除操作。

TXC 标志可用来产生发送结束中断( 见对TXCIE 位的描述)。

• Bit 5 – UDRE: USART 数据寄存器空UDRE标志指出发送缓冲器(UDR)是否准备好接收新数据。

UDRE为1说明缓冲器为空,已准备好进行数据接收。

UDRE标志可用来产生数据寄存器空中断(见对UDRIE位的描述)。

Atmega16的IO使用

例4.2.2二进制数输出控制

如图4-6所示为二进制数输入、输出控制的电路原理图。

图4-6 并行输入/输出应用

PC口作为输入接口使用,每一位接有上拉电阻和开关。 当开关断开时,输入为高电平,读取的结果为1;当开关 闭合时,输入为低电平,读取的结果为0。这样8个开关 s0~s7的状态可以组成一个8位的二进制输入数。如图4-7 所示,s7、s5、s2、s0断开,s6、s4、s3、s1闭合。 开关: S7 S6 S5 S4 S3 S2 S1 S0 状态: 开 闭 开 闭 闭 开 闭 开 输入值:1 0 1 0 0 1 0 1 所以,输入的二进制数为0xa5。

位控制

位控制具有把一个位变量输出到某个引脚的含义。所以 位控制时,赋值语句的左边为接口输出变量的位操作符。 例如把C口的第0位控制为高电平,可编写程序如下: DDRC=0xff; PORTC.0=1;

位运算

位运算一般有:置1、清0、取反、与、或、非、异或等运算。 置1:位变量=1; 清0:位变量=0; 取反:位变量=!位变量 与运算:位变量3=位变量1&位变量2 或运算:位变量3=位变量1|位变量2 异或运算:位变量3=位变量1^位变量2 非运算:位变量2=!位变量1

并行输入工作原理 并行输出工作原理 并行输入/输出接口工作原理

并行输入图4-1所示。引脚的 状态取决于外电路,缓冲器后的状态为引脚状态,三态门的输 出由RP端控制,当RP为0时,三态门的输出为高阻状态,数据 总线不受引脚影响;当RP为1时,三态门的输出与输入相同, 此时为读引脚状态。在读接口时,RP控制端有效。

并行输入接口某一位的简化接口电路如图:

并行输出工作原理

并行输出接口中某一位的简化接口电路如图所示。当控制端WP为0 (低电平)时,数据锁存器的输出端Q为上次输出的值,与输入端D 无关,数据总线操作不影响输出。当控制端WP为1时,数据锁存器 的输出端Q的值为输入端D的值,为输出数据状态。数据输出到引脚。 锁存器输出端Q为0时,输出为低电平;锁存器输出端Q为1时,输出 高电平。RL控制端为读取输出值。

AVR教程系列一(6):ATmega16 简介(一)

ATmega16 简介ATmega16是基于增强的AVR RISC结构的低功耗8 位CMOS微控制器。

由于其先进的指令集以及单时钟周期指令执行时间,ATmega16 的数据吞吐率高达1 MIPS/MHz,从而可以缓减系统在功耗和处理速度之间的矛盾。

ATmega16 AVR 内核具有丰富的指令集和32 个通用工作寄存器。

所有的寄存器都直接与算逻单元(ALU) 相连接,使得一条指令可以在一个时钟周期内同时访问两个独立的寄存器。

这种结构大大提高了代码效率,并且具有比普通的CISC 微控制器最高至10 倍的数据吞吐率。

ATmega16 有如下特点:16K字节的系统内可编程Flash(具有同时读写的能力,即RWW),512 字节EEPROM,1K 字节SRAM,32 个通用I/O 口线,32 个通用工作寄存器,用于边界扫描的JTAG 接口,支持片内调试与编程,三个具有比较模式的灵活的定时器/ 计数器(T/C),片内/外中断,可编程串行USART,有起始条件检测器的通用串行接口,8路10位具有可选差分输入级可编程增益(TQFP 封装) 的ADC ,具有片内振荡器的可编程看门狗定时器,一个SPI 串行端口,以及六个可以通过软件进行选择的省电模式。

工作于空闲模式时CPU 停止工作,而USART、两线接口、A/D 转换器、SRAM、T/C、SPI 端口以及中断系统继续工作;掉电模式时晶体振荡器停止振荡,所有功能除了中断和硬件复位之外都停止工作;在省电模式下,异步定时器继续运行,允许用户保持一个时间基准,而其余功能模块处于休眠状态; ADC 噪声抑制模式时终止CPU 和除了异步定时器与ADC 以外所有I/O 模块的工作,以降低ADC 转换时的开关噪声; Standby 模式下只有晶体或谐振振荡器运行,其余功能模块处于休眠状态,使得器件只消耗极少的电流,同时具有快速启动能力;扩展Standby 模式下则允许振荡器和异步定时器继续工作。

第2讲单片机IO端口

12

继电器控制

例6.2 控制恒温箱的加热的硬件电路设计 恒温箱的加热源采用500W 电炉,电炉的工 作电压220v,电流2.3A。选用HG4200 继电器, 开关负载能力为5A/AC220V,继电器吸合线圈 的工作电压5v,功耗0.36W,计算得吸合电流 为0.36/5 = 72mA。设计控制电路如图6-8。 I/O 引脚输出“1”时,三极管导通,继电器吸合, 电炉开始加热。I/O 引脚输出“0”时,三极管 截止,继电器释放,加热停止。

端口A 数据寄存器- PORTA 端口A 数据方向寄存器- DDRA 端口A 输入引脚地址- PINA

27

28

29

30

8

式中,Vled 为LED 的导通电压。 由于AVR 的I/O 口输出“0”时,可以吸收最大 40mA 的电流,因此采用控制发光二极管 负极的设计比较好。8 个LED 发光二极管控制系 统的硬件电路见图6-6。

9

10

2) 软件设计 ATmega16 的PA 口工作在输出方式下,8 个 引脚分别控制8 个发光二极管。 当I/O 口输出“0”时LED 导通发光,输出“1” 时LED 截止熄灭。 下面给出一个简单的控制程序,其完成的功 能是8 个LED 逐一循环发光1 秒,构成 “走马灯”

1

通用I/O 口的基本结构与特性

图6-1 为通用I/O 口的基本结构示 意图。从图中可以看出,每组I/O 口配备三个8 位寄存器,它们分别 是方向控制寄存器DDRx,数据寄存 器PORTx,和输入引脚寄存器PINx (x=A\B\C\D)。I/O 口的工作方式 和表现特征由这3 个I/O 口寄存器 控制。

6

1) 使用AVR 的I/O 口,首先要正确设置其工 作方式,确定其工作在输入方式还是输入方 式。 2) 当I/O 工作在输入方式,要读取外部引脚 上的电平时,应读取PINxn 的值,而不是 PORTxn 的值。 3) 当I/O 工作在输入方式,要根据实际情况 使用或不使用内部的上拉电阻。 4) 一旦将I/O 口的工作方式由输出设置成输 入方式后,必须等待一个时钟周期后才能正 确的读到外部引脚PINxn 的值。

ATMEGA16的寄存器详细说明

ISC01

ISC00

INT0中断

0

0

低电平中断

0

1

INT1 引脚上任意的逻辑电平变化都将引发中断

1

0

下降沿中断

1

1

上升沿中断

3.通用中断屏蔽寄存器 GICR

bit7

bit6

bit5

INT1

INT0

INT2

INT1:使能外部中断请求1 INT0:使能外部中断请求0 INT2:使能外部中断请求2

4.通用中断标志寄存器 GIFR

0x24

INT2

外部中断请求2

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ 6

☆萧联珠☆

☆azhu_uestc@

Atmega16 寄存器

20

0x26

TIMER0 COMP

21

0x28

SPM_RDY

定时器/ 计数器0 比较匹配 保存程序存储器内容就绪

1.状态寄存器 SREG

定时器/计数器1事件捕捉

7

0x0c

TIMER1 COMPA

定时器/计数器1比较匹配 A

8

0x0e

TIMER1 COMPB

定时器/计数器1比较匹配B

9

0x10

TIMER1 OVF

定时器/计数器1溢出

10

0x12

TIMER0 OVF

定时器/计数器0溢出

11

0x14

SPI,STC

SPI 串行传输结束

12

0x16

Bit4

Bit3

Bit2

Bit1

Bit0

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ 4

第8章 Mega16 IO端口应用

// position 为控制位的位置 // PA 口输出全 1,LED 全灭 // PA 口工作为输出方式

Logo 8.4 I/O口应用实例

实例2:设计一个4种闪烁方式交替循环的彩灯,闪烁方式如图8-6 所示:

图8-6

Logo � 提示:在CVAVR中,提供int rand (void)和void srand(int seed)函数,产生随机数。函数包含在头文件stdlib.h中,具体 内容查阅CVAVR帮助文档。

Logo

� ATmega16芯片有PORTA、PORTB、PORTC、 PORTD(简称PA、PB、PC、PD)4组8位,共 32路通用I/O 接口,分别对应于芯片上32根I/O引 脚。

图8-1

Logo

图8-2为AVR单片机通用I/O口的 基本结构示意图。从图中可以看 出,每组I/O口配备三个8位寄存 器,它们分别是方向控制寄存器 DDRx,数据寄存器PORTx ,和 输入引脚寄存器PINx (x=A\B\C\D)。I/O口的工作方 式和表现特征由这3个I/O口寄存 器控制。

ATmega16A引脚功能说明

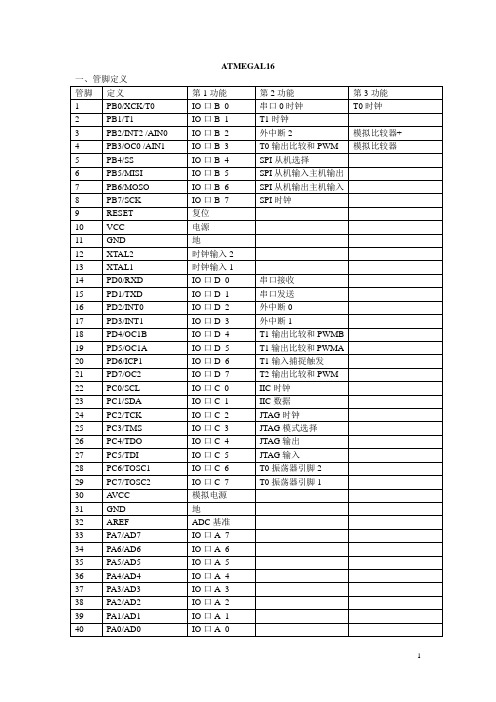

引脚功能说明:

VCC 数字电路的电源

GND地

端口A(PA7..PA0) 端口A 做为A/D 转换器的模拟输入端

端口B(PB7..PB0) 端口B 为8 位双向I/O 口,具有可编程的内部上拉电阻

端口C(PC7..PC0)端口C 为8 位双向I/O 口,具有可编程的内部上拉电阻。

端口D(PD7..PD0)端口D 为8 位双向I/O 口,具有可编程的内部上拉电阻RESET复位输入引脚。

持续时间超过最小门限时间的低电平将引起系统复位

XTAL1反向振荡放大器与片内时钟操作电路的输入端。

XTAL2反向振荡放大器的输出端。

AVCC AVCC是端口A与A/D转换器的电源。

不使用ADC时,该引脚应直接与VCC连接。

使用ADC

时应通过一个低通滤波器与VCC 连接。

AREF A/D 的模拟基准输入引脚。

AVRATmega16实验教程

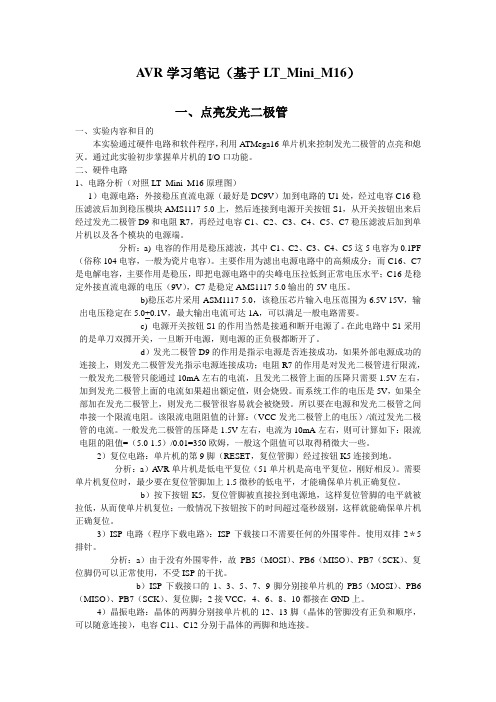

A VR学习笔记(基于LT_Mini_M16)一、点亮发光二极管一、实验内容和目的本实验通过硬件电路和软件程序,利用ATMega16单片机来控制发光二极管的点亮和熄灭。

通过此实验初步掌握单片机的I/O口功能。

二、硬件电路1、电路分析(对照LT_Mini_M16原理图)1)电源电路:外接稳压直流电源(最好是DC9V)加到电路的U1处,经过电容C16稳压滤波后加到稳压模块AMS1117-5.0上,然后连接到电源开关按钮S1,从开关按钮出来后经过发光二极管D9和电阻R7,再经过电容C1、C2、C3、C4、C5、C7稳压滤波后加到单片机以及各个模块的电源端。

分析:a) 电容的作用是稳压滤波,其中C1、C2、C3、C4、C5这5电容为0.1PF (俗称104电容,一般为瓷片电容)。

主要作用为滤出电源电路中的高频成分;而C16、C7是电解电容,主要作用是稳压,即把电源电路中的尖峰电压拉低到正常电压水平;C16是稳定外接直流电源的电压(9V),C7是稳定AMS1117-5.0输出的5V电压。

b)稳压芯片采用ASM1117-5.0,该稳压芯片输入电压范围为6.5V-15V,输出电压稳定在5.0+0.1V,最大输出电流可达1A,可以满足一般电路需要。

c) 电源开关按钮S1的作用当然是接通和断开电源了。

在此电路中S1采用的是单刀双掷开关,一旦断开电源,则电源的正负极都断开了。

d)发光二极管D9的作用是指示电源是否连接成功,如果外部电源成功的连接上,则发光二极管发光指示电源连接成功;电阻R7的作用是对发光二极管进行限流,一般发光二极管只能通过10mA左右的电流,且发光二极管上面的压降只需要1.5V左右,加到发光二极管上面的电流如果超出额定值,则会烧毁。

而系统工作的电压是5V,如果全部加在发光二极管上,则发光二极管很容易就会被烧毁。

所以要在电源和发光二极管之间串接一个限流电阻。

该限流电阻阻值的计算:(VCC-发光二极管上的电压)/流过发光二极管的电流。

Atmega16端口的第二功能

端口A端口B引脚配置如下:•SCK –端口B, Bit 7SCK:SPI 通道的主机时钟输出,从机时钟输入端口。

工作于从机模式时,不论 DDB7 设置如何,这个引脚都将设置为输入。

工作于主机模式时,这个引脚的数据方向由DDB7 控制。

设置为输入后,上拉电阻由PORTB7控制。

•MISO –端口 B, Bit 6MISO:SPI 通道的主机数据输入,从机数据输出端口。

工作于主机模式时,不论DDB6 设置如何,这个引脚都将设置为输入。

工作于从机模式时,这个引脚的数据方向由DDB6 控制。

设置为输入后,上拉电阻由PORTB6控制。

•MOSI –端口 B, Bit 5MOSI: SPI 通道的主机数据输出,从机数据输入端口。

工作于从机模式时,不论DDB5 设置如何,这个引脚都将设置为输入。

当工作于主机模式时,这个引脚的数据方向由 DDB5控制。

设置为输入后,上拉电阻由PORTB5控制。

•SS –端口 B, Bit 4SS: 从机选择输入。

工作于从机模式时,不论DDB4 设置如何,这个引脚都将设置为输入。

当此引脚为低时SPI 被激活。

工作于主机模式时,这个引脚的数据方向由DDB4 控制。

设置为输入后,上拉电阻由PORTB4控制。

• AIN1/OC0 –端口 B, Bit 3AIN1,模拟比较负输入。

配置该引脚为输入时,切断内部上拉电阻,防止数字端口功能与模拟比较器功能相冲突。

OC0,输出比较匹配输出:PB3 引脚可作为T/C0比较匹配的外部输出。

实现该功能时,PB3 引脚必须配置为输出( 设DDB3 为1) 。

在 PWM模式的定时功能中, OC0 引脚作为输出。

• AIN0/INT2 –端口 B, Bit 2AIN0,模拟比较正输入。

配置该引脚为输入时,切断内部上拉电阻,防止数字端口功能与模拟比较器功能相冲突。

INT2,外部中断源 2 : PB2 引脚作为MCU的外部中断源。

• T1 –端口B, Bit 1T1, T/C1 计数器源。

ATmega16寄存器

ATmega16寄存器状态寄存器——SREGI:全局中断触发禁⽌位,为中断总控制开关。

T:通⽤标志位,⽤户⾃定义。

H:半进位标志位。

S:符号标志位。

V:溢出标志位。

N:负数标志位。

Z:零标志位。

C:进/借位标志位。

通⽤中断控制寄存器——GICRINT1:外部中断1使能。

INT0:外部中断0使能。

INT2:外部中断2使能。

IVSEL:中断向量表选择。

当IVSEL=0时,中断向量区的位置定义在FLASH的开始处;当IVSEL=1时,定义在引导程序载⼊区的起始处。

IVCE:中断向量表转移允许位。

必须在IVCE位被写⼊1后的4个时钟周期内,修改IVSEL。

4个时钟周期后,或IVSEL位写⼊后,IVCE位由硬件⾃动清零。

OCIE2:T/C2输出⽐较匹配中断使能位。

TOIE2:T/C2溢出中断使能位。

TICIE1:T/C1输⼊捕获中断使能位。

OCIE1A:T/C1输出⽐较A中断使能位。

OCIE1B:T/C1输出⽐较B匹配中断使能位;TOIE1:T/C1溢出中断使能位。

OCIE0:T/C0输出⽐较中断使能位。

TOIE0:T/C0溢出中断使能位。

TIFR寄存器中的各个中断标志是与TIMSK中的使能位⼀⼀对应。

当SPMIE位被置位,若状态寄存器中的I位也被置位时,SPM完成中断即被使能。

只要SPMCSR寄存器中的SPMEN位被清零(程序存储器操作完成),SPM中断服务将被执⾏(避免轮询占⽤较多机时)。

RWWSB:RWW区忙标志当开始对RWW区进⾏⾃编程(页擦除或页写⼊)操作时,RWWSB位将被硬件置位,RWWSB ⼀旦被置位,对RWW区的读操作将被禁⽌。

在⾃编程操作完成后,向RWWSRE位写⼊1,会将RWWSB位清除。

此外,如果开始⼀个页读取操作,也会将RWWSB位清零。

RWWSRE:读RWW区允许当启动对RWW区⾃我编程(页擦除或页写⼊)操作时,RWWSB位被硬件置1,禁⽌对RWW区的读操作。

在⾃我编程操作完成后(SPMEN=0),同时将RWWSRE位和SPMEN 位置为1,在其后的4个时钟周期内的SPM指令将使RWW区重新开放。

AVR单片机i-o(输入-输出)端口详解

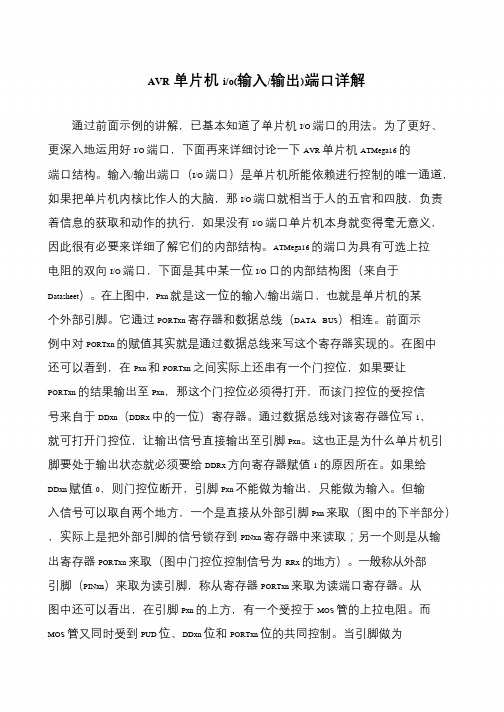

AVR单片机i/o(输入/输出)端口详解通过前面示例的讲解,已基本知道了单片机I/O 端口的用法。

为了更好、更深入地运用好I/O 端口,下面再来详细讨论一下AVR 单片机ATMega16 的端口结构。

输入/输出端口(I/O 端口)是单片机所能依赖进行控制的唯一通道,如果把单片机内核比作人的大脑,那I/O 端口就相当于人的五官和四肢,负责着信息的获取和动作的执行,如果没有I/O 端口单片机本身就变得毫无意义,因此很有必要来详细了解它们的内部结构。

ATMega16 的端口为具有可选上拉电阻的双向I/O 端口,下面是其中某一位I/O 口的内部结构图(来自于Datasheet)。

在上图中,Pxn 就是这一位的输入/输出端口,也就是单片机的某个外部引脚。

它通过PORTxn 寄存器和数据总线(DATA BUS)相连。

前面示例中对PORTxn 的赋值其实就是通过数据总线来写这个寄存器实现的。

在图中还可以看到,在Pxn 和PORTxn 之间实际上还串有一个门控位,如果要让PORTxn 的结果输出至Pxn,那这个门控位必须得打开,而该门控位的受控信号来自于DDxn(DDRx 中的一位)寄存器。

通过数据总线对该寄存器位写1,就可打开门控位,让输出信号直接输出至引脚Pxn。

这也正是为什么单片机引脚要处于输出状态就必须要给DDRx 方向寄存器赋值1 的原因所在。

如果给DDxn 赋值0,则门控位断开,引脚Pxn 不能做为输出,只能做为输入。

但输入信号可以取自两个地方,一个是直接从外部引脚Pxn 来取(图中的下半部分),实际上是把外部引脚的信号锁存到PINxn 寄存器中来读取;另一个则是从输出寄存器PORTxn 来取(图中门控位控制信号为RRx 的地方)。

一般称从外部引脚(PINxn)来取为读引脚,称从寄存器PORTxn 来取为读端口寄存器。

从图中还可以看出,在引脚Pxn 的上方,有一个受控于MOS 管的上拉电阻。

而MOS 管又同时受到PUD 位、DDxn 位和PORTxn 位的共同控制。

AVRatmega16单片机端口地址

AVRatmega16单片机端口地址/* avr/iom16.h - definitions for ATmega16 */#ifndef _AVR_IOM16_H_#define _AVR_IOM16_H_ 1/* This file should only be included from , never directly. */ #ifndef _AVR_IO_H_# error "Include instead of this file."#endif#ifndef _AVR_IOXXX_H_# define _AVR_IOXXX_H_"iom16.h"#else# error "Attempt to include more than one file."#endif/* Registers and associated bit numbers */#define TWBR _SFR_IO8(0x00)#define TWSR _SFR_IO8(0x01)#define TWPS0 0#define TWPS1 1#define TWS3 3#define TWS4 4#define TWS5 5#define TWS6 6#define TWS7 7#define TWAR _SFR_IO8(0x02) #define TWGCE 0#define TWA0 1#define TWA1 2#define TWA2 3#define TWA3 4#define TWA4 5#define TWA5 6#define TWA6 7 #define TWDR _SFR_IO8(0x03) /* Combine ADCL and ADCH */#ifndef __ASSEMBLER__#define ADC _SFR_IO16(0x04) #endif#define ADCW _SFR_IO16(0x04) #define ADCL _SFR_IO8(0x04)#define ADCH _SFR_IO8(0x05) #define ADCSRA _SFR_IO8(0x06) #define ADPS0 0#define ADPS1 1#define ADPS2 2#define ADIE 3#define ADIF 4#define ADATE 5#define ADSC 6#define ADEN 7#define ADMUX _SFR_IO8(0x07) #define MUX0 0#define MUX1 1#define MUX2 2#define MUX3 3#define MUX4 4#define ADLAR 5#define REFS0 6#define REFS1 7#define ACSR _SFR_IO8(0x08)#define ACIS0 0#define ACIS1 1#define ACIC 2#define ACIE 3#define ACI 4#define ACO 5#define ACBG 6#define ACD 7#define UBRRL _SFR_IO8(0x09) #define UCSRB _SFR_IO8(0x0A) #define TXB8 0#define RXB8 1#define UCSZ2 2#define RXEN 4#define UDRIE 5#define TXCIE 6#define RXCIE 7#define UCSRA _SFR_IO8(0x0B) #define MPCM 0#define U2X 1#define PE 2#define DOR 3#define FE 4#define UDRE 5#define TXC 6#define RXC 7#define UDR _SFR_IO8(0x0C) #define SPCR _SFR_IO8(0x0D) #define SPR0 0#define SPR1 1#define CPHA 2#define CPOL 3#define MSTR 4#define DORD 5#define SPE 6#define SPIE 7#define SPSR _SFR_IO8(0x0E) #define SPI2X 0#define SPIF 7#define SPDR _SFR_IO8(0x0F) #define PIND _SFR_IO8(0x10) #define PIND0 0#define PIND1 1#define PIND2 2#define PIND3 3#define PIND4 4#define PIND5 5#define PIND6 6#define PIND7 7#define DDRD _SFR_IO8(0x11) #define DDD1 1#define DDD2 2#define DDD3 3#define DDD4 4#define DDD5 5#define DDD6 6#define DDD7 7#define PORTD _SFR_IO8(0x12) #define PD0 0#define PD1 1#define PD2 2#define PD3 3#define PD4 4#define PD5 5#define PD6 6#define PD7 7#define PINC _SFR_IO8(0x13) #define PINC0 0#define PINC1 1#define PINC2 2#define PINC3 3#define PINC5 5#define PINC6 6#define PINC7 7#define DDRC _SFR_IO8(0x14) #define DDC0 0 #define DDC1 1#define DDC2 2#define DDC3 3#define DDC4 4#define DDC5 5#define DDC6 6#define DDC7 7#define PORTC _SFR_IO8(0x15) #define PC0 0 #define PC1 1#define PC2 2#define PC3 3#define PC4 4#define PC5 5#define PC7 7#define PINB _SFR_IO8(0x16) #define PINB0 0 #define PINB1 1#define PINB2 2#define PINB3 3#define PINB4 4#define PINB5 5#define PINB6 6#define PINB7 7#define DDRB _SFR_IO8(0x17) #define DDB0 0 #define DDB1 1#define DDB2 2#define DDB4 4#define DDB5 5#define DDB6 6#define DDB7 7#define PORTB _SFR_IO8(0x18) #define PB0 0 #define PB1 1#define PB2 2#define PB3 3#define PB4 4#define PB5 5#define PB6 6#define PB7 7#define PINA _SFR_IO8(0x19) #define PINA0 0 #define PINA1 1#define PINA2 2#define PINA3 3#define PINA4 4#define PINA5 5#define PINA6 6#define PINA7 7#define DDRA _SFR_IO8(0x1A) #define DDA0 0 #define DDA1 1 #define DDA3 3#define DDA4 4#define DDA5 5#define DDA6 6#define DDA7 7#define PORTA _SFR_IO8(0x1B) #define PA0 0 #define PA1 1#define PA2 2#define PA4 4#define PA5 5#define PA6 6#define PA7 7/* EEPROM Control Register */#define EECR _SFR_IO8(0x1C) #define EERE 0#define EEWE 1#define EEMWE 2#define EERIE 3/* EEPROM Data Register */#define EEDR _SFR_IO8(0x1D) /* EEPROM Address Register */#define EEAR _SFR_IO16(0x1E) #define EEARL _SFR_IO8(0x1E) #define EEARH _SFR_IO8(0x1F) #define UCSRC _SFR_IO8(0x20) #define UCPOL 0#define UCSZ0 1#define UCSZ1 2#define USBS 3#define UPM0 4#define UPM1 5#define UMSEL 6#define URSEL 7#define UBRRH _SFR_IO8(0x20) #define URSEL 7#define WDTCR _SFR_IO8(0x21)#define WDP0 0#define WDP1 1#define WDP2 2#define WDE 3#define WDTOE 4#define ASSR _SFR_IO8(0x22)#define TCR2UB 0#define OCR2UB 1#define TCN2UB 2#define AS2 3#define OCR2 _SFR_IO8(0x23)#define TCNT2 _SFR_IO8(0x24)#define TCCR2 _SFR_IO8(0x25) #define CS20 0#define CS21 1#define CS22 2#define WGM21 3#define COM20 4#define COM21 5#define WGM20 6#define FOC2 7/* Combine ICR1L and ICR1H */#define ICR1 _SFR_IO16(0x26)#define ICR1L _SFR_IO8(0x26)#define ICR1H _SFR_IO8(0x27)/* Combine OCR1BL and OCR1BH */ #define OCR1B _SFR_IO16(0x28)#define OCR1BL _SFR_IO8(0x28) #define OCR1BH _SFR_IO8(0x29)/* Combine OCR1AL and OCR1AH */ #define OCR1A _SFR_IO16(0x2A) #define OCR1AL _SFR_IO8(0x2A) #define OCR1AH _SFR_IO8(0x2B)/* Combine TCNT1L and TCNT1H */ #define TCNT1 _SFR_IO16(0x2C) #define TCNT1L _SFR_IO8(0x2C) #define TCNT1H _SFR_IO8(0x2D) #define TCCR1B _SFR_IO8(0x2E) #define CS10 0#define CS12 2#define WGM12 3#define WGM13 4#define ICES1 6#define ICNC1 7#define TCCR1A _SFR_IO8(0x2F) #define WGM10 0#define WGM11 1#define FOC1B 2#define FOC1A 3#define COM1B0 4#define COM1B1 5#define COM1A0 6#define COM1A1 7/*The ADHSM bit has been removed from all documentation, as being not needed at all since the comparator has proven to be fast enough even without feeding it more power.*/#define SFIOR _SFR_IO8(0x30)#define PSR10 0#define PSR2 1#define PUD 2#define ACME 3#define ADTS0 5#define ADTS1 6#define ADTS2 7#define OSCCAL _SFR_IO8(0x31) #define OCDR _SFR_IO8(0x31) #define TCNT0 _SFR_IO8(0x32)#define TCCR0 _SFR_IO8(0x33) #define CS00 0#define CS02 2#define WGM01 3#define COM00 4#define COM01 5#define WGM00 6#define FOC0 7#define MCUCSR _SFR_IO8(0x34) #define PORF 0 #define EXTRF 1#define BORF 2#define WDRF 3#define JTRF 4#define ISC2 6#define JTD 7#define MCUCR _SFR_IO8(0x35) #define ISC00 0 #define ISC01 1#define ISC10 2#define ISC11 3#define SM0 4#define SM1 5#define SE 6#define SM2 7#define TWCR _SFR_IO8(0x36) #define TWIE 0#define TWEN 2#define TWWC 3#define TWSTO 4#define TWSTA 5#define TWEA 6#define TWINT 7#define SPMCR _SFR_IO8(0x37) #define SPMEN 0#define PGERS 1#define PGWRT 2#define BLBSET 3#define RWWSRE 4#define RWWSB 6 #define SPMIE 7#define TIFR _SFR_IO8(0x38) #define TOV0 0#define OCF0 1#define TOV1 2#define OCF1B 3#define OCF1A 4#define ICF1 5#define TOV2 6#define OCF2 7#define TIMSK _SFR_IO8(0x39) #define TOIE0 0#define OCIE0 1#define TOIE1 2#define OCIE1B 3#define OCIE1A 4#define TICIE1 5#define TOIE2 6#define OCIE2 7#define GIFR _SFR_IO8(0x3A) #define INTF2 5#define INTF0 6#define INTF1 7#define GICR _SFR_IO8(0x3B) #define IVCE 0#define IVSEL 1#define INT2 5#define INT0 6#define INT1 7#define OCR0 _SFR_IO8(0x3C) /* SP [0x3D..0x3E] *//* SREG [0x3F] *//* Interrupt vectors *//* Vector 0 is the reset vector. *//* External Interrupt Request 0 */ #define INT0_vect_VECTOR(1)#define SIG_INTERRUPT0_VECTOR(1)/* External Interrupt Request 1 */#define INT1_vect_VECTOR(2)#define SIG_INTERRUPT1_VECTOR(2)/* Timer/Counter2 Compare Match */ #define TIMER2_COMP_vect_VECTOR(3)#define SIG_OUTPUT_COMPARE2_VECTOR(3)/* Timer/Counter2 Overflow */#define TIMER2_OVF_vect_VECTOR(4)#define SIG_OVERFLOW2_VECTOR(4)/* Timer/Counter1 Capture Event */ #define TIMER1_CAPT_vect_VECTOR(5)#define SIG_INPUT_CAPTURE1_VECTOR(5)/* Timer/Counter1 Compare Match A */#define TIMER1_COMPA_vect_VECTOR(6)#define SIG_OUTPUT_COMPARE1A_VECTOR(6)/* Timer/Counter1 Compare Match B */#define TIMER1_COMPB_vect_VECTOR(7)#define SIG_OUTPUT_COMPARE1B_VECTOR(7)/* Timer/Counter1 Overflow */#define TIMER1_OVF_vect_VECTOR(8)#define SIG_OVERFLOW1_VECTOR(8) /* Timer/Counter0 Overflow */#define TIMER0_OVF_vect_VECTOR(9)#define SIG_OVERFLOW0_VECTOR(9)/* Serial Transfer Complete */#define SPI_STC_vect_VECTOR(10)#define SIG_SPI_VECTOR(10)/* USART, Rx Complete */#define USART_RXC_vect_VECTOR(11)#define SIG_USART_RECV_VECTOR(11)#define SIG_UART_RECV_VECTOR(11)/* USART Data Register Empty */ #define USART_UDRE_vect _VECTOR(12)#define SIG_USART_DATA_VECTOR(12)#define SIG_UART_DATA_VECTOR(12)/* USART, Tx Complete */#define USART_TXC_vect_VECTOR(13)#define SIG_USART_TRANS_VECTOR(13)#define SIG_UART_TRANS_VECTOR(13)/* ADC Conversion Complete */ #define ADC_vect _VECTOR(14)#define SIG_ADC_VECTOR(14)/* EEPROM Ready */#define EE_RDY_vect_VECTOR(15)#define SIG_EEPROM_READY_VECTOR(15)/* Analog Comparator */#define ANA_COMP_vect_VECTOR(16)#define SIG_COMPARATOR_VECTOR(16)/* 2-wire Serial Interface */#define TWI_vect_VECTOR(17)#define SIG_2WIRE_SERIAL_VECTOR(17)/* External Interrupt Request 2 */#define INT2_vect_VECTOR(18)#define SIG_INTERRUPT2_VECTOR(18)/* Timer/Counter0 Compare Match */ #define TIMER0_COMP_vect_VECTOR(19)#define SIG_OUTPUT_COMPARE0_VECTOR(19)/* Store Program Memory Ready */ #define SPM_RDY_vect _VECTOR(20)#define SIG_SPM_READY_VECTOR(20)#define _VECTORS_SIZE 84/* Constants */#define SPM_PAGESIZE 128#define RAMEND 0x45F #define XRAMENDRAMEND#define E2END 0x1FF#define E2PAGESIZE 4#define FLASHEND 0x3FFF /* Fuses */#define FUSE_MEMORY_SIZE 2/* Low Fuse Byte */#define FUSE_CKSEL0(unsigned char)~_BV(0)#define FUSE_CKSEL1(unsigned char)~_BV(1)#define FUSE_CKSEL2(unsigned char)~_BV(2)#define FUSE_CKSEL3(unsigned char)~_BV(3)#define FUSE_SUT0 (unsigned char)~_BV(4)#define FUSE_SUT1 (unsigned char)~_BV(5)#define FUSE_BODEN(unsigned char)~_BV(6)#define FUSE_BODLEVEL (unsigned char)~_BV(7)#define LFUSE_DEFAULT(FUSE_CKSEL1 & FUSE_CKSEL2 & FUSE_CKSEL3 & FUSE_SUT0) /* High Fuse Byte */#define FUSE_BOOTRST (unsigned char)~_BV(0)#define FUSE_BOOTSZ0(unsigned char)~_BV(1)#define FUSE_BOOTSZ1(unsigned char)~_BV(2)#define FUSE_EESAVE(unsigned char)~_BV(3)#define FUSE_CKOPT(unsigned char)~_BV(4)#define FUSE_SPIEN (unsigned char)~_BV(5)#define FUSE_JTAGEN(unsigned char)~_BV(6)#define FUSE_OCDEN(unsigned char)~_BV(7)#define HFUSE_DEFAULT(FUSE_BOOTSZ0 & FUSE_BOOTSZ1 & FUSE_SPIEN & FUSE_JTAGEN)/* Lock Bits */#define __LOCK_BITS_EXIST #define__BOOT_LOCK_BITS_0_EXIST #define__BOOT_LOCK_BITS_1_EXIST /* Signature */ #define SIGNATURE_0 0x1E#define SIGNATURE_1 0x94#define SIGNATURE_2 0x03#endif /* _AVR_IOM16_H_ */。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第九课A Tmega16(L)的IO端口

本教程节选自周兴华老师《手把手教你学A VR单片机C程序设计》教程,如需转载,请注明出处!读者可通过当当网、淘宝网等网站购买本教程,如需购买配书实验器材,可登陆周兴华单片机培训中心网购部自助购买!

ATmega16(L)单片机有32个通用I/O口,分为PA、PB、PC和PD四组,每组都是8位。

这些I/O 口都可以通过各自的端口寄存器设置成输入和输出(即作为普通端口使用),有些I/O口还具有第二功能(我们在后面使用到这些第二功能时再介绍)。

ATmega16(L)单片机的I/O口在不考虑第二功能时,其基本输入输出功能都是相同的。

如图7-1所示为ATmega16(L)单片机I/O口的结构图。

每个端口对应3个寄存器,即方向寄存器DDRX(X=A、B、C、D)、端口寄存器PORTX(X=A、B、C、D)、输入引脚PINX(X=A、B、C、D),各个端口的工作状况都可以通过对DDRX、PORTX和PINX的操作来完成。

所有的A VR单片机的I/O端口都具有读、写和修改功能。

表7-1列出了A Tmega16(L)的I/O端口的组合控制设置。

ATmega16(L)单片机每一组I/O口的所有管脚都可以单独选择上拉电阻。

引脚缓冲器可以吸收20mA 的电流,能够直接驱动LED显示。

如果设置了弱上拉电阻,当管脚被拉低时,引脚会输出电流。

1.DDRX

DDRX为端口方向寄存器。

当DDRX的某一位置1时相应引脚作为输出使用。

反之,当DDRX的某一位置0时,对应的引脚单片机培训作为输入使用。

例如:

DDRB=0xF0;//此语句将PB端口的PB0~PB3位设为输入,而PB4~PB7位设为输出。

2.PORTX

PORTX为端口数据寄存器。

如果引脚设为输出,则对PORTX进行写操作即改变引脚的输出值。

图7-1A Tmega16(L)的I/O端口

表7-1A Tmega16(L)的I/O端口的组合控制设置

DDRxn(n=0~7)PORTxn(n=0~

7)

I/O 上拉备注

0 0 输入关闭三态(高阻)

0 1 输入打开提供弱上拉,被外部电路拉低时输

出电流

1 0 输出关闭输出0

1 1 输出关闭输出1

例如:

DDRB=0xFF; //此语句将PB端口的PB0~PB7位设为输出。

PORTB=0x55; //PB端口输出01010101。

例如:

DDRB=0x00; //此语句将PB端口的PB0~PB7位设为输入。

PORTB=0xF0; // PB0~PB3位不设上拉,无信号输入时处高阻态。

PB4~PB7位设为上拉,无信号输入时处高电平。

上海周兴华单片机提供单片机培训、FPGA培训、protel培训、PCB设计培训等各种课程,是单片机工程师的要摇篮;

3.PINX

PINX是相应端口的输入引脚地址,如果希望读取引脚的逻辑电平值,一定要读取PINX,而不是PORTX。

注意:PINX是只读的,不能对其赋值。

例如:

DDRB=0x00; //此语句将PB端口的PB0~PB7位设为输入。

PORTB=0xFF; //PB0~PB7位设为上拉,无信号输入时处高电平。

temp=PINB; //将PB口引脚信号读入变量temp中。