海思芯片4G ddr配置方法

海思 3516AV200全功能核心板技术手册说明书

海思3516AV200全功能核心板技术手册一、应用场合:1. 适用于开发以下产品:(1)网络摄像机。

(2)4G/WIFI无线传输产品。

(3)安防监控产品。

(4)网络音视频产品。

(5)编码器。

(6)4K摄像机。

(7)1200万抓拍摄像机。

(8)多路摄像机。

(9)运动相机。

(10)航拍摄像机。

(11)人工智能(AI)产品。

2. 适用于学习linux平台、熟悉ARM开发。

3. 适用于需要熟悉海思音视频编解码、AI算法、多路图像处理、图像拼接、图像展开、4G/WIFI无线传输的开发人员。

二、型号:IPC-4KCODE-MAIN-V4三、产品特色:■核心芯片采用海思高性能多媒体处理器片上系统(SOC),内部集成双核A7(800MHZ)、A17(1.25GHZ)。

■集成了海思第四代ISP,支持WDR、多级降噪、六轴防抖及多种图像增强和矫正算法,为客户提供专业级的图像质量■图像质量优异、功耗低。

■采用标准的H.264/H.265 High Profile压缩算法,方便在窄带上实现高清晰的图像传输。

■最大支持600万编码,最高支持600万/30帧或者1080P/90帧H.264/H.265编码。

■支持多达2路Sensor输入,支持全景相机和无人机等多种产品应用。

■支持双向语音对讲。

■支持ONVIF协议,可对接海康、大华、美电贝尔、雄迈等NVR。

■支持GB28181协议。

■支持手机监看。

■支持WIFI:热点和STA模式。

■支持4G全网通:联通/移动/电信,5模或者7模。

■支持二次开发四、技术参数:五、产品外观及接口定义: 核心板正面:核心板背面:(一)、核心板与底板连接J3座子定义:(二)、核心板与底板连接座子J5定义:(三)、核心板与sensor1接接座子J2定义:(四)、核心板与sensor2连接座子J6定义:。

MTK 4G modem 配置

MTK平台modem 配置先从modem配置表里了解一下每一个文件夹对应哪个频段的配置其他没有标记的,目前我们是用不到的,也不要去修改里面的参数。

打开每一个需要修改的文件夹,可以看到三个子文件夹,类似下图:我们只需要修改上面框选里面的文件夹里面的选项即可。

进入到文件夹里面,发现有好几个文件,我们只需要修改下面标红的两个就可以了,一般都是**_mipi.h和**_rf.h文件各个文件夹里面文件详细说明如下图:了解了上面文件说明后,下面开始讲具体参数配置。

一、mmll_rf USID配置以及修改由于我们目前使用到的SKY的PA和开关,所以他们两个的USID是一样的,出厂默认都是OxF,按照常理来讲,由于PA和开关挂在不同的MIPI通路上,是不会有地址冲突的问题,但是目前MT6735平台存在弱4G信号下,切不回2G通话,也就是有时候打不进来电话,所以需要将这两个设备的USID改成不一样,修改PA和开关都可以,下面示例修改PA 的USID。

首先打开SKY77643的规格书,找到这个位置稍后将会用到里面的Product ID和Manufacturer ID然后在mmll_rf文件夹里面打开这两个文件夹在mml1_custom_mipi.c文件里面找到这个位置,按照上面的描述修改相应的值后面的new USID可以修改为0x1~0xE之间的一个,在mml1_custom_mipi.h文件里面对应修改就可以了,由于我们修改的是PA,所以在port sel 下面需要选取MIPI_PORT0,如果是开关的话,就需要对应修改为MIPI_PORT1。

至于在这里选取修改的USID是PA0还是PA1,ASM0还是ASM1,可以从后面的文件里面看出来。

比如在4G里面的lte_custom_mipi.c文件里面,可以看到在TPC这里会有一个USID的调用。

这里可以看到,在同一个文件里面对同一个PA可能会有两个USID的调用,主要因为这个modem沿用了phase-1设计的模板,很多东西没有和phase-2设计选用的PA对应上来,我们目前的设计中,FDD和TDD已经做到一个PA里面去了,所以USID应该是要一致的,所以我们后来把所有用到PA1的地方全部改为了PA0。

海思Dongle操作简化版指导书

海思Dongle操作简化版指导书拟制日期2011-1-12 审核日期批准日期华为技术有限公司版权所有侵权必究(DVP05T04 V2.8 / 仅供内部使用)修订记录目录1前言 (5)2P C端驱动安装 (5)3H iStudio连接Dongle设置 (8)3.1双击HiStudio,打开HiStudio工具 (8)3.2连接类型选择COM,选择默认的COM端口 (8)3.3点击OK后成功连接到Dongle (9)4H iStudio框架介绍 (9)4.1主框架界面 (9)4.2常用插件介绍 (10)4.2.1Stat. GUI Viewer (10)4.2.2LTE AirLayer及保存 (14)4.2.3NV Browser (16)5M obile Partner使用介绍 (17)5.1Mobile Partner安装升级 (17)5.2Mobile Partner 简介 (17)5.2.1功能简介 (17)5.2.2界面简介 (17)5.3操作指导 (22)5.3.1操作步骤 (22)5.4注意事项 (25)6D ongle入网配置 (26)6.1配置NV项 (26)6.1.1打开NV项配置窗口 (26)6.1.2配置USIM环境 (28)6.1.3修改IMSI (软USIM下才需要配置) (29)6.1.4设置UE搜索频段 (30)6.1.5设置UE能力 ................................................................................... 错误!未定义书签。

6.1.6设置安全功能开关 (30)6.1.7设置Key值与op值(软USIM下才需要配置) ................................ 错误!未定义书签。

6.1.8设置候选频点(该项不是入网必须配置) (31)6.2入网测试 (34)7F AQ (35)7.1查询当前Dongle版本号 (35)7.2USB Stick上PING包不通定位方法 ...................................................... 错误!未定义书签。

MEMORY存储芯片MT29F4G01AAADDHC-ITX D中文规格书

(I DD5R), I PP6x for self refresh cases (I DD6N, I DD6E, I DD6R, I DD6A), I PP7 for the operating bank interleave read case (I DD7) and I PP9 for the MBIST-PPR operation case. These have the same definitions as the I DD currents referenced but are measured on the V PP supply.•I DDQ currents are measured as time-averaged currents with V DDQ balls of the device under test grouped together. Micron does not specify I DDQ currents.•I PP and I DDQ currents are not included in I DD currents, I DD and I DDQ currents are not included in I PP currents, and I DD and I PP currents are not included in I DDQ currents. Note: I DDQ values cannot be directly used to calculate the I/O power of the device. They can be used to support correlation of simulated I/O power to actual I/O power. In DRAM module application, I DDQ cannot be measured separately because V DD and V DDQ are using a merged-power layer in the module PCB.The following definitions apply for I DD, I PP and I DDQ measurements.•“0” and “LOW” are defined as V INืV IL(AC)max•“1” and “HIGH” are defined as V INุV IH(AC)min•“Midlevel” is defined as inputs V REF = V DD/2•Timings used for I DD, I PP and I DDQ measurement-loop patterns are provided in the Current Test Definition and Patterns section.•Basic I DD, I PP, and I DDQ measurement conditions are described in the Current Test Definition and Patterns section.•Detailed I DD, I PP, and I DDQ measurement-loop patterns are described in the Current Test Definition and Patterns section.•Current measurements are done after properly initializing the device. This includes, but is not limited to, setting:R ON = R ZQ/7 (34 ohm in MR1);Qoff = 0B (output buffer enabled in MR1);R TT(NOM) = R ZQ/6 (40 ohm in MR1);R TT(WR) = R ZQ/2 (120 ohm in MR2);R TT(Park) = disabled;TDQS feature disabled in MR1; CRC disabled in MR2; CA parity feature disabled in MR3; Gear-down mode disabled in MR3; Read/Write DBI disabled in MR5; DM disa-bled in MR5•Define D = {CS_n, RAS_n, CAS_n, WE_n}: = {HIGH, LOW, LOW, LOW}; apply BG/BA changes when directed.•Define D_n = {CS_n, RAS_n, CAS_n, WE_n}: = {HIGH, HIGH, HIGH, HIGH}; apply in-vert of BG/BA changes when directed above.Note: The measurement-loop patterns must be executed at least once before actual cur-rent measurements can be taken, with the exception of IDD9 which may be measured any time after MBIST-PPR entry.Figure 246: Measurement Setup and Test Load for I DDx , I PPx , and I DDQxFigure 247: Correlation: Simulated Channel I/O Power to Actual Channel I/O PowerApplication-specific memory channel environmentI DD Q test loadC hanne l I /O power numberNote: 1.Supported by I DDQ measurement.I DD DefinitionsTable 137: Basic I DD , I PP , and I DDQ Measurement ConditionsTable 137: Basic I DD, I PP, and I DDQ Measurement Conditions (Continued)8Gb: x4, x8, x16 DDR4 SDRAM Current Specifications – Measurement Conditions8Gb: x4, x8, x16 DDR4 SDRAM Current Specifications – Measurement Conditions。

海思商用终端操作指导V1.0

海思商用终端操作指导拟制海思团队日期2011-1-12 审核日期批准日期华为技术有限公司版权所有侵权必究(DVP05T04 V2.8 / 仅供内部使用)修订记录目录1前言 (4)2P C端驱动安装 (4)3简化版HSO使用说明 (10)3.1入网配置 (15)3.1.1配置Quick configure (15)4M obile Partner使用介绍 (19)4.1Mobile Partner安装升级 (19)4.2Mobile Partner 简介 (20)4.2.1功能简介 (20)4.2.2界面简介 (20)4.3操作指导 (25)4.3.1操作步骤 (25)4.4Mobile Partner日志使用 (27)4.5注意事项 (28)1前言1.1 HSO版本更新记录B180:更新快速配置功能,对支持的Band中上下选择不一致的问题进行改进1.2 HSO安装标识海思Dongle的操作主要通过HiStudio工具完成。

如果没有HiStudio工具,可通过Mobile Partner连接入网。

本操作指导书主要介绍了HSO的使用界面、常规配置,并对Mobile Partner等操作进行说明,后续会陆续更新FAQ等信息。

2PC端驱动安装注意:有两种方案,一种是使用海思之前提供的单独的驱动软件,例如:Windows-5.06.08.00;另一种是使用数据卡缓存中携带的Mobile Connect安装包,其中包括驱动和Mobile Partner两个软件。

安装Mobile Partner即可。

在使用终端之前,最好先安装WinXP补丁(如果不确认系统是否已经安装的情况下)。

2.1 单独驱动安装2.1.1 驱动获取可以向海思Dongle指定的接口人获取。

驱动目录结构如下:2.1.2 驱动安装断开Dongle与PC的连接,点击DriverSetup.exe ,等待一会安装完成。

注意此时没有任何提示。

如果先前已经安装过老版本的驱动,需要先执行DriverUninstall.exe完成后,等待一分钟左右;再执行DriverSetup.exe,再等待一分钟左右。

2、4G华为参数设置

邻高于ThreshXlow异频频点低优先级重选门 限(2分贝)/邻高于ThreshXhigh异频频点高优 先级重选门限(2分贝) )

RXBRANCH (接收通道)

VSWR(驻波)

UEONLINEINFO(用户信息dsp)

UETIMERCONST(UE定时器信息)

1、打开异频切换开关(ENODEBALGOSWITCH) 2、打开MLB算法开关(CELLALGOSWITCH) 3、设置MLB参数 4、设置MLB触发的A4门限 5、异频频点设置是否允许进行负载切换

SCTPLNK(SCTP链路) SCTPHOST(核心网,时延跟踪) ENODEBUNCTION查询基站标识

LTE

MIMOADAPTIVEPARACFG(传输模式) IPRT (路由配置) ENODBEALGOSWTCH(基站级算法开关)

CELLPHYTOPO(物理结构) CELLSIMULOAD(模拟负载加扰) CELLRESEL(小区重选信息)

OCN:CellIndividualOffset 小区偏移量: OCS:CellSpecificOffset 服务小区偏置 (lst cell) Ofn:邻小区频率偏移量:OfS:服务小区频率 偏置(无效) Mn+Ofn+Ocn-Hys>Thresh邻小区大于 Ofn:QoffsetFreq 频率偏置,Ocn: CellIndividualOffset 小区偏移量,Hys: InterFreqHoA4Hyst 异频切换幅度迟滞 A1/A2 A1/A2

Mn + Ofn - Hys > Thresh INTERRATHOUTRANGROUP

异系统

LICENSE(许可) CNOPERATORTA(查询跟踪区域码) CFGFILE(基站配置文件) CELLRACTHD(准入算法门限参数)

Hi3516A Hi3516D 硬件设计用户指南

版本 03 02 01

00B04 00B03 00B02

00B01

修订说明

修改 1.1.3、1.2.1 和 1.4 小节 修改 1.2.5 小节 第一次正式版本发布,修改图 1-14 和图 1-15,添加图 118 和图 1-19,2.1.3 小节有新增内容。添加 Hi3516D 的相 关内容。

修改图 1-2 及图 1-17 1.3.3.2 章节,VI 接口中有修改。 第二次临时版本发布 新增第 3 章 ESD 设计建议,其他章节都涉及修改。 初始版本

产品版本 V100 V100

读者对象

本文档(本指南)主要适用于以下工程师: z 技术支持工程师 z 单板硬件开发工程师

修订记录

修订记录累积了每次文档更新的说明。最新版本的文档包含以前所有文档版本的更新 内容。

修订日期 2016-03-28 2015-11-02

版本 05 04

修订说明 1.2.5、1.3.5、1.3.8 小节涉及修改 修改 2.1.3 小节的相关内容

文档版本 05 (2016-03-28)

海思专有和保密信息 版权所有 © 深圳市海思半导体有限公司

i

Hi3516A/Hi3516D 硬件设计 用户指南

前言

修订日期 2015-06-15 2015-02-10 2014-12-20

2014-10-20 2014-09-25 2014-09-14

2014-07-15

Hi3516A/Hi3516D 硬件设计

用户指南

文档版本 发布日期

05 2016-03-28

版权所有 © 深圳市海思半导体有限公司 2014-2016。保留一切权利。

非经本公司书面许可,任何单位和个人不得擅自摘抄、复制本文档内容的部分或全部,并不得以任何 形式传播。

TI 海思 安霸...摄像机芯片简要介绍

TI 海思安霸...摄像机芯片简要介绍很多年以前业界就谈到安防视频监控领域的三个趋势:数字化、网络化、智能化。

目前国内市场上安防视频监控系统的主流产品已经从十多年前的纯模拟视频监控系统,逐步转变成了纯数字的百万高清视频监控系统,即从视频采集、视频传输、视频录像和回放全部采用模拟信号转变为全部是数字信号。

相比于模拟视频监控设备,百万高清数字摄像机大大提升了画质,像素达到1280×720、1920×1080或更高,因此有了“百万高清”之名。

同时,对比模拟监控设备传输技术而言,数字视频监控设备仅需普通网线,易于实现远距离传输,更重要是降低了工程造价且易于维护。

随着纯数字高清监控系统配套设备越来越齐全,解决方案越来越完善,它已经成为安防视频监控领域不可逆转的潮流,并占据市场主导地位。

摄像机芯片的功能从数字摄像机的组成结构来看,它主要由镜头、图像传感器(CCD或者CMOS器件)、ARM/DSP等组成。

镜头聚集被摄物体反射的光线至图像传感器上,再由图像传感器经过广电转换成数字视频信号输出给芯片,芯片进行一系列数字图像信号处理(ISP)和数据压缩之后,通过网络传输给后端解码显示设备,进而实现视频预览、录像、回放等功能。

从上面我们可以看出,摄像机芯片是整个摄像机里面核心部件,它接收来自图像传感器获取的图像,然后进行一系列的运算和处理,实现了数字网络摄像机的所有功能。

数字摄像机芯片,习惯上又称之为片上系统(SoC,System-on-Chip),它将处理器资源、内存资源、编解码算法、外围设备接口等都集成在单个平台上,其中大部分功能固化在芯片上,并且对一些特殊功能需求模块化,采用提供源代码方式给用户,用户再根据不同的应用需求进行二次开发;除此之外,SoC还可以增加视频协处理器以及其他视频子系统,实现如预览、缩放、光学处理、图文叠加等功能,从而进一步增强视频处理能力。

当前百万高清摄像机芯片厂家及产品SoC方案作为高清数字摄像机芯片解决方案,能够有效满足百万高清摄像机内部复杂视频处理运算以及外围设备接口扩展。

海思HI3520DV400改网络RMII模式uboot开发

海思HI3520DV400改网络RMII模式uboot开发本文由俊_竹_科_技原创,欢迎转载,请注明出处。

海思HI3520DV400的uboot默认的RGMII模块。

俊竹科技在做板时,把网络芯片换成RMII 的100M网络芯片。

当然如果你的板子换成MII的芯片,修改的方法一样,只是两个地方值不一样而已。

主要修改以下两个地方:1、修改uboot配置头文件。

打开uboot的源码目录,找到海思HI3520DV400的头文件,路径参考:Z:\home\hi3520DV400\Hi3521DV100_SDK_V2.0.4.0\osdrv\opensource\uboot\u-boot-2010.06\i nclude\configs打开目录下的hi3520dv400.h文件,位置大概貌在文件的190行。

修改#define CONFIG_HIGMAC_PHY1_ADDR1#define CONFIG_HIGMAC_PHY1_INTERFACE_MODE1/*2*/CONFIG_HIGMAC_PHY1_INTERFACE_MODE原来的值为2,这里修改为1。

原因是这里是0,MII,1,RMII,2RGMII,根据你的网络芯片修改。

附图。

CONFIG_HIGMAC_PHY1_ADDR的值根据你的硬件情况,看看是否需要修改。

我们的板子是RMII,这里不用修改。

2、修改exsl文件。

打开Hi3520DV400_PINOUT_CN.xlsx文件,参考路径是:hi3520dV400\Hi3521D V100R001C02SPC040\ReleaseDoc\zh\00.hardware\chip\Hi3520DV400看这个表格的内容,uboot默认的RGMII的值为1,我们需要改为3。

我们打开配置表格Hi3520dv400-DMEB2LC-uboot-DDR3_1866M_16bit_512M-A7_1000M-BUS_300M.xlsm参考路径:Z:\home\hi3520DV400\Hi3521DV100_SDK_V2.0.4.0\osdrv\tools\pc\uboot_tools原值为0x1,我们这里修改为0x3。

海思芯片常用命令-概述说明以及解释

海思芯片常用命令-概述说明以及解释1.引言1.1 概述海思芯片(Hisilicon)作为一家知名的芯片设计公司,致力于提供高性能、低功耗的芯片解决方案。

海思芯片在各类智能设备中得到广泛应用,如监控摄像头、智能家居、视频会议等领域。

在使用海思芯片时,了解常用命令是至关重要的。

这些命令可以帮助开发者更好地调试和优化软件,提高软件性能,进而提升设备的用户体验和竞争力。

本文将介绍海思芯片常用的命令,包括其功能、用法和示例演示,帮助读者更好地了解和应用海思芯片,为其开发工作提供一定的参考和指导。

"1.2 文章结构":本文将分为三个主要部分进行阐述。

首先,我们将介绍海思芯片的简介,包括其发展历程、技术特点和应用领域。

接着,我们将详细介绍海思芯片常用命令的相关知识,包括命令的分类、常用命令的功能和使用方法。

最后,我们将通过命令实例的演示,更直观地展示常用命令的实际应用情景,帮助读者更好地理解和掌握这些命令。

通过这三个部分的阐述,读者将能够全面了解海思芯片常用命令的重要性和应用价值,为其在实际项目中的应用提供帮助和指导。

1.3 目的海思芯片作为一种主流的芯片型号,广泛应用于各种智能设备中。

本文旨在介绍海思芯片常用命令,帮助读者更好地了解和掌握海思芯片的操作方法,提高其在实际应用中的效率和准确性。

通过本文的学习,读者可以快速上手海思芯片的操作,并灵活运用各种命令来满足不同的需求,从而更好地发挥海思芯片的性能和功能。

同时,本文还将展示一些实际的命令实例,帮助读者更直观地理解命令的使用方法和效果,为其在实际工作中提供参考和指导。

希望本文能够为读者提供一份实用的参考资料,使他们更加熟练地操作海思芯片,为智能设备的开发和应用提供有力支持。

2.正文2.1 海思芯片简介海思芯片,全称海思半导体(HiSilicon)是华为公司旗下的全球领先的芯片设计公司,专注于为华为手机、智能家居、物联网等产品提供先进的芯片解决方案。

海思机顶盒芯片方案路标(2012-11-27 )

Entry

Hi3110Q

• 252MHz • SDR/DDR • 1xQAM

Hi3110EV400

• 400MHz • Float CPU • DDR / DDR2 • 3xDEMUX • 1xQAM • M/JPEG Decoding • Chip ID

~2011

HISILICON Confidential

图片硬件解码器 JPEG 6400像素,PNG 6400像素

JPEG 6400像素,PNG 6400像素

TS流

3xTS IN+1xTS OUT

1xTS IN+1xRF IN+1xTS OUT

PVR

支持全业务PVR

支持全业务PVR

网口

1xMAC with PHY

1xMAC

USB

2xUSB 2.0 HOST with PHY

支持

不支持

操作系统

Linux

Linux/RTOS

封装

BGA382

HUAWEI TECHNOLOGIES CO., LTD.

QFP176

Huawei Confidential

Page 5

SD Chipsets Roadmap

SD

IPTV

DVB/IP Hybrid

Middle

Hi3560

• 270MHz • MPEG2/4/H264 • 1xEthernet • 1xUSB2.0 • JPEG Decoding • NAND Flash • CF Card

Hi3715

• 600MHz • MPEG2/H264/AVS

VC1/REAL/VP6/VP8 • 2x1080P30 / MVC • 1xEthernet with PHY • 2xUSB2.0 with PHY • PVR • DVB-CI/CI+ • HW Security • BGA

海思芯片手册

海思芯片手册一、介绍海思芯片是华为公司旗下的一款AI芯片,性能强大、功耗低,被广泛应用于智能手机、物联网设备以及其他人工智能领域。

本手册将详细介绍海思芯片的各种技术规格和使用方法。

二、技术规格2.1 芯片架构海思芯片采用了先进的FinFET工艺,具有多核心架构,包括CPU、GPU和NPU。

这种架构可以实现不同的计算任务在不同的核心间分配,提高整体性能。

2.2 缓存和存储海思芯片拥有大容量的高速缓存和内存,提供快速的数据读写速度。

同时,还支持外部存储设备的扩展,满足各种应用需求。

2.3 AI加速海思芯片的独特之处在于内置了AI加速引擎,可以高效地进行机器学习和深度学习任务。

这一特性使得海思芯片在人工智能领域具有明显的优势。

三、使用方法3.1 芯片选型在选择海思芯片时,需要根据具体的应用需求和预算来确定合适的型号。

不同的型号配置和性能略有差异,用户可以根据自己的需求进行选择。

3.2 软件开发海思芯片支持多种软件开发环境和编程语言,如C、C++和Python等。

用户可以根据自己的熟悉程度和项目需求来选择适合的开发方式。

3.3 系统集成在进行系统集成时,需要注意与其他硬件设备的兼容性和接口的对接。

海思芯片提供了详细的技术文档和接口说明,开发者可以根据文档进行相应的配置和接线。

3.4 芯片调试在进行芯片调试时,可以利用海思芯片的调试工具和开发板。

通过调试器连接开发板和计算机,可以实时查看芯片的运行状态和调试信息,加快开发进度。

四、常见问题解答4.1 如何选择适合的海思芯片?在选择芯片时,应根据应用需求和预算来确定型号和配置。

建议用户根据实际情况进行评估,选择性能与价格都能够满足需求的芯片。

4.2 如何进行软件开发?海思芯片支持多种编程语言和开发环境,用户可以根据自己的熟悉程度选择合适的方式。

一般来说,使用C或C++进行开发可以更好地发挥芯片的性能优势。

4.3 如何进行系统集成?在进行系统集成时,需要了解海思芯片的接口定义和系统要求。

jlink配置-S3C2440

jlink配置-S3C2440J-Flash ARM的配置。

一般说来file-->open project里面会找到一些*.jflash的配置文件,加载他们就行了,但是没找到适合S3C2440的。

所以自己建了一个MINI2440.jflash,手动进行配置:j-link设置1. 打开J-Flash ARM,并进入菜单:Options-->Project settings2.主要设置CPU选项和Flash选项CPU :Core --> ARM9, Little endianUse target RAM(faster)-->Addr:40000000 4KB(不选很慢;从Nor flash启动时内部Boot SRAM的地址和大小,参考S3C2440A的芯片手册)初始化序列(Init sequence)按下面的填,简单做了下注释。

##-------Action-----Value0------Value1HaltDisable MMUWrite 32bit 0x53000000 0x00000000 ; pWTCON , 看门狗定时器控制寄存器Write 32bit 0x4A000008 0xFFFFFFFF ; INTMSK , 中断屏蔽寄存器Write 32bit 0x4A00001C 0x000007FF ; INTSUBMSK , 针对INTMAK具体化的一个中断请求屏蔽寄存Write 32bit 0x56000050 0x000055AA ; rGPFCON , Port F controlWrite 32bit 0x4C000014 0x00000007 ; CLKDIVN , CPU时钟分频控制寄存器Write 32bit 0x4C000000 0x00FFFFFF ; LOCKTIME , 锁时计数寄存器Write 32bit 0x4C000004 0x00061012 ; MPLLCON , MPLL寄存器Write 32bit 0x4C000008 0x00040042 ; UPLLCON , UPLL寄存器Write 32bit 0x48000000 0x22111120 ; Bus width & wait statusWrite 32bit 0x48000004 0x00002F50 ; Boot ROM controlWrite 32bit 0x48000008 0x00000700 ; BANK1 controlWrite 32bit 0x4800000C 0x00000700 ; BANK2 controlWrite 32bit 0x48000010 0x00000700 ; BANK3 controlWrite 32bit 0x48000014 0x00000700 ; BANK4 controlWrite 32bit 0x48000018 0x0007FFFC ; BANK5 controlWrite 32bit 0x4800001C 0x00018005 ; BANK6 controlWrite 32bit 0x48000020 0x00018005 ; BANK7 controlWrite 32bit 0x48000024 0x008E0459 ; DRAM/SDRAM refresh Write 32bit 0x48000028 0x00000032 ; Flexible Bank SizeWrite 32bit 0x4800002C 0x00000030 ; Mode register set for SDRAMWrite 32bit 0x48000030 0x00000030 ; Mode register set for SDRAM3. Flash取消"Automatically detect flash memory",然后"Select Flash Device"。

海思ddr计算表格

海思ddr计算表格摘要:1.概述海思DDR计算表格的重要性2.海思DDR计算表格的组成与作用3.如何使用海思DDR计算表格进行内存计算4.海思DDR计算表格在实际应用中的优势与局限性5.总结:海思DDR计算表格在内存计算领域的价值正文:随着科技的飞速发展,芯片设计和制造技术也在不断进步。

作为我国华为公司旗下的一款芯片,海思DDR计算表格在内存计算领域具有显著的优势。

本文将从以下几个方面介绍海思DDR计算表格的相关知识,帮助大家更好地理解和应用这一工具。

首先,我们要了解海思DDR计算表格的重要性。

在海思芯片的设计过程中,DDR(双倍数据率)计算表格发挥着至关重要的作用。

通过这个表格,工程师可以快速、准确地计算出内存带宽、延迟等关键参数,为芯片的优化提供有力支持。

接下来,我们来看看海思DDR计算表格的组成与作用。

这个表格主要包括以下几个部分:1.DDR速率:包括DDR3、DDR4等不同速率的标准。

2.通道数:表示内存颗粒的通道数量,一般为1或2通道。

3.内存容量:以GB为单位,表示内存颗粒的容量。

4.内存频率:以MHz为单位,表示内存的工作频率。

5.带宽:表示内存颗粒的带宽,计算公式为:通道数× 内存频率× 8(字节/秒)。

6.延迟:表示内存响应时间,以纳秒(ns)为单位。

了解了海思DDR计算表格的组成后,我们来看一下如何使用这个表格进行内存计算。

以一个DDR4内存模块为例,其参数如下:DDR4 2400MHz 4GB 16-18-18-38 1.2V根据这些参数,我们可以使用以下公式计算内存带宽和延迟:1.带宽计算:2 × 2400 × 16 × 8 = 51200 MB/s2.延迟计算:18 × 4 + 18 × 2 + 12 × 2 = 120 ns通过海思DDR计算表格,我们可以方便地得到内存模块的带宽和延迟,为芯片的性能评估和优化提供依据。

海思HI3531 4路高清SDI 1080P开发板使用手册

海思HI3531 4路高清SDI 1080P开发板使用手册海思HI3531 4路高清SDI 1080P开发板使用手册��、简介1) 开发板图片2) 资源情况主芯片为海思Hi3531带4片2Gbit DDR,一共1Gbyte带2个千兆网口,PHY为RTL8211EG带音频输入输出,均支持双声道立体声,AD/DA芯片为TLV320AIC31IRHBR 带4个TTL UART串口(其中包括一个调试串口)带2个SATA口,均带PM功能,可以接扩展模块,扩展为更多SATA口带1个时钟芯片DS1339带1个HDMI输出,可支持1080P@60fps 带1个VGA输出,可支持2560x1600@60fps 带2个USB输出,可以接USBHUB扩展更多USB口带4路SDI输入接口,可以支持4路1080P视频,AD芯片为GV7601 带2路CVBS输出带JTAG/PCIE/IR/GPIO/蜂鸣器等其他接口一、接线和启动拿到开发板之后,首先接好串口线(注意,不管什么接口,请在断电情况下插拔)如上图所示,J11为缺省的调试串口,带有箭头标记的为第一管脚接好串口线后打开串口调试工具超级终端或者其他调试工具都可以,下面的例子以putty为例,波特率设为115200,打开串口,然后上电 12V(内正外负)可以看到嵌入式操作系统开始启动启动完成输入ifconfig可以看到板子的IP情况如果接好网线,可以telnet到板卡,进行相关操作。

如果遇到串口不能输入的情况,请关掉软件,重新打开这个串口,或者重新插拔一下串口线二、启动示例程序板卡启动之后就是一个嵌入式linux系统,可以输入各种linux命令板子里面/nand/目录下带有各种例子,可以运行查看1)解码H264文件通过HDMI输出的例子请先接好HDMI显示器,然后运行 cd/nand./sample_vdec 0然后选0,选择frame mode就可以看到海思自带的一个例子,这个例子解码同级目录下的stream_chn0.h264,然后输出到HDMI显示器2) 解码H264文件通过VGA输出的例子请先接好VGA显示器,然后运行 cd /nand./sample_vdec 33) 视频输入直接输出到视频输出的例子请先接好VGA或者HDMI显示器 cd /nand. /sample_vio 2然后输入1 选择多画面分割模式可以看到 SDI的输入源显示在显示器上4) 其他例子请自行摸索测试三、SDK的安装与编译请通读SDK包中的 \\01.software\\board\\documents_cn 目录下的相关文档请注意,本板卡,已经烧写了uboot和内核文件系统,并且启动已经加载了海思相关驱动如果不小心擦除了uboot,可以通过海思自带的FastBoot3.1_BVT.exe烧写恢复,具体可以参看海思相关文档如果要执行SDK中的load3531脚本,请修改为4hd模式,并且去掉sil9024.ko驱动的加载详细情况,可以参考SDK中的文档,大概步骤如下1) 安装虚拟机软件推荐VirtualBox2) 在虚拟机上安装Linux系统,可以选择Ubuntu 等 3) 在Linux上安装GCC等编译器和开发相关工具4) 在Linux上解压缩Hi3531_SDK_VX.X.X.X.tgz 的压缩包 5) 在Linux上安装跨平台编译器arm-hisiv200-linux-gcc6) 编写Hello Word程序,然后通过arm-hisiv200-linux-gcc 编译,然后把编译后的程序放到Hi3531板卡上运行(配置好NFS可以加快开发进度) 7) 编译sdk中的sample,放到Hi3531板卡上运行四、系统资源简介SDI输入一共有4路 J7 ~ J10 分别接GV7601芯片J7 对应U1 对应VIU0/SIO0 J8 对应U2 对应VIU1/SIO1 J9 对应U3 对应VIU2/SIO2 J10 对应U4 对应VIU3/SIO3感谢您的阅读,祝您生活愉快。

海思Hi3559AV100内存分配——MMZ

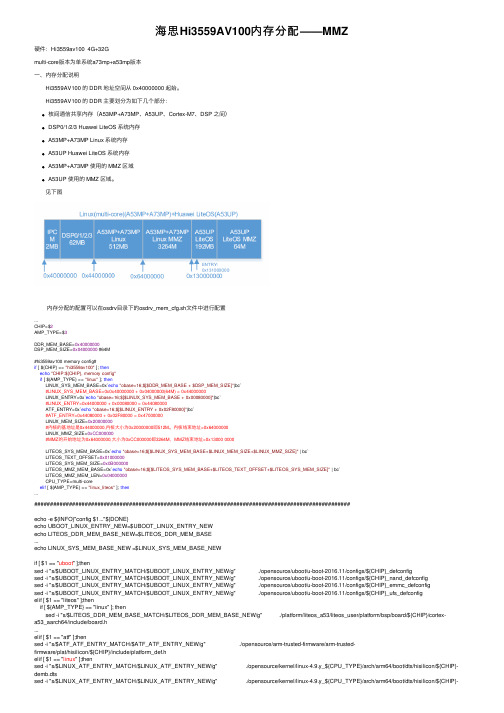

海思Hi3559AV100内存分配——MMZ硬件:Hi3559av100 4G+32Gmulti-core版本为单系统a73mp+a53mp版本⼀、内存分配说明 Hi3559AV100 的 DDR 地址空间从 0x40000000 起始。

Hi3559AV100 的 DDR 主要划分为如下⼏个部分:核间通信共享内存(A53MP+A73MP、A53UP、Cortex-M7、DSP 之间)DSP0/1/2/3 Huawei LiteOS 系统内存A53MP+A73MP Linux 系统内存A53UP Huawei LiteOS 系统内存A53MP+A73MP 使⽤的 MMZ 区域A53UP 使⽤的 MMZ 区域。

见下图 内存分配的配置可以在osdrv⽬录下的osdrv_mem_cfg.sh⽂件中进⾏配置...CHIP=$2AMP_TYPE=$3DDR_MEM_BASE=0x40000000DSP_MEM_SIZE=0x04000000 #64M#hi3559av100 memory config#if [ ${CHIP} == "hi3559av100" ]; thenecho"CHIP:${CHIP}, memory config"if [ ${AMP_TYPE} == "linux" ]; thenLINUX_SYS_MEM_BASE=0x`echo"obase=16;$[$DDR_MEM_BASE + $DSP_MEM_SIZE]"|bc`#LINUX_SYS_MEM_BASE=0x0x40000000 + 0x04000000(64M) = 0x44000000LINUX_ENTRY=0x`echo"obase=16;$[$LINUX_SYS_MEM_BASE + 0x00080000]"|bc`#LINUX_ENTRY=0x44000000 + 0x00080000 = 0x44080000ATF_ENTRY=0x`echo"obase=16;$[$LINUX_ENTRY + 0x02F80000]"|bc`#ATF_ENTRY=0x44080000 + 0x02F80000 = 0x47000000LINUX_MEM_SIZE=0x20000000#内核的基地址是0x44000000,内核⼤⼩为0x20000000即512M。

海思vo用户时序配置

1、配置时序在sample中只需要设置为User时序即可,如下图:用户时序的结构体:typedef struct tagVO_SYNC_INFO_S{HI_BOOL bSynm; /* sync mode(0:timing,as BT.656; 1:signal,as LCD) */ HI_BOOL bIop; /* interlaced or progressive display(0:i; 1:p) */HI_U8 u8Intfb; /* interlace bit width while output */HI_U16 u16Vact ; /* vertical active area */HI_U16 u16Vbb; /* vertical back blank porch */HI_U16 u16Vfb; /* vertical front blank porch */HI_U16 u16Hact; /* herizontal active area */HI_U16 u16Hbb; /* herizontal back blank porch */HI_U16 u16Hfb; /* herizontal front blank porch */HI_U16 u16Hmid; /* bottom herizontal active area */HI_U16 u16Bvact; /* bottom vertical active area */HI_U16 u16Bvbb; /* bottom vertical back blank porch */HI_U16 u16Bvfb; /* bottom vertical front blank porch */HI_U16 u16Hpw; /* horizontal pulse width */HI_U16 u16Vpw; /* vertical pulse width */HI_BOOL bIdv; /* inverse data valid of output */HI_BOOL bIhs; /* inverse horizontal synch signal */HI_BOOL bIvs; /* inverse vertical synch signal */} VO_SYNC_INFO_S;如SDK中默认的PAL时序:{0,0,0, 288,22,2 ,720,132,12, 1, 288,23,2, 126,3, 0,0,0}上面部分属性,与显示通道的总体控制寄存器DHDCTRL(0x205ca000)是对应的。

Histudio使用手册

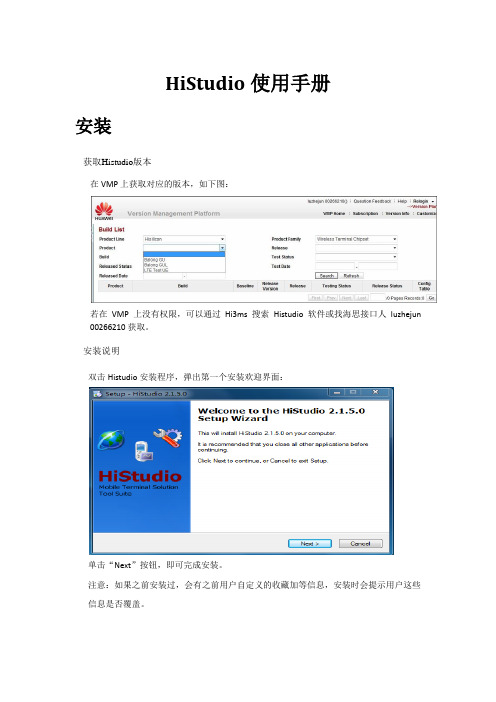

HiStudio使用手册安装获取Histudio版本在VMP上获取对应的版本,如下图:若在VMP上没有权限,可以通过Hi3ms搜索Histudio软件或找海思接口人luzhejun 00266210获取。

安装说明双击Histudio安装程序,弹出第一个安装欢迎界面:单击“Next”按钮,即可完成安装。

注意:如果之前安装过,会有之前用户自定义的收藏加等信息,安装时会提示用户这些信息是否覆盖。

启动主架构界面Histudio第一次启动界面如下:如果HiStudio所在的计算机中存在多块网卡或一块网卡绑定多个IP地址时,那么用户必须要通过Connection -> Settings菜单来设置与UE进行通信的IP地址。

打开设置窗口后,(1)选择本机上的所有网卡上绑定的所有IP地址都会显示在IP Address列表中,对应的MAC地址显示在MAC Address中,用户选择与UE进行通信的IP地址,(2) 设置正确的UE的IP地址;(3)按OK完成设置。

备注:设置moderm端口完成连接设之后,一定要断开与UE的连接,然后再重新连接一次,使设置生效。

连接分两种式:Ethernet和COM,如下图上图为打开LV(Air&Layer)实例和SG(Stat.GUI)组件后的界面示意图。

图中标示说明如下:(1)菜单栏(2)工具栏(连接功能部分)(3)工具栏(组件部分)(4)自定义命令工具栏部分业务功能简介业务功能划分Histudio从业务上支持UE端LOG数据的显示和处理,统计信息的图形化显示和处理,以及各种控制命令的管理,同时支持与第三方程序的连接和数据处理。

LOG信息处理Histudio支持的LOG数据包括Air Message(空口消息)、Layer Message(层间消息),Print Message(打印信息),Event (关键事件)和L1 Message(L1 消息)的处理。

统计可视化界面表现Histudio对各种观测量进行可视化表现,通过表格和图形的方式,表现上报观测量的趋势信息,方便用户对观测量进行分析;控制命令管理Histudio对各种命令进行了统一管理,并根据用户的使用习惯给出两种命令的管理方式,分别是命令可视化组件(CG)和诊断命令行(DCL)两个组件方式。