高速串行信号中的时钟恢复重要性_Clock Recovery Primer Part 1

高速串行信号中的时钟恢复重要性_Clock Recovery Primer Part 1

Clock Recovery Primer, Part 1 PrimerPrimer/bertscope2Table of Contentsed?........................................3How.Does.Clock.Recovery.Work?. (3)PLL-Based Clock Recovery ..............................................4Generic Phased Lock Loop Block Diagram .......................4What it Does .....................................................................4How it Works ....................................................................4What Does a Measured Loop ResponseLook Like? (5)Examples (6)Example 1: Testing a 10 Gb/s Clock Recovery Circuit (6)Example 2: Behavior of a Clock Data Recovery (CDR)Circuit (8)Where.Does.Clock.Recovery.Appear.in..Measurements? (12)Loop Bandwidth Setting in Measurements (14)The.Effect.of.Peaking....................................................15The.Effect.of.Transition.Density.and.Anomalous.Clock.Recovery.Behavior.. (16)Pattern Effects ................................................................16Anomalous Locking .. (16)Where.to.Go.Next..........................................................17Acknowledgements.......................................................17References.. (18)/bertscope 3Clock Recovery Primer, Part 1AbstractClock recovery is a common part of many measure-ments, whether as part of the test setup or part of the device under test. We’re going to look at clock recovery from a practical point of view, with emphasis on how it affects measurements. This document closely mirrors the poster “The Anatomy of Clock Recovery, Part 1.”Why is Clock Recovery Used?Most gigabit communication systems are synchronous; that is, the data within them is timed against a common clock. High speed systems (such as serial buses and optical) usually send NRZ (Non-Return to Zero) data, coded to have the clock it is timed against embedded within it. Whether traveling across inches of circuit board, or across continents on optical fiber, the relationship between data and the clock it is timed against can become disturbed. Extracting clock directly from the data ensures that data regeneration at the receiver can be achieved correctly.Receivers typically improve the incoming data before passing it on. They do this by passing it through a decision circuit that retimes the data and squares up the pulses. This process isdependent upon a clock signal synchronous with the incoming data, hence the use of clock recovery inside the receiver. Timing variations such as jitter on the incoming data can be reduced or removed if the clock used for retiming moves in the same way at the same time.As we will see, in practice the operation is more complex than this, and the frequency of the incoming jitter is important.How Does Clock Recovery Work?There are many different architectures for clock recovery, and a large amount of literature describing the advantages and disadvantages of each. In measurement equipment, the most common type is based on a phase locked loop (PLL). We will look at this in more detail in a moment. Before we do, it is worth noting that other architectures have been used in measurement equipment in the past.Older sampling scope clock recovery modules were often feed-forward designs with fixed frequency filters switched in for each rate. Suitable band pass filters are difficult to make with narrow bands. They have also not been frequency agile, and will not track data with moving center frequencies, such as is found in spread spectrum clocking (SSC; see poster “Anatomy of Clock Recovery, Part 2”).Figure.1..If clock and data were to move in time by the same amount at the same time, a decision circuit could remove the effect of jitter.Primer/bertscope4PLL-Based Clock RecoveryClock recovery is usually applied to NRZ data. Unlike PLLs used in RF applications, data signals require modification to the PLL design. One challenge is the property of NRZ (Non-Return to Zero) data that there is no discrete spectral line at the data rate. This restricts the types of phase detector that can be employed in the PLL. Examples include Bang-Bang and Hogge designs.Generic Phased Lock Loop Block Diagram What it DoesA Voltage Controlled Oscillator (VCO) free-runs initially, near the data rate of interest.A portion of the VCO signal forms one input to a phase detector.The other input to the phase detector is the incoming data. The phase detector compares the phases of the two inputs and produces an output voltage related to the phase difference (the ‘Error Signal’ above).Usually this signal is filtered in some way before it becomes the frequency control voltage of the VCO.The error signal is a demodulated, high pass filtered equivalent of the jitter present on the input data.Many different circuits can be used for the Loop Filter for different applications.How it WorksThe aim of the recovery circuit is to derive a clock that is synchronous with the incoming data.Its ability to do this is dependent upon seeing transitions in the data.For data segments with runs of identical bits, the PLL must still stay locked.The loop gain, K, has the most significant effect on the loop bandwidth and speed. Any filtering within the loop filter typically has a secondary effect [1], p.21.The system transfer function (the normal loop response seen in literature, referred to as ‘H(s)’), performs a low pass filtering operation on the phase modulation of the input signal.The error response transfer function (referred to as ‘E(s)’) performs a high pass filtering function.The loop tracks input phase modulation within the loop bandwidth, and fails to track phase modulation outside the bandwidth.This gives the loop the ability to track low frequency jitter, but to ignore high frequency jitter outside the loop bandwidth of the PLL.Figure.2..NRZ spectrum showing one challenge for clock recovery – the lack of adiscrete spectral line at the bit rate.Figure.3..PLL Block Diagram./bertscope 5Clock Recovery Primer, Part 1What Does a Measured Loop Response Look Like?A measured loop response is shown in Figure 4.One measure of the jitter tracking characteristic of a PLL is the loop bandwidth (LBW). This is often measured as the point where the transfer function of (jitter out/jitter in) is –3 dB. This is not the only way that loops can be defined [1], pp. 17–18.A wide loop bandwidth sounds ideal. However, it is usually cost and technology dependent. Wide loop bandwidths contribute more noise/random jitter. A wide loop bandwidth improves jitter tolerance; a narrow loop bandwidthremoves more jitter from the recovered clock (beneficial to downstream synchronizers) but impairs jitter tolerance. Current loop bandwidths used in measurements are typically in the range from 1 to 10 MHz.Figure.4..A measured loop response showing a PLL tracking the input jitter (left side) and then failing to track the jitter (right side).Primer/bertscope6ExamplesWe are going to look at two examples of clock recovery measurements, one with a commercial clock recovery component (Section 4), the other with a commercial clock/data recovery chip (Section 5). In each case, the classical method of test is to use sinusoidal jitter (SJ) and to change modulation frequency. Here we will keep the jitter amplitude constant throughout.Example 1: Testing a 10 Gb/s Clock Recovery CircuitRecovered clock is derived from jittered dataRecovered clock tracks less and less jitter as the frequency of jitter on the data is increasedRecovered clock is compared against jittered data in the analyzerThe analyzer measures jitter relative to the clock trigger signalIn this way, we can measure the clock recovery error transfer functionWideband equipment, such as BERTs and oscilloscopes, has intrinsic jitter that masks the loop responses at low levels in measurements such as this. As we will see later, the portions of loop responses not visible here can still have significant effects, manifesting themselves as eye closure and bit errors in some situations.Figure.5..The effect of the intrinsic jitter of a wideband measuring instrument on loopmeasurements./bertscope 7Clock Recovery Primer, Part 1Figure.6..Deriving a clock trigger from data and using it to trigger a measurement. The response is sometimes called the ‘Observed Jitter Transfer Function.’Primer/bertscope8Example 2: Behavior of a Clock Data Recovery (CDR) CircuitA CDR recovers clock from incoming data, then uses the recovered clock as the reference to trigger a retiming flip-flop to clean up the incoming data. This measurement setup used a commercially available clock data recovery chip testedat 2.488 Gb/s, with a PRBS-7 pattern and 40% (0.4 UI) Sinusoidal Jitter signal of varying modulation frequency. The amplitude is constant; only the modulation frequency is varied, in the same way receiver clock recovery is traditionally tested. All analyzer measurements show data signal relative to the trigger.Figure.7..The chip being measured.Figure.8..The chip used for these measurements./bertscope 9Clock Recovery Primer, Part 1Figure.9.1.and.9.2..Two measurement configurations of the CDR chip. The measured responses are also shown in the graph of Figure 10.Primer/bertscope10Figure.9.3.and.9.4..Two further measurement configurations of the CDR chip. The measured responses are also shown in the graph of Figure 10./bertscope 11Clock Recovery Primer, Part 1Conclusions.for.Example.2Recovered clock jitter below the loop bandwidth tracks the input jitterRecovered clock jitter above the loop bandwidth is attenuated, so the recovered clock does not track high frequency jitterJitter of retimed data is dominated by the jitter of the retiming clockHigh frequency jitter on incoming data can be of sufficiently high amplitude to cause bit-detection errors, even though the retimed, regenerated data stream appears clean on an analyzer screenTriggering of test equipment plays a crucial role in the results obtainedFigure.10..Overlaid responses of the CDR chip measured as detailed in Figure 9.Primer/bertscope12Where Does Clock Recovery Appear in Measurements?Clock recovery can be part of the device under test, and also of the test setup. Typically, when it is part of the test setup, it is intended to emulate the behavior of a receiver, particularly in tracking low frequency jitter. Ideally, this means that only jitter beyond the clock recovery tracking range of a typical receiver is seen on the test equipment eye diagram.Figure.11..The figure shows where clock recovery can appear in a device under test, and test equipment used to characterize it./bertscope 13Clock Recovery Primer, Part 1Figure.12..Building on Figure 11, the table gives details of how clock recovery is used, and what can go wrong.Primer/bertscope14Loop Bandwidth Setting in MeasurementsLoop bandwidth can have a significant effect on the observed jitter in a measurement. Varying the loop bandwidth can give an indication of the jitter spectrum. The loop bandwidthschosen for testing could be very narrow (for example, to show all the jitter a transmitter under test is creating) or wide (for example, to show only the jitter that a transmitter produces that its intended system receiver is not able to filter out with its own PLL). Typically, it is the latter, and such a clock recovery is referred to as a “Golden PLL.” A system designer is mainly interested in jitter that is beyond the capabilities of the receiver to track.Some standards (like FB-DIMM) have a range of loopbandwidths specified. While test instruments should emulate the characteristics of the test device, a range in parameters could lead to unintended results.For transmitter testing, it might be desirable to have a high loop bandwidth to make the tested transmitter look as good as possible (the transmitter intrinsic jitter is largely tracked out, so it doesn’t appear in the measurement, making the transmitter look good).For receiver jitter tolerance, the stressed eye is often set up using jitter measured on an eye diagram. The aim might be to stress the eye with jitter beyond the effect of the receiver clock recovery’s ability to track it out. If the clock recovery used for stress calibration has a lower loop bandwidth than the receiver under test will, some jitter will be included in the eye measurement that will be tracked out by the receiver. This could make the composition of the finished stressed eye less demanding than it should be.ing the same jittered signal, eye diagrams measured against a recoveredclock with narrow and wide loop bandwidth settings.Figure.14..Transmitter testing and the effect of changing loop bandwidth.Figure.15..Receiver testing and the effect of changing loop bandwidth./bertscope 15Clock Recovery Primer, Part 1The Effect of PeakingPeaking is a region near the loop bandwidth where the jitter out of a clock recovery device can be greater than the jitter input. Standards often restrict the amount of allowed peaking. The reasons why this is done are evident from the following measurements.An instrument-grade clock recovery with configurable slope and peaking was used for this measurement Loop bandwidth was set to 1 MHzThe stimulus was a fixed 400 kHz sinusoidal jitter input signal to the clock recoveryThe loop was set to 0 dB peaking (red measured response) and +3 dB peaking (green measured response).The eye diagram from the green response shows jitter gain — more jitter out of the device than was present on the input.3 dB equates to a factor of 1.41.Confirms that jitter gain is indeed +3 dB: 35 ps input x 1.41 = 49 ps jitter output.Many standards restrict the amount of peaking allowed (see table on “Anatomy of Clock Recovery, Part 2” poster). Jitter gain, particularly in a repeatered system, is highly undesirable.Peaking increases the noise/random jitter.Figure.16..Measurement of a clock recovery instrument using the same input signal containing jitter. Varying the peaking can increase the jitter beyond the amount presenton the input.Primer/bertscope16The Effect of Transition Density and Anomalous Clock Recovery BehaviorWe will look at two loop effects; the first relating the transition density of different patterns and how this affects clock recovery; the second, how locking can go wrong.Pattern EffectsThe pattern “101010…” has a transition density of 100% (every bit has a transition). PRBS patterns have an average transition density identical to a "1100" pattern — i.e., 50%. Other patterns may have a lower transition density, or one that changes in certain sections of the same pattern (such as some sections of long PRBS patterns).The number of transitions controls the amount of energy going into the clock recovery loop. The energy in the loop affects the loop parameters, including loop gain and loop bandwidth. Therefore changing patterns can alter the loop behavior.Halving the transition density can have the effect ofapproximately halving the loop bandwidth for most loop designs. Some instrument grade clock recovery solutions calibrate loop bandwidth based on the measured transition density of the incoming data. Care must be taken — some standards specify loop bandwidth at a particular transition density, and assume that the loop bandwidth will be different for measurements using the required test patterns.Anomalous LockingSidelocking- Signals with periodic modulation produce discrete spectral lines - Narrow band PLL can lock on to any sufficiently high amplitude discrete spectral line, whether the carrier or not - Called ‘sidelocking’- Short PRBS patterns have fewer, higher energy spectral lines that are widely spaced, so can be more problematic than long PRBS patterns Harmonic Locking- Data, like square wave modulation, has harmonics that can provide opportunities to lock at multiples of the desired frequency - This can also happen with some designs ofphase detectors for subharmonics, and fractional subharmonics, particularly for long runs of ones or zeros [1], p. 341These are some reasons why instrument clock recovery solutions usually require an initial frequency to be accurately established prior to acquisition.Figure.17..Conceptual view of sidelocking.Figure.18..Conceptual view of harmonic locking./bertscope 17Clock Recovery Primer, Part 1Where to Go NextIn the same way that the second “Anatomy of Clock Recovery” poster tackles more complex topics, there is a companion second primer [16], “Anatomy of Clock Recovery, Part 2,” which can be downloaded from the website.In this companion paper, the following topics are discussed: Survey of clock recovery used in various standards Types and orders Spread spectrum clocking Clock recovery and stress testingThe effect of trigger delay in measurements Distributed clock schemes Clock domainsAcknowledgementsConsiderable help has been generously given by the following people:Floyd M. GardnerEric Kvamme, Hollis Poche, Maxtor Corporation Harvey Newman, Infineon Technologies Stretch Camnitz, Avago Technologies Mark Marlett, LSI LogicRansom Stephens, Teraspeed Consulting John Calvin, TektronixGerry Talbot, Advanced Micro DevicesPrimer/bertscope18References[1] Gardner, Floyd M. 2005, 3rd Ed. Phaselock Techniques.New Jersey, John Wiley & Sons Inc. The original and definitive textbook on PLLs. Revised edition has much improved introductory chapters.[2] Best, Roland E. 2003, 5th Ed. Phase-Locked Loops,Design, Simulation and Applications. New York,McGraw-Hill. Includes instructive PLL simulation software on CD-ROM.[3] Kroupa, Venceslav F . 2003. Phase Lock Loops andFrequency Synthesis. John Wiley & Sons, Ltd., United Kingdom.[4] 10 Gigabit Ethernet and XAUI: search on “802.3aeTM”Governing body (and owner of trademark) [5] Fibre Channel information: Fibre Channel IndustryAssociation, /[6] OIF CEI standard: /public/impagreements.html [7] Serial ATA standard: [8] SONET information: GR-253-CORE, SynchronousOptical Network (SONET) Transport Systems: Common Generic Criteria, /[9] SDH information: http://www.itu.int/ITU-T/, G.xxxseries of documents, for example G.957 was anoriginal defining document for optical interfaces, G.958 described jitter.[10] XFP and XFI information: [11] Fully Buffered DIMM standard, JEDEC Study Group 45: [12] PCI Express ™ standard: /specifications/pciexpress/[13] Serial Attached SCSI information: SCSI TradeAssociation, [14] PCI Express ™ Jitter Modeling Whitepaper, Revision1.0RD, July 14, 2004, sections 3 & 4: /specifications/pciexpress/technical_library/[15] MJSQ – “Methodologies for Jitter and Signal QualitySpecification” is a document written as part of the INCITS project T11.2. /index.htm [16] ‘The Anatomy of Clock Recovery, Part 2’,Clock Recovery Primer, Part 1/bertscope19Contact.Tektronix:ASEAN./.Australasia..(65) 6356 3900Austria*..00800 2255 4835 Balkans,.Israel,.South.Africa.and.other.ISE.Countries.+41 52 675 3777Belgium*..00800 2255 4835Brazil..+55 (11) 3759 7600Canada..1 (800) 833-9200 Central.East.Europe,.Ukraine.and.the.Baltics..+41 52 675 3777Central.Europe.&.Greece..+41 52 675 3777Denmark..+45 80 88 1401Finland..+41 52 675 3777France*..00800 2255 4835Germany*..00800 2255 4835Hong.Kong..400-820-5835India..000-800-650-1835Italy*..00800 2255 4835Japan..81 (3) 6714-3010Luxembourg..+41 52 675 3777 Mexico,.Central/South.America.&.Caribbean..52 (55) 56 04 50 90Middle.East,.Asia.and.North.Africa..+41 52 675 3777herlands*..00800 2255 4835Norway..800 16098People’s.Republic.of.China..400-820-5835Poland..+41 52 675 3777Portugal..80 08 12370Republic.of.Korea..001-800-8255-2835Russia.&.CIS..+7 (495) 7484900South.Africa. +27 11 206 8360Spain*..00800 2255 4835Sweden*..00800 2255 4835Switzerland*..00800 2255 4835Taiwan..886 (2) 2722-9622.United.Kingdom.&.Ireland*..00800 2255 4835USA..1 (800) 833-9200 *.If.the.European.phone.number.above.is.not.accessible,.please.call.+41.52.675.3777Contact List Updated 25 May 2010. rmationTektronix maintains a comprehensive, constantly expanding collection of application notes, technical briefs and other resources to help engineers working on the cutting edge of technology. Please visit Copyright © 2010, Tektronix. All rights reserved. Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supersedes that in all previously published material. Specification and price change privileges reserved. TEKTRONIX and TEK are registered trademarks of Tektronix, Inc. All other trade names referenced are the service marks, trademarks or registered trademarks of their respective companies.09/10 EA/WWW 65W-26023-0。

cdr时钟恢复原理

cdr时钟恢复原理CDR时钟恢复原理CDR(Clock and Data Recovery)时钟恢复电路是高速通信系统中一个重要的模块,它是将来自外部世界的串行数据流和时钟信号恢复出来的模块,以保证高速通信系统的可靠性和稳定性。

CDR时钟恢复原理主要有以下几点:1. 时钟信号恢复CDR时钟恢复电路的核心是时钟信号恢复电路,其中包括相锁环(PLL)电路、延迟锁定环(DLL)电路等。

时钟信号恢复电路的作用是通过对输入数据的采样和调整来恢复数据中的时钟信号。

PLL电路是最常用的时钟恢复电路,它通过对输入数据的采样,检测数据中的时钟信号,通过反馈控制电路调节本地时钟的频率和相位,实现时钟恢复的目的。

2. 数据恢复CDR时钟恢复电路中的数据恢复模块主要是通过对采样到的数据进行判决,恢复出原始的数字信号。

数据恢复模块的设计决定了整个CDR 时钟恢复电路的性能和稳定性。

3. 自适应算法当外界环境发生变化时,CDR时钟恢复电路需要具备自适应能力,使其能够及时调整自己的参数,以保持良好的性能。

常用的自适应算法包括自适应等化算法、自适应滤波算法、自适应决策反馈等。

4. 抗噪性能CDR时钟恢复电路中的抗噪性能直接影响到它在高速通信系统中的可靠性和稳定性。

在设计CDR时钟恢复电路时,需要考虑到外界噪声对系统性能的影响,并采用一些措施来提高系统抗噪性能,例如滤波器、前置放大器等。

5. 稳定性和可靠性CDR时钟恢复电路在高速通信系统中是一个核心模块,它需要具备高度的稳定性和可靠性。

稳定性和可靠性取决于电路中各个模块的设计和参数选择,需要在实际应用中进行充分调试和测试,以确保系统的稳定性和可靠性。

综上所述,CDR时钟恢复原理涉及到多个方面,包括时钟信号恢复、数据恢复、自适应算法、抗噪性能、稳定性和可靠性等,需要在设计和应用中综合考虑,以保证高速通信系统的正常运行和性能指标的达标。

高速数据传输系统中的时钟恢复与时序校准

高速数据传输系统中的时钟恢复与时序校准随着科技的不断进步,高速数据传输系统在现代通信中扮演着至关重要的角色。

然而,由于信号传输的复杂性和高速性,时钟恢复和时序校准成为了这些系统中的重要问题。

本文将介绍高速数据传输系统中的时钟恢复和时序校准的原理和方法。

时钟恢复是指在接收端恢复出与发送端相同的时钟信号。

在高速数据传输系统中,由于传输链路的噪声和失真,时钟信号可能会发生偏移和抖动,导致接收端无法准确地解读数据。

为了解决这个问题,可以使用时钟恢复电路。

时钟恢复电路通过对接收到的信号进行采样和重构,以恢复出准确的时钟信号。

常用的时钟恢复方法有边沿对齐和时钟数据恢复。

边沿对齐是一种常用的时钟恢复方法。

它基于传输信号的边沿来恢复时钟信号。

在接收端,时钟恢复电路会对传输信号进行采样,并根据采样到的边沿来生成时钟信号。

这种方法的优点是实现简单,但对传输信号的边沿要求较高。

时钟数据恢复是一种更为复杂的时钟恢复方法。

它通过对传输信号进行采样并解调,以恢复出准确的时钟信号和数据。

在接收端,时钟数据恢复电路会对传输信号进行采样,并解调出时钟信号和数据。

这种方法的优点是对传输信号的边沿要求较低,但实现难度较大。

时序校准是指在高速数据传输系统中对时钟和数据进行校准,以保证数据的准确传输。

在高速数据传输系统中,时钟和数据的传输速率往往不完全一致,容易导致时钟和数据之间的偏移。

为了解决这个问题,可以使用时序校准电路。

时序校准电路通过对时钟和数据进行延迟和对齐,以保证数据的准确传输。

常用的时序校准方法有延迟锁定环和自适应等化器。

延迟锁定环是一种常用的时序校准方法。

它通过对时钟和数据进行延迟和对齐,以保证数据的准确传输。

在接收端,延迟锁定环会对时钟和数据进行延迟,并通过反馈机制来调整延迟值,使得时钟和数据能够保持同步。

这种方法的优点是实现简单,但对传输信号的时钟和数据要求较高。

自适应等化器是一种更为复杂的时序校准方法。

它通过对传输信号进行采样和反馈,以自动调整等化器的参数,以保证数据的准确传输。

高速数字信号传输设计中的时钟数据恢复技术

高速数字信号传输设计中的时钟数据恢复技术在高速数字信号传输设计中,时钟数据恢复技术起着至关重要的作用。

当信号传输速度达到一定水平时,准确、稳定的时钟信号是保证数据传输质量的关键。

在本文中,我们将深入探讨高速数字信号传输设计中的时钟数据恢复技术。

首先,让我们了解时钟数据恢复技术的基本原理。

在数字通信中,发送端和接收端的时钟频率可能会产生偏差,导致数据传输时钟信号不同步,从而影响到数据的准确性和稳定性。

时钟数据恢复技术的主要目的就是通过在接收端重新生成一个稳定的时钟信号,以确保正确采样数据。

这种技术在高速传输中尤为重要,因为在高速传输中时钟偏差会更加明显。

时钟数据恢复技术主要有两种方法:一种是基于信号的恢复,另一种是基于时钟的恢复。

基于信号的恢复方法通过分析接收到的数据信号来提取时钟信息,然后根据这些信息生成本地时钟信号。

这种方法适用于信号质量较好的情况下,但在高噪声环境下可能会受到影响。

而基于时钟的恢复方法则是通过在数据中嵌入时钟信息,然后在接收端利用这些信息来恢复时钟信号。

这种方法对信号质量要求不高,但可能会增加数据传输的复杂性。

在实际应用中,常用的时钟数据恢复技术包括Costas环、PLL(锁相环)和CDR(时钟数据恢复器)。

Costas环是一种经典的时钟数据恢复技术,通过对接收信号的相位进行解调,提取出时钟信息并进行时钟恢复。

PLL则是一种常用的时钟同步技术,通过对输入信号进行频率和相位的比较,使得输出时钟信号与输入信号同步。

而CDR则是一种更加先进的技术,通过对接收到的数据进行采样和比较,自动调整时钟频率和相位来实现时钟数据恢复。

在设计高速数字信号传输系统时,选择合适的时钟数据恢复技术至关重要。

不同的应用场景可能需要不同的技术方案,例如对于长距离传输和高噪声环境下,CDR技术可能更适合;而对于简单的短距禁止传输,PLL可能就足够了。

在选择时钟数据恢复技术时,还需要考虑到系统的复杂度、成本和功耗等因素,以寻求最佳的平衡点。

SERDES关键技术总结

SERDES关键技术总结SERDES(Serializer/Deserializer)是一种用于高速串行通信的关键技术,通过将并行数据转换为串行数据进行传输,可以提供更高的数据传输速度,并帮助减少电缆数量和布线复杂性。

下面是对SERDES关键技术的总结:1. 前向纠错编码(Forward Error Correction,FEC):FEC是一种通过在发送端增加冗余数据来纠正传输中的错误的技术。

FEC可以提高传输信号的可靠性,减少误码率,以适应高速串行通信的需求。

2. 消除时钟抖动(Clock Jitter Elimination):时钟抖动是指时钟信号的相位和频率变化,由于时钟抖动会导致数据在传输过程中出错,因此消除时钟抖动是实现高速串行通信的关键。

SERDES通过使用特殊的时钟恢复技术,可以有效地抵消时钟抖动,保证数据传输的正确性。

3. 自适应等化器(Adaptive Equalizer):等化器是一种用于补偿信号受损影响的技术,通过对信号进行预处理和滤波,可以减少传输中的失真。

自适应等化器可以根据接收到的反馈信息实时调整等化器参数,以适应不同信道条件和传输距离,提高信号的传输质量。

4. 动态电源管理(Dynamic Power Management):SERDES在高速数据传输时需要消耗大量的功率,因此动态电源管理是必不可少的技术。

动态电源管理技术可以根据传输的需求,动态地调整电源供应方式和功耗,以实现更低的功耗和更好的能效。

5. 串并转换器(Serial-to-Parallel Converter)和并串转换器(Parallel-to-Serial Converter):SERDES的核心是串并转换器和并串转换器,它们是将并行数据转换为串行数据或将串行数据转换为并行数据的关键部件。

串并转换器将多个并行数据源组合成一个高速串行数据流,用于发送端;并串转换器将高速串行数据流拆分为多个并行数据流,用于接收端。

高速串行通信系统设计中的时钟恢复技术

高速串行通信系统设计中的时钟恢复技术在高速串行通信系统设计中,时钟恢复技术起着至关重要的作用。

时钟恢复技术是指在通信过程中确保接收端能够正确恢复发送端的时钟信号,从而保证数据的准确传输。

下面将介绍高速串行通信系统设计中的时钟恢复技术的原理和方法。

首先,要了解为什么需要时钟恢复技术。

在高速串行通信系统中,由于信号传输距离远、传输速率高,信号在传输过程中受到多种因素的影响,例如传输介质的损耗、延迟等,导致接收端无法准确识别发送端的时钟信号。

如果接收端无法正确恢复时钟信号,就会导致数据传输错误,严重影响通信质量。

为了解决时钟信号恢复问题,一种常用的方法是采用时钟数据恢复电路。

时钟数据恢复电路通过对接收到的数据进行采样、比较和调整,从而恢复出正确的时钟信号。

常见的时钟数据恢复电路包括延时锁相环(DLL)和相位锁定环(PLL)。

延时锁相环是一种常用的时钟恢复技术,它通过调整延时单元的延时时间,使接收端的时钟信号与发送端的时钟信号同步。

延时锁相环通常包括相位检测器、环路滤波器和延时单元。

相位检测器用于检测两个时钟信号之间的相位误差,环路滤波器用于对误差进行滤波和放大,延时单元用于根据误差信号调整延时时间。

相位锁定环是另一种常用的时钟恢复技术,它通过比较接收端数据的相位和发送端的时钟信号相位,从而调整本地时钟信号的频率和相位,使两者同步。

相位锁定环通常包括相位频率检测器、环路滤波器和调节单元。

相位频率检测器用于检测相位和频率误差,环路滤波器用于对误差进行滤波和放大,调节单元用于根据误差信号调整本地时钟信号。

除了延时锁相环和相位锁定环,还有其他一些时钟恢复技术,如周期估计法、数据边界对齐法等。

这些技术在不同的通信系统中有着不同的应用,选择合适的时钟恢复技术对于提高通信系统的性能至关重要。

总的来说,时钟恢复技术在高速串行通信系统设计中扮演着关键的角色。

通过合理选择和设计时钟恢复电路,可以保证通信系统在高速传输时能够准确恢复时钟信号,确保数据的准确传输。

超高速数码信号传输中的时钟恢复技术研究

高速数字信号传输设计中的时钟数据恢复算法在高速数字信号传输设计中,时钟数据恢复算法扮演着至关重要的角色。

时钟数据恢复算法是指用于从接收到的高速数字信号中恢复出正确的时钟信号和数据的算法。

在数字通信系统中,由于传输介质和其他因素的影响,接收到的信号可能会受到时钟抖动、噪声干扰等问题,导致时钟信号和数据产生偏移或失真。

时钟数据恢复算法的作用就是通过对接收信号进行采样、时钟提取、相位调整等操作,来有效地恢复出正确的时钟和数据。

在高速数字信号传输中,时钟数据恢复算法通常应用在串行通信接口中,用于将串行数据信号还原为并行数据信号。

其中一个常见的时钟数据恢复算法是基于边沿速率的时钟恢复算法。

该算法通过检测接收到的信号中的边沿来生成时钟信号,然后利用这个时钟信号对数据信号进行采样和恢复。

另一个常见的算法是相关性检测算法,它通过对接收信号进行相关性分析,来估计时钟信号和数据信号之间的关系,进而进行时钟数据恢复。

时钟数据恢复算法的设计需要考虑到多个方面的因素,包括传输介质特性、信号特点、抖动噪声情况等。

首先,需要对接收信号的波形进行分析,了解信号中的时钟信息和数据信息的特点,进而选择合适的恢复算法。

其次,针对不同的传输介质和抖动噪声情况,需要进行合适的滤波和增益调整,以提高时钟数据恢复的准确性和稳定性。

此外,还需要考虑到时钟频率的漂移和偏移等问题,设计相应的自适应算法来进行校准和调整。

在实际应用中,时钟数据恢复算法的性能直接影响到数字通信系统的稳定性和可靠性。

一个高效的时钟数据恢复算法可以有效地降低误码率,提高通信质量。

因此,工程师们在设计数字通信系统时需要认真考虑时钟数据恢复算法的选择和优化,以确保系统能够在高速数字信号传输中保持高性能和稳定性。

总的来说,高速数字信号传输设计中的时钟数据恢复算法是一个复杂而关键的技。

高速数字信号传输设计中的时钟数据恢复算法

高速数字信号传输设计中的时钟数据恢复算法在高速数字信号传输设计中,时钟数据恢复算法扮演着至关重要的角色。

时钟数据恢复算法是指用于从接收到的高速数字信号中恢复出正确的时钟信号和数据的算法。

在数字通信系统中,由于传输介质和其他因素的影响,接收到的信号可能会受到时钟抖动、噪声干扰等问题,导致时钟信号和数据产生偏移或失真。

时钟数据恢复算法的作用就是通过对接收信号进行采样、时钟提取、相位调整等操作,来有效地恢复出正确的时钟和数据。

在高速数字信号传输中,时钟数据恢复算法通常应用在串行通信接口中,用于将串行数据信号还原为并行数据信号。

其中一个常见的时钟数据恢复算法是基于边沿速率的时钟恢复算法。

该算法通过检测接收到的信号中的边沿来生成时钟信号,然后利用这个时钟信号对数据信号进行采样和恢复。

另一个常见的算法是相关性检测算法,它通过对接收信号进行相关性分析,来估计时钟信号和数据信号之间的关系,进而进行时钟数据恢复。

时钟数据恢复算法的设计需要考虑到多个方面的因素,包括传输介质特性、信号特点、抖动噪声情况等。

首先,需要对接收信号的波形进行分析,了解信号中的时钟信息和数据信息的特点,进而选择合适的恢复算法。

其次,针对不同的传输介质和抖动噪声情况,需要进行合适的滤波和增益调整,以提高时钟数据恢复的准确性和稳定性。

此外,还需要考虑到时钟频率的漂移和偏移等问题,设计相应的自适应算法来进行校准和调整。

在实际应用中,时钟数据恢复算法的性能直接影响到数字通信系统的稳定性和可靠性。

一个高效的时钟数据恢复算法可以有效地降低误码率,提高通信质量。

因此,工程师们在设计数字通信系统时需要认真考虑时钟数据恢复算法的选择和优化,以确保系统能够在高速数字信号传输中保持高性能和稳定性。

总的来说,高速数字信号传输设计中的时钟数据恢复算法是一个复杂而关键的技。

高速数据传输系统中的时钟恢复与时序校准

高速数据传输系统中的时钟恢复与时序校准在现代科技的发展中,高速数据传输系统扮演着至关重要的角色。

无论是互联网、移动通信还是计算机网络,都离不开高速数据传输系统的支持。

而在这些系统中,时钟恢复与时序校准是保证数据传输可靠性的关键环节。

时钟恢复是指在数据传输过程中,接收端需要通过一定的方法来恢复发送端的时钟信号。

由于信号在传输过程中会受到噪声、衰减等因素的影响,时钟信号可能会发生偏移或失真。

而时钟恢复的目的就是通过接收到的数据信号,重新生成一个与发送端同步的时钟信号。

为了实现时钟恢复,通常会采用一些特定的算法和电路设计。

其中,最常见的方法是使用锁相环(PLL)技术。

锁相环是一种通过比较输入信号和本地时钟信号的相位差,并根据差值来调整本地时钟信号的频率和相位的反馈控制系统。

通过不断调整本地时钟信号,使其与输入信号同步,从而实现时钟恢复。

除了时钟恢复外,时序校准也是高速数据传输系统中不可或缺的一环。

时序校准是指在数据传输过程中,为了保证数据的准确性和稳定性,需要对数据信号进行时序的校准和调整。

在高速数据传输系统中,时序校准主要包括数据对齐、时钟提取和时钟校准三个方面。

数据对齐是指将接收到的数据信号按照正确的顺序进行排列,以确保数据的正确性。

在数据传输中,由于信号在传输过程中会受到干扰和失真的影响,导致接收到的数据信号可能会发生错位。

因此,需要通过一定的算法和电路设计,对接收到的数据信号进行对齐操作,使其按照正确的顺序排列。

时钟提取是指从接收到的数据信号中提取出时钟信号。

在高速数据传输系统中,时钟信号通常会被混合在数据信号中传输,因此需要通过一定的方法来提取出时钟信号。

常见的方法包括使用锁相环技术或者专门的时钟恢复电路。

时钟校准是指对接收到的时钟信号进行校准和调整,以确保其与发送端的时钟信号同步。

在高速数据传输系统中,由于信号在传输过程中会受到噪声、衰减等因素的影响,导致接收到的时钟信号可能会发生偏移或失真。

高速通信系统中的时钟恢复技术

高速通信系统中的时钟恢复技术随着互联网的快速发展,高速通信系统的应用范围不断扩大。

高速通信系统通常需要在不同的设备之间传输大量的数据,而时钟同步问题是这些设备之间交流的重要问题之一。

为了保证高速通信系统的正确性和可靠性,时钟恢复技术显得尤为重要。

本文将对高速通信系统中的时钟恢复技术进行探讨。

一、时钟同步问题在高速通信系统中,时钟同步指的是保持不同设备之间的时钟频率、相位和时间的同步。

在通信系统中,时钟同步问题是非常重要的,因为任何精度误差都会导致数据传输损失和系统崩溃。

时钟同步问题的难点在于,不同设备之间的时钟是由不同的晶振驱动的。

而在不同的环境中,晶振的频率和精度会变化,导致时钟频率的不同,这就会引起时钟同步问题。

二、时钟恢复技术时钟恢复技术是用于解决时钟同步问题的一种重要技术。

它通过同步数据传输的时钟信号来恢复时钟的同步性。

在高速通信系统中,时钟恢复技术可以划分为两种类型:线性插值时钟恢复技术和非线性插值时钟恢复技术。

1、线性插值时钟恢复技术线性插值时钟恢复技术基于线性插值方法,通过许多样本的统计来恢复时钟。

它是一种精度高的时钟恢复技术,广泛应用于高速通信系统中。

该技术的原理是,通过利用两个相邻数据信号的时间间隔来计算时钟信号的周期。

这样可以在时钟信号中添加插值点,从而恢复数据传输的时钟同步性。

由于线性插值时钟恢复技术的精度高,因此它在高速通信系统中被广泛使用。

2、非线性插值时钟恢复技术非线性插值时钟恢复技术是一种新型的时钟恢复技术,它采用基于梳状滤波器的信号复原方法,从而实现了高精度的时钟恢复。

在非线性插值时钟恢复技术中,时钟信号被转换为等间隔离散样本,并通过梳状滤波器来进行时钟恢复。

这样可以在高速通信系统中完成高精度的时钟恢复,以便高速数据传输。

三、时钟恢复技术的应用时钟恢复技术在许多场合都被广泛应用。

在高速通信系统中,独立时钟链的时钟恢复技术在网络中被广泛应用,这种技术可以确保时间同步的可靠性。

高速通信接口中的时钟提取与恢复技术

高速通信接口中的时钟提取与恢复技术在高速通信接口中,时钟提取与恢复技术是非常重要的一项技术。

在数字通信中,时钟信号是保持数据传输顺利进行的关键。

时钟提取与恢复技术能够帮助确保数据的正常传输并保持通信的稳定性。

时钟提取与恢复技术主要是指在接收端将接收到的数据信号中的时钟信息提取出来,并将其与本地时钟同步,以确保数据的准确接收和处理。

在高速通信接口中,由于信号传输距离远、传输速度快,时钟信号可能会因为受到信号失真、传输延迟等影响而产生抖动或失真。

这就需要时钟提取与恢复技术来解决这些问题。

时钟提取与恢复技术通常是通过专门的时钟恢复模块实现的。

在接收端,通过时钟恢复模块可以从接收到的数据信号中提取出时钟信号,然后与本地时钟进行同步。

这样可以保证接收数据时在适当的时机采样数据,确保数据的准确性和完整性。

时钟提取与恢复技术在高速通信接口中的应用非常广泛。

无论是在网络通信、数据存储、数字视频传输等领域,时钟提取与恢复技术都起着至关重要的作用。

对于高速通信接口而言,时钟信号的稳定性和准确性直接影响到数据传输的可靠性和性能。

在实际应用中,时钟提取与恢复技术通常会受到许多因素的影响,比如信号失真、传输延迟、温度变化等。

因此,设计一个稳定可靠的时钟提取与恢复技术方案是非常重要的。

工程师们需要根据具体的应用场景和需求,选择适合的时钟提取与恢复技术方案,并进行充分的测试和验证,确保系统可以稳定、可靠地工作。

总的来说,高速通信接口中的时钟提取与恢复技术是数字通信中非常重要的一环。

它可以帮助确保数据的准确传输,保持通信的稳定性,提高系统的可靠性和性能。

因此,工程师们在设计高速通信系统时,一定要重视时钟提取与恢复技术的应用,选择合适的方案,确保系统能够稳定可靠地运行。

高速信号传输与时钟恢复技术研究

高速信号传输与时钟恢复技术研究随着大数据时代的到来,数据的传输量越来越大,数据传输速率的要求也越来越高。

高速信号传输与时钟恢复技术的研究成为了越来越重要的课题。

一、高速信号传输技术高速信号传输技术是指在信号具有高速、高频、大幅度变化的情况下,保证信号传输的准确性、稳定性和高速性的一种技术。

1. 信号传输的准确性在高速信号传输过程中,由于存在信号失真、信号干扰等因素,会导致信号传输的准确性降低。

针对这个问题,研究人员采用了预加重、均衡、串并转换等技术,使信号传输的准确性得到了提高。

2. 信号传输的稳定性在高速信号传输过程中,由于存在信号衰减、串扰等因素,会导致信号传输的稳定性降低。

针对这个问题,研究人员采用了匹配阻抗、差分传输、封闭式传输等技术,使信号传输的稳定性得到了提高。

3. 信号传输的高速性随着时代的发展,对高速信号传输速率的要求也越来越高。

现在的高速信号传输技术已经能够实现很高的速率,比如USB3.2技术支持的最高速率可以达到20Gbps。

二、时钟恢复技术高速信号传输技术中,时钟数据的传输非常重要。

时钟信号的不准确或者不稳定都会影响信号传输的准确性,因此时钟恢复技术的研究非常重要。

时钟恢复技术是指当接收到的信号中不包含时钟信息时,通过接收到的其它信息来恢复时钟信息的一种技术。

1. 时钟数据的获取时钟数据获取有两种方式:一种是对收到的信号进行采样,另一种是通过PLL锁相环来获取。

2. 时钟数据的恢复将时钟数据恢复到正常范围内,有两种方式:一种是通过比较数据间隙的大小,来判断信号的位移,以此恢复时钟数据;另一种是通过构造包络线,根据包络线的周期来进行时钟恢复。

三、快速时钟同步技术在高速信号传输中,往往需要同时在多个设备之间进行信号传输,此时需要使用快速时钟同步技术。

快速时钟同步技术是指,在多个设备之间进行时钟同步,以达到信号传输的同步的一种技术。

1. 快速时钟同步的原理快速时钟同步的原理是在多个设备之间,通过空中介质或者电缆,传递不同设备的时钟信号,经过特定处理后,使得多个设备之间的时钟信号同步。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)是一种重要的数字通信技术,用于在高速数据传输中恢复时钟信号。

本文将介绍时钟数据恢复的基本概念、工作原理、应用领域、优势以及发展趋势。

一、基本概念1.1 时钟数据恢复是指在数字通信系统中,通过采样和重构技术,从接收到的数据流中提取出时钟信号。

1.2 时钟数据恢复通常用于高速串行通信系统,以确保数据传输的稳定性和准确性。

1.3 时钟数据恢复可以根据不同的传输标准和速率进行调整和优化,以适应不同的应用场景。

二、工作原理2.1 时钟数据恢复的工作原理主要包括信号采样、时钟提取和时钟重构三个步骤。

2.2 信号采样是通过对接收到的数据流进行采样,获取数据的波形信息。

2.3 时钟提取是从采样的数据中提取出时钟信号,以确定数据的传输速率和时序关系。

2.4 时钟重构是根据提取出的时钟信号,对接收到的数据进行重新定时,以恢复原始的时钟信号。

三、应用领域3.1 时钟数据恢复广泛应用于高速数字通信系统,如光纤通信、高速总线、数据存储等领域。

3.2 在光纤通信系统中,时钟数据恢复可以提高数据传输的稳定性和可靠性,减少误码率。

3.3 在数据存储系统中,时钟数据恢复可以确保数据的读写速度和准确性,提高系统性能和可靠性。

四、优势4.1 时钟数据恢复可以有效解决高速数据传输中时钟漂移和时钟颤动等问题,提高系统的稳定性和可靠性。

4.2 时钟数据恢复可以适应不同的传输标准和速率,具有较强的通用性和灵便性。

4.3 时钟数据恢复技术不断发展和优化,可以满足不断增长的数据传输需求和挑战。

五、发展趋势5.1 随着数字通信技术的不断发展,时钟数据恢复技术将继续向更高速、更稳定、更智能的方向发展。

5.2 时钟数据恢复技术将与其他数字通信技术相结合,实现更高效的数据传输和处理。

5.3 时钟数据恢复技术将在5G通信、物联网、人工智能等领域发挥越来越重要的作用,推动数字化社会的发展和进步。

总结:时钟数据恢复是一种重要的数字通信技术,通过采样和重构技术,可以提取出时钟信号,确保高速数据传输的稳定性和准确性。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)引言概述:时钟数据恢复(Clock Data Recovery, CDR)是一种数字通信领域中常用的技术,用于从接收到的信号中恢复出时钟信息,并将其用于数据采样和解码。

本文将介绍时钟数据恢复的工作原理以及其在通信系统中的应用。

一、时钟数据恢复的原理1.1 时钟信号的重要性时钟信号在数字通信系统中起着至关重要的作用,它用于同步发送和接收端的数据采样和解码过程。

时钟信号的准确性和稳定性直接影响到通信系统的性能。

1.2 时钟数据恢复的需求在数字通信中,接收到的信号可能会受到传输介质、噪声等因素的影响,导致时钟信号的失真和抖动。

因此,需要一种方法来从接收到的信号中恢复出准确的时钟信息。

1.3 时钟数据恢复的原理时钟数据恢复的原理是基于接收到的信号中的边缘信息来恢复时钟信号。

通过比较信号的上升沿和下降沿的时间间隔,可以推测出时钟信号的频率和相位,从而实现时钟数据的恢复。

二、时钟数据恢复的应用2.1 数字通信系统时钟数据恢复在数字通信系统中广泛应用,用于恢复接收端的时钟信号,以确保数据的准确采样和解码。

它可以应对传输介质的噪声和失真,提高通信系统的可靠性和性能。

2.2 光纤通信在光纤通信中,时钟数据恢复被用于恢复接收端的光信号的时钟信息。

光信号在传输过程中可能会受到光纤的色散和衰减等影响,导致时钟信号的失真。

时钟数据恢复技术可以有效地恢复出准确的时钟信号,提高光纤通信系统的性能。

2.3 高速串行通信在高速串行通信中,时钟数据恢复被用于恢复接收端的时钟信号。

高速串行通信中的时钟信号往往由数据信号中的边缘信息推测而来,因此时钟数据恢复技术对于保证数据的准确采样和解码至关重要。

三、时钟数据恢复的算法3.1 相位锁定环路(Phase Locked Loop, PLL)相位锁定环路是一种常用的时钟数据恢复算法。

它通过不断调整本地时钟的相位和频率,使其与接收到的信号的相位和频率保持同步,从而实现时钟数据的恢复。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)引言概述:时钟数据恢复(Clock Data Recovery, CDR)是一种用于恢复传输信号中的时钟信息的技术。

在数字通信中,信号传输过程中可能会受到噪声、失真等干扰,导致时钟信息的丢失或者不稳定。

CDR技术通过对传输信号进行采样和重构,恢复出准确的时钟信号,确保数据的可靠传输。

本文将从原理、应用、算法、性能和未来发展等五个方面详细介绍时钟数据恢复技术。

一、原理:1.1 时钟信号的重要性:时钟信号在数字通信中起到同步和定时的作用,确保数据的准确传输。

1.2 时钟信号的丢失和不稳定性原因:传输信号受到噪声、失真、衰减等干扰因素影响,导致时钟信息的丢失或者不稳定。

1.3 CDR的作用:CDR技术通过采样和重构传输信号,恢复出准确的时钟信号,保证数据的可靠传输。

二、应用:2.1 光纤通信中的CDR:光纤通信中,光信号在传输过程中容易受到衰减、色散等影响,导致时钟信息的丢失。

CDR技术可以恢复出准确的时钟信号,提高光纤通信的性能。

2.2 高速串行通信中的CDR:高速串行通信中,时钟信号的恢复对于数据的传输速率和稳定性至关重要。

CDR技术可以在高速串行通信中实时恢复时钟信号,确保数据的可靠传输。

2.3 高频信号处理中的CDR:在高频信号处理中,时钟信号的准确性对于信号处理算法的性能有着重要影响。

CDR技术可以提供准确的时钟信号,提高高频信号处理的精度和效果。

三、算法:3.1 时钟恢复算法的分类:时钟恢复算法可以分为基于锁相环(PLL)的算法和基于非锁相环的算法两类。

3.2 基于PLL的时钟恢复算法:基于PLL的时钟恢复算法通过不断调整反馈环路的相位和频率,使得恢复的时钟信号与原始时钟信号同步。

3.3 基于非锁相环的时钟恢复算法:基于非锁相环的时钟恢复算法通过统计和估计传输信号的特征,恢复出准确的时钟信号。

四、性能:4.1 时钟恢复的误差和抖动:时钟恢复算法的性能可以通过误差和抖动来评估,误差指恢复的时钟信号与原始时钟信号之间的差距,抖动指时钟信号的不稳定性。

时钟数据恢复(CDR)

时钟数据恢复(CDR)引言概述:时钟数据恢复(Clock Data Recovery,CDR)是一种常见的数字信号处理技术,用于在数字通信系统中恢复丢失或者损坏的时钟信号。

CDR技术在高速通信领域具有重要的应用价值,能够提高数据传输的可靠性和稳定性。

本文将从五个大点来详细阐述CDR技术的原理、应用、算法和发展趋势。

正文内容:1. CDR技术的原理1.1 时钟信号的重要性1.2 时钟信号的损失与恢复1.3 CDR技术的基本原理2. CDR技术的应用2.1 高速通信系统2.2 光纤通信系统2.3 无线通信系统3. CDR技术的算法3.1 直接数字控制(DDC)3.2 预估与补偿(Feedforward and Feedback)3.3 相位锁定环(Phase-Locked Loop,PLL)4. CDR技术的发展趋势4.1 高速率与低功耗4.2 自适应与自校准4.3 多通道与多模式5. CDR技术的挑战与解决方案5.1 噪声与颤动的影响5.2 时钟频率偏移的补偿5.3 多通道干扰的抑制总结:CDR技术作为一种重要的数字信号处理技术,在高速通信领域发挥着关键的作用。

本文从CDR技术的原理、应用、算法和发展趋势进行了详细阐述。

CDR技术的原理包括时钟信号的重要性、损失与恢复以及CDR技术的基本原理。

CDR技术在高速通信系统、光纤通信系统和无线通信系统等领域具有广泛的应用。

CDR 技术的算法包括直接数字控制、预估与补偿和相位锁定环等。

CDR技术的发展趋势主要包括高速率与低功耗、自适应与自校准以及多通道与多模式等方面。

然而,CDR技术也面临着一些挑战,如噪声与颤动的影响、时钟频率偏移的补偿和多通道干扰的抑制等。

未来,CDR技术将继续发展,以应对不断增长的通信需求。

高速高密度信号传输系统中的时钟恢复技术研究

高速高密度信号传输系统中的时钟恢复技术研究随着科技的持续发展,高速高密度信号传输系统在现代通信、计算机和数据存储等领域中发挥着重要作用。

这些系统的性能要求越来越高,而时钟恢复技术则成为确保系统高可靠性和稳定性的关键之一。

本文将探讨在高速高密度信号传输系统中的时钟恢复技术,并介绍一些相关的研究。

在高速高密度信号传输系统中,时钟恢复技术的目标是从输入的恢复时钟信号中提取有效的时钟信息,并用于同步和采样数据。

时钟信号具有一定的时钟抖动、相位偏移和噪声等问题,这些问题会对系统的性能产生负面影响。

因此,时钟恢复技术需要能够准确、快速地使用恢复时钟信号,以确保系统的正常运行。

在研究中,一种常见的时钟恢复技术是基于频率锁定循环(PLL)的方式。

PLL技术通过监测输入时钟信号的相位偏移并将其反馈给产生时钟信号的振荡器,从而实现时钟恢复和同步。

通过这种方式,PLL可以自适应地调整时钟频率和相位,以适应不同的输入信号条件。

然而,PLL技术存在一定的复杂性和延迟,并且对恢复时钟信号质量具有一定的要求。

为了解决PLL技术的一些问题,研究者提出了许多改进的时钟恢复技术。

其中一种技术是基于半周期恢复的方式。

这种技术通过监测输入时钟信号的半周期边沿,并将其延迟半个周期后作为恢复的时钟信号,以实现时钟恢复。

相比于PLL技术,半周期恢复技术具有更低的复杂性和延迟,并且对恢复时钟信号的质量要求较低。

然而,半周期恢复技术在恢复时钟频率的调整上相对有限。

除了上述技术,还有一种被广泛应用的时钟恢复技术是基于追踪环(TC)的方式。

TC技术是一种基于二阶锁相环的时钟恢复技术,可以实现高精度和高抗噪声能力的时钟恢复。

通过使用TC技术,可以在输入时钟信号中提取出时钟相位和频率的信息,并将其用于产生恢复时钟信号。

相比于其他技术,TC技术可以实现更高的时钟恢复精度和更广泛的适应性。

除了这些常见的时钟恢复技术,还有一些新颖的研究正在进行中。

例如,基于深度学习算法的时钟恢复技术被提出,并在一些领域取得了很好的应用效果。

时钟与数据恢复(CDR)技术在高速串行通信链路中的应用

时钟数据恢复(CDR)电路广泛应用于电信、光收发器、数据存储局域网以及无线产品中,随着对于带宽的要求越来越高,以及分配和占用频谱的增加,因而在设计中,CDR技术的优势将日益突出。

与此同时,供应商的产品都将系统或板级接口从并行方式转换成串行方式。

时钟数据恢复(CDR)技术的产生近几年,CDR技术的应用大为增长,已超出了在处理较宽并行数据总线跨背板连接时对接收端时钟管理和数据偏斜的需求。

由于这些并行数据总线信号占用较大的板尺寸并消耗较大的功率,因而它们之间的路由非常困难,故需要采用多层路由结构来处理信号和总线端接问题。

除此之外,还必需解决高位宽数据总线所产生的EMI(电磁干扰)问题。

随着通信新技术的出现和电信号处理技术的改进以及要求通过FR(帧中继)-4背板、光纤和无线媒介发送电信号技术问题的问世,从而使CDR技术尤为显得重要。

为确保证时钟和数据相组合的信号能同时到达,在发送端首先将时钟和数据复合的通信技术已广泛被采用并不稀罕,而关键在于如何在接收端将时钟和数据能分离开来,而这项工作须由CDR电路完成。

此时,将数据从并行格式转换到串行格式或实现相反转换的产品又称为串行器/解串器。

这些串行器/解串器的产品通常包含有CDR电路,用于对串行数据流的解串。

本文论述的是:在高速串行通信应用中成功实现CDR技术、功能的电路结构;而在典型高速串行通信链路的概述中,又对数据是如何传输及如何从链路中重新捕获数据作分析;而在通用CDR拓扑中将讨论CDR的不同结构并分折数据链路发送端和接收端时钟基准振荡器的设计要领。

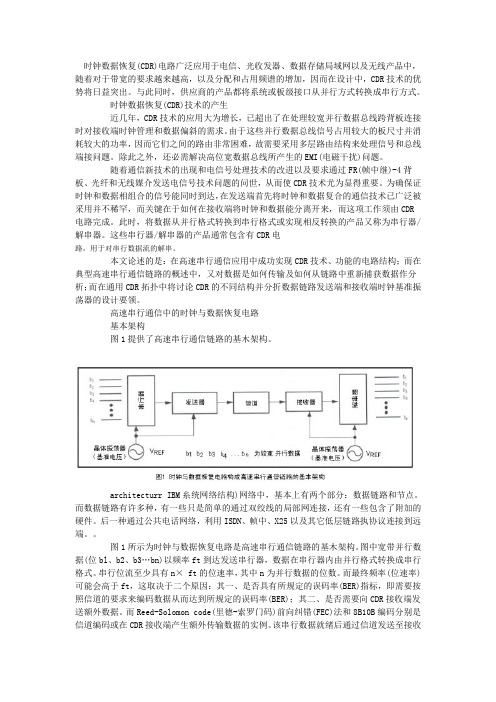

高速串行通信中的时钟与数据恢复电路基本架构图1提供了高速串行通信链路的基木架构。

architecturr IBM糸统网络结构)网络中,基本上有两个部分:数据链路和节点。

而数据链路有许多种,有一些只是简单的通过双绞线的局部网连接,还有一些包含了附加的硬件。

后一种通过公共电话网络,利用ISDN、帧中、X25以及其它低层链路执协议连接到远端。

时钟数据恢复(CDR)

时钟数据恢复(CDR)引言概述:时钟数据恢复(CDR)是一种电子设备中常见的技术,它的主要作用是将传输过程中的时钟信号从输入数据中恢复出来。

CDR技术在通信、计算机和数据存储等领域中起着重要的作用。

本文将从四个方面详细介绍CDR技术的原理、应用、优势和未来发展。

一、CDR技术的原理1.1 时钟信号的重要性:时钟信号在数字系统中起着同步和定时的作用,是数据传输的基础。

没有准确的时钟信号,数据传输可能会出现错误。

1.2 时钟数据恢复的需求:在长距离传输、高速传输和复杂信道环境中,时钟信号可能会受到噪声、失真和抖动等干扰,导致时钟信号的丢失或变形。

1.3 CDR技术的原理:CDR技术通过采样、检测和锁定的方式,从输入数据中恢复出准确的时钟信号。

具体而言,CDR技术会对输入数据进行采样,检测采样点的时钟相位误差,并通过反馈机制调整本地时钟信号,最终实现时钟数据的恢复。

二、CDR技术的应用2.1 通信领域:CDR技术在光纤通信和高速数据传输中广泛应用。

它可以恢复出光纤通信中的时钟信号,保证数据的传输质量和可靠性。

2.2 计算机领域:CDR技术在计算机内部的总线、接口和芯片中使用。

它可以恢复出高速总线和接口中的时钟信号,确保数据的同步和稳定传输。

2.3 数据存储领域:CDR技术在硬盘驱动器和固态硬盘中起着重要的作用。

它可以恢复出存储介质中的时钟信号,确保数据的读取和写入的准确性和稳定性。

三、CDR技术的优势3.1 自适应性:CDR技术具有自适应性,可以根据输入数据的特性和环境条件自动调整时钟恢复的参数,适应不同的传输场景。

3.2 高精度:CDR技术能够实现高精度的时钟恢复,可以达到纳秒级的时钟相位误差,确保数据传输的准确性和稳定性。

3.3 抗干扰能力:CDR技术具有较强的抗干扰能力,可以有效抑制噪声、失真和抖动等干扰信号,提高数据传输的可靠性和鲁棒性。

四、CDR技术的未来发展4.1 高速传输:随着数据传输速率的不断提高,CDR技术将面临更高的挑战。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Clock Recovery Primer, Part 1 PrimerPrimer/bertscope2Table of Contentsed?........................................3How.Does.Clock.Recovery.Work?. (3)PLL-Based Clock Recovery ..............................................4Generic Phased Lock Loop Block Diagram .......................4What it Does .....................................................................4How it Works ....................................................................4What Does a Measured Loop ResponseLook Like? (5)Examples (6)Example 1: Testing a 10 Gb/s Clock Recovery Circuit (6)Example 2: Behavior of a Clock Data Recovery (CDR)Circuit (8)Where.Does.Clock.Recovery.Appear.in..Measurements? (12)Loop Bandwidth Setting in Measurements (14)The.Effect.of.Peaking....................................................15The.Effect.of.Transition.Density.and.Anomalous.Clock.Recovery.Behavior.. (16)Pattern Effects ................................................................16Anomalous Locking .. (16)Where.to.Go.Next..........................................................17Acknowledgements.......................................................17References.. (18)/bertscope 3Clock Recovery Primer, Part 1AbstractClock recovery is a common part of many measure-ments, whether as part of the test setup or part of the device under test. We’re going to look at clock recovery from a practical point of view, with emphasis on how it affects measurements. This document closely mirrors the poster “The Anatomy of Clock Recovery, Part 1.”Why is Clock Recovery Used?Most gigabit communication systems are synchronous; that is, the data within them is timed against a common clock. High speed systems (such as serial buses and optical) usually send NRZ (Non-Return to Zero) data, coded to have the clock it is timed against embedded within it. Whether traveling across inches of circuit board, or across continents on optical fiber, the relationship between data and the clock it is timed against can become disturbed. Extracting clock directly from the data ensures that data regeneration at the receiver can be achieved correctly.Receivers typically improve the incoming data before passing it on. They do this by passing it through a decision circuit that retimes the data and squares up the pulses. This process isdependent upon a clock signal synchronous with the incoming data, hence the use of clock recovery inside the receiver. Timing variations such as jitter on the incoming data can be reduced or removed if the clock used for retiming moves in the same way at the same time.As we will see, in practice the operation is more complex than this, and the frequency of the incoming jitter is important.How Does Clock Recovery Work?There are many different architectures for clock recovery, and a large amount of literature describing the advantages and disadvantages of each. In measurement equipment, the most common type is based on a phase locked loop (PLL). We will look at this in more detail in a moment. Before we do, it is worth noting that other architectures have been used in measurement equipment in the past.Older sampling scope clock recovery modules were often feed-forward designs with fixed frequency filters switched in for each rate. Suitable band pass filters are difficult to make with narrow bands. They have also not been frequency agile, and will not track data with moving center frequencies, such as is found in spread spectrum clocking (SSC; see poster “Anatomy of Clock Recovery, Part 2”).Figure.1..If clock and data were to move in time by the same amount at the same time, a decision circuit could remove the effect of jitter.Primer/bertscope4PLL-Based Clock RecoveryClock recovery is usually applied to NRZ data. Unlike PLLs used in RF applications, data signals require modification to the PLL design. One challenge is the property of NRZ (Non-Return to Zero) data that there is no discrete spectral line at the data rate. This restricts the types of phase detector that can be employed in the PLL. Examples include Bang-Bang and Hogge designs.Generic Phased Lock Loop Block Diagram What it DoesA Voltage Controlled Oscillator (VCO) free-runs initially, near the data rate of interest.A portion of the VCO signal forms one input to a phase detector.The other input to the phase detector is the incoming data. The phase detector compares the phases of the two inputs and produces an output voltage related to the phase difference (the ‘Error Signal’ above).Usually this signal is filtered in some way before it becomes the frequency control voltage of the VCO.The error signal is a demodulated, high pass filtered equivalent of the jitter present on the input data.Many different circuits can be used for the Loop Filter for different applications.How it WorksThe aim of the recovery circuit is to derive a clock that is synchronous with the incoming data.Its ability to do this is dependent upon seeing transitions in the data.For data segments with runs of identical bits, the PLL must still stay locked.The loop gain, K, has the most significant effect on the loop bandwidth and speed. Any filtering within the loop filter typically has a secondary effect [1], p.21.The system transfer function (the normal loop response seen in literature, referred to as ‘H(s)’), performs a low pass filtering operation on the phase modulation of the input signal.The error response transfer function (referred to as ‘E(s)’) performs a high pass filtering function.The loop tracks input phase modulation within the loop bandwidth, and fails to track phase modulation outside the bandwidth.This gives the loop the ability to track low frequency jitter, but to ignore high frequency jitter outside the loop bandwidth of the PLL.Figure.2..NRZ spectrum showing one challenge for clock recovery – the lack of adiscrete spectral line at the bit rate.Figure.3..PLL Block Diagram./bertscope 5Clock Recovery Primer, Part 1What Does a Measured Loop Response Look Like?A measured loop response is shown in Figure 4.One measure of the jitter tracking characteristic of a PLL is the loop bandwidth (LBW). This is often measured as the point where the transfer function of (jitter out/jitter in) is –3 dB. This is not the only way that loops can be defined [1], pp. 17–18.A wide loop bandwidth sounds ideal. However, it is usually cost and technology dependent. Wide loop bandwidths contribute more noise/random jitter. A wide loop bandwidth improves jitter tolerance; a narrow loop bandwidthremoves more jitter from the recovered clock (beneficial to downstream synchronizers) but impairs jitter tolerance. Current loop bandwidths used in measurements are typically in the range from 1 to 10 MHz.Figure.4..A measured loop response showing a PLL tracking the input jitter (left side) and then failing to track the jitter (right side).Primer/bertscope6ExamplesWe are going to look at two examples of clock recovery measurements, one with a commercial clock recovery component (Section 4), the other with a commercial clock/data recovery chip (Section 5). In each case, the classical method of test is to use sinusoidal jitter (SJ) and to change modulation frequency. Here we will keep the jitter amplitude constant throughout.Example 1: Testing a 10 Gb/s Clock Recovery CircuitRecovered clock is derived from jittered dataRecovered clock tracks less and less jitter as the frequency of jitter on the data is increasedRecovered clock is compared against jittered data in the analyzerThe analyzer measures jitter relative to the clock trigger signalIn this way, we can measure the clock recovery error transfer functionWideband equipment, such as BERTs and oscilloscopes, has intrinsic jitter that masks the loop responses at low levels in measurements such as this. As we will see later, the portions of loop responses not visible here can still have significant effects, manifesting themselves as eye closure and bit errors in some situations.Figure.5..The effect of the intrinsic jitter of a wideband measuring instrument on loopmeasurements./bertscope 7Clock Recovery Primer, Part 1Figure.6..Deriving a clock trigger from data and using it to trigger a measurement. The response is sometimes called the ‘Observed Jitter Transfer Function.’Primer/bertscope8Example 2: Behavior of a Clock Data Recovery (CDR) CircuitA CDR recovers clock from incoming data, then uses the recovered clock as the reference to trigger a retiming flip-flop to clean up the incoming data. This measurement setup used a commercially available clock data recovery chip testedat 2.488 Gb/s, with a PRBS-7 pattern and 40% (0.4 UI) Sinusoidal Jitter signal of varying modulation frequency. The amplitude is constant; only the modulation frequency is varied, in the same way receiver clock recovery is traditionally tested. All analyzer measurements show data signal relative to the trigger.Figure.7..The chip being measured.Figure.8..The chip used for these measurements./bertscope 9Clock Recovery Primer, Part 1Figure.9.1.and.9.2..Two measurement configurations of the CDR chip. The measured responses are also shown in the graph of Figure 10.Primer/bertscope10Figure.9.3.and.9.4..Two further measurement configurations of the CDR chip. The measured responses are also shown in the graph of Figure 10./bertscope 11Clock Recovery Primer, Part 1Conclusions.for.Example.2Recovered clock jitter below the loop bandwidth tracks the input jitterRecovered clock jitter above the loop bandwidth is attenuated, so the recovered clock does not track high frequency jitterJitter of retimed data is dominated by the jitter of the retiming clockHigh frequency jitter on incoming data can be of sufficiently high amplitude to cause bit-detection errors, even though the retimed, regenerated data stream appears clean on an analyzer screenTriggering of test equipment plays a crucial role in the results obtainedFigure.10..Overlaid responses of the CDR chip measured as detailed in Figure 9.Primer/bertscope12Where Does Clock Recovery Appear in Measurements?Clock recovery can be part of the device under test, and also of the test setup. Typically, when it is part of the test setup, it is intended to emulate the behavior of a receiver, particularly in tracking low frequency jitter. Ideally, this means that only jitter beyond the clock recovery tracking range of a typical receiver is seen on the test equipment eye diagram.Figure.11..The figure shows where clock recovery can appear in a device under test, and test equipment used to characterize it./bertscope 13Clock Recovery Primer, Part 1Figure.12..Building on Figure 11, the table gives details of how clock recovery is used, and what can go wrong.Primer/bertscope14Loop Bandwidth Setting in MeasurementsLoop bandwidth can have a significant effect on the observed jitter in a measurement. Varying the loop bandwidth can give an indication of the jitter spectrum. The loop bandwidthschosen for testing could be very narrow (for example, to show all the jitter a transmitter under test is creating) or wide (for example, to show only the jitter that a transmitter produces that its intended system receiver is not able to filter out with its own PLL). Typically, it is the latter, and such a clock recovery is referred to as a “Golden PLL.” A system designer is mainly interested in jitter that is beyond the capabilities of the receiver to track.Some standards (like FB-DIMM) have a range of loopbandwidths specified. While test instruments should emulate the characteristics of the test device, a range in parameters could lead to unintended results.For transmitter testing, it might be desirable to have a high loop bandwidth to make the tested transmitter look as good as possible (the transmitter intrinsic jitter is largely tracked out, so it doesn’t appear in the measurement, making the transmitter look good).For receiver jitter tolerance, the stressed eye is often set up using jitter measured on an eye diagram. The aim might be to stress the eye with jitter beyond the effect of the receiver clock recovery’s ability to track it out. If the clock recovery used for stress calibration has a lower loop bandwidth than the receiver under test will, some jitter will be included in the eye measurement that will be tracked out by the receiver. This could make the composition of the finished stressed eye less demanding than it should be.ing the same jittered signal, eye diagrams measured against a recoveredclock with narrow and wide loop bandwidth settings.Figure.14..Transmitter testing and the effect of changing loop bandwidth.Figure.15..Receiver testing and the effect of changing loop bandwidth./bertscope 15Clock Recovery Primer, Part 1The Effect of PeakingPeaking is a region near the loop bandwidth where the jitter out of a clock recovery device can be greater than the jitter input. Standards often restrict the amount of allowed peaking. The reasons why this is done are evident from the following measurements.An instrument-grade clock recovery with configurable slope and peaking was used for this measurement Loop bandwidth was set to 1 MHzThe stimulus was a fixed 400 kHz sinusoidal jitter input signal to the clock recoveryThe loop was set to 0 dB peaking (red measured response) and +3 dB peaking (green measured response).The eye diagram from the green response shows jitter gain — more jitter out of the device than was present on the input.3 dB equates to a factor of 1.41.Confirms that jitter gain is indeed +3 dB: 35 ps input x 1.41 = 49 ps jitter output.Many standards restrict the amount of peaking allowed (see table on “Anatomy of Clock Recovery, Part 2” poster). Jitter gain, particularly in a repeatered system, is highly undesirable.Peaking increases the noise/random jitter.Figure.16..Measurement of a clock recovery instrument using the same input signal containing jitter. Varying the peaking can increase the jitter beyond the amount presenton the input.Primer/bertscope16The Effect of Transition Density and Anomalous Clock Recovery BehaviorWe will look at two loop effects; the first relating the transition density of different patterns and how this affects clock recovery; the second, how locking can go wrong.Pattern EffectsThe pattern “101010…” has a transition density of 100% (every bit has a transition). PRBS patterns have an average transition density identical to a "1100" pattern — i.e., 50%. Other patterns may have a lower transition density, or one that changes in certain sections of the same pattern (such as some sections of long PRBS patterns).The number of transitions controls the amount of energy going into the clock recovery loop. The energy in the loop affects the loop parameters, including loop gain and loop bandwidth. Therefore changing patterns can alter the loop behavior.Halving the transition density can have the effect ofapproximately halving the loop bandwidth for most loop designs. Some instrument grade clock recovery solutions calibrate loop bandwidth based on the measured transition density of the incoming data. Care must be taken — some standards specify loop bandwidth at a particular transition density, and assume that the loop bandwidth will be different for measurements using the required test patterns.Anomalous LockingSidelocking- Signals with periodic modulation produce discrete spectral lines - Narrow band PLL can lock on to any sufficiently high amplitude discrete spectral line, whether the carrier or not - Called ‘sidelocking’- Short PRBS patterns have fewer, higher energy spectral lines that are widely spaced, so can be more problematic than long PRBS patterns Harmonic Locking- Data, like square wave modulation, has harmonics that can provide opportunities to lock at multiples of the desired frequency - This can also happen with some designs ofphase detectors for subharmonics, and fractional subharmonics, particularly for long runs of ones or zeros [1], p. 341These are some reasons why instrument clock recovery solutions usually require an initial frequency to be accurately established prior to acquisition.Figure.17..Conceptual view of sidelocking.Figure.18..Conceptual view of harmonic locking./bertscope 17Clock Recovery Primer, Part 1Where to Go NextIn the same way that the second “Anatomy of Clock Recovery” poster tackles more complex topics, there is a companion second primer [16], “Anatomy of Clock Recovery, Part 2,” which can be downloaded from the website.In this companion paper, the following topics are discussed: Survey of clock recovery used in various standards Types and orders Spread spectrum clocking Clock recovery and stress testingThe effect of trigger delay in measurements Distributed clock schemes Clock domainsAcknowledgementsConsiderable help has been generously given by the following people:Floyd M. GardnerEric Kvamme, Hollis Poche, Maxtor Corporation Harvey Newman, Infineon Technologies Stretch Camnitz, Avago Technologies Mark Marlett, LSI LogicRansom Stephens, Teraspeed Consulting John Calvin, TektronixGerry Talbot, Advanced Micro DevicesPrimer/bertscope18References[1] Gardner, Floyd M. 2005, 3rd Ed. Phaselock Techniques.New Jersey, John Wiley & Sons Inc. The original and definitive textbook on PLLs. Revised edition has much improved introductory chapters.[2] Best, Roland E. 2003, 5th Ed. Phase-Locked Loops,Design, Simulation and Applications. New York,McGraw-Hill. Includes instructive PLL simulation software on CD-ROM.[3] Kroupa, Venceslav F . 2003. Phase Lock Loops andFrequency Synthesis. John Wiley & Sons, Ltd., United Kingdom.[4] 10 Gigabit Ethernet and XAUI: search on “802.3aeTM”Governing body (and owner of trademark) [5] Fibre Channel information: Fibre Channel IndustryAssociation, /[6] OIF CEI standard: /public/impagreements.html [7] Serial ATA standard: [8] SONET information: GR-253-CORE, SynchronousOptical Network (SONET) Transport Systems: Common Generic Criteria, /[9] SDH information: http://www.itu.int/ITU-T/, G.xxxseries of documents, for example G.957 was anoriginal defining document for optical interfaces, G.958 described jitter.[10] XFP and XFI information: [11] Fully Buffered DIMM standard, JEDEC Study Group 45: [12] PCI Express ™ standard: /specifications/pciexpress/[13] Serial Attached SCSI information: SCSI TradeAssociation, [14] PCI Express ™ Jitter Modeling Whitepaper, Revision1.0RD, July 14, 2004, sections 3 & 4: /specifications/pciexpress/technical_library/[15] MJSQ – “Methodologies for Jitter and Signal QualitySpecification” is a document written as part of the INCITS project T11.2. /index.htm [16] ‘The Anatomy of Clock Recovery, Part 2’,Clock Recovery Primer, Part 1/bertscope19Contact.Tektronix:ASEAN./.Australasia..(65) 6356 3900Austria*..00800 2255 4835 Balkans,.Israel,.South.Africa.and.other.ISE.Countries.+41 52 675 3777Belgium*..00800 2255 4835Brazil..+55 (11) 3759 7600Canada..1 (800) 833-9200 Central.East.Europe,.Ukraine.and.the.Baltics..+41 52 675 3777Central.Europe.&.Greece..+41 52 675 3777Denmark..+45 80 88 1401Finland..+41 52 675 3777France*..00800 2255 4835Germany*..00800 2255 4835Hong.Kong..400-820-5835India..000-800-650-1835Italy*..00800 2255 4835Japan..81 (3) 6714-3010Luxembourg..+41 52 675 3777 Mexico,.Central/South.America.&.Caribbean..52 (55) 56 04 50 90Middle.East,.Asia.and.North.Africa..+41 52 675 3777herlands*..00800 2255 4835Norway..800 16098People’s.Republic.of.China..400-820-5835Poland..+41 52 675 3777Portugal..80 08 12370Republic.of.Korea..001-800-8255-2835Russia.&.CIS..+7 (495) 7484900South.Africa. +27 11 206 8360Spain*..00800 2255 4835Sweden*..00800 2255 4835Switzerland*..00800 2255 4835Taiwan..886 (2) 2722-9622.United.Kingdom.&.Ireland*..00800 2255 4835USA..1 (800) 833-9200 *.If.the.European.phone.number.above.is.not.accessible,.please.call.+41.52.675.3777Contact List Updated 25 May 2010. rmationTektronix maintains a comprehensive, constantly expanding collection of application notes, technical briefs and other resources to help engineers working on the cutting edge of technology. Please visit Copyright © 2010, Tektronix. All rights reserved. Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supersedes that in all previously published material. Specification and price change privileges reserved. TEKTRONIX and TEK are registered trademarks of Tektronix, Inc. All other trade names referenced are the service marks, trademarks or registered trademarks of their respective companies.09/10 EA/WWW 65W-26023-0。