QuickEDA 引脚分配

EDA定义引脚_引脚分配

EDA定义引脚_引脚分配********************************** clock/pll *****************************************set_location_assignment PIN_AF14 -to clk1set_location_assignment PIN_P2 -to clk2set_location_assignment PIN_P26 -to clk3set_location_assignment PIN_D13 -to clk4************************************** rst *******************************************set_location_assignment PIN_L20 -to rst******************************** 4bits button ****************************************set_location_assignment PIN_T21 -to button[0]set_location_assignment PIN_R24 -to button[1]set_location_assignment PIN_U22 -to button[2]set_location_assignment PIN_T22 -to button[3]************************************* SDRAM ******************************************set_location_assignment PIN_AE15 -to sdram_d[0]set_location_assignment PIN_AE16 -to sdram_d[1]set_location_assignment PIN_AF17 -to sdram_d[2]set_location_assignment PIN_AE17 -to sdram_d[3]set_location_assignment PIN_AA25 -to sdram_d[5] set_location_assignment PIN_AA26 -to sdram_d[6] set_location_assignment PIN_Y25 -to sdram_d[7]set_location_assignment PIN_AF22 -to sdram_d[8] set_location_assignment PIN_AE21 -to sdram_d[9] set_location_assignment PIN_AF21 -to sdram_d[10] set_location_assignment PIN_AE20 -to sdram_d[11] set_location_assignment PIN_AF20 -to sdram_d[12] set_location_assignment PIN_AE19 -to sdram_d[13] set_location_assignment PIN_AF19 -to sdram_d[14] set_location_assignment PIN_AE18 -to sdram_d[15]set_location_assignment PIN_R25 -to sdram_a[0]set_location_assignment PIN_P24 -to sdram_a[1]set_location_assignment PIN_M25 -to sdram_a[2] set_location_assignment PIN_L25 -to sdram_a[3]set_location_assignment PIN_AB26 -to sdram_a[4] set_location_assignment PIN_AB25 -to sdram_a[5] set_location_assignment PIN_AC26 -to sdram_a[6] set_location_assignment PIN_AC25 -to sdram_a[7] set_location_assignment PIN_AD25 -to sdram_a[8] set_location_assignment PIN_AE25 -to sdram_a[9] set_location_assignment PIN_T25 -to sdram_a[10] set_location_assignment PIN_AE24 -to sdram_a[11] set_location_assignment PIN_AE23 -to sdram_a[12]set_location_assignment PIN_Y26 -to sdram_dqm[0] set_location_assignment PIN_AE22 -to sdram_dqm[1]set_location_assignment PIN_U26 -to sdram_ba[1]set_location_assignment PIN_V26 -to sdram_cs_nset_location_assignment PIN_V25 -to sdram_ras_nset_location_assignment PIN_W26 -to sdram_cas_nset_location_assignment PIN_W25 -to sdram_we_nset_location_assignment PIN_AF23 -to sdram_ckeset_location_assignment PIN_V21 -to sdram_clk************************************* FLASH ******************************************set_location_assignment PIN_D7 -to flash_a[0]set_location_assignment PIN_K9 -to flash_a[1]set_location_assignment PIN_K6 -to flash_a[2]set_location_assignment PIN_K5 -to flash_a[3]set_location_assignment PIN_J6 -to flash_a[4]set_location_assignment PIN_J5 -to flash_a[5]set_location_assignment PIN_J1 -to flash_a[6]set_location_assignment PIN_J2 -to flash_a[7]set_location_assignment PIN_H1 -to flash_a[8]set_location_assignment PIN_H2 -to flash_a[9]set_location_assignment PIN_G1 -to flash_a[10]set_location_assignment PIN_G2 -to flash_a[11]set_location_assignment PIN_E1 -to flash_a[12]set_location_assignment PIN_E2 -to flash_a[13]set_location_assignment PIN_D1 -to flash_a[14]set_location_assignment PIN_M4 -to flash_a[15]set_location_assignment PIN_L7 -to flash_a[17]set_location_assignment PIN_K7 -to flash_a[18]set_location_assignment PIN_J7 -to flash_a[19]set_location_assignment PIN_H6 -to flash_a[20]set_location_assignment PIN_G5 -to flash_a[21]set_location_assignment PIN_F6 -to flash_a[22]set_location_assignment PIN_C6 -to flash_a[23]set_location_assignment PIN_C7 -to flash_d[0]set_location_assignment PIN_C8 -to flash_d[1]set_location_assignment PIN_D9 -to flash_d[2]set_location_assignment PIN_C9 -to flash_d[3]set_location_assignment PIN_D10 -to flash_d[4]set_location_assignment PIN_C10 -to flash_d[5]set_location_assignment PIN_D11 -to flash_d[6]set_location_assignment PIN_B2 -to flash_d[7]set_location_assignment PIN_F2 -to flash_select_nset_location_assignment PIN_C2 -to flash_read_nset_location_assignment PIN_D2 -to flash_write_n************************************* SRAM *******************************************set_location_assignment PIN_V1 -to sram_a[0]set_location_assignment PIN_V2 -to sram_a[1]set_location_assignment PIN_U2 -to sram_a[2]set_location_assignment PIN_U1 -to sram_a[3]set_location_assignment PIN_T2 -to sram_a[4]set_location_assignment PIN_AB2 -to sram_a[6] set_location_assignment PIN_AC1 -to sram_a[7] set_location_assignment PIN_AC2 -to sram_a[8] set_location_assignment PIN_AD2 -to sram_a[9] set_location_assignment PIN_AF13 -to sram_a[10] set_location_assignment PIN_AE13 -to sram_a[11] set_location_assignment PIN_AE12 -to sram_a[12] set_location_assignment PIN_AE11 -to sram_a[13] set_location_assignment PIN_AF10 -to sram_a[14] set_location_assignment PIN_AE6 -to sram_a[15] set_location_assignment PIN_AF6 -to sram_a[16] set_location_assignment PIN_AE7 -to sram_a[17]set_location_assignment PIN_M2 -to sram_d[0] set_location_assignment PIN_L2 -to sram_d[1] set_location_assignment PIN_K1 -to sram_d[2] set_location_assignment PIN_K2 -to sram_d[3] set_location_assignment PIN_W1 -to sram_d[4] set_location_assignment PIN_W2 -to sram_d[5] set_location_assignment PIN_Y1 -to sram_d[6] set_location_assignment PIN_AA1 -to sram_d[7] set_location_assignment PIN_AF9 -to sram_d[8] set_location_assignment PIN_AE9 -to sram_d[9] set_location_assignment PIN_AF8 -to sram_d[10] set_location_assignment PIN_AE8 -to sram_d[11] set_location_assignment PIN_AF7 -to sram_d[12] set_location_assignment PIN_AE2 -to sram_d[13] set_location_assignment PIN_AE3 -to sram_d[14]set_location_assignment PIN_AF4 -to sram_lb_nset_location_assignment PIN_AE5 -to sram_ub_nset_location_assignment PIN_AA2 -to sram_we_nset_location_assignment PIN_AF5 -to sram_oe_nset_location_assignment PIN_R2 -to sram_ce_n********************************* AC97 *******************************************set_location_assignment PIN_V23 -to ac97_bit_clkset_location_assignment PIN_T23 -to ac97_sdata_iset_location_assignment PIN_U24 -to ac97_irqset_location_assignment PIN_Y21 -to ac97_rst_nset_location_assignment PIN_W24 -to ac97_sdata_oset_location_assignment PIN_AC23 -to ac97_sync********************************* SD *******************************************set_location_assignment PIN_C4 -to sd_csset_location_assignment PIN_D5 -to sd_cmdset_location_assignment PIN_J10 -to sd_datset_location_assignment PIN_D6 -to sd_clk********************************* 16207LCD *******************************************set_location_assignment PIN_AA16 -to lcd_d[1]set_location_assignment PIN_AA17 -to lcd_d[2]set_location_assignment PIN_AB18 -to lcd_d[3]set_location_assignment PIN_AA18 -to lcd_d[4]set_location_assignment PIN_AA20 -to lcd_d[5]set_location_assignment PIN_AB20 -to lcd_d[6]set_location_assignment PIN_AB21 -to lcd_d[7]set_location_assignment PIN_Y12 -to lcd_rsset_location_assignment PIN_W11 -to lcd_rwset_location_assignment PIN_Y15 -to lcd_e*********************************** DM9000 *******************************************set_location_assignment PIN_A21 -to dm9k_d[0]set_location_assignment PIN_B20 -to dm9k_d[1]set_location_assignment PIN_A20 -to dm9k_d[2]set_location_assignment PIN_B19 -to dm9k_d[3]set_location_assignment PIN_A19 -to dm9k_d[4]set_location_assignment PIN_B18 -to dm9k_d[5]set_location_assignment PIN_A18 -to dm9k_d[6]set_location_assignment PIN_B17 -to dm9k_d[7]set_location_assignment PIN_C25 -to dm9k_d[8]set_location_assignment PIN_B25 -to dm9k_d[9]set_location_assignment PIN_B24 -to dm9k_d[10]set_location_assignment PIN_B23 -to dm9k_d[11]set_location_assignment PIN_A23 -to dm9k_d[12]set_location_assignment PIN_B22 -to dm9k_d[13]set_location_assignment PIN_A22 -to dm9k_d[14]set_location_assignment PIN_F25 -to dm9k_cs_n set_location_assignment PIN_F26 -to dm9k_rst_n set_location_assignment PIN_E25 -to dm9k_rd_n set_location_assignment PIN_E26 -to dm9k_wr_n set_location_assignment PIN_D25 -to dm9k_cmd set_location_assignment PIN_D26 -to dm9k_int********************************* VGA30 bits ******************************************set_location_assignment PIN_E15 -to vga_r[9]set_location_assignment PIN_F13 -to vga_r[8]set_location_assignment PIN_K26 -to vga_r[7]set_location_assignment PIN_K25 -to vga_r[6]set_location_assignment PIN_J26 -to vga_r[5]set_location_assignment PIN_J25 -to vga_r[4]set_location_assignment PIN_H26 -to vga_r[3]set_location_assignment PIN_H25 -to vga_r[2]set_location_assignment PIN_G26 -to vga_r[1]set_location_assignment PIN_G25 -to vga_r[0]set_location_assignment PIN_G15 -to vga_b[9] set_location_assignment PIN_G16 -to vga_b[8] set_location_assignment PIN_G17 -to vga_b[7] set_location_assignment PIN_G18 -to vga_b[6] set_location_assignment PIN_H16 -to vga_b[5] set_location_assignment PIN_F20 -to vga_b[4]set_location_assignment PIN_G21 -to vga_b[2]set_location_assignment PIN_J18 -to vga_b[1]set_location_assignment PIN_K19 -to vga_b[0]set_location_assignment PIN_F16 -to vga_g[9]set_location_assignment PIN_F15 -to vga_g[8]set_location_assignment PIN_T24 -to vga_g[7]set_location_assignment PIN_P23 -to vga_g[6]set_location_assignment PIN_M22 -to vga_g[5]set_location_assignment PIN_L21 -to vga_g[4]set_location_assignment PIN_K22 -to vga_g[3]set_location_assignment PIN_J22 -to vga_g[2]set_location_assignment PIN_H23 -to vga_g[1]set_location_assignment PIN_H24 -to vga_g[0]set_location_assignment PIN_C12 -to vga_hsyncset_location_assignment PIN_F12 -to vga_vsyncset_location_assignment PIN_F17 -to vga_blankset_location_assignment PIN_H17 -to vga_syncset_location_assignment PIN_F21 -to vga_clk****************************** 外接LCD *****************************************set_location_assignment PIN_G22 -to vga1_r[7]set_location_assignment PIN_J17 -to vga1_r[6]set_location_assignment PIN_J21 -to vga1_r[5]set_location_assignment PIN_H21 -to vga1_r[4]set_location_assignment PIN_D18 -to vga1_g[7]set_location_assignment PIN_C17 -to vga1_g[6]set_location_assignment PIN_C19 -to vga1_g[5]set_location_assignment PIN_E18 -to vga1_g[4]set_location_assignment PIN_D20 -to vga1_g[3]set_location_assignment PIN_D19 -to vga1_g[2]set_location_assignment PIN_C21 -to vga1_b[7]set_location_assignment PIN_L24 -to vga1_b[6]set_location_assignment PIN_L23 -to vga1_b[5]set_location_assignment PIN_M21 -to vga1_b[4]set_location_assignment PIN_K21 -to vga1_b[3]set_location_assignment PIN_D16 -to vga1_blankset_location_assignment PIN_C15 -to vga1_vsyncset_location_assignment PIN_C16 -to vga1_hsyncset_location_assignment PIN_E5 -to vga1_clk********************************** USB ********************************************set_location_assignment PIN_H10 -to usb_d[0]set_location_assignment PIN_G9 -to usb_d[1]set_location_assignment PIN_B3 -to usb_d[2]set_location_assignment PIN_B4 -to usb_d[3]set_location_assignment PIN_A4 -to usb_d[4]set_location_assignment PIN_B5 -to usb_d[5]set_location_assignment PIN_A5 -to usb_d[6]set_location_assignment PIN_B6 -to usb_d[7]set_location_assignment PIN_A6 -to usb_d[8]set_location_assignment PIN_B7 -to usb_d[9]set_location_assignment PIN_A7 -to usb_d[10]set_location_assignment PIN_B8 -to usb_d[11]set_location_assignment PIN_A8 -to usb_d[12]set_location_assignment PIN_B9 -to usb_d[13]set_location_assignment PIN_A9 -to usb_d[14]set_location_assignment PIN_B10 -to usb_d[15]set_location_assignment PIN_H11 -to usb_a[0]set_location_assignment PIN_E10 -to usb_a[1]set_location_assignment PIN_A10 -to usb_cs_nset_location_assignment PIN_B11 -to usb_read_nset_location_assignment PIN_B12 -to usb_write_nset_location_assignment PIN_B15 -to usb_intset_location_assignment PIN_A17 -to usb_rst_n********************************** UART *******************************************set_location_assignment PIN_C3 -to uart_txdset_location_assignment PIN_F4 -to uart_rxd*************************** PS/2 keyboard and mouse ***********************************set_location_assignment PIN_F14 -to ps2_keyboard_dataset_location_assignment PIN_E12 -to ps2_keyboard_clkset_location_assignment PIN_D15 -to ps2_mouse_dataset_location_assignment PIN_D14 -to ps2_mouse_clk********************************* 8位拨码开关****************************************set_location_assignment PIN_Y22 -to sw[0]set_location_assignment PIN_W21 -to sw[1]set_location_assignment PIN_V22 -to sw[2]set_location_assignment PIN_AD23 -to sw[3]set_location_assignment PIN_AC22 -to sw[4]set_location_assignment PIN_AD22 -to sw[5]set_location_assignment PIN_AC21 -to sw[6]set_location_assignment PIN_AD21 -to sw[7]*********************************** 8位LED *******************************************set_location_assignment PIN_AD16 -to led[0]set_location_assignment PIN_AC16 -to led[1]set_location_assignment PIN_AC18 -to led[2]set_location_assignment PIN_AD19 -to led[3]set_location_assignment PIN_AD17 -to led[4]set_location_assignment PIN_AC17 -to led[5]set_location_assignment PIN_AC20 -to led[6]set_location_assignment PIN_AC19 -to led[7]*************************** 4个8位静态数码管*****************************************set_location_assignment PIN_T4 -to seg1[7]set_location_assignment PIN_U3 -to seg1[6]set_location_assignment PIN_U4 -to seg1[5]set_location_assignment PIN_V3 -to seg1[4]set_location_assignment PIN_Y3 -to seg1[3]set_location_assignment PIN_W4 -to seg1[2] set_location_assignment PIN_W3 -to seg1[1] set_location_assignment PIN_V4 -to seg1[0]set_location_assignment PIN_AA4 -to seg2[7] set_location_assignment PIN_AA3 -to seg2[6] set_location_assignment PIN_H8 -to seg2[5]set_location_assignment PIN_U5 -to seg2[4]set_location_assignment PIN_AB4 -to seg2[3] set_location_assignment PIN_AB3 -to seg2[2] set_location_assignment PIN_T6 -to seg2[1]set_location_assignment PIN_W6 -to seg2[0]set_location_assignment PIN_J8 -to seg3[7]set_location_assignment PIN_J9 -to seg3[6]set_location_assignment PIN_U7 -to seg3[5]set_location_assignment PIN_T7 -to seg3[4]set_location_assignment PIN_U6 -to seg3[3]set_location_assignment PIN_V5 -to seg3[2]set_location_assignment PIN_V6 -to seg3[1]set_location_assignment PIN_V7 -to seg3[0]set_location_assignment PIN_AA6 -to seg4[7]set_location_assignment PIN_W10 -to seg4[6]set_location_assignment PIN_Y5 -to seg4[5]set_location_assignment PIN_AD5 -to seg4[4]set_location_assignment PIN_AC9 -to seg4[3]set_location_assignment PIN_AC8 -to seg4[2]set_location_assignment PIN_AC7 -to seg4[1]set_location_assignment PIN_AC6 -to seg4[0]****************************** 外扩接口*****************************************set_location_assignment PIN_AA7 -to ext_pio16[0]set_location_assignment PIN_AC10 -to ext_pio16[1]set_location_assignment PIN_AC11 -to ext_pio16[2]set_location_assignment PIN_AA13 -to ext_pio16[3]set_location_assignment PIN_AA14 -to ext_pio16[4]set_location_assignment PIN_AC14 -to ext_pio16[5]set_location_assignment PIN_AB15 -to ext_pio16[6]set_location_assignment PIN_AC15 -to ext_pio16[7]set_location_assignment PIN_V10 -to ext_pio16[8]set_location_assignment PIN_Y11 -to ext_pio16[9]set_location_assignment PIN_U17 -to ext_pio16[10]set_location_assignment PIN_V17 -to ext_pio16[11]set_location_assignment PIN_W16 -to ext_pio16[12]set_location_assignment PIN_Y16 -to ext_pio16[13]set_location_assignment PIN_W17 -to ext_pio16[14]set_location_assignment PIN_Y18 -to ext_pio16[15]set_location_assignment PIN_W19 -to ext_pio1set_location_assignment PIN_AC3 -to ext_pio10[0] set_location_assignment PIN_V9 -to ext_pio10[1] set_location_assignment PIN_W8 -to ext_pio10[2] set_location_assignment PIN_Y10 -to ext_pio10[3] set_location_assignment PIN_AA9 -to ext_pio10[4] set_location_assignment PIN_AA10 -to ext_pio10[5] set_location_assignment PIN_AB10 -to ext_pio10[6] set_location_assignment PIN_AA11 -to ext_pio10[7] set_location_assignment PIN_AA12 -to ext_pio10[8] set_location_assignment PIN_AB12 -to ext_pio10[9]。

英飞凌16_32位单片机一级JTAG连接引脚配置

3

D1

O

TMS

1

16

Init

O

4

D2

O

TCK

11

17

Select O VPP Mon

5

D3

O

TRST

9

18

GND SH

GND

4,6,12

6

D4

O

BRKIN

13

19

GND SH

GND

4,6,12

7

D5

O

RESET

8

20

GND SH

GND

4,6,12

8

D6

O OCDSE1)

14

21

GND SH

GND

4,6,12

3

V2.2.1, 2003-07

AP24001 OCDS Level1 JTAG Connector

The Connector Layout

2.3

Signal Description

The following are the Infineon JTAG connector signals.

Note that directions are indicated as follows:

1) This signal is not available on each Microcontroller implementation. This signal must be forced to a low level from the Trace Hardware (Emulator). If the Microcontroller derivative has no corresponding signal, it should be left unconnected in the target hardware.

FPGA(XC5V)引脚分配及功能

在我们“动态频谱资源共享宽带无线通信系统”项目中,使用的FPGA 芯片是Xilinx 公司的XC5VSX95T-FF1136C ,该芯片是Virtex-5 SXT 系列的一款芯片,FF 代表芯片的封装形式是F lip-chip F ine-pitch BGA (引脚之间的间距是1.00mm),1136表示该芯片有1136个引脚。

芯片大小是35*35(mm 2),芯片引脚分布框图如图1所示。

图1 XC5VSX95T-FF1136C 的引脚分布图从图1我们可知,芯片的引脚由34行和34列组成,34*34=1156,但是有20个行列交叉点没有作为引脚(比如A1、AP4),所以该芯片总的引脚数为1156-20=1136。

GPIO(640)在所有引脚中数目最多的是GPIO引脚,总共有640个,由于GPIO引脚采用差分形式传输信号,所以最多可以同时传输320个不同的输入输出信号。

图1中白色圆圈表示的就是GPIO引脚(比如G5、AC8)。

有些GPIO引脚是多功能引脚,也就是说这些引脚除了可以作为数据输入输出,还可以作为其他用途,比如可以在SelectMAP模式配置为数据输入引脚(D27)的G22,可以作为外部门限电压引脚(VREF)的A28。

640个GPIO引脚被分为18组(BANK),其中BANK1、BANK2、BANK3、BANK4为20个引脚,即20*4=80,另外BANK5、BANK6、BANK11、BANK12、BANK13、BANK15、BANK17、BANK18、BANK19、BANK20、BANK21、BANK22、BANK23、BANK25为40个引脚,即40*14=560。

GPIO的分组如图2所示。

图2 XC5VSX95T-FF1136C的GPIO引脚分组图BANK0(27)此外,还有一个分组叫BANK0,该分组是专用配置分组(Dedicated Configuration Bank)。

该分组有27个引脚,其中两个保留引脚(RSVD),6个引脚用于Dedicated System Monitor,剩余19个引脚用于其他专用配置。

EDA用户使用手册及引脚

EDA/SOPC系统开发平台用户使用手册北京百科融创教学仪器设备有限公司目录第一章综述 (3)第二章系统模块 (7)系统组成 (7)模块介绍 (9)使用注意事项: (35)SOPC-NIOSII EDA/SOPC系统开发平台说明 (36)第一章综述SOPC-NIOSII EDA/SOPC 实验开发系统是根据现代电子发展的方向,集EDA 和SOPC 系统开发为一体的综合性实验开发系统,除了满足高校专、本科生和研究生的SOPC 教学实验开发之外,也是电子设计和电子项目开发的理想工具。

整个开发系统由核心板SOPC-NiosII-EP2C35、系统板和扩展板构成,根据用户不同的需求配置成不同的开发系统。

SOPC-NiosII-EP2C35 开发板为基于Altera Cyclone II 器件的嵌入式系统开发提供了一个很好的硬件平台,它可以为开发人员提供以下资源:拥有33216 个逻辑单元和483840 bits片上存储单元Cyclone II EP2C35F672C8 FPGA16 Mbits 的EPCS16 配置芯片1 Mbytes SRAM32 Mbytes SDRAM8 Mbytes NOR Flash ROM64 Mbytes NAND Flash ROMRS-232 DB9 串行接口设备接口10BASE-T J45 接口多路音频CODEC 接口4 个用户自定义按键4 个用户自定义LED1 个七段码LED标准AS 编程接口和JTAG 调试接口50MHz 高精度时钟源两个高密度扩展接口(可与配套实验箱连接)两个标准2.54mm 扩展接口,供用户自由扩展系统上电复位电路支持+5V 直接输入,板上电源管理模块SOPC-NiosII-EP2C35开发板是在经过长期用户需求考察后,结合目前市面上以及实际应用需要,同时兼顾入门学生以及资深开发工程师的应用需求而研发的。

就资源而言,它已经可以组成一个高性能的嵌入式系统,可以运行目前流行的RTOS,如uC/OS、uClinux 等。

FPGA引脚分配方法

第二种:建立TCL文件进行管脚分配。

这种方法比较灵活,是比较常用的。

这种方法具有分配灵活,方便快捷,可重用性等多方面优点。

方法如下:选择Projects菜单项,并选择Generate tcl file for project选项,系统会为你自动生成相应文件,然后你只要向其中添加你的分配内容就可以了。

还有一种方法就是直接用new ,新建一个TCL文件即可,具体不再细讲。

下面是我分配的内容一部分,可供大家参考。

set_global_assignment -name FAMILY Cycloneset_global_assignment -name DEVICE EP1C3T144C8set_global_assignment -name ORIGINAL_QUARTUS_VERSION 8.0 set_global_assignment -name PROJECT_CREATION_TIME_DATE "19:14:58 JANUARY 06, 2009"set_global_assignment -name LAST_QUARTUS_VERSION 8.0set_global_assignment -nameUSE_GENERATED_PHYSICAL_CONSTRAINTS OFF -section_ideda_palaceset_global_assignment -name DEVICE_FILTER_PACKAGE "ANY QFP" set_global_assignment -name LL_ROOT_REGION ON -section_id "Root Region"set_global_assignment -name LL_MEMBER_STATE LOCKED-section_id "Root Region"set_global_assignment -name DEVICE_FILTER_PIN_COUNT 144 set_global_assignment -name DEVICE_FILTER_SPEED_GRADE 8 set_global_assignment -name FITTER_EFFORT "STANDARD FIT" set_global_assignment -name BDF_FILE topDesign.bdfset_global_assignment -name QIP_FILE nios.qipset_global_assignment -name QIP_FILE altpll0.qipset_global_assignment -name USE_CONFIGURATION_DEVICE ON set_global_assignment -name STRATIX_DEVICE_IO_STANDARD "3.3-V LVTTL"set_global_assignment -name PARTITION_NETLIST_TYPE SOURCE -section_id Topset_global_assignment -name PARTITION_COLOR 14622752-section_id Topset_location_assignment PIN_72 -to addr[7]set_location_assignment PIN_69 -to addr[6]set_location_assignment PIN_70 -to addr[5]set_location_assignment PIN_67 -to addr[4]set_location_assignment PIN_68 -to addr[3]set_location_assignment PIN_42 -to addr[2]set_location_assignment PIN_39 -to addr[1]set_location_assignment PIN_40 -to addr[0]set_location_assignment PIN_48 -to data[15]set_location_assignment PIN_47 -to data[14]set_location_assignment PIN_50 -to data[13]set_location_assignment PIN_49 -to data[12]set_location_assignment PIN_56 -to data[11]set_location_assignment PIN_55 -to data[10]set_location_assignment PIN_58 -to data[9]set_location_assignment PIN_57 -to data[8]set_location_assignment PIN_61 -to data[7]set_location_assignment PIN_62 -to data[6]set_location_assignment PIN_59 -to data[5]set_location_assignment PIN_60 -to data[4]set_location_assignment PIN_53 -to data[3]set_location_assignment PIN_54 -to data[2]set_location_assignment PIN_51 -to data[1]set_location_assignment PIN_52 -to data[0]set_location_assignment PIN_16 -to clkset_location_assignment PIN_38 -to csset_location_assignment PIN_141 -to led[3]set_location_assignment PIN_142 -to led[2]set_location_assignment PIN_143 -to led[1]set_location_assignment PIN_144 -to led[0]set_location_assignment PIN_33 -to reset_nset_location_assignment PIN_41 -to rdset_location_assignment PIN_71 -to wrset_location_assignment PIN_105 -to mosiset_location_assignment PIN_107 -to sclkset_location_assignment PIN_106 -to ssset_location_assignment PIN_73 -to motor[0]set_location_assignment PIN_74 -to motor[1]set_location_assignment PIN_75 -to motor[2]set_location_assignment PIN_76 -to motor[3]set_instance_assignment -name PARTITION_HIERARCHY root_partition -to | -section_id Top# Commit assignmentsexport_assignmentsFPGA 点滴(2008-09-30 09:44:45)转载标签:杂谈以此记录心得以及重要的知识点。

FPGA的配置引脚说明

FPGA是基于SRAM编程的,编程信息在系统掉电时会丢失,每次上电时,都需要从器件外部的FLASH或EEPROM中存储的编程数据重现写入内部的SRAM中。

FPGA在线加载需要有CPU的帮助,并且在加载前CPU已经启动并工作。

FPGA的加载模式主要有以下几种:1).PS模式(Passive Serial Configuration Mode),即被动串行加载模式。

PS模式适合于逻辑规模小,对加载速度要求不高的FPGA加载场合。

在此模式下,加载所需的配置时钟信号CCLK由FPGA外部时钟源或外部控制信号提供。

另外,PS加载模式需要外部微控制器的支持。

2).AS模式(Active Serial Configuration Mode),即主动串行加载模式。

在AS模式下,FPGA主动从外部存储设备中读取逻辑信息来为自己进行配置,此模式的配置时钟信号CCLK由FPGA内部提供。

3).PP模式(Passive Parallel Configuration Mode),即被动并行加载模式。

此模式适合于逻辑规模较大,对加载速度要求较高的FPGA加载场合。

PP模式下,外部设备通过8bit并行数据线对FPGA进行逻辑加载,CCLK信号由外部提供。

4).BS模式(Boundary Scan Configuration Mode),即边界扫描加载模式。

也就是我们通常所说的JTAG加载模式。

所有的FPGA芯片都有三个或四个加载模式配置管脚,通过配置MESL[0..3]来选取不同的加载模式。

首先来介绍下PS加载模式,各个厂商FPGA产品的PS加载端口定义存在一些差异,下面就对目前主流的三个FPGA厂商Altera, Xilinx,Lattice的PS加载方式进行一一介绍。

Altera公司的FPGA产品PS加载接口如下图所示。

1).CONFIG_DONE:加载完成指示输出信号,I/O接口,高有效,实际使用中通过电阻上拉到VCC,使其默认状态为高电平,表示芯片已加载完毕,当FPGA正在加载时,会将其驱动为低电平。

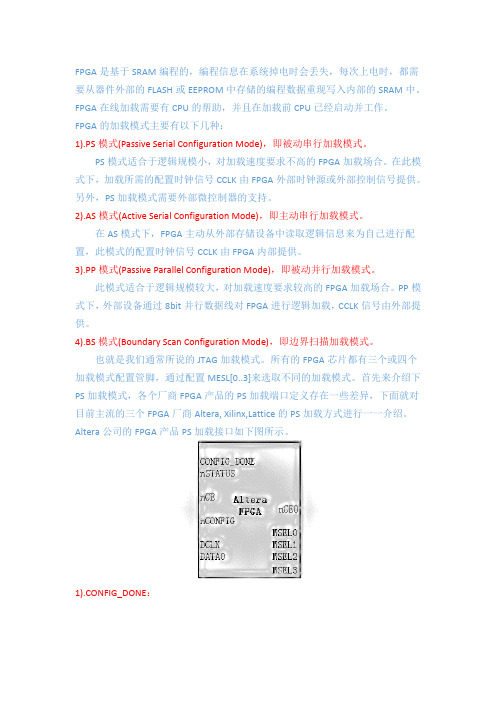

串并口引脚定义图(精)

串口引脚排列图RS-232 — DB9孔式Pin No. Signal1 DCD2 TxD3 RxD4 DSR5 GND6 DTR7 CTS8 RTS9 ---Pin No. Signal1 DCD2 RxD3 TxD4 DTR5 GND6 DSR7 RTS8 CTS9 ---Pin No. Signal2 RxD3 TxD4 CTS6 DTR7 GND8 DCD20 DSRPin No. Signal2 TxD3 RxD4 RTS5 CTS6 DSR7 GND8 DCD 20 DTRPin No. Signal1 DSR2 RTS3 GND4 TxD5 RxD6 DCD7 CTS8 DTRPin No. Signal 1 DCD2 DSR 3RTS4 GND5 TxD6 RxD7 GND8 CTSPin No.Signal2 RxD+(B3 TxD+(B7 GND14 RxD-(A16 TxD-(APC 并行接口引脚定义PC 并行接口外观是 25 针母插座:引脚定义张籍说:有一个名则于嵩的人,青年时代跟随张巡办事;等到张巡起兵讨伐叛贼时,于嵩也曾在敌人围困之中。

张籍大历年间在和州乌江县见过于嵩。

于嵩当时已经六十多岁了。

由于张巡的缘故,当初曾当上了临涣县的县尉,喜欢学问,没有什么书不读。

张籍那时还小,粗略地打听过张巡和许远的事情,了解得不够详细。

于嵩说张巡身高七尺多,胡子长得如同神像。

他曾有一次看到于嵩在读《汉书》,便问:“为什么老是读这一部书?”于嵩回答说:“还没读熟呢。

”张巡说:“我读书不超过三遍,终生不会忘掉。

”于是背诵起于嵩正读的那卷书,背诵完了整卷没错一个字。

于嵩很惊讶,以为张巡碰巧熟读过这一卷,于是随意抽出其他各卷来测试,无不都是这样。

于嵩又从书架上取出另外一些书,试着拿来考问张巡,随问随诵,毫不踌躇。

于嵩跟随张巡的日子很长,也没见过张巡经常读书。

做文章时,拿起纸笔就写,不曾打过草稿。

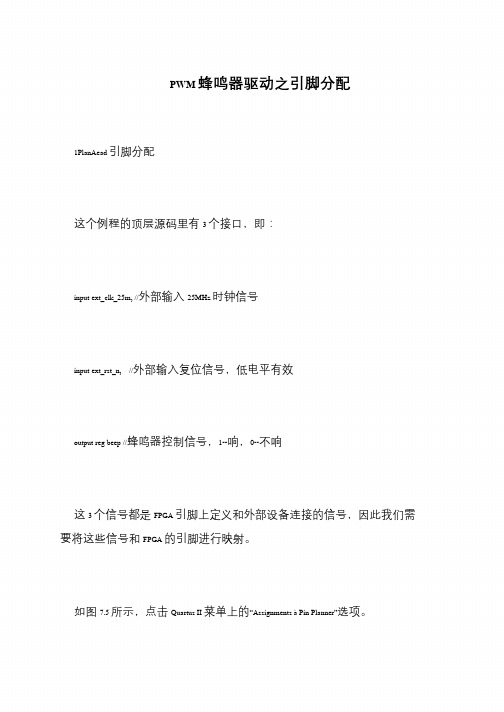

PWM蜂鸣器驱动之引脚分配

图7.9 Tcl Console菜单

接着如图7.10所示,我们在“TclConsole”中输入以下的3条引脚分配脚

本,最后点击“回Βιβλιοθήκη ”。图7.10 tcl脚本输入

此时,我们回到“PinPlanner”中,也可以看到所有引脚自动完成分配。

PWM蜂鸣器驱动之引脚分配

1PlanAead引脚分配

这个例程的顶层源码里有3个接口,即:

input ext_clk_25m, //外部输入25MHz时钟信号

input ext_rst_n,//外部输入复位信号,低电平有效

output reg beep //蜂鸣器控制信号,1--响,0--不响

这3个信号都是FPGA引脚上定义和外部设备连接的信号,因此我们需

前面对ext_clk_25m的引脚分配,我们可以用如下语句实现。

set_location_assignment PIN_23 -to ext_clk_25m

语法“set_location_assignmentPIN_A–toB”是固定格式,A代表FPGA引

脚号,B代表FPGA内部的信号名称。就这幺简单。这个脚本要写到哪里?

CLK_25M分别为24和23,则输入PIN_24和PIN_23。

图7.7时钟和复位信号原理图

图7.8蜂鸣器信号原理图

2脚本直接引脚分配

Tcl(ToolCommandLanguage),即工具命令语言。是一种好用易学的编

程语言。在EDA工具中广泛使用,几乎所有FPGA开发工具都支持这种语

言进行辅助设计。例如这里我们就要尝试用tcl脚本进行FPGA的引脚分配。

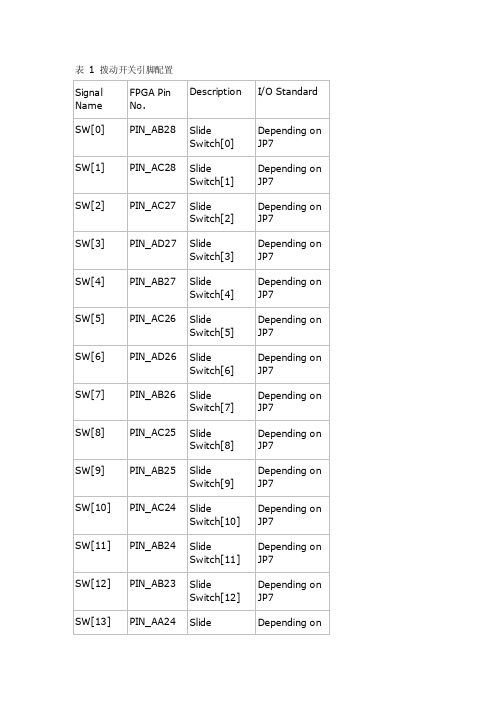

刘善梅《eda技术基础》de2-115所有引脚分配表

表 1 拨动开关引脚配置

表 2 按钮开关引脚配置

表 3 LED 引脚配置

表 4 七段数码管引脚配置

表 5 时钟信号引脚配置信息

表 6 LCD 模块引脚配置

表 7 HSMC 接口引脚配置

表 8 GPIO 引脚配置信息

表 9 扩展接口引脚配置信息

表 10 ADV7123 引脚配置

表 11 音频编解码芯片引脚配置

表 12 RS-232 引脚配置

表 13 PS/2 引脚配置

表 14 千兆以太网芯片引脚配置

表 15 TV 解码芯片引脚配置

表 16 USB (ISP1362)引脚配置

表 17 IR 引脚配置

表 18 SRAM 引脚配置

表 19 SDRAM 引脚配置

表 20 SDRAM 引脚配置

表 21 Flash 引脚配置

表 22 EEPROM 引脚配置

表 23 SD 卡插槽引脚配置。

安路引脚分配-概述说明以及解释

安路引脚分配-概述说明以及解释1.引言1.1 概述概述安路引脚分配是在IC设计与PCB布局中的一项重要任务。

随着电子技术的快速发展,集成电路的功能不断增强,其引脚数量也呈现出飞速增长的趋势。

安路引脚分配准确而合理地将引脚与电气网络相连,确保信号传输在芯片内部和外部有效地进行,是确保电路正常工作的关键一环。

在安路引脚分配中,需要关注引脚的位置,信号的传输距离以及电气特性等因素。

合理的引脚分配可以最大程度地降低电路的噪声干扰,提高电磁兼容性,减少信号互相干扰的可能性,从而提高整个系统的可靠性和稳定性。

同时,安路引脚分配也是一个综合考量的过程,需要考虑引脚的布局密度、引脚之间的物理约束以及芯片的功能模块等因素。

合理的引脚分配可以降低布局的复杂性,减少生产线上的成本及时间,提高生产效率。

本篇文章将重点介绍安路引脚分配的重要性以及相应的原则。

通过分析引脚分配对电路性能的影响,并探讨引脚分配中的一些常见问题和挑战,希望能为相关从业人员提供一些有益的指导和思路。

在文章的结尾,将简要总结安路引脚分配的重要性和原则,并对未来安路引脚分配的发展展望进行展望。

1.2文章结构文章结构部分的内容可以按照以下方式编写:2. 正文2.1 安路引脚分配的重要性2.2 安路引脚分配的原则在这一部分,我们将会详细介绍安路引脚分配的重要性和原则。

首先,我们将讨论为什么安路引脚分配对电路设计非常关键。

接着,我们将介绍一些常用的安路引脚分配原则,以帮助读者更好地理解和应用这些原则。

这两个方面的内容将帮助读者更好地理解安路引脚分配的重要性和遵循合适的原则来提高电路性能。

下面,我们将详细介绍每个小节的内容:2.1 安路引脚分配的重要性在本节中,我们将详细介绍安路引脚分配的重要性。

安路引脚分配是指将电路中的不同功能引脚与相应的安路连接起来,以提供电源供电和信号传输的路径。

正确的安路引脚分配可以有效减少电路中的干扰和噪声,提高电路的性能和可靠性。

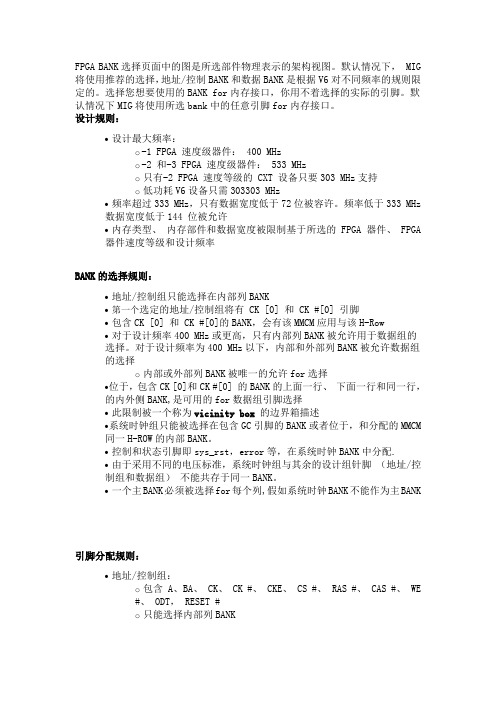

DDR3,DIMM在FPGA上引脚分配规则,完全手打中文

FPGA BANK选择页面中的图是所选部件物理表示的架构视图。

默认情况下, MIG 将使用推荐的选择,地址/控制BANK和数据BANK是根据V6对不同频率的规则限定的。

选择您想要使用的BANK for内存接口,你用不着选择的实际的引脚。

默认情况下MIG将使用所选bank中的任意引脚for内存接口。

设计规则:∙设计最大频率:o-1 FPGA 速度级器件: 400 MHzo-2 和-3 FPGA 速度级器件: 533 MHzo只有-2 FPGA 速度等级的 CXT 设备只要303 MHz支持o低功耗V6设备只需303303 MHz∙频率超过333 MHz,只有数据宽度低于72位被容许。

频率低于333 MHz 数据宽度低于144 位被允许∙内存类型、内存部件和数据宽度被限制基于所选的 FPGA 器件、 FPGA 器件速度等级和设计频率BANK的选择规则:∙地址/控制组只能选择在内部列BANK∙第一个选定的地址/控制组将有 CK [0] 和 CK #[0] 引脚∙包含CK [0] 和 CK #[0]的BANK,会有该MMCM应用与该H-Row∙对于设计频率400 MHz或更高,只有内部列BANK被允许用于数据组的选择。

对于设计频率为400 MHz以下,内部和外部列BANK被允许数据组的选择o内部或外部列BANK被唯一的允许for选择∙位于,包含CK [0]和CK #[0] 的BANK的上面一行、下面一行和同一行,的内外侧BANK,是可用的for数据组引脚选择∙此限制被一个称为vicinity box的边界箱描述∙系统时钟组只能被选择在包含GC引脚的BANK或者位于,和分配的MMCM 同一H-ROW的内部BANK。

∙控制和状态引脚即sys_rst,error等,在系统时钟BANK中分配.∙由于采用不同的电压标准,系统时钟组与其余的设计组针脚(地址/控制组和数据组)不能共存于同一BANK。

∙一个主BANK必须被选择for每个列,假如系统时钟BANK不能作为主BANK引脚分配规则:∙地址/控制组:o包含 A、BA、 CK、 CK #、 CKE、 CS #、 RAS #、 CAS #、 WE#、 ODT, RESET #o只能选择内部列BANKo内存时钟信号(CK [0] 和 CK#[0]) 分配给差分对引脚(P Npair)o VRN/VRP 引脚若被用于引脚分配,DCI级联应该被采用,用以支持地址/时钟的 DCI 标准PS: XILINX公司的Virtex系列FPGA芯片上,每个BANK都有一对VRP/VRN管脚。

EDA技术布局常用规则

EDA技术布局常用规则1.我们要注意贴片器件(电阻电容)与芯片和其余器件的最小距离芯片:一般我们定义分立器件和IC芯片的距离0.5~0.7mm,特殊的地方可能因为夹具配置的不同而改变2.对于分立直插的器件一般的电阻如果为分立直插的比贴片的距离略大一般在1~3mm之间。

注意保持足够的间距(因为加工的麻烦,所以直插的基本不会用)3.对于IC的去耦电容的摆放每个IC的电源端口附近都需要摆放去耦电容,且位置尽可能靠近IC的电源口,当一个芯片有多个电源口的时候,每个口都要布置去耦电容。

4.在边沿附近的分立器件由于一般都是用拼板来做PCB,因此在边沿附近的器件需要符合两个条件,第一就是与切割方向平行(使器件的应力均匀),第二就是在一定距离之内不能布置器件(防止板子切割的时候损坏元器件)5.如果相邻的`焊盘需要相连,首先确认在外面进行连接,防止连成一团造成桥接,同时注意此时的铜线的宽度。

6.焊盘如果在铺通区域内需要考虑热焊盘(必须能够承载足够的电流),如果引线比直插器件的焊盘小的话需要加泪滴(角度小于45度),同样适用于直插连接器的引脚。

7.元件焊盘两边的引线宽度要一致,如果时间焊盘和电极大小有差距,要注意是否会出现短路的现象,最后要注意保留未使用引脚的焊盘,并且正确接地或者接电源。

8.注意通孔最好不要打在焊盘上。

9.另外就是要注意的是引线不能和板边过近,也不允许在板边铺铜(包括定位孔附近区域)10.大电容:首先要考虑电容的环境温度是否符合要求,其次要使电容尽可能的远离发热区域拓展:EDA技术各项软件的优缺点Prote,AD国内低端设计的主流,国外基本没人用。

简单易学,适合初学者,容易上手;占用系统资源较多,对电脑配置要求较高。

在国内使用Protel的人还是有相当的市场的,毕竟中小公司硬件电路设计还是低端的居多,不过建议各位尽早接触学习别的功能更优秀的软件,不要总在低层次徘徊,对薪水不是很友好啊,呵呵。

AltiumDesignerWinter09提供了唯一一款统一的应用方案,其综合电子产品一体化开发所需的所有必须技术和功能。

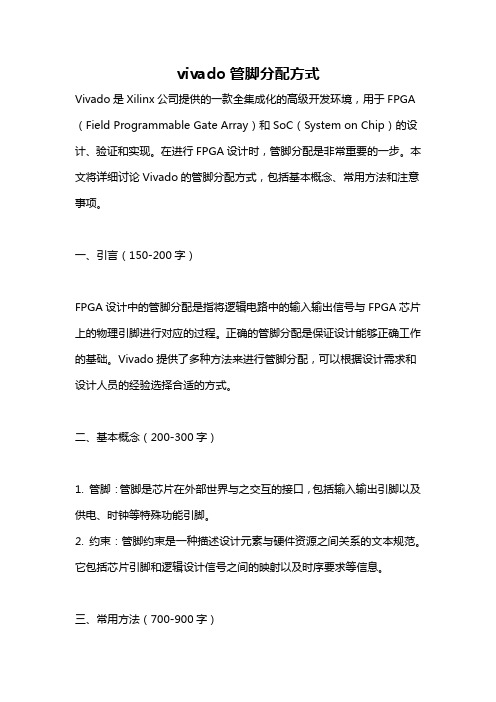

vivado管脚分配方式

vivado管脚分配方式Vivado是Xilinx公司提供的一款全集成化的高级开发环境,用于FPGA (Field Programmable Gate Array)和SoC(System on Chip)的设计、验证和实现。

在进行FPGA设计时,管脚分配是非常重要的一步。

本文将详细讨论Vivado的管脚分配方式,包括基本概念、常用方法和注意事项。

一、引言(150-200字)FPGA设计中的管脚分配是指将逻辑电路中的输入输出信号与FPGA芯片上的物理引脚进行对应的过程。

正确的管脚分配是保证设计能够正确工作的基础。

Vivado提供了多种方法来进行管脚分配,可以根据设计需求和设计人员的经验选择合适的方式。

二、基本概念(200-300字)1. 管脚:管脚是芯片在外部世界与之交互的接口,包括输入输出引脚以及供电、时钟等特殊功能引脚。

2. 约束:管脚约束是一种描述设计元素与硬件资源之间关系的文本规范。

它包括芯片引脚和逻辑设计信号之间的映射以及时序要求等信息。

三、常用方法(700-900字)根据设计的复杂度和需求,Vivado提供了多种管脚分配的方法。

1. 自动分配(200-300字)Vivado提供了自动分配功能,通过分析设计的逻辑连接关系和芯片引脚的约束信息,自动将逻辑信号分配到合适的引脚上。

这种方式适用于简单的设计,能够快速完成管脚分配。

2. 手动分配(200-300字)对于复杂的设计,设计人员可以选择手动分配管脚。

手动分配可以更好地控制信号的布局和引脚的使用,能够满足一些特殊的设计要求。

在Vivado 中,可以通过物理视图和引脚规则编辑器来进行手动分配。

3. 约束文件(200-300字)Vivado使用约束文件来指定管脚分配的规则。

约束文件是一种以文本形式描述的设计约束规范,包括芯片引脚和逻辑信号之间的映射以及时序约束等信息。

设计人员可以在约束文件中指定每个信号的引脚位置和特性要求,并在Vivado中进行综合和实现时引用这些约束文件。

EDA实训(附录EDA开发板的管脚分配表)

EDA实训武汉软件工程职业学院电子系电子信息教研室多功能数字钟的设计一、实训目的1、了解数字钟的工作原理。

2、进一步熟悉用VHDL语言编写驱动七段码管显示的代码。

3、掌握VHDL编写中的一些小技巧。

二、实训原理多功能数字钟应该具有的功能有:显示时-分-秒、整点报时、小时和分钟可调等基本功能。

首先要知道钟表的工作机理,整个钟表的工作应该是在1Hz信号的作用下进行,这样每来一个时钟信号,秒增加1秒,当秒从59秒跳转到00秒时,分钟增加1分,同时当分钟从59分跳转到00分时,小时增加1小时,但是需要注意的是,小时的范围是从0~23时。

在实训中为了显示的方便,由于分钟和秒钟显示的范围都是从0~59,所以可以用一个3位的二进制码显示十位,用一个四位的二进制码(BCD码)显示个位,对于小时因为它的范围是从0~23,所以可以用一个2位的二进制码显示十位,用4位二进制码(BCD码)显示个位。

实训中由于七段码管是扫描的方式显示,所以虽然时钟需要的是1Hz时钟信号,但是扫描确需要一个比较高频率的信号,因此为了得到准确的1Hz信号,必须对输入的系统时钟进行分频。

对于整点报时功能,用户可以根据系统的硬件结构和自身的具体要求来设计。

本实训设计的是当进行整点的倒计时5秒时,让LED来闪烁进行整点报时的提示。

三、实训内容本实验的任务就是设计一个多功能数字钟,要求显示格式为小时-分钟-秒钟,整点报时,报时时间为10秒,即从整点前10秒钟开始进行报时提示,喇叭开始发声,直到过整点时,在整点前5秒LED开始闪烁,过整点后,停止闪烁。

调整时间的的按键用按键模块的S1和S2,S1调节小时,每按下一次,小时增加一个小时,S2调整分钟,每按下一次,分钟增加一分钟。

另外用按键作为系统时钟复位,复位后全部显示00-00-00。

四、实训步骤1、打开QUARTUSII软件,新建一个工程。

2、建完工程之后,再新建一个VHDL File,打开VHDL编辑器对话框。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

I/O方向 O O O O O O O O I I I I I I I I O O O O O I I I O O O O O O O O O O O O O O O O I O O I O O O O O O O O O O O

外设名称

跳线及复用

8个独立LED灯, 主板上的LED1-8 与核心板上LED18共用管脚

独立按键, 核心板上KEY1-4 液晶显示控制 直流电机 注意短接JP1电源 跳线 8563 LM75

七段数码管 段码

—

— 七段数码管 位码 —

232串口 ADC

— —

DAC

—

步进电机 注意 短接JP4电源跳线 红外收发 通过 JP2跳线来选择频 率

FPGA管脚 50 53 54 55 176 47 48 49 156 158 141 143 124 123 122 121 175 174 173 140 139 138 137 136 169 170 167 168 165 166 163 164 160 159 162 161 215 216 213 214 135 133 134 131 132 125 126 127 128 218 217 222 219 203 224

电路图上标号 LED1 LED2 LED3 LED4 LED5 LED6 LED7 LED8 KEY8 KEY7 KEY6 KEY5 KEY4 KEY3 KEY2 KEY1 BEEP LCD_LIGHT LCD_EN DcMotorSpeed DcMotorA DcMotorB 8563_INT LM75_OS SEG0 SEG1 SEG2 SEG3 SEG4 SEG5 SEG6 SEG7 DIG0 DIG1 DIG2 DIG3 DIG4 DIG5 DIG6 DIG7 UART_RXD UART_TXD AD_nCS AD_DAT AD_CLK DAC_LDAC DAC_LOAD DAC_DATA DAC_CLK ULN2003A ULN2003B ULN2003C ULN2003D IR_CLK IR_TX

223 202 207 206 226 227 233 228 225

待定

待定

待定

待定

待定

I O O I I IO O I O I I I O O O O O O O O O O O O O O O O O IO IO IO IO I O O 根据使 用来定 义 O

红外收发 通过 JP2跳线来选择频 率 485接口

待定

主板上PACK1 用户IO口

要通过连接线从主 板上的JP6或核心板 上的PACK复用

PACK1片选

—

—

56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98

IR_RX RS485_DI RS485_RE_DE 485_RO USBVIN USB_SUSPD USB_nRST USB_nINT USB_nCS SD_WP SD_INSERT SPI_MISO SPI_CLK SPI_MOSI SD_nCS SD_POWER VGA_VSYNC VGA_HSYNC VGA_R0 VGA_R1 VGA_R2 VGA_G0 VGA_G1 VGA_G2 VGA_B0 VGA_B1 LATTICE_STR LATTICE_SI LATTICE_SCK MS_DATA MS_CLK KB_DATA KB_CLK RTL8019_INT RTL8019_nCS RTL8019_RST P_IO1 P_IO2 P_IO3 P_IO4 P_IO5 P_IO6 EXT_nCS

—

—

USB接口

—

SD/MMC卡接口

要通过连接线从主 板上的JP6或核心板 上的PACK复用

VGA接口

要通过连接线从主 板上的JP6或核心板 上的PACK复用

LED点阵接口 注 要通过连接线从主 意短接JP5电源跳 板上的JP6或核心板 线 上的PACK复用 鼠标接口 键盘接口 以太网接口 要通过连接线从主 板上的JP6或核心板 上的PACK复用 要通过连接线从主 板上的JP6或核心板 上的PACK复用

序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55