基于FPGA的直接数字频率合成器设计与实现[1]

基于FPGA的直接数字频率合成器设计及仿真

个时 钟脉 冲 的作用 下继续 与频 率控 制字k 相加 。

这 样 .相位 累加 器将 在时钟 作用 下 .不 断对频 率

控 制 字进行 线性 相位 累加 。 由此 可见 .相位 累加

目前 各大 芯片 制造厂 商都 相继 推 出 了采 用 先

进 C S 艺 生产 的 高 性 能 和多 功 能 的D S 片 MO 工 D芯

避簖 辔

V1 o 0O . . N2 1

Fb o 8 e .2 o

器 内 的波 形抽 样值 ( 二进 制 编码1经查 找表查 出 . 从 而完 成相位 到 幅值 的转换 。波 形 存储 器 的输 出 送 到 D A转 换器 后 .D A转换 器 便 可将 数 字 量 形 / /

A E C X系列 、Srt 系列 以及 C co e 。 t i ax yln 等 Ma+ ls 是A t a 司提 供给 客 户 的一个 完 x pul I l r公 e 整 的E A开 发 软件 ,可 完 成从 设 计 输 入 、编译 、 D

式 的波 形 幅值 转换 成所 要合 成 的频 率模 拟 量形 式 信 号 。系统 中 的低 通滤 波器 可用 于 滤除 不需 要 的 取 样分 量 ,以便 输 出频谱纯 净 的正弦波 信 号 。 D S 相 对 带 宽 、频 率 转 换 时 间 、高 分 辨 D在

力 、相 位连续 性 、正交 输 出 以及 集 成化 方 面 的一

器 在 每一个 时钟 脉 冲输 人 时 .都 要把 频 率控 制字

累加一 次 。事实 上 .相位 累加器 输 出的 数据 就是

( 中应 用较 为广 泛 的是A 公 司的A 9 5 其 D D 8 X系列) .

从 而为 电路设 计 者提 供 了多种 选择 。现 在 .D S D

最新-基于FPGA的直接数字频率合成器的设计和实现 精品

基于FPGA的直接数字频率合成器的设计和实现摘要介绍了利用的器件150实现直接数字频率合成器的工作原理、设计思想、电路结构和改进优化方法。

关键词直接数字频率合成现场可编程门阵列直接数字频率合成,即,一般简称是从相位概念出发直接合成所需要波形的一种新的频率合成技术。

目前各大芯片制造厂商都相继推出采用先进工艺生产的高性能和多功能的芯片其中应用较为广泛的是公司的985系列,为电路设计者提供了多种选择。

然而在某些场合,专用的芯片在控制方式、置频速率等方面与系统的要求差距很大,这时如果用高性能的器件设计符合自己需要的电路就是一个很好的解决方法。

1是公司着眼于通信、音频处理及类似场合的应用而推出的器件芯片系列,总的来看将会逐步取代10系列,成为首选的中规模器件产品。

它具有如下特点11采用查找表和嵌入式阵列块相结合的结构,特别适用于实现复杂逻辑功能存储器功能,例如通信中应用的数字信号处理、多通道数据处理、数据传递和微控制等。

2典型门数为1万到10万门,有多达49152位的每个有4096位。

3器件内核采用25电压,功耗低,能够提供高达250的双向功能,完全支持33和66的局部总线标准。

4具有快速连续式延时可预测的快速通道互连;具有实现快速加法器、计数器、乘法器和比较器等算术功能的专用进位链和实现高速多扇入逻辑功能的专用级连接。

150具有典型门数50000门,逻辑单元2880个,嵌入系统块10个,完全符合单片实现电路的要求。

因此采用它设计电路,设计工具为的下一代设计工具软件。

范文先生网收集整理1电路工作原理图1所示是一个基于的电路的工作原理框图。

的工作原理是以数控振荡器的方式产生频率、相位可控制的正弦波。

电路一般包括基准时钟、频率累加器、相位累加器、幅度相位转换电路、转换器和低通滤波器。

基于FPGA的两种DDS实现

基于FPGA的两种DDS实现直接数字频率合成(Direct Digital Synthesis,DDS)是一种基于数字信号处理的频率合成方法,通过将一个连续的幅度和相位可调的数字信号与一个时钟信号相乘,可以产生高精度的频率信号。

在FPGA(Field Programmable Gate Array)中,DDS可以通过数字逻辑实现。

本文将介绍两种基于FPGA的DDS实现方法。

LUT是FPGA中常用的存储组件,可以用于存储预先生成的数字信号样本。

基于LUT的DDS实现方法是将一个固定的正弦波样本表存储在LUT 中,然后通过改变LUT的读指针位置来产生不同频率的正弦波信号。

具体实现步骤如下:1)根据需要生成的信号频率,计算出每一个时钟周期对应的读指针步进量,即相位步进量。

2)初始化读指针位置为0,以时钟信号为基准,每一个时钟周期将读指针位置加上相位步进量。

3)将读指针位置作为索引,从LUT中读取相应的正弦波样本值。

4)将读取到的正弦波样本值输出为DDS的输出信号。

基于LUT的DDS实现有以下优点:-简单易于实现,适合低频率应用。

-输出信号的频率可精确控制,具有较高的频率精度。

-可以通过修改LUT中的正弦波表,实现不同幅度和相位的输出信号。

另一种常见的DDS实现方法是基于相位累加器。

相位累加器是一个用于存储和计算相位信息的寄存器,通过不断累加相位步进量来产生不同频率的输出信号。

具体实现步骤如下:1)根据需要生成的信号频率,计算出每一个时钟周期对应的相位步进量。

2)初始化相位累加器为0,在每一个时钟周期将相位步进量加到累加器中。

3)将相位累加器的高位作为正弦波LUT的读指针,将读取到的正弦波样本值输出为DDS的输出信号。

基于相位累加器的DDS实现有以下优点:-输出信号的频率可精确控制,具有较高的频率精度。

-可以通过修改相位步进量,实现不同频率的输出信号。

-相位累加器可以很容易地实现相位调制和频率调制等功能,具有较高的灵活性。

利用FPGA设计与实现直接数字频率合成器

1 D ] 的工 作 原 理 D

D F 一 种可 把 一 系列 数 字 量 形 式 信 号 通 过 D S是 D C转换 成模 拟 信号 的合 成 技 术 。 D F A D S的 主要 思 想 是从 相位 的概 念 出发 来 合 成 所 需 波 形 , 核 心结 其

p o r sgv n b e Ma wok r ga i ie y t t r s MAT m h h LAB a g a e. l ug n

基于FPGA的数字频率合成器设计与实现

相位 累加器是 典型 的反馈 电路 , Ⅳ位全加 器 和 Ⅳ位 由

累加寄存 器级 联而 成 , 对代 表频率 的二 进制 码进 行 累加运 算 J 。相位累加器 的位数 N=3 。可 以达 到较 高频率 分辨 2 率。该模块通过 V ro 语言编写 。仿真电路如图 2所示 。 ei g l

第2 期

贾伟伟 , 基于 F G 等: P A的数字频率合成 器设计的 R M三部 分组成 。其 中累加器进行 D S O D 相位调节 , 出的结 果 , 入 3 输 送 2位 的 D触 发 器 , 生 读取 产 R M 的地址信号 , O 由于受 到 R M的限制 , O 我们截 取高 1 O位

收稿 日期 : 1 一l 2 1 2一l 0 2

本系统整体 电路 图如图 4所示 , 包括 累加器 、2位的 寄 3

作 者简介 : 贾伟伟 (9 1一 ) 男 , 18 , 山西临汾人 , 硕士研究生 , 助教 , 究方向: 研 嵌入式及通信技 术。 李 美凤 (9 2一 ) 女 ,山西忻州人 ,硕士研 究生 , 18 , 助教 , 究方向: 研 电路 与 系统。

相位 累加器在基准 时钟的作 用下 , 行线 性相位 累加 , 进 当 J 位相位累加器 累加 Ⅳ次后 就会产 生一次 溢 出, 7 、 r 这样 就 完成 了一个周期 , 这个周期 也就是 D S信号的频率周期 。 D

图 3 波形文件仿真图

23 系统整体模块及仿真图 .

DS D 模块的输出频率 是系统工作频率/ 相位累加 ,

0p 8 4 .p 0o s B. s 09p 10op 2. s 10Qp 6. s

基于FPGA的频率合成器的实现

D S电 路 一 般 包 括 基 准 时 钟 、 率 累 加 器 、 位 累 加 器 、 度 / D 频 相 幅 相 能 的 要 求 合 理 选 择 R M。 0 位转 换 电路 、 , 换 器 。频 率 累加 器 对 输 入 信 号 进 行 累 加运 算 , 生 D A转 产 为了解决 R M 受限的瓶颈 , O 此设 计 采用 了 RO 压 缩 技 术 。 可 以 M 频率 控 制 数 据 。相 位 累加 器 由 N 位 全 加 器 和 N位 累 加 寄 存 器 级 联 而 将 0 2T 幅 度 值 . ~叮的 只存 0 2的部 分 。 因为 正 弦 函 数 存 在 以 下 特性 : ~ 成 , 代 表 频 率 的 2进 制 码 进 行 累加 运 算 , 典 型 的 反 馈 电路 , 生 累 对 是 产 s ()sn叮 x s ( +) s ( ̄-) i x= i(— ) i x:一i 2 x n T =一 n 丌 n 加结 果 。 幅 度/ 位 转 换 电 路 实 质 上 是 一 个 波 形 寄存 器 ,以 供 查 表 使 相 其中 , 于区间 0w2 x位 ~ / 。可见 其 他 部 分 均 可 以用 0 "2的 部 分表 ~r r / 用 。 出 的数 据 送 入 DA 转 换 器 和 低 通 滤 波 器 。 S的优 点 是 易 于控 示 。这 样 可将 RO 的大 小 压 缩 到 原 来 的 14 实 现 时 ,^2个 R M 单 读 / DD M /。 21 O

【 摘 要 】 本文介绍 了直接数 字频率合成 器( ) DDS的原理 , 并通过现场可编程 门阵列 F GA以查找表的方式予以实现 2 P 4位 DDS的方案。 相

对 于传 统 的 专 用 的数 字频 率 合 成 器 芯 片 . 高性 能 的 F G 器件 设 计 符 合 自己 需要 的数 字频 率合 成 电路 具 有 方 便 的 控 制 方 式 和 快 速 的置 频 速 用 P A

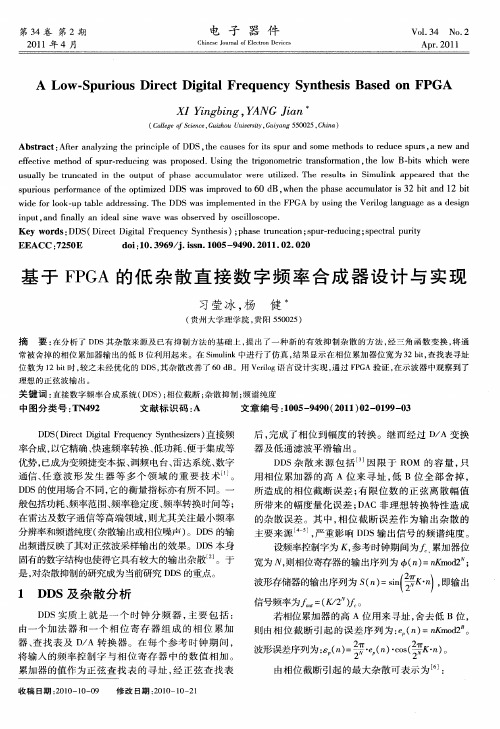

基于FPGA的低杂散直接数字频率合成器设计与实现

ef ci e meh d o p rr d cn s p o o e . i g t e t g n me r r n fr t n,h o B— i ih w r f t t o fs u .e u i g wa r p s d Usn h r o o t c t so ma i t e lw b t wh c e e e v i i a o s

D S杂 散 来 源包 括 因 限 于 R M 的 容 量 , D O 只

D S Drc Dga Feu nySn ei r) D ( i t i t rqe c y t s es 直接频 e il h z

率合成 , 以它精确 、 快速 频率转换 、 功耗 、 低 便于 集成等

优势 , 已成 为变频捷 变本振 、 调频 电 台、 雷达 系统 、 数字 通信 、 意 波 形 发 生 器 等 多 个 领 域 的 重 要 技 术 。 任 J

wi e f rl o u a l d r s i g Th d o k— p tb e a d e sn . e DDS wa mp e n e n t e FPGA y usn h rlg ln u g sa d sg o si l me t d i h b i g t e Ve io a g a e a e i n

s u iu e fr n e o h pi z d DDS wa mpr v d t 0 d wh n t e p a e a c mu a o s3 ta d 1 i p ro s p ro ma c ft e o t mie si o e o 6 B, e h h s c u l tri 2 bi n b t 2

基于FPGA直接数字频率合成器DDS的设计

量, 相位增加量 的大d E频率控制字确定 。信号波形 的数据 表包 含待 , h 产生信号一个周期 的幅度一相位信息 。 从数据表中读出相位累加器输 出相位信号值对应 的幅度 数据 .通过 D C 该数据转换成所需 的模 A 将 拟信号波形输 出。相位累加器 的相位 累加 为循 环迭加 . 这样使得输 出 信号 的相位是 连续的 直接数字合 成器 D S D 就是 根据上述原理 而设 计的数字控制频率合成器

k y p r ft u la e ato hen ce rDDS ,DDS d sg e u la ,b h h s c u ltra d te wa eol aatbe ta a e rt btaywa eoi O e in d n ce r y t ep a e a c muao n h v fYn d t a l h tc n gneaea irr v frlt r T

生任意波形。F G P A器件 作为 系统控制 的核 心 , 其灵活的现 场可更改性 , 可再配置能力 , 系统的各种改进非常方便 , 对 在不更改硬件 电路的基础 上进一步提 高系统的性能 【 关键词 】 直接数字频率合成 ; 相位 累加器 ;P A FG

Di e tDi i e u nc y t e sg Be s d o r c g t Fr q e y S n h  ̄s De i n a e n FPGA al

F PGA e iea h o esse c nr 1Ta lofrh ri rv h efr n e o es se d vc stec r ytm o to. nas u te mp o etep roma c ft y tm. h

【 e od] icdgaFeuny ytesF G Pae cu u t K yw rsDr t it rqec n s ;P A;hs acm lo e il s hi ar

基于FPGA的DDS直接数字频率合成器设计与实现

图 5

期只采样 2点,难 以保证输出精度 。为了保证输 出精度 ,规 定最低每 周期采样 8 点,此时 K 2/ = 2 ,则 :f = = 8 18 … K×

f/ 1 . 2 H c2= 6 5 M z 5

( )最 小步长的正弦波 ( 6 1 图 )

频 率 控 制 字 : 00 0 0 0 00001 相 位 控 制 字 : 00 0 0 0 00000

r — V v\ 1 / 厂 八 八八 / / ^厂 r u 厂 九 \ ^\ 、

图7

仿 真测得正弦波频率为:2 2 . 8 8 7 s2 .6 s /( 0 3 76 u 一 0 2 u )≈ 1. 4 3 H ,与计算参 数相 近,误差来 自于仿真测量时的显 5 6 1M z

2 波形存储 .

本设计 中波形存储 为连续存储 ,对正 弦波进行采样 利用 O a ts制造 一个 R M ,进 行 查值 操 作 , 波 形 的 存 储 方 法 ur u O表 在 上可 以有两种 方案 ,一个是对正弦波从 0到 2 进行采样 ,在 兀 这 次 设计 和 以上 的 参 数 选 取 上 均 基 于 这 种 方 案 ,这 个 方 案 的

示 误差 。

正弦波幅值的获得 ,可通过 C语言编程得到,将 C程序

所 得 结 果 导 出 到一 个 文 件 中 便 可 得 到 正 弦波 幅 值 。 3 系 统 设计 . 由波 形 存 储 模 式 ,设 计 系统 模 型 框 图 4 :

( )最 大 步 长 的 正 弦波 ( 7 2 图 ) 频 率 控 制 字 : 0 10 0 0 00000 相 位 控 制 字 :0 0 0 0 0 0 0 0 00

优 点 是 实现 简 单 ,思 路 清 晰 ;另一 种 方 案 是 对 正 弦波 从 0到

基于FPGA芯片频率合成器设计

基于FPGA芯片的频率合成器设计摘要:本文结合直接数字频率合成(dds)技术的基本原理及工作特点,给出了利用fpga芯片设计快速跳频频率合成器的方法。

关键词:跳频相位 dds fpga 频率合成跳频通信因其具有抗干扰、抗截获的能力,并能做到频谱资源共享,在当前抗干扰通信系统中被广泛应用。

跳频通信系统的一项重要参数是频率的跳变速度。

它在很大程度上决定了跳频通信系统抗跟踪式干扰的能力,这一点在电子对抗中尤为重要。

因此,快速跳频频率合成器的设计就成为跳频通信的关键之一。

目前频率合成主有三种方法:直接模拟合成法、锁相环合成法和直接数字合成法。

直接模拟合成法频率转换时间快(小于100ns),但是体积大、功耗大,目前已基本不被采用。

锁相环合成法结构简化、便于集成,且频谱纯度高,目前使用比较广泛,但存在高分辨率和快转换速度之间的矛盾,一般只能用于大步进频率合成技术中。

直接数字合成(dds)是近年来迅速发展起来的一种新的频率合成方法。

这种方法简单可靠、控制方便,且具有很高的频率分辨率和转换速度,非常适合快速跳频通信的要求。

本文阐述了dds的基本原理,并给出一种基于fpga芯片的直接数字频率合成器的设计方案。

一、dds的基本原理及特点1、基本原理直接数字频率合成是采用数字化技术,通过控制相位的变化速度,直接产生各种不同频率信号的一种频率合成方法。

它由相位累加器、波形存储器、d/a转换器等组成。

参考时钟fr由一个稳定的晶体振荡器产生,用它来同步整个合成器的各个组成部分。

相位累加器由n位加法器与n位相位寄存器级联构成,类似于一个简单的加法器。

每来一个时钟脉冲,加法器就将频率控制字k与相位寄存器输出的累加相位数据相加,然后把相加后的结果送至相位累加器的数据输入端。

相位寄存器就将加法器在上一时钟作用后产生的新相位数据反馈到加法器的输入端,以使加法器在下一个时钟的作用下继续将相位数据与频率控制字相加。

这样,相位累加器在参考时钟的作用下进行线性相位累加。

基于FPGA的直接数字频率合成器设计

一

直接 数 字 频 率 合 成 (D i r e c t D i g i t a l F r e q u e n c y S y n t h e s i z e r) 是 从 相 位 的概 念 直 接 合 成 所 需 波 形 的 种技 术 , 简称 D D F S , 它不 仅 可 以产 生 不 同频 率 的 正 弦波 , 而 且 可 以 控 制 波 形 的初 始 相 位 ( 王允 文,

1 9 9 6) 。

收稿 日期 : 2 0 1 3 . 1 0 - 2 8; 修回 日期: 2 0 1 3 — 1 1 - 0 5 基金项 目: 贵州省质量技术监督局项 目( Z K 0 0 2 ) 。 作者简介 : 胡鹏飞 ( 1 9 8 5 一 ) 硕士。主要研究方 向 : 嵌入式技术 。

频 率合 成器 也 叫信 号 源 或 振 荡 器 , 是 指 产生 所 需 参数 的 电测 试 信 号 的 仪 器 。按 信 号 波形 可 分 为

需要功率或大或小 、 频率或高或低 的振荡器 。

2 数 字频 率 合成 原 理

1 . 1 直 接数 字频 率合成 基本 原理

正弦信号、 函数信号、 脉 冲信号和 随机信 号发生器 四大类 。信 号 发 生 器 在 电 路 实 验 和 实 验 和 设 备 检 测中具有广泛 的用途 , 例如在通信 、 广播 、 电视系统 中, 都需要高频( 射频) 发射 , 把音频( 低频 ) 、 视频信 号或者脉冲信号运载出去 , 就需要能够产生高频的

贵 州 科 学3 2 ( 1 ) : 4 7 - 5 0 , 2 0 1 4

Gu & h o u S c i e n c e

基于FPGA的直接数字频率合成器的设计实现

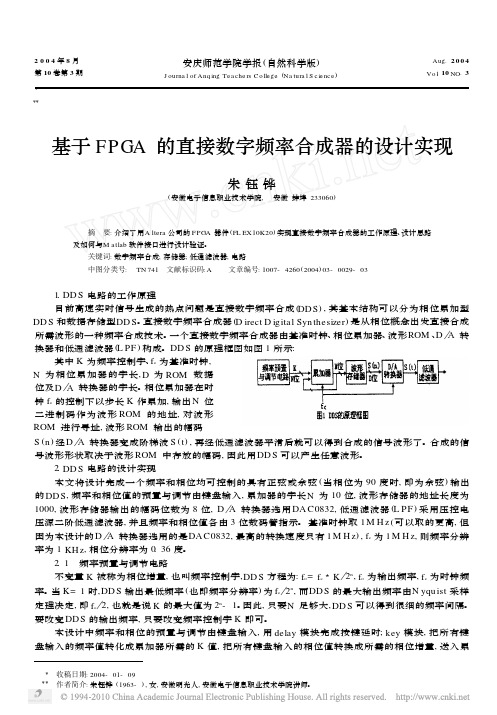

2004年8月第10卷第3期安庆师范学院学报(自然科学版)J ourna l of Anq ing Te a che rs Co lle ge(Na tura l S c ie nce)Aug.2004Vo l.10NO.3ΞΞΞ基于FPGA的直接数字频率合成器的设计实现朱钰铧(安徽电子信息职业技术学院, 安徽蚌埠233060) 摘 要:介绍了用A ltera公司的FPGA器件(FL EX10K20)实现直接数字频率合成器的工作原理、设计思路及如何与M atlab软件接口进行设计验证。

关键词:数字频率合成;存储器;低通滤波器;电路中图分类号: TN741 文献标识码:A 文章编号:1007-4260(2004)03-0029-03 1.DD S电路的工作原理目前高速实时信号生成的热点问题是直接数字频率合成(DD S),其基本结构可以分为相位累加型DD S和数据存储型DD S。

直接数字频率合成器(D irect D ig ita l Syn thesizer)是从相位概念出发直接合成所需波形的一种频率合成技术。

一个直接数字频率合成器由基准时钟、相位累加器、波形ROM、D A转换器和低通滤波器(L PF)构成。

DD S的原理框图如图1所示:其中K为频率控制字、f c为基准时钟,N为相位累加器的字长,D为ROM数据位及D A转换器的字长。

相位累加器在时钟f c的控制下以步长K作累加,输出N位二进制码作为波形ROM的地址,对波形ROM进行寻址,波形ROM输出的幅码S(n)经D A转换器变成阶梯波S(t),再经低通滤波器平滑后就可以得到合成的信号波形了。

合成的信号波形形状取决于波形ROM中存放的幅码,因此用DD S可以产生任意波形。

2.DD S电路的设计实现本文将设计完成一个频率和相位均可控制的具有正弦或余弦(当相位为90度时,即为余弦)输出的DD S,频率和相位值的预置与调节由键盘输入,累加器的字长N为10位,波形存储器的地址长度为1000,波形存储器输出的幅码位数为8位,D A转换器选用DA C0832,低通滤波器(L PF)采用压控电压源二阶低通滤波器,并且频率和相位值各由3位数码管指示。

基于FPGA的直接数字频率合成器的设计

天津师范大学本科毕业论文(设计)题目:基于FPGA的直接数字频率合成器的设计学院:计算机与信息工程学院学生姓名:金宝学号:04509150专业:信息工程年级:2004级完成日期:2008年5月指导教师:李骊基于FPGA的直接数字频率合成器的设计摘要:直接数字频率合成器(DDS)是一种以数字采样技术为基础,以相位累加器为主体的频率合成器。

DDS具有相位噪声低、频率分辨率高、频率转换时间短、工作频带宽线路简洁一系列的优点,是目前战术通信的主要技术基础之一。

本设计是利用FPGA芯片设计直接数字频率合成器,从而实现频率变化、相位变化和幅度变化。

首先对DDS的原理进行了详细讨论,然后通过各种方案的比较和论证,设计实现了基于FPGA的DDS。

设计中采用的是VHDL语言编程,并使用Quartus II软件仿真,通过硬件实现,设计简单,并经实践证明是可行的。

关键字:直接数字频率合成;现场可编程门阵列;硬件描述语言Design and Implementation of Direct Digital FrequencySynthesiZer Based on FPGAAbstract :DDS (Direct Digital Frequency Synthesizer) is a synthesizer which is based on the digital sampling technique and makes phasic accumulator as its principal part. DDS has a series of merits, including low phasic noise, high frequency resolution, short frequency circuitry. It is one of bases of critical technique on tactical communications.This paper designs DDS to implement the changes in frequency, phase and extent by FPGA chips. First of all, it discusses the principle of DDS in detail. Then its design implements DDS based on FPGA by comparing and demonstrating all kinds of schemes. This design is programmed in VHDL language and uses Quartus II as a emulator. The brief design is available after hardware implementation and practical certificate.Key words :Direct Digital Synthesis;FPGA;VHDL目录1 绪论............................................................... - 1 - 1.1 直接数字频率合成技术简介....................................... - 1 - 1.2. DDS的产生..................................................... - 1 - 1.3 直接数字频率合成技术概念....................................... -2 - 1.4 直接数字频率合成技术的工作特点................................. - 2 - 1.5 直接数字频率合成技术在军事通信中的应用......................... -3 - 1.6 课题背景....................................................... - 3 -1.7 课题内容....................................................... - 4 -2 总体方案设计....................................................... - 4 - 2.1 实现DDS的三种技术方案......................................... - 4 -2.1.1 采用高性能DDS单片电路的解决方案............................ - 5 -2.1.2 采用低频正弦波DDS单片电路的解决方案........................ - 6 -2.1.3 自行设计的基于FPGA芯片的解决方案........................... - 6 - 2.2 DDS工作原理.................................................... - 8 -2.2.1 直接频率合成器(DDS)的优缺点............................... - 9 -2.2.2 影响DDS合成技术应用的问题................................. - 11 -2.2.3 技术难点................................................... - 11 - 2.3 现场可编程技术................................................ - 11 -2.3.1 FPGA基本结构.............................................. - 13 -2.3.2 FPGA设计流程.............................................. - 13 -3 数字合成器(DDS)的实现............................................. - 15 - 3.1 VHDL语言简介.................................................. - 15 - 3.2 QuartusII软件简介............................................. - 17 - 3.3 直接数字合成器(DDS)方案的实现................................. - 19 -3.3.1 相位累加器................................................. - 19 -3.3.2 相位调制器................................................. - 21 -3.3.3 正弦查询表ROM ............................................. - 23 -3.3.4 数模转换器DAC ............................................. - 26 -3.3.5 合并——DDS顶层文件....................................... - 26 -4 直接频率合成器DDS的仿真与调试.................................... - 28 - 4.1 综合.......................................................... - 28 - 4.2 仿真.......................................................... - 28 - 4.3硬件实现....................................................... - 29 -4.3.1 配置引脚................................................... - 29 -4.3.2 下载....................................................... - 29 -4.3.3 硬件连接与实现............................................. - 30 -5 总结与展望........................................................ - 31 - 参考文献............................................................ - 32 - 致谢.............................................................. - 33 -1 绪论频率合成器是一种频率稳定度较高的离散间隔型频率信号发生器。

基于FPGA的直接数字频率合成器的设计和实现

基于FPGA的直接数字频率合成器的设计和实现基于FPGA的直接数字频率合成器的设计和实现摘要:介绍了利用Altera的FPGA器件(ACEX EP1K50)实现直接数字频率合成器的工作原理、设计思想、电路结构和改进优化方法。

关键词:直接数字频率合成(DDS)现场可编程门阵列(FPGA)直接数字频率合成(Direct Digital Fraquency Synthesis,即DDFS,一般简称DDS)是从相位概念出发直接合成所需要波形的一种新的频率合成技术。

目前各大芯片制造厂商都相继推出采用先进CMOS工艺生产的高性能和多功能的DDS芯片(其中应用较为广泛的是AD公司的AD985X系列),为电路设计者提供了多种选择。

然而在某些场合,专用的DDS芯片在控制方式、置频速率等方面与系统的要求差距很大,这时如果用高性能的FPGA器件设计符合自己需要的DDS电路就是一个很好的解决方法。

ACEX 1K是Altera公司着眼于通信、音频处理及类似场合的应用而推出的FPGA器件芯片系列,总的来看将会逐步取代FLEX 10K系列,成为首选的中规模器件产品。

它具有如下特点:(1)ACEX 1K采用查找表(LUT)和EAB(嵌入式阵列块)相结合的结构,特别适用于实现复杂逻辑功能存储器功能,例如通信中应用的数字信号处理、多通道数据处理、数据传递和微控制等。

(2)典型门数为1万到10万门,有多达49152位的RAM(每个EAB有4096位RAM)。

(3)器件内核采用2.5V电压,功耗低,能够提供高达250MHz 的双向I/O功能,完全支持33MHz和66MHz的PCI局部总线标准。

(4)具有快速连续式延时可预测的快速通道互连(Fast Track);具有实现快速加法器、计数器、乘法器和比较器等算术功能的专用进位链和实现高速多扇入逻辑功能的专用级连接。

ACEX EP1K50具有典型门数50000门,逻辑单元2880个,嵌入系统块10个,完全符合单片实现DDS电路的要求。

基于FPGA的直接数字频率合成器的设计和实现

能够提 供 高达 20 5 MHz的 双 向 IO 功 能 , 全 支 持 / 完

3 MHz 6 MHz的 P I 部 总线 标 准 。 3 和 6 C 局 快速 连 续式 延 时 可 预测 具

的 快 速 通 道 互 连 ( a tT ak ; 提 供 实 现 快 速 加 法 F s r c ) 能 器 、 数 器 、 法器 和 比较 器 等 算术 功 能 的专 用 进位 链 计 乘 和 实 现 高速 多 扇入 逻辑 功 能 的专 用级 连链 。

西安交通大孥电子物理与器件 国家重点实验 室 ( 西安 704) 109

周俊峰 陈 涛

【 摘 要 】 介 绍 了 利 用 Al r t a的 F GA 器 件 ( E P K5 ) e P AC X E 1 0 实现 直 接 数 字 频 率 合 成 器 的 工作 原 理 、 计 思路 、 路 结 构 和 改进优 化 方 法 。 设 电

路 设计 者 提供 了多 种 选 择 。然 而 在 某 些 场 合 , DS芯 D

片 在 控 制 方 式 、 频 速 率 等方 面 与 系 统 的 要 求 差 距 很 置 大 , 时 如 果用 高 性 能 的 F GA 器 件来 设 计 符 合 自己 这 P 需要 的 DD S电路 就 是一 个 很 好 的解 决 方法 。 AC X 1 器 件 是 Al r E K t a公 司 着 眼 于 通 信 、 频 e 音

路 、 A 转换 器 和低 通 滤波 器 ( P 。 D/ L F)

处理 及 类 似场 合 的应用 而 推 出 的芯 片 系列 , 的来 看 , 总

它将 会 逐 步 取 代 F E 0 系 列 , 为 首选 的 中规 模 L X 1K 成 器件 产 品 。AC X 1 器 件具 有 以下优 点 : E K

直接数字频率合成器的FPGA实现

直接数字频率合成器的FPGA 实现实现摘要:给出了基于FPGA 芯片的直接数字频率合成器(DDS )的设计方法。

因为DDS 技术的实现依赖于高速、高性能的数字器件,选用现场可编程器件FPGA 作为目标器件,作为目标器件,可利用其高速、可利用其高速、可利用其高速、高性能及可重构性,高性能及可重构性,高性能及可重构性,根据需要方便地实现各种比根据需要方便地实现各种比较复杂的调频、较复杂的调频、调相和调幅功能。

调相和调幅功能。

调相和调幅功能。

并且在设计中采用流水线技术,并且在设计中采用流水线技术,并且在设计中采用流水线技术,以提高相位累以提高相位累加器的速度。

随着微电子技术的不断发展,随着微电子技术的不断发展,开发者能很容易地将整个应用系统实开发者能很容易地将整个应用系统实现在一片FPGA 中,从而实现片上系统(SoC )。

因此,用FPGA 实现DDS 就有了更广泛的现实意义,并在现代通信系统中具有良好的实用性。

关键词:直接数字频率合成器,现场可编程门阵列(FPGA ),相位累加器,数/模转换器模转换器1、引言、引言直接数字频率合成器DDS (Direct Digital Frequency Synthesizer ),是一种新型的频率合成技术。

型的频率合成技术。

它是一种采用数字化技术、它是一种采用数字化技术、它是一种采用数字化技术、通过控制相位的变化速度,通过控制相位的变化速度,通过控制相位的变化速度,直接直接产生各种不同频率信号的频率合成方法。

DDS 具有较高的频率分辨率,可实现快速的频率切换且在频率改变时能够保持相位的连续,快速的频率切换且在频率改变时能够保持相位的连续,很容易实现频率、很容易实现频率、相位和幅度的数控调制。

幅度的数控调制。

因此,因此,因此,在现代通信领域,在现代通信领域,在现代通信领域,直接数字频率合成器的应用越来越广直接数字频率合成器的应用越来越广泛,在数字化的调制解调模块中,DDS 取代了VCO (模拟的压控振荡器)而被大量应用。

基于FPGA的直接数字频率合成器设计

维普资讯

自 化 术与 用 20 年 第8 动 技 应 06 第2 卷 期 5

i- 机 应 用 J算

Co p t p i t s m u er a pl ca i on

以及对 D S的深入研究 , DF DF D S的最高工作频率以及噪声性能

已接近锁相 频率合成器的水平。 随着这种频率合成技术 的发展 , DF 现 已广泛应用于通信 D S 系统 、 跳频和扩频 系统 、 电子战和干扰系统 、 多普勒和线性调频、

图 1 DS D F 基 原理框图

Th sg f h e De ino e DDF nFP t S o GA

S J a mi , U in- n FU i - i , U i - i J n xa LI J a x n ( r esF rs yUnv  ̄ t, ri 5 0 0 Chn ) Not at oet h r ie i Habn1 0 4 , ia y

语 占是 VH1L )。

关键 词 : 直接 数 宁 频 串 合 成( DF ) D S ;现 场 可 编 程 门 阵 删( P F GA) VID ; iL

中旧 分 类号 :TH9 5 1 3 .3 文献 标 识 码 :B 文章 编 号 :0 3 2 12 0 )8 0 9 4 10 74 (0 60 0 2 0

u e s d VHDL. Ke wo d DDFS FP A; y r: ; G VHDL

1 引言

直接数字频率合成 ( DF )是继直接频率合成和间接频率 D S 合成之后, 随着数字集成 电路和微 电子技术 , 尤其是现场可编程 门阵列 ( P F GA) 器件的发展而迅速 发展起来的第三代频率合成

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

收稿日期:2004-04-09基金项目:“十五”国防重点预研项目,无人机系统技术项目(41325)作者简介:陈铭(1980─),男,湖南衡阳人,硕士研究生,主要从事无人机数据链技术的研究;薛敏彪(1957—),男,上海市人,研究员,硕士生导师,主要从事无人机测控数据链总体技术研究。

文章编号:1000-8829(2004)09-0001-02基于FPG A 的直接数字频率合成器设计与实现Design and Implementation of Direct Digital Frequency Synthesizer Based on FP G A(西北工业大学 365研究所,陕西西安 710072) 陈 铭,薛敏彪,胡永红,周 平摘要:介绍了直接数字频率合成器的基本组成及设计原理,并对各组成部分进行了理论分析,给出了基于FPG A 的具体设计方案及实现方法。

仿真结果表明,该设计简单合理,使用灵活方便,具有良好的性价比,可应用于各种数字接收系统。

关键词:直接数字频率合成器(DDS );FPG A ;M odelsim 中图分类号:T N741文献标识码:BAbstract :The structure and principles of Direct Digital Frequency Syn 2thesizer is introduced ,and each constituent is theoretically analyzed ,and als o a detailed design based on FPG A is given.The result of simulation shows that the design is simple and feasible ,convenient and flexible to use ,of high ratio for quality to price ,and can be applied in a variety of digital receivers.K ey w ords :direct digital frequency synthesizer (DDS );FPG A ;M odelsim 直接数字频率合成器(DDS ,direct digital frequency synthethiz 2er )是使用一种将相位直接合成所需波形的新的频率合成器。

它在相对带宽、频率转换时间、正交输出、相位连续、频率分辨率等性能指标上远远超过了传统的频率合成器。

目前市场上有多种可供选择的DDS 芯片,比如AD 公司的AD985X 系列。

但是这些专用芯片成本高,同时还存在一些灵活性方面的缺陷,特别是在有关军用的软件无线电技术中的应用受到限制,因此很有必要采用高性能的FPG A 自行设计出符合自己需要的DDS 。

1 DDS 原理组成如图1所示,直接数字频率合成器(DDS )的主要功能就是产生一个正弦波S (n )=cos (2πf 0n/f s )(1)式中,f 0为输入中频信号的频率;f s 为采样频率。

DDS 主要由相位累加器、量化器、查找表及加扰器等功能模块组成。

各部分功能如下:相位累加器:将数字本振频率转换成相位,每来一个时钟脉冲就累加一个相位增量;量化器:将累加后的相位值合理地截短,转换为查找表的输入地址,从而有效地减少查找表的深度;查找表:将相位地址与正弦值一一对应,输出所需的正弦信号;加扰器:在累加后的相位值中加入噪声,以消除累加器引入的谐振误差。

2 DDS 的设计分析(1)相位累加器。

在输入的每个时钟脉冲相位的基础上增加一个相位增量Δθ=2πf 0/f s 。

若用B θ(n )表示相位累加器的宽度,f out 表示输出频率,Δθ表示相位增量,Δf 表示频率分辨率,则它们之间的关系可以表示为f out =f sΔθ2Bθ(n )(2)Δf =f s2Bθ(n )(3) 由于频率转换速度是DDS 最重要的指标之一,因此这一部分的设计采用了进位链与流水线技术相结合的方法,一方面提高了芯片资源的利用率,另一方面提高了系统的性能与速度。

(2)量化器。

由于通常要求的频率分辨率较高,根据式(3),使得B θ(n )比较大,比如180MH z 的采样频率下,若频率精度为1H z ,则B θ(n )=28bits ,若将它直接作为查找表地址,则所需的ROM 就非常大,由于目前的FPG A 中集成的RAM 有限,这样就需要采用片外RAM ,会加大系统的复杂性。

因此在设计中加入一个量化器Q ,其作用是将累加后的相位θ(n )量化并转换为地址Θ(n ),作为查找表T 的地址输入,若用B Θ(n )表示查找表地址的宽度,S FDR 表示无杂散动态范围(dB ),则有B Θ(n )≥[log 2S FDR6](4) 式(4)表示查找表地址的宽度每增加一位,S FDR 可以提高约6dB 。

(3)查找表。

查找表根据地址将预先存在RAM 中的样本逐一读出产生所需频率的正弦波。

查找表有2个关键的参数,一个是查找表的深度,它由B Θ(n )决定,根据正弦波的对称性,只需要在RAM 中存入1/4个周期的波形,因此,查找表的深度应为2B Θ(n )-2;另一个是查找表内每个数据的长度B out ,为了防止发生“钝化”现象,它应该满足下式B out ≥max{log 2[11-cos (2π/2B θ(n )),log 2[1sin (2π/2Bθ(n ))]}(5)・1・基于FPG A的直接数字频率合成器设计与实现图1 DDS 原理框图 (4)加扰器。

由于所采用的量化器Q 将B θ(n )截断为B Θ(n ),所以极大地减少了查找表的长度,然而由此会在输出波形的频谱上引入了一些谐振分量,而在时域上会产生一个缓慢变化的包络。

解决的办法是在Q1前加上一个加扰器D1,让它产生方差约等于相位累加器最低有效位的随机噪声,这种设计方法可以有效地消除频谱中的谐振分量,并且在相同的S FDR 参数下,所需的地址宽度比由式(4)计算得来的B Θ(n )还要减少两位。

3 基于FPG A 的DDS 设计与仿真 FPG A (field programmable gate array )是一种门电路可以高达上百万,时钟频率可以达到几百兆的可编程逻辑器件。

以X ilinx 公司的Virtex Ⅱ为例,它的基本组成是可配置逻辑模块(C LB ),每个C LB 由2个S lice 组成,每个S lice 内含一个4输入的查找表(LUT ),一个进位逻辑和一个触发器。

同时不同型号的芯片还分别集成了数量不等的乘法器、RAM 等资源。

该小型飞行器测控系统的接收机要求DDS 的基本参数为:系统时钟为180MH z (即输出波形的采样率);频率分辨率为1H z ;S FDR =68dB ;输出频率为70MH z ;输出数据宽度为12bits 。

经计算,所需的RAM 大小为1K ×12bits ,并且考虑到在同一片FPG A 中还需集成其他功能,因此选择了X ilinx 公司Virtex Ⅱ系列的XC2V1000作为硬件开发平台,该芯片的容量为40×32个C LB (可配置逻辑块),有40个乘法模块,最大有720K B 的BlockRAM 。

本设计使用了片内集成的BlockRAM ,利用X ilinx 公司C ore G enerator 6.1.03i 工具来调用芯片上的RAM 资源,并通过Mem ory Editor 来输入正弦波形,极大地方便了设计过程。

经过在X ilinx 公司ISE6.1中进行初步合成,共使用了90个查找表(约合23个C LB ),190个Reg ,1个BlockRAM 。

在开发过程中,采用了VH D L 语言,运用Mentor G raphic 公司的M odelsim SE 5.7g 进行了模拟与仿真,并以Synpicity 公司的Synpilify Pro7.2作为合成工具,最后用X ilinx 公司的ISE6.1进行布线和下载。

图2 两种设计的频谱比较图3 M odelism 中的时序仿真图 分别对没有使用加扰器和使用加扰器的情况下进行模拟,在M odelsim 中分别得到两组数据,得出图2所示的结果。

并给出了加扰后的电路时序图以及数据。

从仿真结果可以清楚地看到,量化器Q 虽然在保证S FDR 不变的前提下有效地减少了查找表的深度,但是却引入了谐振误差,加入加扰器D 后,一方面消除了谐振误差,另一方面在不影响S FDR 的条件下进一步减少了查找表的深度。

4 结束语该直接数字频率合成器已在上述数字接收机中使用并测试,测试结果与仿真结果拟和较好。

由于它可以根据不同应用的需要随时更改参数,所以可推广应用于其他测控系统的数字接收机中。

参考文献:[1] Uwe M eyer 2Baese.数字信号处理的FPG A 实现[M].刘凌,等,译.北京:清华大学出版社,2003.[2] 杨小牛,等.软件无线电原理与应用[M].北京:电子工业出版社,2001.[3] O ’Leary P ,M aloberti F.A direct 2digital synthesizer with im proved spectralperformance[J ].IEEE T ran.on C ommunication ,1991,39(7).[4] 曾繁泰,等.VH D L 程序设计[M].北京:清华大学出版社,2001.[5] Virtex 2ⅡPlatform FPG A User G uide[Z].X inlinx Inc.,2004.□・2・《测控技术》2004年第23卷第9期。