MC74F126中文资料

74HC126

NXP Semiconductors

74HC126; 74HCT126

Quad buffer/line driver; 3-state

4. Functional diagram

$ 2( $ 2( $ 2( $ 2(

<

<

(1

74HC_HCT126

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2014. All rights reserved.

Product data sheet

Rev. 3 — 22 September 2014

2 of 16

NXP Semiconductors

74HC126; 74HCT126

Quad buffer/line driver; 3-state

5.2 Pin description

Table 2. Symbol 1OE, 2OE, 3OE, 4OE 1A, 2A, 3A, 4A 1Y, 2Y, 3Y, 4Y GND VCC Pin description Pin 1, 4, 10, 13 2, 5, 9, 12 3, 6, 8, 11 7 14 Description data enable input (active HIGH) data input data output ground (0 V) supply voltage

3. Ordering information

Table 1. Ordering information Package Temperature range 74HC126N 74HCT126N 74HC126D 74HCT126D 74HC126DB 74HCT126DB 74HC126PW 74HCT126PW 40 C to +125 C TSSOP14 40 C to +125 C SSOP14 40 C to +125 C SO14 plastic small outline package; 14 leads; body width 3.9 mm plastic shrink small outline package; 14 leads; body width 5.3 mm plastic thin shrink small outline package; 14 leads; body width 4.4 mm SOT108-1 SOT337-1 SOT402-1 40 C to +125 C Name DIP14 Description plastic dual in-line package; 14 leads (300 mil) Version SOT27-1 Type number

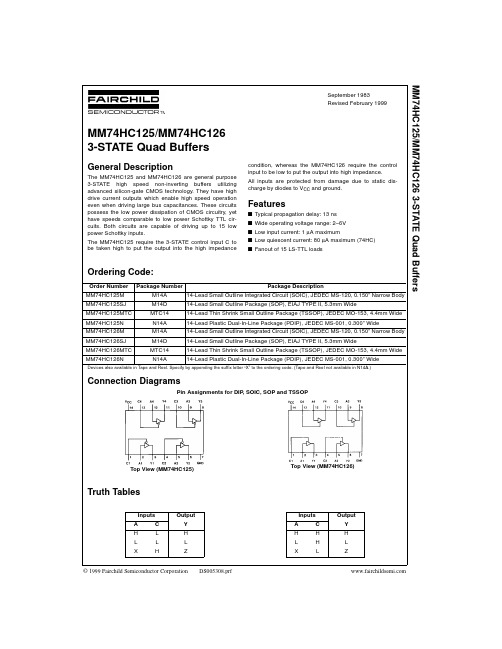

MM74HC126N中文资料

age to the device may occur.

Note 2: Unless otherwise specified all voltages are referenced to ground.

Note 3: Power Dissipation temperature derating — plastic “N” package: − 12 mW/°C from 65°C to 85°C.

tPHL, tPLH tPZH tPHZ tPZL tPLZ

Maximum Propagation Delay Time Maximum Output Enable Time to HIGH Level Maximum Output Disable Time from HIGH Level Maximum Output Enable Time to LOW Level Maximum Output Disable Time from LOW Level

TTL74系列芯片大全(中英文对照)

7400 TTL 2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器74645 TTL 三态输出八同相总线传送接收器74670 TTL 三态输出4×4寄存器堆7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双D触发器7476 TTL 带预置清除双J-K触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器SN74LSOO四2输入与非门SN74LSO2四2输入或非门SN74LS04六反相器SN74LS06六反相缓冲器/驱动器SN74LS08四2输入与非门SN74LS10三3输入与非门SN74LS12三3输入与非门SN74LS14六反相器.斯密特触发SN74LS16六反相缓冲器/驱动器SN74LS20双4输入与门SN74LS22双4输入与门SN74LS26四2输入与非门SN74LS28四输入端或非缓冲器SN74LS32四2输入或门SN74LS37四输入端与非缓冲器SN74LS40四输入端与非缓冲器SN74LS47BCD-七段译码驱动器SN74LS49BCD-七段译码驱动器SN74LS54四输入与或非门SN74LS63六电流读出接口门SN74LS74双D触发器SN74LS76双J-K触发器SN74LS83双J-K触发器SN74LS86四2输入异或门SN74LS904位十进制波动计数器SN74LS9212分频计数器SN74LS965位移位寄存器SN74LS109正沿触发双J-K触发器SN74LS113双J-K负沿触发器SN74LS121单稳态多谐振荡器SN74LS123双稳态多谐振荡器SN74LS125三态缓冲器SN74LS1313-8线译码器SN74LS13313输入与非门SN74LS137地址锁存3-8线译码器SN74LS139双2-4线译码-转换器SN74LS14710-4线优先编码器SN74LS153双4选1数据选择器SN74LS155双2-4线多路分配器SN74LS157四2选1数据选择器SN74LS160同步BDC十进制计数器SN74LS162同步BDC十进制计数器SN74LS1648位串入并出移位寄存SN74LS1668位移位寄存器SN74LS1694位可逆同步计数器SN74LS17216位多通道寄存器堆SN74LS1746D型触发器SN74LS176可预置十进制计数器SN74LS182超前进位发生器SN74LS18964位随机存储器SN74LS191二进制同步可逆计数器SN74LS193二进制可逆计数器SN74LS195并行存取移位寄存器SN74LS197可预置二进制计数器SN74LS2383-8线译码/多路转换器SN74LS241八缓冲/驱动/接收器SN74LS243四总线收发器SN74LS245八总线收发器SN74LS248BCD-七段译码驱动器SN74LS251三态8-1数据选择器SN74LS256双四位选址锁存器SN74LS258四2选1数据选择器SN74LS260双5输入或非门SN74LS266四2输入异或非门SN74LS275七位树型乘法器SN74LS279四R-S触发器SN74LS2834位二进制全加器SN74LS2934位二进制计数器SN74LS365六缓冲器带公用启动器SN74LS367六总线三态输出缓冲器SN74LS3738D锁存器SN74LS3754位双稳锁存器SN74LS386四2输入异或门SN74LS393双4位二进制计数器SN74LS5748位D型触发器SN74LS6848位数字比较器SN74LSO1四2输入与非门SN74LS03四2输入与非门SN74LS05六反相器SN74LS07六缓冲器/驱动器SN74LS09四2输入与非门SN74LS11三3输入与非门SN74LS13三3输入与非门SN74LS15三3输入与非门SN74LS17六反相缓冲器/驱动器SN74LS21双4输入与门SN74LS25双4输入与门SN74LS27三3输入与非门SN74LS30八输入端与非门SN74LS33四2输入或门SN74LS38双2输入与非缓冲器SN74LS42BCD-十进制译码器SN74LS48BCD-七段译码驱动器SN74LS51三3输入双与或非门SN74LS55四4输入与或非门SN74LS73双J-K触发器SN74LS754位双稳锁存器SN74LS78双J-K触发器SN74LS854位幅度比较器SN74LS884位全加器SN74LS918位移位寄存器SN74LS93二进制计数器SN74LS954位并入并出寄存器SN74LS107双J-K触发器SN74LS112双J-K负沿触发器SN74LS114双J-K负沿触发器SN74LS122单稳态多谐振荡器SN74LS124双压控振荡器SN74LS126四3态总线缓冲器SN74LS132二输入与非触发器SN74LS136四异或门SN74LS1383-8线译码/转换器SN74LS145BCD十进制译码/驱动器SN74LS1488-3线优先编码器SN74LS1518选1数据选择器SN74LS1544-16线多路分配器SN74LS156双2-4线多路分配器SN74LS158四2选1数据选择器SN74LS1614位二进制计数器SN74LS1634位二进制计数器SN74LS1658位移位寄存器SN74LS1684位可逆同步计数器SN74LS1704x4位寄存器堆SN74LS1734D型寄存器SN74LS1754D烯触发器SN74LS181运算器/函数发生器SN74LS183双进位保存全价器SN74LS190同步BCD十进制计数器SN74LS192BCD-同步可逆计数器SN74LS194双向通用移位寄存器SN74LS196可预置十进制计数器SN74LS221双单稳态多谐振荡器SN74LS240八缓冲/驱动/接收器SN74LS242四总线收发器SN74LS244八缓冲/驱动/接收器SN74LS247BCD-七段译码驱动器SN74LS249BCD-七段译码驱动SN74LS253双三态4-1数据选择器SN74LS257四3态2-1数据选择器SN74LS2598位可寻址锁存器SN74LS2612x4位二进制乘发器SN74LS273八进制D型触发器SN74LS276四J-K触发器SN74LS2809位奇偶数发生校检器SN74LS290十进制计数器SN74LS2954位双向通用移位寄存器SN74LS366六缓冲器带公用启动器SN74LS368六总线三态输出反相器SN74LS3748D触发器SN74LS3778位单输出D型触发器SN74LS390双十进制计数器SN74LS5738位三态输出D型锁存器SN74LS6708位数字比较器SN74HC00 四2输入与非门SN74HC02 四2输入或非门SN74HC03 四2输入或非门SN74HC04 六反相器SN74HC05 六反相器SN74HC08 四2输入与门SN74HC10 三3输入与非门SN74HC11 三3输入与门SN74HC14 六反相器/斯密特触发SN74HC20 双四输入与门SN74HC21 双四输入与非门SN74HC27 三3输入与非门SN74HC30 八输入端与非门SN74HC32 四2输入或门SN74HC42 BCD十进制译码器SN74HC73 双J-K触的器SN74HC76 双J-K触的器SN74HC86 四2输入异或门SN74HC107 双J-K触发器SN74HC113 双J-K负沿触发器SN74HC123 双稳态多谐振荡器SN74HC125 三态缓冲器SN74HC126 四三态总线缓冲器SN74HC132 二输入与非缓冲器SN74HC137 二输入与非缓冲器SN74HC138 3-8线译码/解调器SN74HC139 双2-4线译码/解调器SN74HC148 8选1数据选择器SN74HC151 双4选1数据选择器SN74HC154 4-16线多路分配器SN74HC157 四2选1数据选择器SN74HC161 4位二进制计数器SN74HC163 4位二进制计数器SN74HC164 8位串入并出移位寄存器SN74HC165 8位移位寄存器SN74HC173 4D型触发器SN74HC174 6D触发器SN74HC175 4D型触发器SN74HC191 二进制同步可逆计数器SN74HC221 双单稳态多谐振荡器SN74HC238 3-8线译码器SN74HC240 八缓冲器SN74HC244 八总线3态输出缓冲器SN74HC245 八总线收发器SN74HC251 三态8-1数据选择器SN74HC259 8位可寻址锁存器SN74HC266 四2输入异或非门SN74HC273 8D型触发器SN74HC367 六缓冲器/总线驱动器SN74HC368 六缓冲器/总线驱动器SN74HC373 8D锁存器SN74HC374 8D触发器SN74HC393 双4位二进制计数器SN74HC541 8位三态输出缓冲器SN74HC573 8位三态输出D型锁存器SN74HC574 8D型触发器SN74HC595 8位移位寄存器/锁存器SN74HC4028 7级二进制串行加数器SN74HC4046 锁相环SN74HC4051 8选1模拟开关SN74HC4053 三2选1模拟开关SN74HC4060 14位计数/分频/振荡器SN74HC4066 四双相模拟开关SN74HC4078 3输入端三或门SN74HC4511 7段锁存/译码驱动器SN74HC4520 双二进制加法计数器74F00 高速四2输入与非门74F02 高速四2输入或非门74F04 高速六反相器74F08 高速四2输入与门74F10 高速三3输入与门74F14 高速六反相斯密特触发74F32 高速四2输入或门74F38 高速四2输入或门74F74 高速双D型触发器74F86 高速四2输入异或门74F139 高速双2-4线译码/驱动器74F151 高速双2-4线译码/驱动器74F153 高速双4选1数据选择器74F157 高速双4选1数据选择器74F161 高速6D型触发器74F174 高速6D型触发器74F175 高速4D型触发器74F244 高速八总线3态缓冲器74F245 高速八总线收发器74F373 高速8D锁存器SN74HCT04 六反相器。

74系列芯片简介——功能与描述

7400、74H00、74L00、74LS00、74S00、74HC00、74C00、74F00、74ALS00四2输入与非门Y=\AB。

7401、74LS01、74HC01、74ALS01四2输入与非门(OC)Y=\AB。

7402、74L02、74LS02、74S02、74HC02、74C02、74ALS02、74F02四2输入或非门。

Y=/A+B。

7403、74L03、74LS03、74ALS03、74S03、74HC037404、74H04、74L04、74S04、74HC04、74C04、74F04、74ALS04六反相器Y=/A。

7405、74H05、74LS05、74S05、74HC05、74F05、74ALS05六反相器(OC)Y=/A。

7406、74LS06六反相缓冲器/驱动器(OC、高压输出)Y=/A;是7405高耐压输出型,耐压30V。

7407、74LS07、74HC07六缓冲器/驱动器(OC、高压输出)Y=A; 30V耐高压输出。

7408、74LS08、74F08、74ALS08、74S08、74HC08、74C08四2输入与门Y=AB。

7409、74LS09、74F09、74ALS09、74S09、74HC09四2输入与门(OC)Y=AB。

7410、74H10、74L10、74LS10、74ALS10、74S10、74HC10、74C1074H11、74LS11、74S11、74F11、74ALS11、74HC11三3输入与门Y=ABC。

7412、74LS12、74ALS12三3输入与非门(OC)Y=\ABC。

7413、74LS13双4输入与非门Y=\ABCD。

7414、74LS14、74HC14、74C1474H15、74LS15、74ALS15、74S15三3输入与门(OC)Y=ABC。

7416、74LS16六反相缓冲器/驱动器Y=/A;7417、74LS17六缓冲器/驱动器(OC、高压输出)Y=A;15V耐压输出。

74F74中文资料

TL F 946954F 74F74 Dual D-Type Positive Edge-Triggered Flip-FlopDecember1994 54F 74F74Dual D-Type Positive Edge-Triggered Flip-FlopGeneral DescriptionThe’F74is a dual D-type flip-flop with Direct Clear and Setinputs and complementary(Q Q)outputs Information at theinput is transferred to the outputs on the positive edge ofthe clock pulse Clock triggering occurs at a voltage level ofthe clock pulse and is not directly related to the transitiontime of the positive-going pulse After the Clock Pulse inputthreshold voltage has been passed the Data input is lockedout and information present will not be transferred to theoutputs until the next rising edge of the Clock Pulse inputAsynchronous InputsLOW input to S D sets Q to HIGH levelLOW input to C D sets Q to LOW levelClear and Set are independent of clockSimultaneous LOW on C D and S Dmakes both Q and Q HIGHFeaturesY Guaranteed4000V minimum ESD protection Commercial MilitaryPackagePackage DescriptionNumber74F74PC N14A14-Lead(0 300 Wide)Molded Dual-In-Line54F74DM(Note2)J14A14-Lead Ceramic Dual-In-Line74F74SC(Note1)M14A14-Lead(0 150 Wide)Molded Small Outline JEDEC74F74SJ(Note1)M14D14-Lead(0 300 Wide)Molded Small Outline EIAJ54F74FM(Note2)W14B14-Lead Cerpack54F74LM(Note2)E20A20-Lead Ceramic Leadless Chip Carrier Type C Note1 Devices also available in13 reel Use Suffix e SCXNote2 Military grade device with environmental and burn-in processing Use suffix e DMQB FMQB and LMQBLogic SymbolsTL F 9469–3TL F 9469–4IEEE IECTL F 9469–6TRI-STATE is a registered trademark of National Semiconductor CorporationC1995National Semiconductor Corporation RRD-B30M75 Printed in U S AConnection DiagramsPin Assignmentfor DIP SOIC and FlatpakTL F 9469–1Pin Assignmentfor LCCTL F 9469–2 Unit Loading Fan Out54F 74FPin Names Description U L Input IIH I ILHIGH LOW Output I OH I OLD1 D2Data Inputs1 0 1 020m A b0 6mACP1 CP2Clock Pulse Inputs(Active Rising Edge)1 0 1 020m A b0 6mAC D1 C D2Direct Clear Inputs(Active LOW)1 0 3 020m A b1 8mAS D1 S D2Direct Set Inputs(Active LOW)1 0 3 020m A b1 8mAQ1 Q1 Q2 Q2Outputs50 33 3b1mA 20mATruth TableInputs OutputsS D C D CP D Q QL H X X H LH L X X L HL L X X H HH H L h H LH H L l L HH H L X Q0Q0H(h)e HIGH Voltage LevelL(l)e LOW Voltage LevelX e ImmaterialQ0e Previous Q(Q)before LOW-to-HIGH Clock TransitionLower case letters indicate the state of the referenced input or output onesetup time prior to the LOW-to-HIGH clock transitionLogic DiagramTL F 9469–5 Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays2Absolute Maximum Ratings(Note1)If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications Storage Temperature b65 C to a150 CAmbient Temperature under Bias b55 C to a125 CJunction Temperature under Bias b55 C to a175 C Plastic b55 C to a150 CV CC Pin Potential toGround Pin b0 5V to a7 0V Input Voltage(Note2)b0 5V to a7 0V Input Current(Note2)b30mA to a5 0mA Voltage Applied to Outputin HIGH State(with V CC e0V)Standard Output b0 5V to V CC TRI-STATE Output b0 5V to a5 5V Current Applied to Outputin LOW State(Max)twice the rated I OL(mA) ESD Last Passing Voltage(Min)4000V Note1 Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired Functional operation under these conditions is not impliedNote2 Either voltage limit or current limit is sufficient to protect inputs Recommended Operating ConditionsFree Air Ambient TemperatureMilitary b55 C to a125 C Commercial0 C to a70 C Supply VoltageMilitary a4 5V to a5 5V Commercial a4 5V to a5 5VDC Electrical CharacteristicsSymbol Parameter54F 74FUnits V CC Conditions Min Typ MaxV IH Input HIGH Voltage2 0V Recognized as a HIGH Signal V IL Input LOW Voltage0 8V Recognized as a LOW Signal V CD Input Clamp Diode Voltage b1 2V Min I IN e b18mAV OH Output HIGH54F10%V CC2 5I OH e b1mA Voltage74F10%V CC2 5V Min I OH e b1mA74F5%V CC2 7I OH e b1mAV OL Output LOW54F10%V CC0 5V Min I OL e20mAVoltage74F10%V CC0 5I OL e20mAI IH Input HIGH54F20 0m A Max V IN e2 7V Current74F5 0I BVI Input HIGH Current54F100m A Max V IN e7 0V Breakdown Test74F7 0I CEX Output HIGH54F250m A Max V OUT e V CC Leakage Current74F50V ID Input Leakage74F4 75V0 0I ID e1 9m ATest All Other Pins GroundedI OD Output Leakage74F3 75m A0 0V IOD e150mVCircuit Current All Other Pins GroundedI IL Input LOW Current b0 6mA Max V IN e0 5V(D CP)b1 8V IN e0 5V(C D S D) I OS Output Short-Circuit Current b60b150mA Max V OUT e0VI CC Power Supply Current10 516 0mA Max3AC Electrical Characteristics74F54F74FT A e a25 CT A V CC e Mil T A V CC e Com Symbol Parameter V CC e a5 0VC L e50pF C L e50pF UnitsC L e50pFMin Typ Max Min Max Min Maxf max Maximum Clock Frequency10012580100MHzt PLH Propagation Delay3 85 36 83 88 53 87 8ns t PHL CP n to Q n or Q n4 46 28 04 410 54 49 2t PLH Propagation Delay3 24 66 13 28 03 27 1ns t PHL C Dn or S Dn to Q n or Q n3 57 09 03 511 53 510 5AC Operating Requirements74F54F74FSymbol ParameterT A e a25 CT A V CC e Mil T A V CC e Com Units V CC e a5 0VMin Max Min Max Min Maxt s(H)Setup Time HIGH or LOW2 03 02 0t s(L)D n to CP n3 04 03 0ns t h(H)Hold Time HIGH or LOW1 02 01 0t h(L)D n to CP n1 02 01 0t w(H)CP n Pulse Width4 04 04 0ns t w(L)HIGH or LOW5 06 05 0t w(L)C Dn or S Dn Pulse Width4 04 04 0nsLOWt rec Recovery Time2 03 02 0nsC Dn or S Dn to CP4Ordering InformationThe device number is used to form part of a simplified purchasing code where the package type and temperature range are defined as follows74F74S C XTemperature Range Family Special Variations74F e Commercial QB e Military grade device with54F e Military environmental and burn-inprocessingDevice Type X e Devices shipped in13 reelPackage Code Temperature RangeP e Plastic DIP C e Commercial(0 C to a70 C)D e Ceramic DIP M e Military(b55 C to a125 C)F e FlatpakL e Leadless Chip Carrier(LCC)S e Small Outline SOIC JEDECSJ e Small Outline SOIC EIAJPhysical Dimensions inches(millimeters)20-Lead Ceramic Leadless Chip Carrier(L)NS Package Number E20A5Physical Dimensions inches(millimeters)(Continued)14-Lead Ceramic Dual-In-Line Package(D)NS Package Number J14A14-Lead(0 150 Wide)Molded Small Outline JEDEC(S)NS Package Number M14A6Physical Dimensions inches(millimeters)(Continued)14-Lead(0 300 Wide)Molded Small Outline EIAJ(SJ)NS Package Number M14D14-Lead(0 300 Wide)Molded Dual-In-Line Package(P)NS Package Number N14A754F 74F 74D u a l D -T y p e P o s i t i v e E d g e -T r i g g e r e d F l i p -F l o pPhysical Dimensions inches (millimeters)(Continued)14-Lead Ceramic Flatpak (F)NS Package Number W14BLIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION As used herein 1 Life support devices or systems are devices or 2 A critical component is any component of a life systems which (a)are intended for surgical implant support device or system whose failure to perform can into the body or (b)support or sustain life and whose be reasonably expected to cause the failure of the life failure to perform when properly used in accordance support device or system or to affect its safety or with instructions for use provided in the labeling can effectivenessbe reasonably expected to result in a significant injury to the userNational Semiconductor National Semiconductor National Semiconductor National Semiconductor National Semiconductores National Semiconductor CorporationGmbHJapan LtdHong Kong LtdDo Brazil Ltda(Australia)Pty Ltd 2900Semiconductor DriveLivry-Gargan-Str 10Sumitomo Chemical13th Floor Straight Block Rue Deputado Lacorda Franco Building 16。

MC74LVX04 高速 CMOS 六路非 gates 数据手册说明书

MC74LVXU04Hex Inverter(Unbuffered)The MC74LVX04 is an advanced high speed CMOS unbuffered hex inverter. The inputs tolerate voltages up to 7.0 V , allowing the interface of 5.0 V systems to 3.0 V systems.Features•High Speed: t PD = 4.1 ns (Typ) at V CC = 3.3 V•Low Power Dissipation: I CC = 2 m A (Max) at T A = 25°C •Power Down Protection Provided on Inputs •Balanced Propagation Delays •Low Noise: V OLP = 0.5 V (Max)•Pin and Function Compatible with Other Standard Logic Families •These Devices are Pb−Free and are RoHS CompliantFigure 1. Logic DiagramO0A0O1A1O2A2O3A3O4A4O5A5See detailed ordering and shipping information in the package dimensions section on page 4 of this data sheet.ORDERING INFORMATIONMARKING DIAGRAMSTSSOP−14DT SUFFIXCASE 948GSOIC−14 NB D SUFFIXCASE 751ALVX U04ALYW G G 114LVXU04= Specific Device Code A = Assembly Location WL, L = Wafer Lot Y= YearWW, W = Work WeekG or G= Pb−Free Package(Note: Microdot may be in either location)TSSOP−14SOIC−14 NB1314121110982134567V CC A5O5A4O4A3O3A0O0A1O1A2O2GNDPIN ASSIGNMENT14−Lead (Top View)MAXIMUM RATINGSSymbol Parameter Value Unit V CC DC Supply Voltage−0.5 to +7.0V V IN DC Input Voltage−0.5 to +7.0V V OUT DC Output Voltage−0.5 to V CC+ 0.5VI IK DC Input Diode Current V I < GND−20mAI OK DC Output Diode Current V O < GND±20mAI OUT DC Output Sink Current±25mAI CC DC Supply Current per Supply Pin±50mA T STG Storage Temperature Range−65 to +150_C T L Lead Temperature, 1 mm from Case for 10 Seconds260_C T J Junction Temperature under Bias+150_C q JA Thermal Resistance SOICTSSOP250_C/WP D Power Dissipation in Still Air at 85_C SOICTSSOP250mW MSL Moisture Sensitivity Level 1F R Flammability Rating Oxygen Index: 30% − 35%UL94−**********V ESD ESD Withstand Voltage Human Body Model (Note 1)Machine Model (Note 2)Charged Device Model (Note 3)> 2000> 2002000VI Latchup Latchup Performance Above V CC and Below GND at 85_C (Note 4)±300mA Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.1.Tested to EIA/JESD22−A114−A.2.Tested to EIA/JESD22−A115−A.3.Tested to JESD22−C101−A.4.Tested to EIA/JESD78.RECOMMENDED OPERATING CONDITIONSSymbol Parameter Min Max Unit V CC Supply Voltage 2.0 3.6V V I Input Voltage(Note 5)0 5.5V V O Output Voltage(HIGH or LOW State)0V CC V T A Operating Free−Air Temperature−40+85_CD t/D V Input Transition Rise or Fall Rate V CC = 3.0 V ±0.3 V0100ns/V Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.5.Unused inputs may not be left open. All inputs must be tied to a high− or low−logic input voltage level.DC ELECTRICAL CHARACTERISTICSSymbol Parameter Test Conditions V CCVT A = 25°C T A = −40 to 85°CUnit Min Typ Max Min MaxV IH High−Level Input Voltage 2.03.03.61.52.02.41.52.02.4VV IL Low−Level Input Voltage 2.03.03.60.50.80.80.50.80.8VV OH High−Level Output Voltage (V in = V IH or V IL)I OH = −50 m AI OH = −50 m AI OH = −4 mA2.03.03.01.92.92.582.03.01.92.92.48VV OL Low−Level Output Voltage (V in = V IH or V IL)I OL = 50 m AI OL = 50 m AI OL = 4 mA2.03.03.00.00.00.10.10.360.10.10.44VI in Input Leakage Current V in = 5.5 V or GND 3.6±0.1±1.0m AI CC Quiescent Supply Current V in = V CC or GND 3.6 2.020.0m A AC ELECTRICAL CHARACTERISTICS (Input t r = t f= 3.0ns)Symbol Parameter Test ConditionsT A = 25°C T A = −40 to 85°CUnit Min Typ Max Min Maxt PLH, t PHL Propagation Delay, Input toOutputV CC = 2.7V C L = 15 pFC L = 50 pF5.47.910.113.61.01.012.516.0nsV CC = 3.3 ± 0.3V C L = 15 pFC L = 50 pF4.16.66.29.71.01.07.511.0t OSHL t OSLH Output−to−Output Skew(Note 6)V CC = 2.7V C L = 50 pFV CC = 3.3 ±0.3V C L = 50 pF1.51.51.51.5ns6.Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device.The specification applies to any outputs switching in the same direction, either HIGH−to−LOW (t OSHL) or LOW−to−HIGH (t OSLH); parameter guaranteed by design.CAPACITIVE CHARACTERISTICSSymbol ParameterT A = 25°C T A = −40 to 85°CUnit Min Typ Max Min MaxCin Input Capacitance41010pFC PD Power Dissipation Capacitance (Note 7)18pF7.C PD is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load.Average operating current can be obtained by the equation: I CC(OPR) = C PD V CC f in + I CC/6 (per buffer). C PD is used to determine the no−load dynamic power consumption; P D = C PD V CC2 f in + I CC V CC.NOISE CHARACTERISTICS (Input t r = t f = 3.0 ns, C L = 50 pF, V CC = 3.3 V, Measured in SOIC Package)Symbol CharacteristicT A = 25°CUnit Typ MaxV OLP Quiet Output Maximum Dynamic V OL0.30.5V V OLV Quiet Output Minimum Dynamic V OL−0.3−0.5V V IHD Minimum High Level Dynamic Input Voltage 2.0V V ILD Maximum Low Level Dynamic Input Voltage0.8VFigure 2. Switching Waveforms V CCGNDAO*Includes all probe and jig capacitanceFigure 3. Test CircuitC L *ORDERING INFORMATIONDevicePackage Shipping †MC74LVXU04DG SOIC−14 NB (Pb−Free)55 Units / Rail MC74LVXU04DR2G SOIC−14 NB (Pb−Free)2500 Tape & Reel MC74LVXU04DTG TSSOP−14(Pb−Free)96 Units / Rail MC74LVXU04DTR2GTSSOP−14(Pb−Free)2500 Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.SOIC −14 NB CASE 751A −03ISSUE LDATE 03 FEB 2016SCALE 1:1GENERICMARKING DIAGRAM*XXXXX = Specific Device Code A = Assembly Location WL = Wafer Lot Y = YearWW = Work WeekG= Pb −Free PackageSTYLES ON PAGE 2NOTES:1.DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.2.CONTROLLING DIMENSION: MILLIMETERS.3.DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF AT MAXIMUM MATERIAL CONDITION.4.DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSIONS.5.MAXIMUM MOLD PROTRUSION 0.15 PERSIDE.DETAIL ADIM MIN MAX MIN MAX INCHESMILLIMETERS D 8.558.750.3370.344E 3.80 4.000.1500.157A 1.35 1.750.0540.068b 0.350.490.0140.019L 0.40 1.250.0160.049e 1.27 BSC 0.050 BSC A30.190.250.0080.010A10.100.250.0040.010M0 7 0 7 H 5.80 6.200.2280.244h 0.250.500.0100.019____14X0.581.27PITCH*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.*This information is generic. Please refer to device data sheet for actual part marking.Pb −Free indicator, “G” or microdot “G ”, may or may not be present. Some products may not follow the Generic Marking.MECHANICAL CASE OUTLINEPACKAGE DIMENSIONSSOIC −14CASE 751A −03ISSUE LDATE 03 FEB 2016STYLE 7:PIN 1.ANODE/CATHODEMON ANODEMON CATHODE4.ANODE/CATHODE5.ANODE/CATHODE6.ANODE/CATHODE7.ANODE/CATHODE8.ANODE/CATHODE9.ANODE/CATHODE 10.ANODE/CATHODE MON CATHODE MON ANODE 13.ANODE/CATHODE 14.ANODE/CATHODESTYLE 5:PIN MON CATHODE2.ANODE/CATHODE3.ANODE/CATHODE4.ANODE/CATHODE5.ANODE/CATHODE6.NO CONNECTIONMON ANODEMON CATHODE9.ANODE/CATHODE 10.ANODE/CATHODE 11.ANODE/CATHODE 12.ANODE/CATHODE 13.NO CONNECTION MON ANODESTYLE 6:PIN 1.CATHODE2.CATHODE3.CATHODE4.CATHODE5.CATHODE6.CATHODE7.CATHODE8.ANODE9.ANODE 10.ANODE 11.ANODE 12.ANODE 13.ANODE 14.ANODESTYLE 1:PIN MON CATHODE2.ANODE/CATHODE3.ANODE/CATHODE4.NO CONNECTION5.ANODE/CATHODE6.NO CONNECTION7.ANODE/CATHODE8.ANODE/CATHODE9.ANODE/CATHODE 10.NO CONNECTION 11.ANODE/CATHODE 12.ANODE/CATHODE 13.NO CONNECTION MON ANODE STYLE 3:PIN 1.NO CONNECTION2.ANODE3.ANODE4.NO CONNECTION5.ANODE6.NO CONNECTION7.ANODE8.ANODE9.ANODE10.NO CONNECTION 11.ANODE 12.ANODE13.NO CONNECTION MON CATHODE STYLE 4:PIN 1.NO CONNECTION2.CATHODE3.CATHODE4.NO CONNECTION5.CATHODE6.NO CONNECTION7.CATHODE8.CATHODE9.CATHODE10.NO CONNECTION 11.CATHODE 12.CATHODE13.NO CONNECTION MON ANODE STYLE 8:PIN MON CATHODE2.ANODE/CATHODE3.ANODE/CATHODE4.NO CONNECTION5.ANODE/CATHODE6.ANODE/CATHODEMON ANODEMON ANODE9.ANODE/CATHODE 10.ANODE/CATHODE 11.NO CONNECTION 12.ANODE/CATHODE 13.ANODE/CATHODE MON CATHODESTYLE 2:CANCELLEDTSSOP −14 WBCASE 948G ISSUE CDATE 17 FEB 2016SCALE 2:1DIM MIN MAX MIN MAX INCHES MILLIMETERS A 4.90 5.100.1930.200B 4.30 4.500.1690.177C −−− 1.20−−−0.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSC H 0.500.600.0200.024J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M0 8 0 8 NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBARPROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY .7.DIMENSION A AND B ARE TO BEDETERMINED AT DATUM PLANE −W −.____14X REF GENERICMARKING DIAGRAM*XXXX XXXX ALYW G G 114A = Assembly Location L = Wafer Lot Y = YearW = Work WeekG= Pb −Free Package14X0.360.65PITCHSOLDERING FOOTPRINT(Note: Microdot may be in either location)*This information is generic. Please refer to device data sheet for actual part marking.Pb −Free indicator, “G” or microdot “G ”, may or may not be present. Some products may not follow the Generic Marking.MECHANICAL CASE OUTLINEPACKAGE DIMENSIONSPUBLICATION ORDERING INFORMATIONTECHNICAL SUPPORTLITERATURE FULFILLMENT:。

M74VHC1G126DFT1G资料

MC74VHC1G126Noninverting 3−State BufferThe MC74VHC1G126 is an advanced high speed CMOS noninverting 3−state buffer fabricated with silicon gate CMOS technology. It achieves high speed operation similar to equivalent Bipolar Schottky TTL while maintaining CMOS low power dissipation.The internal circuit is composed of three stages, including a buffered 3−state output which provides high noise immunity and stable output.The MC74VHC1G126 input structure provides protection when voltages up to 7.0 V are applied, regardless of the supply voltage. This allows the MC74VHC1G126 to be used to interface 5.0 V circuits to 3.0 V circuits.Features•High Speed: t PD = 3.5 ns (Typ) at V CC = 5.0 V•Low Power Dissipation: I CC = 1 m A (Max) at T A = 25°C •Power Down Protection Provided on Inputs •Balanced Propagation Delays•Pin and Function Compatible with Other Standard Logic Families •Chip Complexity: FETs = 58; Equivalent Gates = 15•Pb−Free Packages are AvailableFigure 1. Pinout (Top View)V CCOE IN A OUT YGND IN AOUT YOE Figure 2. Logic SymbolSee detailed ordering and shipping information in the package dimensions section on page 4 of this data sheet.ORDERING INFORMATIONMAXIMUM RATINGSSymbol Characteristics Value Unit V CC DC Supply Voltage−0.5 to +7.0V V IN DC Input Voltage−0.5 to +7.0VV OUT DC Output Voltage V CC = 0High or Low State−0.5 to 7.0−0.5 to V CC + 0.5VI IK Input Diode Current−20mA I OK Output Diode Current V OUT < GND; V OUT > V CC+20mA I OUT DC Output Current, per Pin+25mA I CC DC Supply Current, V CC and GND+50mA P D Power dissipation in still air SC−88A, TSOP−5200mW q JA Thermal resistance SC−88A, TSOP−5333°C/W T L Lead temperature, 1 mm from case for 10 s260°C T J Junction temperature under bias+150°C T stg Storage temperature−65 to +150°CV ESD ESD Withstand Voltage Human Body Model (Note 1)Machine Model (Note 2)Charged Device Model (Note 3)> 2000> 200N/AVI Latchup Latchup Performance Above V CC and Below GND at 125°C (Note 4)±500mA Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.1.Tested to EIA/JESD22−A114−A2.Tested to EIA/JESD22−A115−A3.Tested to JESD22−C101−A4.Tested to EIA/JESD78RECOMMENDED OPERATING CONDITIONSSymbol Characteristics Min Max Unit V CC DC Supply Voltage 2.0 5.5V V IN DC Input Voltage0.0 5.5V V OUT DC Output Voltage0.0V CC VT A Operating Temperature Range−55+125°Ct r, t f Input Rise and Fall Time V CC = 3.3 V ± 0.3 VV CC = 5.0 V ± 0.5 V 010020ns/VDevice Junction Temperature versusTime to 0.1% Bond FailuresJunctionTemperature °C Time, Hours Time, Years 801,032,200117.890419,30047.9100178,70020.411079,6009.4 12037,000 4.2 13017,800 2.0 1408,900 1.011101001000TIME, YEARSNORMALIZEDFAILURERATEFigure 3. Failure Rate vs. TimeJunction TemperatureDC ELECTRICAL CHARACTERISTICSSymbol Parameter Test Conditions V CC(V)T A = 25°C T A≤ 85°C−55 ≤ T A≤ 125°CUnit Min Typ Max Min Max Min MaxV IH Minimum High−LevelInput Voltage 2.03.04.55.51.52.13.153.851.52.13.153.851.52.13.153.85VV IL Maximum Low−LevelInput Voltage 2.03.04.55.50.50.91.351.650.50.91.351.650.50.91.351.65VV OH Minimum High−LevelOutput VoltageV IN = V IH or V IL V IN = V IH or V ILI OH = −50 m A2.03.04.51.92.94.42.03.04.51.92.94.41.92.94.4VV IN = V IH or V ILI OH = −4 mAI OH = −8 mA3.04.52.583.942.483.802.343.66VV OL Maximum Low−LevelOutput VoltageV IN = V IH or V IL V IN = V IH or V ILI OL = 50 m A2.03.04.50.00.00.00.10.10.10.10.10.10.10.10.1VV IN = V IH or V ILI OL = 4 mAI OL = 8 mA3.04.50.360.360.440.440.520.52VI OZ Maximum 3−StateLeakage Current V IN = V IH or V ILV OUT = V CC or GND5.5±0.25±2.5±2.5m AI IN Maximum InputLeakage Current V IN = 5.5 V or GND0 to5.5±0.1±1.0±1.0m AI CC Maximum QuiescentSupply CurrentV IN = V CC or GND 5.5 1.02040m A AC ELECTRICAL CHARACTERISTICS C load = 50 pF, Input t r = t f= 3.0 nsSymbol Parameter Test ConditionsT A = 25°C T A≤ 85°C−55 ≤ T A≤ 125°CUnit Min Typ Max Min Max Min Maxt PLH, t PHL Maximum PropagationDelay,Input A to Y(Figures 3. and 5.)V CC = 3.3 ± 0.3 V C L = 15 pFC L = 50 pF4.56.48.011.59.513.012.016.0nsV CC = 5.0 ± 0.5 V C L = 15 pFC L = 50 pF3.54.55.57.56.58.58.510.5t PZL, t PZH Maximum OutputEnable Time,Input OE to Y(Figures 4. and 5.)V CC = 3.3 ± 0.3 V C L = 15 pFR L = 1000 W C L = 50 pF4.56.48.011.59.513.011.515.0nsV CC = 5.0 ± 0.5 V C L = 15 pFR L = 1000 W C L = 50 pF3.54.55.17.16.08.08.510.5t PLZ, t PHZ Maximum OutputDisable Time,Input OE to Y(Figures 4. and 5.)V CC = 3.3 ± 0.3 V C L = 15 pFR L = 1000 W C L = 50 pF6.58.09.713.211.515.014.518.0nsV CC = 5.0 ± 0.5 V C L = 15 pFR L = 1000 W C L = 50 pF4.87.06.88.88.010.010.012.0C IN Maximum InputCapacitance4.0101010pFC OUT Maximum 3−State OutputCapacitance (Output inHigh Impedance State)6.0pFC PD Power Dissipation Capacitance (Note 5)Typical @ 25°C, V CC = 5.0 VpF8.05.C PD is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load.Average operating current can be obtained by the equation: I CC(OPR) = C PD V CC f in + I CC. C PD is used to determine the no−load dynamic power consumption; P D = C PD V CC2 f in + I CC V CC.SWITCHING WAVEFORMSY V CCGND HIGH IMPEDANCECC WHENPZL.PZH. HIGH IMPEDANCEAFigure 8. Input Equivalent CircuitDEVICE ORDERING INFORMATIONDevice Order Number Package Type Tape and Reel Size†MC74VHC1G126DFT1SC−88A/SOT−353/SC−70178 mm (7”)3000 Units / Tape & ReelM74VHC1G126DFT1G SC−88A/SOT−353/SC−70(Pb−Free)178 mm (7”)3000 Units / Tape & ReelMC74VHC1G126DFT2SC−88A/SOT−353/SC−70178 mm (7”)3000 Units / Tape & ReelM74VHC1G126DFT2G SC−88A/SOT−353/SC−70(Pb−Free)178 mm (7”)3000 Units / Tape & ReelMC74VHC1G126DTT1TSOP−5/SOT−23/SC−59178 mm (7”)3000 Units / Tape & ReelM74VHC1G126DTT1G TSOP−5/SOT−23/SC−59(Pb−Free)178 mm (7”)3000 Units / Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.3.419A−01 OBSOLETE. NEW STANDARD 419A−02.4.DIMENSIONS A AND B DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS.DIM A MIN MAX MIN MAX MILLIMETERS1.802.200.0710.087INCHES B 1.15 1.350.0450.053C 0.80 1.100.0310.043D 0.100.300.0040.012G 0.65 BSC 0.026 BSC H −−−0.10−−−0.004J 0.100.250.0040.010K 0.100.300.0040.012N 0.20 REF 0.008 REF S2.00 2.200.0790.087SC−88A / SOT−353 / SC70CASE 419A−02ISSUE Hǒmm inchesǓ*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*TSOP−5 / SOT23−5 / SC59−5DT SUFFIX CASE 483−02ISSUE D*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH THICKNESS. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL.4. A AND B DIMENSIONS DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS.DIM MIN MAX MIN MAX INCHESMILLIMETERS A 2.90 3.100.11420.1220B 1.30 1.700.05120.0669C 0.90 1.100.03540.0433D 0.250.500.00980.0197G 0.85 1.050.03350.0413H 0.0130.1000.00050.0040J 0.100.260.00400.0102K 0.200.600.00790.0236L 1.25 1.550.04930.0610M 0 10 0 10 S2.503.000.09850.1181____ǒmm inchesǓON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

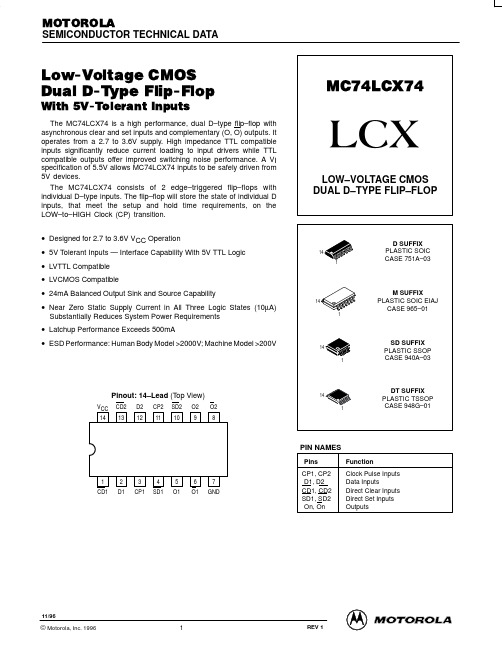

MC74LCX74中文资料

* Absolute maximum continuous ratings are those values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation under absolute–maximum–rated conditions is not implied. 1. Output in HIGH or LOW State. IO absolute maximum rating must be observed.

DC ELECTRICAL CHARACTERISTICS

TA = –40°C to +85°C Symbol VIH VIL VOH Characteristic HIGH Level Input Voltage (Note 2.) LOW Level Input Voltage (Note 2.) HIGH Level Output Voltage Condition 2.7V ≤ VCC ≤ 3.6V 2.7V ≤ VCC ≤ 3.6V 2.7V ≤ VCC ≤ 3.6V; IOH = –100µA VCC = 2.7V; IOH = –12mA VCC = 3.0V; IOH = –18mA VCC = 3.0V; IOH = –24mA VOL LOW Level Output Voltage 2.7V ≤ VCC ≤ 3.6V; IOL = 100µA VCC = 2.7V; IOL= 12mA VCC = 3.0V; IOL = 16mA VCC = 3.0V; IOL = 24mA 2. These values of VI are used to test DC electrical characteristics only. VCC – 0.2 2.2 2.4 2.2 0.2 0.4 0.4 0.55 V Min 2.0 0.8 Max Unit V V V

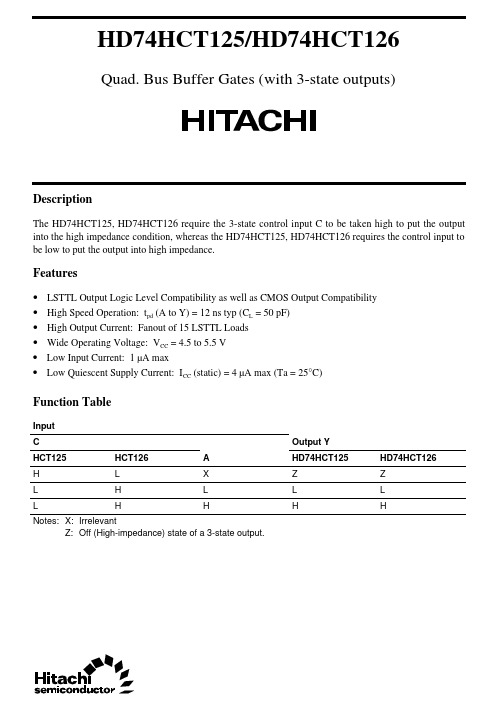

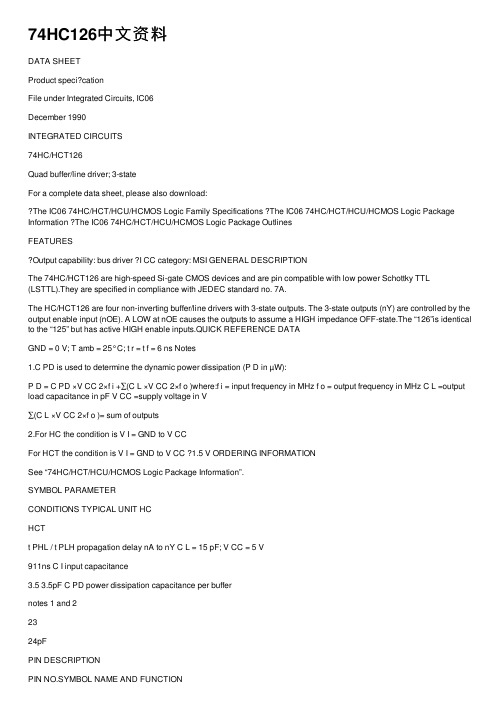

HD74HCT126中文资料

HD74HCT125/HD74HCT126Quad. Bus Buffer Gates (with 3-state outputs)DescriptionThe HD74HCT125, HD74HCT126 require the 3-state control input C to be taken high to put the output into the high impedance condition, whereas the HD74HCT125, HD74HCT126 requires the control input to be low to put the output into high impedance.Features• LSTTL Output Logic Level Compatibility as well as CMOS Output Compatibility• High Speed Operation: t pd (A to Y) = 12 ns typ (C L = 50 pF)• High Output Current: Fanout of 15 LSTTL Loads• Wide Operating Voltage: V CC = 4.5 to 5.5 V• Low Input Current: 1 µA max• Low Quiescent Supply Current: I CC (static) = 4 µA max (Ta = 25°C)Function TableInputC Output YHCT125HCT126A HD74HCT125HD74HCT126H L X Z ZL H L L LL H H H HNotes:X:IrrelevantZ:Off (High-impedance) state of a 3-state output.HD74HCT125/HD74HCT126 Pin ArrangementHD74HCT125HD74HCT1262HD74HCT125/HD74HCT1263Absolute Maximum RatingsItemSymbol Rating Unit Supply voltage range V CC –0.5 to +7.0V Input voltage V IN –0.5 to V CC + 0.5V Output voltage V OUT –0.5 to V CC + 0.5V Output currentI OUT ±35mA DC current drain per V CC , GND I CC , I GND ±75mA DC input diode current I IK ±20mA DC output diode current I OK ±20mA Power dissipation per package P T 500mW Storage temperatureTstg–65 to +150°CDC CharacteristicsTa = 25°CTa = –40 to +85°CTest Conditions Item Symbol Min Typ Max MinMax Unit V CC (V)Input voltageV IH 2.0——2.0—V 4.5 to 5.5V IL——0.8—0.8V 4.5 to 5.5Output voltageV OH 4.4—— 4.4—V4.5Vin = V IH or V IL I OH = –20 µA4.18——4.13— 4.5I OH = –6 mAV OL——0.1—0.1V 4.5Vin = V IH or V IL I OL = 20 µA——0.26—0.33 4.5I OL = 6 mAOff-state output current I OZ ——±0.5—±5.0µA 5.5Vin = V IH or V IL ,Vout = V CC or GND Input current Iin ——±0.1—±1.0µA 5.5Vin = V CC or GNDQuiescent supply currentI CC——4.0—40µA 5.5Vin = V CC or GND, Iout = 0 µAHD74HCT125/HD74HCT1264AC Characteristics (C L = 50 pF, Input t r = t f = 6 ns)Ta = 25°CTa = –40 to +85°CTest Conditions Item Symbol Min Typ Max MinMax Unit V CC (V)Propagation delay t PHL—1220—25ns4.5timet PLH —1220—25 4.5Output enable t ZL —1230—38ns 4.5timet ZH —1230—38 4.5Output disable t LZ —1530—38ns 4.5timet HZ —1530—38 4.5Output rise/fall t TLH —412—15ns 4.5timet THL —412—15 4.5Input capacitanceCin—510—10pF —Hitachi CodeJEDECEIAJWeight (reference value)DP-14ConformsConforms0.97 gUnit: mm元器件交易网Hitachi CodeJEDECEIAJWeight (reference value)FP-14DA —Conforms 0.23 g*Dimension including the plating thickness Base material dimension° – 8°Hitachi CodeJEDEC EIAJWeight (reference value)FP-14DN Conforms Conforms 0.13 g° – 8°*Pd platingHitachi CodeJEDECEIAJWeight (reference value)TTP-14D ——0.05 g*Dimension including the plating thickness Base material dimensionCautions1.Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,copyright, trademark, or other intellectual property rights for information contained in this document.Hitachi bears no responsibility for problems that may arise with third party’s rights, includingintellectual property rights, in connection with use of the information contained in this document.2.Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.3.Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,contact Hitachi’s sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,traffic, safety equipment or medical equipment for life support.4.Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installationconditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.5.This product is not designed to be radiation resistant.6.No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.7.Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor products.Hitachi, Ltd.Semiconductor & Integrated Circuits.Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109Copyright ' Hitachi, Ltd., 1999. All rights reserved. Printed in Japan.Hitachi Asia Pte. Ltd.16 Collyer Quay #20-00Hitachi TowerSingapore 049318Tel: 535-2100Fax: 535-1533URLNorthAmerica : http:/Europe : /hel/ecg Asia (Singapore): .sg/grp3/sicd/index.htm Asia (Taiwan): /E/Product/SICD_Frame.htm Asia (HongKong): /eng/bo/grp3/index.htm Japan : http://www.hitachi.co.jp/Sicd/indx.htmHitachi Asia Ltd.Taipei Branch Office3F, Hung Kuo Building. No.167, Tun-Hwa North Road, Taipei (105)Tel: <886> (2) 2718-3666Fax: <886> (2) 2718-8180Hitachi Asia (Hong Kong) Ltd.Group III (Electronic Components)7/F., North Tower, World Finance Centre,Harbour City, Canton Road, Tsim Sha Tsui,Kowloon, Hong Kong Tel: <852> (2) 735 9218Fax: <852> (2) 730 0281 Telex: 40815 HITEC HXHitachi Europe Ltd.Electronic Components Group.Whitebrook ParkLower Cookham Road MaidenheadBerkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000Fax: <44> (1628) 778322Hitachi Europe GmbHElectronic components Group Dornacher Stra§e 3D-85622 Feldkirchen, Munich GermanyTel: <49> (89) 9 9180-0Fax: <49> (89) 9 29 30 00Hitachi Semiconductor (America) Inc.179 East Tasman Drive,San Jose,CA 95134 Tel: <1> (408) 433-1990Fax: <1>(408) 433-0223For further information write to:。

MC74HC163AD中文资料

1 9 7 10 Pin 16 = VCC Pin 8 = GND

FUNCTION TABLE

Inputs Clock Reset* L H H H H Load X L H H H Enable P X X H L X Enable T X X H X L Output Q Reset Load Preset Data Count No Count No Count 1 2 3 P0 4 P1 5 P2 6 P3 7 8 Enable GND P

v

v

Lead Temperature, 1 mm from Case for 10 Seconds Plastic DIP or SOIC Package Ceramic DIP

* Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recommended Operating Conditions. †Derating — Plastic DIP: – 10 mW/_C from 65_ to 125_C Ceramic DIP: – 10 mW/_C from 100_ to 125_C SOIC Package: – 7 mW/_C from 65_ to 125_C For high frequency or heavy load considerations, see Chapter 2 of the Motorola High–Speed CMOS Data Book (DL129/D).

元器件交易网

MOTOROLA

74F125中文资料

元器件交易网DIP14:plastic dual in-line package; 14 leads (300 mil)SOT27-1SO14:plastic small outline package; 14 leads; body width 3.9 mm SOT108-1NOTESDefinitionsShort-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.DisclaimersLife support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.Philips Semiconductors811 East Arques AvenueP.O. Box 3409Sunnyvale, California 94088–3409Telephone 800-234-7381© Copyright Philips Electronics North America Corporation 1998All rights reserved. Printed in U.S.A.print code Date of release: 10-98。

74126中文资料

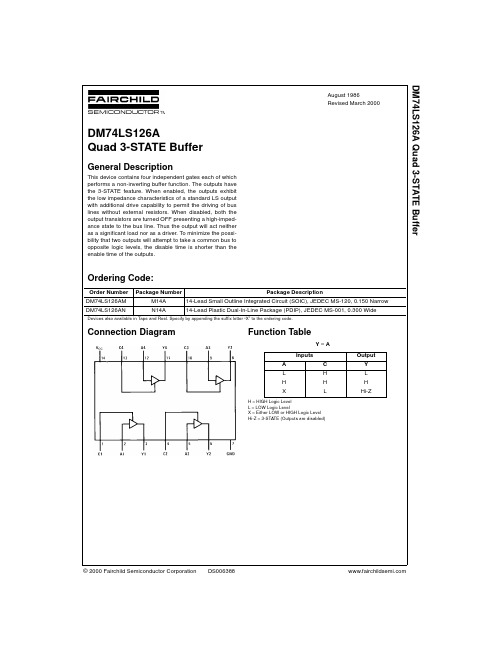

© 2000 Fairchild Semiconductor Corporation DS006388August 1986Revised March 2000DM74LS126A Quad 3-STATE BufferDM74LS126AQuad 3-STATE BufferGeneral DescriptionThis device contains four independent gates each of which performs a non-inverting buffer function. The outputs have the 3-STATE feature. When enabled, the outputs exhibit the low impedance characteristics of a standard LS output with additional drive capability to permit the driving of bus lines without external resistors. When disabled, both the output transistors are turned OFF presenting a high-imped-ance state to the bus line. Thus the output will act neither as a significant load nor as a driver. To minimize the possi-bility that two outputs will attempt to take a common bus to opposite logic levels, the disable time is shorter than the enable time of the outputs.Ordering Code:Devices also available in T ape and Reel. Specify by appending the suffix letter “X” to the ordering code.Connection Diagram Function TableY = AH = HIGH Logic Level L = LOW Logic LevelX = Either LOW or HIGH Logic Level Hi-Z = 3-STATE (Outputs are disabled)Order Number Package NumberPackage DescriptionDM74LS126AM M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow DM74LS126ANN14A14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 WideInputs Output A C Y L H L H H H XLHi-Z 2D M 74L S 126AAbsolute Maximum Ratings (Note 1)Note 1: The “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings.The “Recommended Operating Conditions” table will define the conditions for actual device operation.Recommended Operating ConditionsElectrical Characteristicsover recommended operating free air temperature range (unless otherwise noted)Note 2: All typicals are at V CC = 5V, T A = 25°C.Note 3: Not more than one output should be shorted at a time, and the duration should not exceed one second.Switching CharacteristicsV CC = 5V, T A = 25°CNote 4: C L = 5pF.Supply Voltage 7V Input Voltage7VOperating Free Air Temperature Range 0°C to +70°C Storage Temperature Range−65°C to +150°CSymbol ParameterMin Nom Max Units V CC Supply Voltage4.7555.25V V IH HIGH Level Input Voltage V V IL LOW Level Input Voltage 0.8V I OH HIGH Level Output Current −2.6mA I OL LOW Level Output Current 24mA T AFree Air Operating Temperature70°CSymbol ParameterConditionsMinTyp Max Units (Note 2)V I Input Clamp Voltage V CC = Min, I I = −18 mA −1.5V V OH HIGH Level V CC = Min, I OH = Max 2.4VOutput Voltage V IH = MinV OLLOW Level V CC = Min, I OL = Max0.350.5Output VoltageV IL = Max, V IH = Min VI OL = 12 mA, V CC = Min 0.250.4I I Input Current @ Max Input Voltage V CC = Max, V I = 7V 0.1mA I IH HIGH Level Input Current V CC = Max, V I = 2.7V 20µA I IL LOW Level Input Current V CC = Max, V I = 0.4V −0.4mA I OZH Off-State Output Current with V CC = Max, V O = 2.4V 20µA HIGH Level Output Voltage Applied V IH = Min, V IL = Max I OZL Off-State Output Current with V CC = Max, V O = 0.4V −20µA LOW Level Output Voltage Applied V IH = Min, V IL = Max I OS Short Circuit Output Current V CC = Max (Note 3)−20−100mA I CCSupply CurrentV CC = Max1222mAR L = 667ΩSymbol ParameterC L = 50 pF C L = 150 pF UnitsMinMax MinMax t PLH Propagation Delay Time LOW-to-HIGH Level Output 1521ns t PHL Propagation Delay Time HIGH-to-LOW Level Output 1822ns t PZH Output Enable Time to HIGH Level Output 3036ns t PZL Output Enable Time to LOW Level Output3042ns t PHZ Output Disable Time from HIGH Level Output (Note 4)25ns t PLZOutput Disable Time from LOW Level Output (Note 4)25nsDM74LS126APhysical Dimensions inches (millimeters) unless otherwise noted14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 NarrowPackage Number M14A4D M 74L S 126A Q u a d 3-S T A TE B u f f e rPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 WidePackage Number N14AFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user. 2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。

74系列芯片中文资料(非常全)

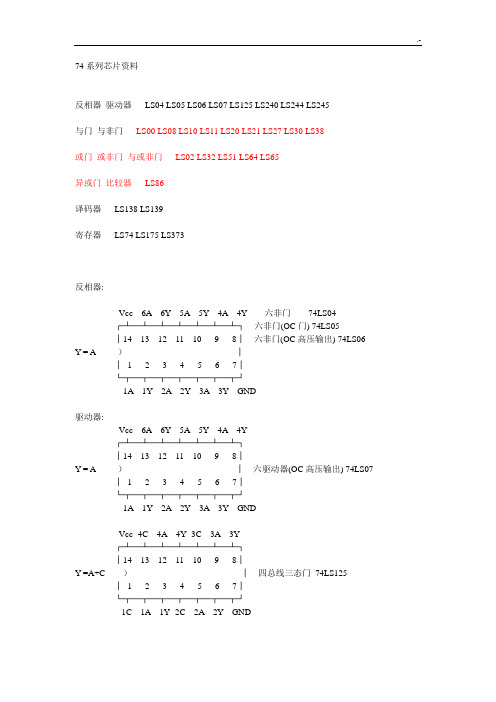

74系列芯片资料反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38或门或非门与或非门LS02 LS32 LS51 LS64 LS65异或门比较器LS86译码器LS138 LS139寄存器LS74 LS175 LS373反相器:Vcc 6A 6Y 5A 5Y 4A 4Y 六非门74LS04┌┴─┴─┴─┴─┴─┴─┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )││1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GND驱动器:Vcc 6A 6Y 5A 5Y 4A 4Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = A )│六驱动器(OC高压输出) 74LS07 │1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GNDVcc -4C 4A 4Y -3C 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐_ │14 13 12 11 10 9 8│Y =A+C )│四总线三态门74LS125 │1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘-1C 1A 1Y -2C 2A 2Y GNDVcc -G B1 B2 B3 B4 B8 B6 B7 B8┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8位总线驱动器74LS245 │20 19 18 17 16 15 14 13 12 11│)│DIR=1 A=>B│1 2 3 4 5 6 7 8 9 10│DIR=0 B=>A└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘DIR A1 A2 A3 A4 A5 A6 A7 A8 GND正逻辑与门,与非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = AB )│2输入四正与门74LS08 │1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐__ │14 13 12 11 10 9 8│Y = AB )│2输入四正与非门74LS00 │1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 1C 1Y 3C 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐___ │14 13 12 11 10 9 8│Y = ABC )│3输入三正与非门74LS10 │1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 2A 2B 2C 2Y GNDVcc H G Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│8输入与非门74LS30│1 2 3 4 5 6 7│________└┬─┬─┬─┬─┬─┬─┬┘Y = ABCDEFGHA B C D E F GND正逻辑或门,或非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐2输入四或门74LS32│14 13 12 11 10 9 8│)│Y = A+B│1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4Y 4B 4A 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐2输入四或非门74LS02│14 13 12 11 10 9 8│___)│Y = A+B│1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Y 1A 1B 2Y 2A 2B GNDVcc 2Y 2B 2A 2D 2E 1F┌┴─┴─┴─┴─┴─┴─┴┐双与或非门74S51│14 13 12 11 10 9 8│_____)│2Y = AB+DE│1 2 3 4 5 6 7│_______└┬─┬─┬─┬─┬─┬─┬┘1Y = ABC+DEF1Y 1A 1B 1C 1D 1E GNDVcc D C B K J Y┌┴─┴─┴─┴─┴─┴─┴┐4-2-3-2与或非门74S64 74S65(OC门) │14 13 12 11 10 9 8│______________)│Y = ABCD+EF+GHI+JK│1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘A E F G H I GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器2输入四异或门74LS86Vcc 4B 4A 4Y 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│_ _│1 2 3 4 5 6 7│Y=AB+AB└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2Y 2A 2B GND8*2输入比较器74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8*2输入比较器74LS688│20 19 18 17 16 15 14 13 12 11│)││1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B83-8译码器74LS138Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6 __ _ _ _ __ _ _ __ _ _ __ _┌┴─┴─┴─┴─┴─┴─┴─┴┐Y0=A B C Y1=A B C Y2=A B C Y3=A B C│16 15 14 13 12 11 10 9 │)│__ _ _ __ _ __ _ __│1 2 3 4 5 6 7 8│Y4=A B C Y5=A B C Y6=A B C Y7=A B C└┬─┬─┬─┬─┬─┬─┬─┬┘A B C -CS0 -CS1 CS2 -Y7 GND双2-4译码器74LS139Vcc -2G 2A 2B -Y0 -Y1 -Y2 -Y3 __ __ __ __ __ __ __ __┌┴─┴─┴─┴─┴─┴─┴─┴┐Y0=2A 2B Y1=2A 2B Y2=2A 2B Y3=2A 2B│16 15 14 13 12 11 10 9 │)│__ __ __ __ __ __ __ __│ 1 2 3 4 5 6 7 8│Y0=1A 1B Y1=1A 1B Y2=1A 1B Y3=1A 1B└┬─┬─┬─┬─┬─┬─┬─┬┘-1G 1A 1B -Y0 -Y1 -Y2 -Y3 GND8*2输入比较器74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8*2输入比较器74LS688 │20 19 18 17 16 15 14 13 12 11│)││1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8寄存器:Vcc 2CR 2D 2Ck 2St 2Q -2Q┌┴─┴─┴─┴─┴─┴─┴┐双D触发器74LS74│14 13 12 11 10 9 8 │)││1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Cr 1D 1Ck 1St 1Q -1Q GNDVcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8位锁存器74LS373│20 19 18 17 16 15 14 13 12 11│)││1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘-OE 1Q 1D 2D 2Q 3Q 3D 4D 4Q GND--------------------------------------------------------------------------------常见数字逻辑器件中文注解74系列:74LS00 TTL 2输入端四与非门74LS01 TTL 集电极开路2输入端四与非门74LS02 TTL 2输入端四或非门74LS03 TTL 集电极开路2输入端四与非门74LS04 TTL 六反相器74LS05 TTL 集电极开路六反相器74LS06 TTL 集电极开路六反相高压驱动器74LS07 TTL 集电极开路六正相高压驱动器74LS08 TTL 2输入端四与门74LS09 TTL 集电极开路2输入端四与门74LS10 TTL 3输入端3与非门74LS107 TTL 带清除主从双J-K触发器74LS109 TTL 带预置清除正触发双J-K触发器74LS11 TTL 3输入端3与门74LS112 TTL 带预置清除负触发双J-K触发器74LS12 TTL 开路输出3输入端三与非门74LS121 TTL 单稳态多谐振荡器74LS122 TTL 可再触发单稳态多谐振荡器74LS123 TTL 双可再触发单稳态多谐振荡器74LS125 TTL 三态输出高有效四总线缓冲门74LS126 TTL 三态输出低有效四总线缓冲门74LS13 TTL 4输入端双与非施密特触发器74LS132 TTL 2输入端四与非施密特触发器74LS133 TTL 13输入端与非门74LS136 TTL 四异或门74LS138 TTL 3-8线译码器/复工器74LS139 TTL 双2-4线译码器/复工器74LS14 TTL 六反相施密特触发器74LS145 TTL BCD—十进制译码/驱动器74LS15 TTL 开路输出3输入端三与门74LS150 TTL 16选1数据选择/多路开关74LS151 TTL 8选1数据选择器74LS153 TTL 双4选1数据选择器74LS154 TTL 4线—16线译码器74LS155 TTL 图腾柱输出译码器/分配器74LS156 TTL 开路输出译码器/分配器74LS157 TTL 同相输出四2选1数据选择器74LS158 TTL 反相输出四2选1数据选择器74LS16 TTL 开路输出六反相缓冲/驱动器74LS160 TTL 可预置BCD异步清除计数器74LS161 TTL 可予制四位二进制异步清除计数器74LS162 TTL 可预置BCD同步清除计数器74LS163 TTL 可予制四位二进制同步清除计数器74LS164 TTL 八位串行入/并行输出移位寄存器74LS165 TTL 八位并行入/串行输出移位寄存器74LS166 TTL 八位并入/串出移位寄存器74LS169 TTL 二进制四位加/减同步计数器74LS17 TTL 开路输出六同相缓冲/驱动器74LS170 TTL 开路输出4×4寄存器堆74LS173 TTL 三态输出四位D型寄存器74LS174 TTL 带公共时钟和复位六D触发器74LS175 TTL 带公共时钟和复位四D触发器74LS180 TTL 9位奇数/偶数发生器/校验器74LS181 TTL 算术逻辑单元/函数发生器74LS185 TTL 二进制—BCD代码转换器74LS190 TTL BCD同步加/减计数器74LS191 TTL 二进制同步可逆计数器74LS192 TTL 可预置BCD双时钟可逆计数器74LS193 TTL 可预置四位二进制双时钟可逆计数器74LS194 TTL 四位双向通用移位寄存器74LS195 TTL 四位并行通道移位寄存器74LS196 TTL 十进制/二-十进制可预置计数锁存器74LS197 TTL 二进制可预置锁存器/计数器74LS20 TTL 4输入端双与非门74LS21 TTL 4输入端双与门74LS22 TTL 开路输出4输入端双与非门74LS221 TTL 双/单稳态多谐振荡器74LS240 TTL 八反相三态缓冲器/线驱动器74LS241 TTL 八同相三态缓冲器/线驱动器74LS243 TTL 四同相三态总线收发器74LS244 TTL 八同相三态缓冲器/线驱动器74LS245 TTL 八同相三态总线收发器74LS247 TTL BCD—7段15V输出译码/驱动器74LS248 TTL BCD—7段译码/升压输出驱动器74LS249 TTL BCD—7段译码/开路输出驱动器74LS251 TTL 三态输出8选1数据选择器/复工器74LS253 TTL 三态输出双4选1数据选择器/复工器74LS256 TTL 双四位可寻址锁存器74LS257 TTL 三态原码四2选1数据选择器/复工器74LS258 TTL 三态反码四2选1数据选择器/复工器74LS259 TTL 八位可寻址锁存器/3-8线译码器74LS26 TTL 2输入端高压接口四与非门74LS260 TTL 5输入端双或非门74LS266 TTL 2输入端四异或非门74LS27 TTL 3输入端三或非门74LS273 TTL 带公共时钟复位八D触发器74LS279 TTL 四图腾柱输出S-R锁存器74LS28 TTL 2输入端四或非门缓冲器74LS283 TTL 4位二进制全加器74LS290 TTL 二/五分频十进制计数器74LS293 TTL 二/八分频四位二进制计数器74LS295 TTL 四位双向通用移位寄存器74LS298 TTL 四2输入多路带存贮开关74LS299 TTL 三态输出八位通用移位寄存器74LS30 TTL 8输入端与非门74LS32 TTL 2输入端四或门74LS322 TTL 带符号扩展端八位移位寄存器74LS323 TTL 三态输出八位双向移位/存贮寄存器74LS33 TTL 开路输出2输入端四或非缓冲器74LS347 TTL BCD—7段译码器/驱动器74LS352 TTL 双4选1数据选择器/复工器74LS353 TTL 三态输出双4选1数据选择器/复工器74LS365 TTL 门使能输入三态输出六同相线驱动器74LS365 TTL 门使能输入三态输出六同相线驱动器74LS366 TTL 门使能输入三态输出六反相线驱动器74LS367 TTL 4/2线使能输入三态六同相线驱动器74LS368 TTL 4/2线使能输入三态六反相线驱动器74LS37 TTL 开路输出2输入端四与非缓冲器74LS373 TTL 三态同相八D锁存器74LS374 TTL 三态反相八D锁存器74LS375 TTL 4位双稳态锁存器74LS377 TTL 单边输出公共使能八D锁存器74LS378 TTL 单边输出公共使能六D锁存器74LS379 TTL 双边输出公共使能四D锁存器74LS38 TTL 开路输出2输入端四与非缓冲器74LS380 TTL 多功能八进制寄存器74LS39 TTL 开路输出2输入端四与非缓冲器74LS390 TTL 双十进制计数器74LS393 TTL 双四位二进制计数器74LS40 TTL 4输入端双与非缓冲器74LS42 TTL BCD—十进制代码转换器74LS352 TTL 双4选1数据选择器/复工器74LS353 TTL 三态输出双4选1数据选择器/复工器74LS365 TTL 门使能输入三态输出六同相线驱动器74LS366 TTL 门使能输入三态输出六反相线驱动器74LS367 TTL 4/2线使能输入三态六同相线驱动器74LS368 TTL 4/2线使能输入三态六反相线驱动器74LS37 TTL 开路输出2输入端四与非缓冲器74LS373 TTL 三态同相八D锁存器74LS374 TTL 三态反相八D锁存器74LS375 TTL 4位双稳态锁存器74LS377 TTL 单边输出公共使能八D锁存器74LS378 TTL 单边输出公共使能六D锁存器74LS379 TTL 双边输出公共使能四D锁存器74LS38 TTL 开路输出2输入端四与非缓冲器74LS380 TTL 多功能八进制寄存器74LS39 TTL 开路输出2输入端四与非缓冲器74LS390 TTL 双十进制计数器74LS393 TTL 双四位二进制计数器74LS40 TTL 4输入端双与非缓冲器74LS42 TTL BCD—十进制代码转换器74LS447 TTL BCD—7段译码器/驱动器74LS45 TTL BCD—十进制代码转换/驱动器74LS450 TTL 16:1多路转接复用器多工器74LS451 TTL 双8:1多路转接复用器多工器74LS453 TTL 四4:1多路转接复用器多工器74LS46 TTL BCD—7段低有效译码/驱动器74LS460 TTL 十位比较器74LS461 TTL 八进制计数器74LS465 TTL 三态同相2与使能端八总线缓冲器74LS466 TTL 三态反相2与使能八总线缓冲器74LS467 TTL 三态同相2使能端八总线缓冲器74LS468 TTL 三态反相2使能端八总线缓冲器74LS469 TTL 八位双向计数器74LS47 TTL BCD—7段高有效译码/驱动器74LS48 TTL BCD—7段译码器/内部上拉输出驱动74LS490 TTL 双十进制计数器74LS491 TTL 十位计数器74LS498 TTL 八进制移位寄存器74LS50 TTL 2-3/2-2输入端双与或非门74LS502 TTL 八位逐次逼近寄存器74LS503 TTL 八位逐次逼近寄存器74LS51 TTL 2-3/2-2输入端双与或非门74LS533 TTL 三态反相八D锁存器74LS534 TTL 三态反相八D锁存器74LS54 TTL 四路输入与或非门74LS540 TTL 八位三态反相输出总线缓冲器74LS55 TTL 4输入端二路输入与或非门74LS563 TTL 八位三态反相输出触发器74LS564 TTL 八位三态反相输出D触发器74LS573 TTL 八位三态输出触发器74LS574 TTL 八位三态输出D触发器74LS645 TTL 三态输出八同相总线传送接收器74LS670 TTL 三态输出4×4寄存器堆74LS73 TTL 带清除负触发双J-K触发器74LS74 TTL 带置位复位正触发双D触发器74LS76 TTL 带预置清除双J-K触发器74LS83 TTL 四位二进制快速进位全加器74LS85 TTL 四位数字比较器74LS86 TTL 2输入端四异或门74LS90 TTL 可二/五分频十进制计数器74LS93 TTL 可二/八分频二进制计数器74LS95 TTL 四位并行输入\\输出移位寄存器74LS97 TTL 6位同步二进制乘法器CD系列:CD4000 双3输入端或非门+单非门TICD4001 四2输入端或非门HIT/NSC/TI/GOLCD4002 双4输入端或非门NSCCD4006 18位串入/串出移位寄存器NSCCD4007 双互补对加反相器NSCCD4008 4位超前进位全加器NSCCD4009 六反相缓冲/变换器NSCCD4010 六同相缓冲/变换器NSCCD4011 四2输入端与非门HIT/TICD4012 双4输入端与非门NSCCD4013 双主-从D型触发器FSC/NSC/TOSCD4014 8位串入/并入-串出移位寄存器NSCCD4015 双4位串入/并出移位寄存器TICD4016 四传输门FSC/TICD4017 十进制计数/分配器FSC/TI/MOTCD4018 可预制1/N计数器NSC/MOTCD4019 四与或选择器PHICD4020 14级串行二进制计数/分频器FSCCD4021 08位串入/并入-串出移位寄存器PHI/NSCCD4022 八进制计数/分配器NSC/MOTCD4023 三3输入端与非门NSC/MOT/TICD4024 7级二进制串行计数/分频器NSC/MOT/TICD4025 三3输入端或非门NSC/MOT/TICD4026 十进制计数/7段译码器NSC/MOT/TICD4027 双J-K触发器NSC/MOT/TICD4028 BCD码十进制译码器NSC/MOT/TICD4029 可预置可逆计数器NSC/MOT/TICD4030 四异或门NSC/MOT/TI/GOLCD4031 64位串入/串出移位存储器NSC/MOT/TICD4032 三串行加法器NSC/TICD4033 十进制计数/7段译码器NSC/TICD4034 8位通用总线寄存器NSC/MOT/TICD4035 4位并入/串入-并出/串出移位寄存NSC/MOT/TI CD4038 三串行加法器NSC/TICD4040 12级二进制串行计数/分频器NSC/MOT/TICD4041 四同相/反相缓冲器NSC/MOT/TICD4042 四锁存D型触发器NSC/MOT/TICD4043 4三态R-S锁存触发器("1"触发) NSC/MOT/TI CD4044 四三态R-S锁存触发器("0"触发) NSC/MOT/TI CD4046 锁相环NSC/MOT/TI/PHICD4047 无稳态/单稳态多谐振荡器NSC/MOT/TICD4048 4输入端可扩展多功能门NSC/HIT/TICD4049 六反相缓冲/变换器NSC/HIT/TICD4050 六同相缓冲/变换器NSC/MOT/TICD4051 八选一模拟开关NSC/MOT/TICD4052 双4选1模拟开关NSC/MOT/TICD4053 三组二路模拟开关NSC/MOT/TICD4054 液晶显示驱动器NSC/HIT/TICD4055 BCD-7段译码/液晶驱动器NSC/HIT/TI CD4056 液晶显示驱动器NSC/HIT/TICD4059 “N”分频计数器NSC/TICD4060 14级二进制串行计数/分频器NSC/TI/MOT CD4063 四位数字比较器NSC/HIT/TICD4066 四传输门NSC/TI/MOTCD4067 16选1模拟开关NSC/TICD4068 八输入端与非门/与门NSC/HIT/TICD4069 六反相器NSC/HIT/TICD4070 四异或门NSC/HIT/TICD4071 四2输入端或门NSC/TICD4072 双4输入端或门NSC/TICD4073 三3输入端与门NSC/TICD4075 三3输入端或门NSC/TICD4076 四D寄存器CD4077 四2输入端异或非门HITCD4078 8输入端或非门/或门CD4081 四2输入端与门NSC/HIT/TICD4082 双4输入端与门NSC/HIT/TICD4085 双2路2输入端与或非门CD4086 四2输入端可扩展与或非门CD4089 二进制比例乘法器CD4093 四2输入端施密特触发器NSC/MOT/ST CD4094 8位移位存储总线寄存器NSC/TI/PHICD4095 3输入端J-K触发器CD4096 3输入端J-K触发器CD4097 双路八选一模拟开关CD4098 双单稳态触发器NSC/MOT/TICD4099 8位可寻址锁存器NSC/MOT/STCD40100 32位左/右移位寄存器CD40101 9位奇偶较验器CD40102 8位可预置同步BCD减法计数器CD40103 8位可预置同步二进制减法计数器CD40104 4位双向移位寄存器CD40105 先入先出FI-FD寄存器CD40106 六施密特触发器NSC\\TICD40107 双2输入端与非缓冲/驱动器HAR\\TI CD40108 4字×4位多通道寄存器CD40109 四低-高电平位移器CD40110 十进制加/减,计数,锁存,译码驱动STCD40147 10-4线编码器NSC\\MOTCD40160 可预置BCD加计数器NSC\\MOTCD40161 可预置4位二进制加计数器NSC\\MOTCD40162 BCD加法计数器NSC\\MOTCD40163 4位二进制同步计数器NSC\\MOTCD40174 六锁存D型触发器NSC\\TI\\MOTCD40175 四D型触发器NSC\\TI\\MOTCD40181 4位算术逻辑单元/函数发生器CD40182 超前位发生器CD40192 可预置BCD加/减计数器(双时钟) NSC\\TICD40193 可预置4位二进制加/减计数器NSC\\TICD40194 4位并入/串入-并出/串出移位寄存NSC\\MOTCD40195 4位并入/串入-并出/串出移位寄存NSC\\MOTCD40208 4×4多端口寄存器CD4501 4输入端双与门及2输入端或非门CD4502 可选通三态输出六反相/缓冲器CD4503 六同相三态缓冲器CD4504 六电压转换器CD4506 双二组2输入可扩展或非门CD4508 双4位锁存D型触发器CD4510 可预置BCD码加/减计数器CD4511 BCD锁存,7段译码,驱动器CD4512 八路数据选择器CD4513 BCD锁存,7段译码,驱动器(消隐)CD4514 4位锁存,4线-16线译码器CD4515 4位锁存,4线-16线译码器CD4516 可预置4位二进制加/减计数器CD4517 双64位静态移位寄存器CD4518 双BCD同步加计数器CD4519 四位与或选择器CD4520 双4位二进制同步加计数器CD4521 24级分频器CD4522 可预置BCD同步1/N计数器CD4526 可预置4位二进制同步1/N计数器CD4527 BCD比例乘法器CD4528 双单稳态触发器CD4529 双四路/单八路模拟开关CD4530 双5输入端优势逻辑门CD4531 12位奇偶校验器CD4532 8位优先编码器CD4536 可编程定时器CD4538 精密双单稳CD4539 双四路数据选择器CD4541 可编程序振荡/计时器CD4543 BCD七段锁存译码,驱动器CD4544 BCD七段锁存译码,驱动器CD4547 BCD七段译码/大电流驱动器CD4549 函数近似寄存器CD4551 四2通道模拟开关CD4553 三位BCD计数器CD4555 双二进制四选一译码器/分离器CD4556 双二进制四选一译码器/分离器CD4558 BCD八段译码器CD4560 "N"BCD加法器CD4561 "9"求补器CD4573 四可编程运算放大器CD4574 四可编程电压比较器CD4575 双可编程运放/比较器CD4583 双施密特触发器CD4584 六施密特触发器CD4585 4位数值比较器CD4599 8位可寻址锁存器。

MC74VHC1G126 MC74VHC1GT126 非转换3态缓冲器说明书