DSP第06章 时钟及看门狗+页码

DSP第6章TMS320F2812的时钟及看门狗

1 1 1 1 1 1 1 1 1 3 1 6 程序监视器控制寄存器 程序监视器复位密钥寄存器 PLL控制寄存器 控制寄存器 系统控制&状态寄存器 系统控制 状态寄存器 程序监视器计数寄存器 低功耗工作模式控制寄存器0 低功耗工作模式控制寄存器 低功耗工作模式控制寄存器1 低功耗工作模式控制寄存器

10

PLL旁路 旁路

PLL使能 使能

7

盐城工学院

电气与新能源综合实验教学示范中心

DSP应用技术 DSP应用技术

处理器内部时钟电路

8

盐城工学院

电气与新能源综合实验教学示范中心

DSP应用技术 DSP应用技术

6.1.3 时钟单元寄存器

长度 (×16 位)

寄存器名

地址

描述

保留

0x7010~ ~ 0x7019

第6章 TMS320F2812的时钟及看门狗 TMS320F2812的时钟及看门狗

1

盐城工学院

电气与新能源综合实验教学示范中心

DSP应用技术 DSP应用技术

6.1 时钟单元

6.1.1 时钟单元基本结构

TMS320F2812处理器内部集成了振荡器、锁相环、看 处理器内部集成了振荡器、锁相环、 处理器内部集成了振荡器 门狗及工作模式选择等控制电路。 门狗及工作模式选择等控制电路。 振荡器、锁相环主要为处理器 主要为处理器CPU及相关外设提供可 振荡器、锁相环主要为处理器 及相关外设提供可 编程的时钟, 编程的时钟,每个外设的时钟都可以通过相应的寄存器 进行编程设置; 进行编程设置 看门狗可以监控程序的运行状态 提高系统的可靠性。 可以监控程序的运行状态, 看门狗可以监控程序的运行状态,提高系统的可靠性。

8

SPIENCLK

SP第6章看门狗定时器模块

位7:是WD的标志位。该位表明了WD是否发生过系统复 位信号。WD引发的系统复位可将该位置1,任何其他的系统复 位事件对该位都没有影响。当该位为0时,表示自上次 WDCNTR清零以来,WD没有发出过系统复位信号;为1时, 表示自上次WDCNTR清零以来,WD已经发出过系统复位信 号。 位6:是WD的使能位。该位只有在系统配置寄存器SCSR2的

《DSP原理及应用》

4

北京理工大学珠海学院信息学院

第6章 看门狗定时器模块

6.2 WD寄存器的配置

WD的所有寄存器都是8位字宽,并且与16位CPU外设 数据总线的低8位相连。对WD操作的设置比较简单,可通过 3个相关寄存器来配置。 1.WD计数寄存器(WDCNTR) :地址为7023h WD计数寄存器包含看门狗计数器的计数值,复位值为0。 2.WD复位关键字寄存器(WDKEY) :地址为7025h 当55h及紧接其后的AAh顺序写入WDKEY时,则该寄存器 将清除WDCNTR寄存器中的内容。写入到WDKEY中任何其他 内容,都将产生一个系统复位操作。

《DSP原理及应用》

5

北京理工大学珠海学院信息学院

第6章 看门狗定时器模块

3.WD控制寄存器(WDCR) :地址为 7 6 4 3 5 7029h

WDFLAG WDDIS WDCHK2 WDCHK1 WDCHK0

2 WDPS2

1

0

WDPS1

WDPS0

WD OVERRIDE位为1时,才可以进行写操作。该位写0时,使 能看门狗;写1时禁止看门狗。 位5-3:是看门狗校验位。当用户对WDCR进行访问时,必须 将这3位写入101ห้องสมุดไป่ตู้否则将引发一个系统复位事件。

第6章 看门狗定时器模块

DSP原理与应用---第6章 McASP

PSAcM 1.3.5

PSAcM置配来骤步的面下照按

。迟延的间之始开元单和沿边号信步同帧指是这。期周钟时 行串个2或1�0为定指被以可迟延号信步同帧�下式模号信步同帧发突在 。息信制控输传 间片芯PSD个两在如例�输传的据数频音非于用要主。的动驱据数是而 �性期周是不生产的号信步同帧下式模种这�式模输传发突持支PSAcM

�作操下如行进要�1到变0从脚 引个一将。脚引的心关所响影仅仅作操写的器存寄TESDP对为 因是这。器存寄TUODP用使是不而器存寄TESDP用使荐推�1 为变0从出输将若�0出输并�脚引出输用通为置配被脚引果如

。]n[TUODP的应相位置将�]n[TESDP位置

1到变0从据数将TESDP用使——脚引出输用通�3-5例

�

子例的理处行进性活灵的帧和钟时PSAcM用利

。了据数取读元单化式格经�)名别的FUBRX收接(器存寄FUBR过 通以可就PSD在现。中FUBRX存缓据数到制复被就据数些这着接�后之RSRX了 到集收被都元单据数个整在。RSRX器存寄位移入移脚引]n[RXA过通据数�收接 � 。)LTCRS( 器存寄制控�)FUBRX(器存缓据数�)RSRX(器存寄位移个一括包器行串个一每 。PSAcM出移或入移据数行串将责负器行串。制控来]n[LTCRS器存寄由器行串 �

�

� �

介简 PSAcM

1. 5

tiB tnacifingiS tsaeL 。充填来)BSL或BSM是般一(位一的中字者或1、0用以可位加附的字于属不 。)尾末(边右的元单在排以可也)始开(边左的元单到列排以可字�时度长元单于小度长 的字当。位低最是以可也�PSAcM出先或进先位高最是以可位些这�内元单个一在 。位加附的字充填来用些那括包也元单�数位的适合说来口接件 器部外和PSD 于对到充填字将了为时有。位些那的字成组括包元单个一�)tolS(元单� 。据数的输传间之件器部外和PSD在了成组它�位组一是字�)droW(字� 。志标为作沿边的钟时 行串个一用是都束结和始开的位个每。分部成组小最的中流据数行串是位�)tiB(位� tiB tnacifingiS tsoM

第6章TMS320F2812的时钟及看门狗

6.2 看门狗

看门狗主要用来检测软件和硬件的运行状态,当内部 计数器溢出时,将产生一个复位信号。 为了避免产生不必要的复位,要求用户定期对看门狗 定时器进行复位。 如果不明的原因使CPU中断程序,看门狗将产生一个复 位信号,使CPU复位,程序从系统软件的开始执行。 看门狗有效地提高了系统的可靠性。

6.1.3 时钟单元寄存器

寄存器名 地址 长度 (×16位) 描述

保留

0x7010~0x7019

10

HISPCP

0x701A

1

HSPCLK时钟的高速外设 模块时钟预分频寄存器 LSPCLK时钟的低速外设 模块时钟预分频寄存器 外设模块时钟控制寄存器

LOSPCP PCLKCR

0x701B 0x701C

2.低速时钟寄存器(LOSPCP)

15 Reserved R-0 3 2 1 LSPCLK R/W-010 0

位15~3

Reserved 保留位

位2~0 LSPCLK 配置与SYSCLKOUT相关的低速外设模块时钟(LSPCLK) 频率。 000 低速时钟=SYSCLKOUT/1 001 低速时钟=SYSCLKOUT/2 010 低速时钟=SYSCLKOUT/4(复位值) 011 低速时钟=SYSCLKOUT/6 100 低速时钟=SYSCLKOUT/8 101 低速时钟=SYSCLKOUT/10 110 低速时钟=SYSCLKOUT/12 111 低速时钟=SYSCLKOUT/14

6.2.1 看门狗的基本结构

程序监视器 控制寄存器 1 0 程序监视器 复位信号 程序监视器 计数寄存器

晶体振荡 器时钟宽度 程序监视器 复位密钥寄存器

或门

程序监视器 中断信号 系统控制和状 态寄存器

dsp看门狗定时器的作用解析

dsp 看门狗定时器的作用解析

一、DSP 看门狗定时器介绍

看门狗在外围监控DSP 中软件的运行以及硬件的操作,当CPU 出现故障时,看门狗将执行系统复位。

如果软件进入了一个不正确的循环或者CPU 出现暂时的混乱,看门狗定时器将出现溢出来使系统复位。

在大多数情况下,DSP 短暂的混乱以及CPU 不正确的操作都可以被看门狗所清除并重新进行设置。

由于看门狗稳定的性能,其增加了CPU 的可靠性,以确保系统的完整。

在看门狗中这个外围设备中,所有的寄存器都是8 位的,连接到16 位CPU 的低8 位外围数据总线上。

240XA 看门狗定时器和C240 看门狗定时器唯一的区别就是其缺乏实时的中断能力。

看门狗定时器将通过对从CPU 出来的CLKOUT 进行分频而得到自己所需的时钟

二、看门狗定时器工作原理

使用时,WDT 将递增,直到溢出,或称超时。

除非处于休眠或空闲模式,WDT 超时会强制器件复位。

为避免WDT 超时复位,用户必须定期用。

DSP课件、、、看门狗

表4 看门狗复位寄存器位功能介绍

位 15~8 名 Reserved 称 保留 首先写0x55,然后再写0xAA到WDKEY会使WDCNTR (看门狗计数器)清零。写其他的任何值都会使看门狗 产生复位信号;读操作将返回WDCR寄存器的值 功能介绍

需要特别说明的是,看门狗模块可以产生复位信号和中断信号,但是 两者不能同时产生。当产生复位信号时,出现故障时,信号直接使器件复位; 当产生中断信号时,出现故障时,模块只能产生中断信号,如果中断使能, 则执行中断服务子程序。看门狗模块的中断信号和复位信号是通过寄存器 SCSR的第二位WDENIN位决定的,具体的位信息在前面已经介绍了,在本程序 中,设置该位信息为1,即屏蔽看门狗复位信号,使能看门狗中断信号,所 以在产生故障时,不会复位芯片,而是执行中断服务子程序。

组员:余洋勇、张佳杰、张萌

1.看门狗模块介绍 1.看门狗模块介绍

看门狗,又叫 watchdog timer,是一个定时器电路, 一般有一个 输入,叫喂狗,一个输出到MCU的RST端,MCU正常工作的时候,每隔一端 时间输出一个信号到喂狗端,给 WDT 清零,如果超过规定的时间不喂 狗,(一般在程序跑飞时),WDT 定时超过,就回给出一个复位信号到MCU, 是MCU复位. 防止MCU死机. 看门狗的作用就是防止程序发生死循环, 或者说程序跑飞 在实际的DSP应用系统当中,运行时极有可能发生干扰和被干扰的 现象。特别是产品化的DSP系统,可靠性是一个不容忽视的问题,严重 时系统会出现程序“跑飞”现象。为了克服这种情况,在可能的情况 下软硬件都应作相应的处理。目前,看门狗技术就是这种处理的有效 措施之一。 F2812中的看门狗模块与240x器件上的看门狗模块基本相同。当8 位看门狗递增计数器计数达到最大值时,看门狗模块输出一个脉冲信 号(512个振荡器时钟宽度)。为了阻止这种情况发生,用户可以屏 蔽计数器或者利用软件定时向看门狗复位控制寄存器写“0x55+0xAA” 序列(可以复位看门狗计数器)。

DSPX系统时钟+中断+看门狗

第4.1节 TMS320F2833X 时钟

第4.2节TMS320F2833X 中断 第4.3节TMS320F2833X 看门狗 习题

DSP原理与应用

2018年11月23日

2

第4.1节TMS320F2833X 时钟

0.25~10倍输入时钟频率:

1.降低外部晶振频率,以减低电磁干扰(EMI) 2.低价晶振 3.避免使用谐振晶体和相关的屏蔽电路

DSP原理与应用 2018年11月23日 15

第4.2节TMS320F2833X 中断

DSP原理与应用

2018年11月23日

16

第4.2节TMS320F2833X 中断

DSP原理与应用

2018年11月23日

17

第4.2节TMS320F2833X 中断

PIEIER,PIEIFR,PIECTRL,PIEACK

DSP原理与应用

The Technology & Applications of DSPs

北京交通大学 电气工程学院 夏明超 郝瑞祥 万庆祝 mchxia@ haorx@ qzhwan@

第四章:TMS320F2833X 系统功能和其他功能

DSP原理与应用

2018年11月23日

30

第4.2节TMS320F2833X 中断

中断优先级和中断向量: INT12

外部引脚中断(XINT3~XINT7) 浮点运算中断(LVF,LUF)

中断优先级和中断向量: INT13

外部引脚中断(XINT13) CPU定时器1(TI RTOS)

27

第4.2节TMS320F2833X 中断

中断优先级和中断向量: INT4

ECAP1~ECAP6中断

DSP第06章时钟及看门狗页码_图文(精)

// Step 5、用户特定函数,重新分配向量(可选择),使能中断: // 重新为WAKEINT 分配 PIE 向量,并指向相应的中断服务程序 EALLOW; PieVectTable.WAKEINT = &wakeint_isr; EDIS; // 使能WAKEINT 的中断INT1 IER |= M_INT1; // 使能 PieCtrlRegs.PIEIER1.bit.INTx8 = 1; // 对程序状态寄存器进行操作,避免清除WDOVERRIDE 标识位 EALLOW; SysCtrlRegs.SCSR.all = BIT1; EDIS; // 计数器清零 WakeCount = 0; // 中断计数 LoopCount = 0; // 循环计数 BP106 36// 使能全局中断,并配置为real-time debug 模式 EINT; // 使能全局中断INTM ERTM; // 使能全局 realtime 中断DBGM // Step 6、主循环 for(;; { LoopCount++; //用KickDog 操作看门狗Key 寄存器,避免产生WAKEINT 中断 // 通常情况下,需要在主循环或定时中断中对Key 进行操作 KickDog(; } } WAKEINT:位于PIE 的组1 的第8 中断 BP106 37// Step 7、中断服务程序 interrupt void wakeint_isr(void { WakeCount++; // 响应中断 PieCtrlRegs.PIEACK.all = PIEACK_GROUP1; } //--------------------------------------------------------------------------// KickDog: 此函数复位看门狗定时器 voidKickDog(void { EALLOW; SysCtrlRegs.WDKEY = 0x0055; SysCtrlRegs.WDKEY = 0x00AA; EDIS; } BP107 38void InitSysCtrl(void // 系统初始化 { Uint16 i; EALLOW; // 禁止看门狗模块 // SysCtrlRegs.WDCR= 0x0068; // 本例中不使用 //初始化锁相环 SysCtrlRegs.PLLCR = 0xA; // 等待锁相环稳定 for(i= 0; i< 5000; i++{} // HISPCP/LOSPCP 预定标寄存器设置 SysCtrlRegs.HISPCP.all = 0x0001; SysCtrlRegs.LOSPCP.all = 0x0002; // 使能选择的外设时钟 // 对于不用的时钟,一般情况下需要禁止相应的中断SysCtrlRegs.PCLKCR.bit.EVAENCLK=1; SysCtrlRegs.PCLKCR.bit.EVBENCLK=1; SysCtrlRegs.PCLKCR.bit.SCIENCLKA=1; //SysCtrlRegs.PCLKCR.bit.SCIENCLKB=1; EDIS; BP107 } 39。

轻松学会DSP——定时器和时钟课件

止、调整频率等。

定时器与时钟的联合编程实例

定时器触发时钟

可以通过定时器触发时钟的启动或停止,实现定时任务与时间戳的 同步。

时钟回调定时器

可以在时钟中断处理程序中调用定时器的回调函数,实现时间敏感 任务的调度。

联合编程注意事项

在联合编程时,需要注意时序问题,确保定时器和时钟的同步运行; 同时还需要注意资源共享问题,避免资源冲突和死锁。

用于控制定时器的启动、停止 、复位等操作,以及设置定时

器的计数值和预置值。

定时器的控制方式

硬件控制方式

通过硬件电路实现定时器的启动、停 止、复位等操作,具有速度快、可靠 性高的优点。

软件控制方式

通过编写程序实现定时器的启动、停 止、复位等操作,具有灵活性高、易 于实现复杂功能的优点。

定时器的计数方式

CHAPTER 05

DSP定时器与时钟的编程实 例

使用C语言编写DSP定时器程序

定时器初始化

在C语言中,需要先对定时器进 行初始化设置,包括设置定时器

模式、计数值等。

定时器中断处理

在定时器溢出时,需要编写中断 处理程序,以执行相应的操作, 如更新计数值、执行回调函数等

。

定时器控制

通过C语言中的函数调用,可以 实现对定时器的控制,如启动、

频率合成

时钟信号还可以用于生成其他频率 的信号,这在信号调制和解调中非 常有用。

定时器与时钟的协同工作

时间基准与事件计数

定时器可以基于时钟信号进行触发,用于计数或测量时间间隔。

同步操作

通过将定时器输出与系统时钟源同步,可以确保DSP中的各种操作 在正确的时间点开始和结束。

动态调整

根据需要,可以通过调整时钟频率或定时器的配置来动态改变DSP 的处理速度或响应时间。

第6讲 DSP外设应用之系统时钟

第6讲DSP外设应用之系统时钟系统时钟,即为各个模块产生所需要的时钟,如C55x core、慢速外设(Slow Peripherals),快速外设(Fast Peripherals)以及其它外设所需的基准时钟。

系统时钟的设置是任何一个可编程器件必须进行的初始化操作。

在DSP5502中,系统的时钟初始化语句为:PLL_setFreq(1, 0xC, 0, 1, 3, 3, 0);该语句为CSL(Chip Support Library)库函数语句,在进行时钟设置时,系统调用该API初始化函数,以完成系统设置,对于C55x 5502所涉及的时钟寄存器如下表所示:系统涉及的函数原型为void PLL_setFreq (Uint16 mode, Uint16 mul, Uint16 div0, Uint16 div1, Uint16 div2,Uint16 div3, Uint16 oscdiv);Uint16 mode // PLL mode//PLL_PLLCSR_PLLEN_BYP ASS_MODE//PLL_PLLCSR_PLLEN_PLL_MODEUint16 mul // Multiply factor, Valid values are (multiply by) 2 to 15.Uint16 div0 // Sysclk 0 Divide Down, Valid values are 0, (divide by 1)//to 31 (divide by 32)Uint16 div1 // Sysclk1 Divider, Valid values are 0, 1, and 3 corresponding//to divide by 1, 2, and 4 respectivelyUint16 div2 // Sysclk2 Divider, Valid values are 0, 1, and 3//corresponding to divide by 1, 2, and 4 respectivelyUint16 div3 // Sysclk3 Divider, Valid values are 0, 1 and 3//corresponding to divide by 1, 2 and 4 respectivelyUint16 oscdiv // CLKOUT3(DSP core clock) divider,Valid values are 0//(divide by 1) to 31 (divide by 32)程序中,对于MODE,则5502有两种模式:PLL旁路模式和PLL使能模式,前者是时钟未经PLL进行倍频,而后者使用PLL功能。

2407DSP第6章 看门狗定时器模块

第6章 看门狗定时器模块

《DSP原理及应用》

1

北京理工大学珠海学院信息学院

第6章 看门狗定时器模块

在计算机控制系统的实际应用中,可靠性是一个非常重要 的问题,尤其是在工业应用场合,系统抗干扰能力显得尤为突 出。为解决干扰问题,除了对干扰源的适当处理外,在计算机 控制系统中也应增加一些防范措施,从而避免程序“跑飞”或 “死机”现象,导致系统工作异常。

为解决这个问题,在TMS320LF240x芯片中增加了看门狗 (WD)定时电路。WD监视系统软件和硬件的运行,它可以按照用 户设定的时间间隔产生中断。如果软件进入非正常循环或CPU 运行出现异常时,则WD定时器计数上溢,并产生系统复位信号, 使系统进入用户预定义的状态。 在系统中的绝大多数异常情况都可以通过WD的操作清除, 故此WD设可大大提高系统的稳定性和可靠性。

《DSP原理及应用》

6

北京理工大学珠海学院信息学院

《DSP原理及应用》

4

北京理工大学珠海学院信息学院

第6章 看门狗定时器模块

6.2 WD寄存器的配臵

WD的所有寄存器都是8位字宽,并且与16位CPU外设数据 总线的低8位相连。对WD操作的设臵比较简单,可通过3个相 关寄存器来配臵。 1.WD计数寄存器(WDCNTR) :地址为7023h WD计数寄存器包含看门狗计数器的计数值,复位值为0。 2.WD复位关键字寄存器(WDKEY) :地址为7025h 当55h及紧接其后的AAh顺序写入WDKEY时,则该寄存器将清 除WDCNTR寄存器中的内容。写入到WDKEY中任何其他内容,都将 产生一个系统复位操作。

位6:是WD的使能位。该位只有在系统配臵寄存器SCSR2的WD OVERRIDE位为1时,才可以进行写操作。该位写0时,使能看门狗; 写1时禁止看门狗。 位5-3:是看门狗校验位。当用户对WDCR进行访问时,必须将 这3位写入101,否则将引发一个系统复位事件。

DSP原理与应用---第6章 McASP教学内容

5.3.3 数据发送和接收

(2) 接收数据就绪

接收数据就绪标志即RSTAT寄存器中的RDATA位反映了XBUF寄存器的状态。当 从XRSR[n] 移位寄存器向X RBUF[n]缓冲器传输数据时,RDATA标志位被置位, 表示RBUF中包含接收的数据并准备好让DSP来读取数据了。当RDATA位被写入1 或者所有被配置为接收器的串行器都被读出了,标志位就会被清零。

以一个取样速率(如:44.1 kHz)接收数据,但以不同的取 样速率(如:48 kHz)发送数据。

5.2.4 串行器

串行器由寄存器SRCTL[n]来控制。串行器负责将串行数据移入或移出McASP。 每一个串行器包括一个移位寄存器(XRSR),数据缓存器(XRBUF),控制寄存器 (SRCTL)。

引脚数据设置寄存器 (PDSET):PDOUT的别名。向PDSET[n]写入1就会将相 应PDOUT[n]设置为1。写入0没有影响。仅在引脚配置为GPIO输出时(PFUNC[n] = 1,PDIR[n] = 1) 此寄存器可用。

引脚数据清除寄存器 (PDCLR):PDOUT的别名。向PDCLR[n]写入一个1就会 将相应PDOUT[n]设置为0。写入0没有影响。仅在引脚配置为GPIO输出时 (PFUNC[n] = 1,PDIR[n] = 1) 此寄存器可用。

McASP的时钟发生器能产生独立的发送和接收时钟,可以对它们单独 进行编程,它们相互之间可以完全异步。串行时钟(位速率时钟)可 以源自:

内部 - 将内部时钟源通过两个分频器产生时钟

外部 - 直接由ACLKR/X引脚输入

混合 - 一个外部高频时钟输入到McASP的AHCLKX引脚或AHCLKR 引脚,然后被分频产生位速率时钟

在这个例子中,当接收到字A的最后一位(A0)时,McASP将RDATA标志位置位, 并产生一个AREVT事件。然而,在AREVT被激活前还需要5个McASP系统时钟( 即AREVT延迟)。紧接着AREVT之后,DSP开始对McASP服务,从XBUF读取字 A(DSP服务时间)。DSP必须在McASP所要求的建立时间之前从XBUF读取字A ( 建立时间)。

DSP原理及应用第二版课件

RS (复位、外部硬件中断)。

NM I (外部硬件中断)。

29

第6章 TMS320C54x片内外设 也可以用软件进行 RS 和 NM I 中断。 NM I 中断不会对

TMS320C54x的任何操作方式发生影响。 NM I中断响应时, 所有其他的中断将被禁止。而复位 RS 是一个对TMS320C54x 所有操作方式产生影响的非屏蔽中断,复位后,TMS320C54x 的相关内部资源设置的状态如下:

31

第6章 TMS320C54x片内外设

ARP = 0 C16 = 0 DROM = 0 OVB = 0 XF = 1

ASM = 0 CLKOFF = 0 FRCT = 0 OVLY = 0

AVIS = 0 CMPT = 0 HM = 0 OVM = 0

BRAF = 0 CPL = 0 INTM = 1 SXM = 1

第6章 TMS320C54x片内外设

6.1 时 钟 发 生 器

图6-1 时钟电路时钟发生器为TMS320C54x提供时钟信 号,它包括一个内部振荡器和一个锁相环电路。时钟发生器可 以由内部振荡电路或外部时钟源驱动。

1

第6章 TMS320C54x片内外设 内部振荡电路驱动方式:将一个晶体跨接到X1和X2/

21

第6章 TMS320C54x片内外设 3.IDLE3模式 IDLE3模式类同于IDLE2,它使片内锁相环PLL暂停工作,

这样就完全使TMS320C54x停止了工作。与IDLE2相比, IDLE3更显著地降低了功耗。此外,如果系统需要工作在较低 频率,则IDLE3状态可重新配置PLL。进入和结束IDLE3模式 的方法同IDLE2。

C=1 DP = 0 OVA = 0 TC = 1

(完整word版)DSP时钟设计

课程设计任务书摘要DSP芯片既具有高速数字信号处理功能又具有实时性强、功耗低、集成度高等嵌入式微计算机的特点,所以随着科技的发展,DSP技术在机电控制领域的应用愈加广泛。

LED数码管显示清晰美观、功耗低,现在已成为电子产品中应用最广泛的显示方式。

本次课程设计就是通过对DSP芯片和数码管的分析研究,利用DSPC55x构建一个时间显示系统,采用数码管显示时间,用按键调整时间。

该时钟系统包括计时、时钟输出、按键输入三个设计部分。

并给出了各部分汇编程序。

关键字:DSP芯片;数码管;按键;汇编程序目录1绪论 (1)2 相关知识 (2)2.1TMS320C55X开发环境 (2)2.2定时器 (2)2.3中断 (3)3设计原理 (4)3.1时钟计时程序 (4)3.2时钟输出程序 (4)3.3按键输入程序 (4)3.4程序流程图 (5)4设计编程及注释 (6)4.1时钟计时程序 (6)4.2时钟输出程序 (9)4.3按键输入程序 (10)4.4SDRAM初始化程序 (11)4.5命令文件 (13)总结 (15)致谢 (16)参考文献 (17)1 绪论近年来数字化已成为现代信息技术的重要标志,数字相机、数字电视、是自收音机、数字电话、数字学习机、数字游戏机已经逐渐进入人们日常生活和工作中。

在我国数字电话已拥有数亿用户,MP3成为上亿青年学生的宠儿,数字电视已开始进入千家万户,这些产品均采用DSP对信号进行处理。

随着DSP技术的迅速发展,其不仅使信号处理能力更加完善,而且使系统开发更加方便、程序编辑调试更加灵活,功耗也进一步降低,成本不断下降。

尤其是将各种通用外设集成到芯片上,从而大大提高了数字信号处理能力。

DSP芯片不仅在通信、计算机领域得到广发应用,而且也逐渐渗透到人们的日常消费领域中。

这就迫切要求理工科大学生熟悉和掌握DSP芯片功能及其在实际中的应用方法,除通过实验教学培养DSP的基本实验方法、分析问题和故障检查方法以及双踪示波器等常用仪器使用方法等基本电路的基本实验技能外,还必须培养大学生工程设计和组织实验能力。

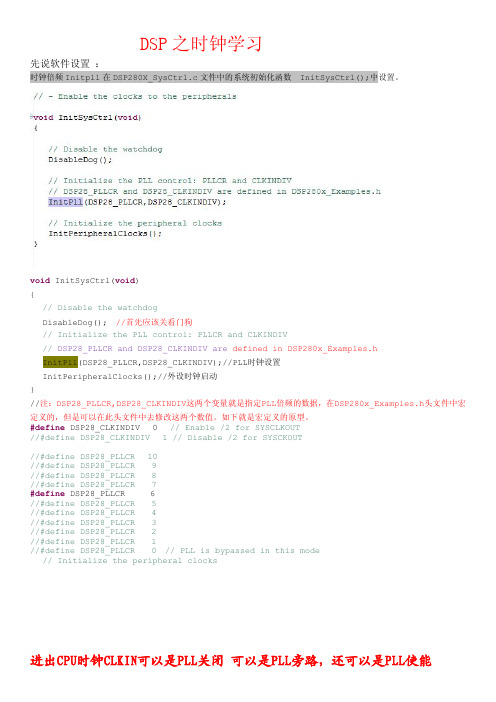

DSP时钟

DSP之时钟学习先说软件设置:时钟倍频Initpll在DSP280X_SysCtrl.c文件中的系统初始化函数InitSysCtrl();中设置。

void InitSysCtrl(void){//Disable the watchdogDisableDog();//首先应该关看门狗//Initialize the PLL control:PLLCR and CLKINDIV//DSP28_PLLCR and DSP28_CLKINDIV are defined in DSP280x_Examples.hInitPll(DSP28_PLLCR,DSP28_CLKINDIV);//PLL时钟设置InitPeripheralClocks();//外设时钟启动}//注:DSP28_PLLCR,DSP28_CLKINDIV这两个变量就是指定PLL倍频的数据,在DSP280x_Examples.h头文件中宏定义的,但是可以在此头文件中去修改这两个数值。

如下就是宏定义的原型。

#define DSP28_CLKINDIV0//Enable/2for SYSCLKOUT//#define DSP28_CLKINDIV1//Disable/2for SYSCKOUT//#define DSP28_PLLCR10//#define DSP28_PLLCR9//#define DSP28_PLLCR8//#define DSP28_PLLCR7#define DSP28_PLLCR6//#define DSP28_PLLCR5//#define DSP28_PLLCR4//#define DSP28_PLLCR3//#define DSP28_PLLCR2//#define DSP28_PLLCR1//#define DSP28_PLLCR0//PLL is bypassed in this mode//Initialize the peripheral clocks进出CPU时钟CLKIN可以是PLL关闭可以是PLL旁路,还可以是PLL使能注:·晶振操作:此模式允许使用外部为器件提供时基。

轻松学会DSP——定时器和时钟PPT学习教案

差分方程

y[k] Ay[k 1] By[k 2] Cx[k 1]

当x[k]为单位冲击信号时,假定初始条件为0

y[0] Ay[1] By[2] Cx[1] 0 y[1] Ay[0] By[1] Cx[0] C y[2] Ay[1] By[0] Cx[1] Ay[1] y[3] Ay[2] By[1] y[n] Ay[n 1] By[n 2]

轻松学会DSP——定时器和时钟

会计学

1

2、定时器的结构

对 DSP的 系 统 时钟CLKOUT信 号 计 数, 先将PSC减 1, 直到PSC为 0。 然后 ,用TDDR重 新 装入 PSC, 同时将 TIM减1。 如此 直到TIM减 为 0。这时 ,DSP的 CPU发 出TINT中 断 ,同时 在DSP的 TOUT引 脚 输出一 个脉冲 信号, 脉冲宽 度与系 统时钟 CLKOUT一 致 。然 后,用 PRD重 新装入 TIM,用 TDDR重 新装 入PSC, 重复 下去, 直到系 统或定 时器复 位。

;Soft=1,Free=1,TSS=1

STM #PERIOD-1, PRD

ANDM #0010h, TCR

;TDDR=0

ORM #0020h, TCR

;TRB=1

STM #0FFFFh, IFR

;清除所有中断

ORM #8h, IMR

;打开时钟中断

RSBX INTM

;开中断

ANDM #0FFEFh, TCR

;T=Y2, Y2复 制 到 Y1

MAC #CA, A

;A = A + T*CA

STH A, 1, Y2

;Y2 = A*2

RETE

第13页/共29页

三、时钟发生器

时钟与看门狗介绍PPT课件

通过下图中可以看到,C28X内核时钟输出,通过LOSPCP低速时钟寄存器设置预分 频,成低速时钟信号LSPCLK,SPI,I2C,MCBSP这些串口通信都是使用的低速时钟信号。 通过HISPCP高速时钟寄存器设置预分频,成高速时钟信号HSPCLK,AD模块采用的是高 速时钟信号,方便灵活设置AD采样率。通过1/2分频给了eCAN模块。直接输出给了系统 控制寄存器模块、DMA模块、EPWM模块、ECAP模块、EQEP模块这些高速外设模块。 当然这些外设基本都有自己的预定标时钟设置寄存器,如果预定标寄存器值为0的话,那 么LSPCLK等时钟信号就成为了外设实际使用时钟信号。当然要使用这些信号需要在外设 时钟寄存器PCLKCR中设置该对应外设使能。

锁相环模块除了为C28X内核提供时钟外,还通过系统时钟输出提供快速和慢速2种 外设时钟。如果使能内部PLL电路,那么可以通过控制寄存器PLLCR软件设置系统的工作 频率。但是要注意,在通过软件改变工作频率时,必须等待系统时钟稳定后才可以继续完 成其他操作。除此之外,每种外设的时钟源都可以通过软件进行使能或者禁止。在具体应 用中,为了降低系统功耗,不使用的外设最好将其外设时钟禁止。外设时钟包括快速外设 和慢速外设两种。分别通过HISPCP和LOSPCP寄存器进行设置。

第8页/共11页

dsp看门狗定时器

看门狗定时器看门狗在外围监控DSP中软件的运行以及硬件的操作,当CPU出现故障时,看门狗将执行系统复位。

如果软件进入了一个不正确的循环或者CPU出现暂时的混乱,看门狗定时器将出现溢出来使系统复位。

在大多数情况下,DSP短暂的混乱以及CPU不正确的操作都可以被看门狗所清除并重新进行设置。

由于看门狗稳定的性能,其增加了CPU的可靠性,以确保系统的完整。

在看门狗中这个外围设备中,所有的寄存器都是8位的,连接到16位CPU的低8位外围数据总线上。

240XA看门狗定时器和C240看门狗定时器唯一的区别就是其缺乏实时的中断能力。

(这句话我也不明白哦)。

看门狗定时器将通过对从CPU出来的CLKOUT进行分频而得到自己所需的时钟。

1.1看门狗定时器的特征看门狗模块包含如下特征:n8位的看门狗计数器通过计数溢出从而使系统复位n6位的独立运行计数器通过对看门狗计数器预定标来feed看门狗计数器(上句为字面意思,我的理解是:该6位的独立运行的计数器通过对WD CLK(看门狗工作时钟)进行分频从而使看门狗计数器得到不同频率的时钟。

独立运行的意思是该计数器不受其他器件的影响,只要启动系统,就开始工作)n看门狗复位键寄存器,当向该寄存器写下合适的组合值(在该DSP中,通过向该寄存器相继写55h和AAh值)时,该寄存器将使看门狗计数器清零,当向该寄存器写下不合适的组合值(除55h和AAh以外的值)时,该寄存器将使系统复位n看门狗核对位,当看门狗定时器出现错误情况时,通过看门狗核对位来复位系统n当系统复位时,将自动启动看门狗定时器n可对独立运行计数器输出的6路分频信号进行选择以下为看门狗定时器的功能框图+含义:向WDCR.5-3位(看门狗核对位)写除101以外的任何数将导致系统复位。

含义:分频后的值与WDCLK有关。

1.1看门狗定时器的操作1.1.1概述看门狗的操作由三个寄存器进行控制n看门狗计数寄存器(WDCNTR)——这个寄存器包含了看门狗计数器的值n看门狗键位寄存器(WDKEY)——当向该寄存器先写55h,然后写AAh时,该寄存器将WDCNTR清零n看门狗控制寄存器(WDCR)——该寄存器包含了用于看门狗配置的如下控制位²看门狗禁止位²看门狗标志位²看门狗核对位(3位)²看门狗分频选择位(3位)1.1.2看门狗定时器时钟看门狗定时器时钟(WDCLK)是一种低频率的时钟。

DSP硬件系统的基本设计中时钟电路的设计Word版

一个完整的DSP系统通常是由DSP芯片和其他相应的外围器件构成。

DSP硬件系统主要包括电源电路、复位电路、时钟电路等。

DSP的时钟电路用来为TMS320C54x芯片提供时钟信号,由一个内部振荡器和一个锁相环PLL组成,可通过晶振或外部的时钟驱动。

以下我们将着重讨论DSP硬件系统的基本设计中时钟电路的设计。

关键字TMS320C54x 时钟产生器软件可编程PLL绪论 (I)第一章时钟产生器 (1)第二章软件可编程PLL (2)第一节软件配置PLL介绍 (2)一时钟模式介绍 (2)二时钟模式设置 (3)第二节程序 (7)一倍频模式向倍频模式的切换 (7)二倍频模式向分频模式的切换 (8)三分频模式向倍频模式的切换 (8)四分频模式向分频模式的切换 (9)第三章心得体会 (11)第四章参考文献 (12)TMS320C54XX1X2\CLKIN4 1 3 2VddTSM320C54XX1X2\CLKINC1C2晶体外部晶振第二章软件可编程PLL第一节软件配置PLL介绍软件可编程PLL的特点是有高度的灵活性,它包括一个用来提供各种时钟乘数因子的时钟标定位、直接开放和禁止PLL的功能和一个PLL锁存定时器,该锁存定时器可以延迟期间PLL时钟模式的切换直到所存操作完成为止。

一时钟模式介绍带有内部的软件可编程PLL的期间可以设置为下面两种时钟模式:PLL模式:输入时钟(CLKIN)乘以31个可能的因子中的一个因子,这些因子取值范围为0.25~15,他们可以通过PLL电路获取。

DIV(分频器)模式:输入时钟(CLKIN)处以2或4.当用DIV模式时,所有的模拟部分,包括PLL电路,都被禁止以使功耗降到最小。

二时钟模式设置复位操作之后,时钟操作模式立即由3个外部引脚CLKMD1,CLKMD2,CLKMD3的直来确定。

3个CLKMD引脚所对应的模式如表1所示,复位之后,软件可编程PLL可以被变成设置为所需的模式。

下列时钟模式引脚作何可以在复位时开放PLL:C5402中是CLKMD(3-1)=000b 110b.当这些时钟模式引脚被组合式,内部的PLL锁相定时器不再激活,因此,系统必须延迟释放复位以保证PLL锁存时间的延迟得以满足。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

引起系统复位,

只要向WDKEY写0x55和0xAA,无论写的顺序

如何都不会导致系统复位,而只有先写0x55再 写0xAA才会使WDCNTR复位。

BP101 ~102

22

看门狗内部原理图

BP103

23

6.2.3 看门狗寄存器

控制寄存器

系统控制和状态寄存器 计数寄存器 复位寄存器

BP98

EALLOW和EDIS

2812中有些配置寄存器是受保护的,在进行修改之前

,需要先去掉保护功能。而保护状态是由状态寄存器 中EALLOW标志来指示的。 汇编指令“EALLOW”就是将该标志位置位,允许对受 保护的寄存器操作 。EALLOW一般和EDIS配套使用, 在对受保护的寄存器操作之后,用EDIS恢复寄存器的 被保护状态。 在复位时EALLOW 位被清除以启用EALLOW 保护, CPU 对受保护寄存器进行的所有写入被忽略且只允许 CPU 读取、JTAG 读取和JTAG 写入。 如果设置了此位,则通过EALLOW 指令可以允许CPU 自由写入受保护的寄存器。在修改寄存器之后,可以 通过执行EDI 指令使它们再次受保护。

BP107

35

void InitSysCtrl(void) // 系统初始化 { Uint16 i; EALLOW; // 禁止看门狗模块 // SysCtrlRegs.WDCR= 0x0068; // 本例中不使用 //初始化锁相环 SysCtrlRegs.PLLCR = 0xA; // 等待锁相环稳定 for(i= 0; i< 5000; i++){} // HISPCP/LOSPCP 预定标寄存器设置 SysCtrlRegs.HISPCP.all = 0x0001; SysCtrlRegs.LOSPCP.all = 0x0002; // 使能选择的外设时钟 // 对于不用的时钟,一般情况下需要禁止相应的中断 SysCtrlRegs.PCLKCR.bit.EVAENCLK=1; SysCtrlRegs.PCLKCR.bit.EVBENCLK=1; SysCtrlRegs.PCLKCR.bit.SCIENCLKA=1; // SysCtrlRegs.PCLKCR.bit.SCIENCLKB=1; EDIS; BP107 }

BP106

34

// Step 7、中断服务程序 interrupt void wakeint_isr(void) { WakeCount++; // 响应中断 PieCtrlRegs.PIEACK.all = PIEACK_GROUP1; } //--------------------------------------------------------------------------// KickDog: 此函数复位看门狗定时器 void KickDog(void) { EALLOW; SysCtrlRegs.WDKEY = 0x0055; SysCtrlRegs.WDKEY = 0x00AA; EDIS; }

作用:可以通过软件配置片上外设时钟,提高

系统的灵活性和可靠性。 优点:采用软件可编程锁相环,能实现片外低 工作频率+片内较高的系统时钟,可以有效降 低系统对外部时钟的依赖和电磁干扰,提高可 靠性和稳定性。 F2812 允许采用内部振荡器或外部时钟源。 内部振荡器:X1/XCLKIN 和X2 间连石英晶体 ,典型的选用30MHz。 外部时钟:直连X1/XCLKIN引脚 ,X2 悬空。

11

EALLOW保护的寄存器

EALLOW ---Edit allow EDIS ---- Edit disable 以下寄存器受EALLOW 保护: 器件仿真寄存器 闪存寄存器 CSM 寄存器 PIE 矢量表 系统控制寄存器 GPIO MUX 寄存器 某些eCAN 寄存器

BP105

// Step 0. 包含需要的头文件 // DSP28_Device.h;采用 #include 包含器件使用的头文件 // DSP28_Example.h ;本例程需要的特定的头文件 #include "DSP28_Device.h" // 函数原型声明 interrupt void wakeint_isr(void); // 全局变量声明 Uint32 WakeCount; //产生WAKEINT 的中断次序 Uint32 LoopCount; //无限循环次数计数

12

6.1.3 时钟单元寄存器

BP98

时钟、锁相环、看门狗以及低功耗模式寄存器

13

6.1.3.1 外设时钟控制寄存器(PCLKCR)

作用:控制片上各种时钟的工作状态,使能或

禁止相关外设的时钟。

BP99

14

外设时钟控制寄存器(PCLKCR)功能定义

BP99

15

6.1.3.2高/低速外设时钟寄存器

看门狗复位寄存器及其功能定义

BP105

30

6.2.3.5 看门狗应用

//看门狗直连PIE 模块的WAKEINT中断,允许将CPU从掉电模式唤醒 // 程序放在无限循环中,可选择用KickDog 函数操作WD key 寄存器。 // 若使用KickDog 函数操作WD key 寄存器将不会产生WAKEINT中断 // 如果不对key 寄存器操作,将会产生WAKEINT 中断// // 观察变量

BP106

33

// 使能全局中断,并配置为real-time debug 模式

EINT; // 使能全局中断INTM ERTM; // 使能全局 realtime 中断DBGM // Step 6、主循环

for(;;)

{ LoopCount++; //用 KickDog 操作看门狗Key 寄存器,避免产生WAKEINT 中断 // 通常情况下,需要在主循环或定时中断中对Key 进行操作 // KickDog(); } } WAKEINT:位于PIE 的组1 的第8 中断

BP106

Байду номын сангаас

// Step 5、用户特定函数,重新分配向量(可选择),使能中断: // 重新为WAKEINT 分配 PIE 向量,并指向相应的中断服务程序 EALLOW; PieVectTable.WAKEINT = &wakeint_isr; EDIS; // 使能WAKEINT 的中断INT1 IER |= M_INT1; // 使能 PieCtrlRegs.PIEIER1.bit.INTx8 = 1; // 对程序状态寄存器进行操作,避免清除WDOVERRIDE 标识位 EALLOW; SysCtrlRegs.SCSR.all = BIT1; EDIS; // 计数器清零 WakeCount = 0; // 中断计数 LoopCount = 0; // 循环计数

BP96

5

晶体振荡器及锁相环模块

/XF_LLDIS选择系统的时钟源: 低电平时采用外部时钟; BP96 高电平时,外部时钟经PLL倍频后为系统提供时钟。

6

锁相环配置模式

系统可以通过锁相环控制寄存器来选择锁相环

的工作模式和倍频的系数。

BP96

7

处理器内部时钟电路

/XF_LLDIS为高电平,可以通过控制寄存器PLLCR软件设置系统

BP101

19

看门狗功能框图

/WDINT信号使能看门狗作为IDLE/STANDBY模式唤醒的定时器。

BP102

20

6.2.2 看门狗的基本操作

BP102

21

注意事项

当向WDKEY写0x55时,WDCNTR复位到使能

位置;只有在向WDKEY写0xAA后才会使 WDCNTR真正的复位。

任何0x55和0xAA以外的数据写到WDKEY都会

24

6.2.3.1 看门狗控制寄存器

BP103

25

看门狗控制寄存器功能定义

BP104

26

6.2.3.2 系统控制和状态寄存器

BP104

27

系统控制和状态寄存器功能定义

BP104

28

6.2.3.3 看门狗计数寄存器

看门狗计数寄存器及其功能定义

BP105

29

6.2.3.4看门狗复位寄存器功能定义

的工作频率。 注意:通过软件改变系统频率时,须等待时钟稳定后才可以继续 ;为降低系统功耗不使用的外设最好将其时钟禁止。 外设时钟也包括两种:快速外设和慢速外设。

BP97

8

改变锁相环倍频系数和外设时钟的应用程序

// 初始化锁相环及外设时钟函数: InitPll: void InitPll(Uint16 val) { volatile Uint16 iVol; if (SysCtrlRegs.PLLCR.bit.DIV != val) { EALLOW; SysCtrlRegs.PLLCR.bit.DIV = val; EDIS; // 在锁相环时钟频率切换过程中,只有当锁相环稳定后CPU 才会 切换到新的PLL 设置。因此在设置完PLLCR 后需要等待PLL 稳定 。PLL 的切换时间大约等于131072 个输入时钟周期。 DisableDog(); for(iVol= 0; iVol< ( (131072/2)/12 ); iVol++) { } } } 9

第6章 时钟及看门狗

张云洲 2010.11.16

1

章节结构

6.1 时钟单元 6.2 看门狗电路

2

6.1 F2812的时钟单元

时钟单元基本结构 锁相环电路 时钟单元寄存器

3

6.1.1 时钟单元基本结构

要点: PLL 看门狗 高、低 速外设

BP95

4

6.1.2 锁相环电路(PLL)

高速外设时钟寄存器(HISPCP)及其功能定义