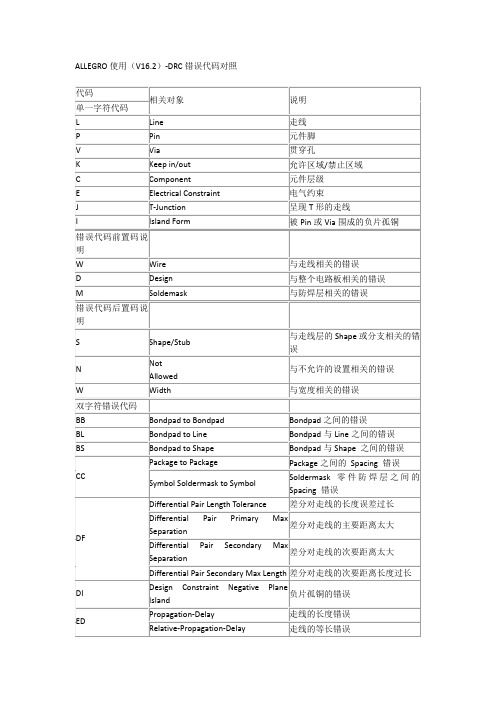

ALLEGRO使用(V16.2)-DRC错误代码对照

ALLEGRO中常见的DRC错误代码意思之欧阳歌谷创作

BL

Bondpad to Line

Bondpad与Line之间的错误

BS

Bondpad to Shape

Bondpad与Shape之间的错误

CC

Package to Package

Package之间的Spacing错误

Symbol Soldermask to Symbol

Soldermask零件防焊层之间的Spacing错误

BB Via与Test Via太近

BB Via to Through Via Spacing

BB Via与Through Via太近

Test Via to Test Via Spacing

Test Via之间太近

Test Via to Through Via Spacing

Test Via与Through Via太近

LW

MinLine Width

走线的宽度太细

Min Neck Width

走线变细的宽度太细

MA

Soldermask Alignment Error Pad

Soldermask Tolerance太小

MC

Pin/Via Soldermask to Symbol Soldermask

Pad与Symbol Soldermask之间的错误

Through Via to Via Keepout Spacing

Through Via在Via Keepout之内

LB

Min Self Crossing Loopback Length

无

LL

Line to Line Spacing

走线之间太近

LS

Line to Shape Spacing

ALLEGRO使用(V16.2)-DRC错误代码对照

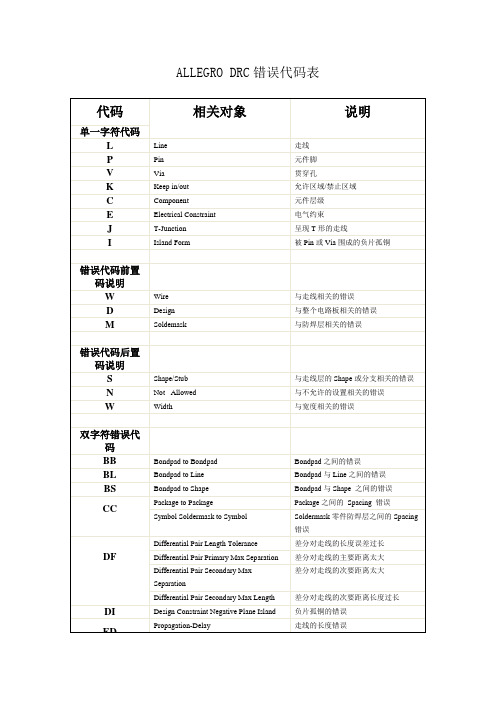

ALLEGRO使用(V16.2)‐DRC错误代码对照代码相关对象 说明单一字符代码L Line 走线P Pin 元件脚V Via 贯穿孔K Keep in/out 允许区域/禁止区域C Component 元件层级E Electrical Constraint 电气约束J T‐Junction 呈现T形的走线I Island Form 被Pin或Via围成的负片孤铜 错误代码前置码说明W Wire 与走线相关的错误D Design 与整个电路板相关的错误M Soldemask 与防焊层相关的错误错误代码后置码说明S Shape/Stub 与走线层的Shape或分支相关的错误N NotAllowed与不允许的设置相关的错误W Width 与宽度相关的错误双字符错误代码BB Bondpad to Bondpad Bondpad之间的错误BL Bondpad to Line Bondpad与Line之间的错误 BS Bondpad to Shape Bondpad与Shape 之间的错误CC Package to Package Package之间的 Spacing 错误 Symbol Soldermask to SymbolSoldermask零件防焊层之间的Spacing 错误DF Differential Pair Length Tolerance 差分对走线的长度误差过长 Differential Pair Primary MaxSeparation差分对走线的主要距离太大 Differential Pair Secondary MaxSeparation差分对走线的次要距离太大 Differential Pair Secondary Max Length差分对走线的次要距离长度过长DI Design Constraint Negative PlaneIsland负片孤铜的错误ED Propagation‐Delay 走线的长度错误 Relative‐Propagation‐Delay 走线的等长错误EL Max Exposed Length 走线在外层(TOP&BOTTOM)的长度过长EP Max Net Parallelism Length‐DistancePair已超过Net之间的平行长度ES Max Stub Length 走线的分支过长ET Electrical Topology 走线连接方式的错误EV Max Via Count 已超过走线使用的VIA的最大数目EX Max Crosstalk 已超过Crosstalk值 Max Peak Crosstalk 已超过Peak Crosstalk值HH Hold to Hold Spacing 钻孔之间的距离太近HW Diagonal Wire to Hold Spacing 斜线与钻孔之间的距离太近Hold to Orthogonal Wire Spacing钻孔与垂直/水平线之间的距离太近IM Impedance Constraint 走线的阻抗值错误 JN T Junction Not Allowed 走线呈T形的错误KB Route Keepinto BondpadBondpad在Keepin之外 Route keepoutto BondpadBondpad在keepout之内 Via KeepouttoBondpadBondpad在Via Keepout之内KC Package to Place Keepin Spacing 元件在Place Keepin之外 Package to Place Keepout Spacing 元件在Place Keepout之内KL Line to Route Keepin Spacing 走线在Route Keepin之外 Line to Route Keepout Spacing 走线在Route Keepout之内KS Shape to Route Keepin Spacing Shape在Route Keepin之外 Shape to Route Keepout Spacing Shape在Route Keepout之内KV BBVia to Route Keepin Spacing BBVia在Route Keepin之外 BBVia to Route Keepout Spacing BBVia在Route Keepout之内 BBVia to Via Keepout Spacing BBVia在Via Keepout之内Test Via to Route Keepin Spacing Test Via在Route Keepin之外 Test Via to Route Keepout Spacing Test Via在Route Keepout之内 Test Via to Via Keepout Spacing Test Via在Via Keepout之内 Through Via to Route Keepin Spacing Through Via在Route Keepin之外 Through Via to Route Keepout Spacing Through Via在Route Keepout之内Through Via to Via Keepout Spacing Through Via在Via Keepout之内LB Min Self Crossing Loopback Length 无LL Line to Line Spacing 走线之间太近LS Line to Shape Spacing 走线与Shape 太近 LW Min Line Width 走线的宽度太细Min Neck Width 走线变细的宽度太细MASoldermask Alignment Error PadSoldermask Tolerance太小MC Pin/Via Soldermask to SymbolSoldermaskPad与Symbol Soldermask之间的错误MM Pin/Via Soldermask to Pin/ViaSoldermaskPadSoldermask之间的错误PB Pin to Bondpad Pin与Bondpad之间的错误PL Line to SMD Pin Spacing 走线与SMD元件脚太近 Line to Test Pin Spacing 走线与Test元件脚太近 Line to Through Pin Spacing 走线与Through元件脚太近PP SMD Pin to SMD Pin Spacing SMD元件脚与SMD元件脚太近 SMD Pin to Test Pin Spacing SMD元件脚与Test元件脚太近 Test Pin to Test Pin Spacing Test元件脚与Test元件脚太近 Test Pin to Through Pin Spacing Test元件脚与Through元件脚太近Through Pin to SMD Pin Spacing Through元件脚与SMD元件脚太近Through Pin to Through Pin SpacingThrough元件脚与Through元件脚太近PS Shape to SMD Pin Spacing Shape与SMD元件脚太近 Shape to Test Pin Spacing Shape与Test元件脚太近 Through Pin to Shape Spacing Through元件脚与Shape太近PV BBVia to SMD Pin Spacing BBVia与SMD元件脚太近 BBVia to Test Pin Spacing BBVia与Test元件脚太近 BBVia to Through Pin Spacing BBVia 与Through元件脚太近 SMD Pin to Test Via Spacing SMD Pin与Test Via太近SMD Pin to Through Via Spacing SMD Pin与Through Via太近 Test Pin to Test Via Spacing Test Pin与Test Via太近Test Pin to Through Via Spacing Test Pin与Through Via太近 Test Via to Through Pin Spacing Test Via与Through Pin太近 Through Pin to Through Via Spacing Through Pin与Through Via太近RC Package to Hard Room 元件在其他的Room之内RE Min Length Route End Segment at 135Degree无 Min Length Route End Segment at 45/90Degree无SB 135Degree Turn to Adjacent Crossing Distance无 90Degree Turn to Adjacent Crossing Distance无SL Min Length Wire Segment 无 Min Length Single Segment Wire 无SN Allow on Etch Subclass 允许在走线层上SO Segment Orientaion 无BB Bondpad to Bondpad Bondpad之间的错误SS Shape to Shape Shape之间的错误TA Max Turn Angle 无VB Via to Bondpad Via 与Bondpad之间的错误VG Max BB Via Stagger Distance 同一段线的BB Via之间的距离太长Min BB Via Gap BB Via之间太近Min BB Via Stagger Distance 同一段线的BB Via之间的距离太近Pad/Pad Direct Connect Pad 在另一个Pad 之上VL BB Via to Line Spacing BB Via与走线太近Line to Through Via Spacing 走线与Through Via太近 Line to Test Via Spacing 走线与Test Via太近VS BB Via to Shape Spacing BB Via与Shape太近 Shape to Test Via Spacing Shape 与Test Via太近 Shape to Through Via Spacing Shape与Through Via太近VV BB Via to BB ViaSpacingBB Via之间太近BB Via to Test Via Spacing BB Via与Test Via太近BB Via to Through Via Spacing BB Via与Through Via太近 Test Via to Test Via Spacing Test Via之间太近Test Via to Through Via Spacing Test Via与Through Via太近 Through Via to Through Via Spacing Through Via之间太近WA Min Bonding Wire Length Bonding Wire 长度太短WE Min End Segment Length 无 Min Length Wire End Segment at 135Degree无 Min Length Wire End Segment at 45/90Degree无WI Max Bonding Wire Length Bonding Wire 长度太长WW Diagonal Wire to Diagonal WireSpacing斜线之间太近Diagonal Wire to Orthogonal WireSpacing斜线与垂直/水平线之间的距离太近Orthogonal Wire to Orthogonal WireSpacing垂直/水平线之间的距离太近WX Max Number of Crossing 无 Min Distance between Crossing 无XB 135 Degree Turn to Adjacent Crossing Distance无 90 Degree Turn to Adjacent Crossing 无DistanceXD Externally Determined Violation 无XS Crossing to Adjacent Segment Distances无。

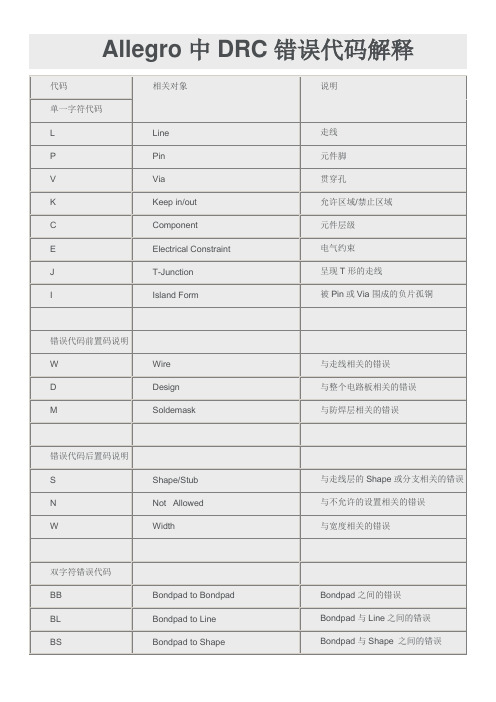

Allegro中常见的DRC错误代码解析

Hold to Orthogonal Wire Spacing

钻孔与垂直/水平线之间的距离太近

IM

Impedance Constraint

走线的阻抗值错误

JN

T Junction Not Allowed

走线呈T形的错误

KB

RouteKeepintoBondpad

Bondpad在Keepin之外

Through ViatoThrough Via Spacing

Through Via之间太近

WA

Min Bonding Wire Length

Bonding Wire长度太短

WE

Min End Segment Length

无

Min Length Wire End Segment at 135Degree

EV

Max Via Count

已超过走线使用的VIA的最大数目

EX

Max Crosstalk

已超过Crosstalk值

Max Peak Crosstalk

已超过Peak Crosstalk值

HH

Hold to Hold Spacing

钻孔之间的距离太近

HW

Diagonal Wire to Hold Spacing

BBVia与Test元件脚太近

BBViato Through Pin Spacing

BBVia与Through元件脚太近

SMD Pin to Test Via Spacing

SMD Pin与Test Via太近

SMDPin toThrough Via Spacing

SMD Pin与Through Via太近

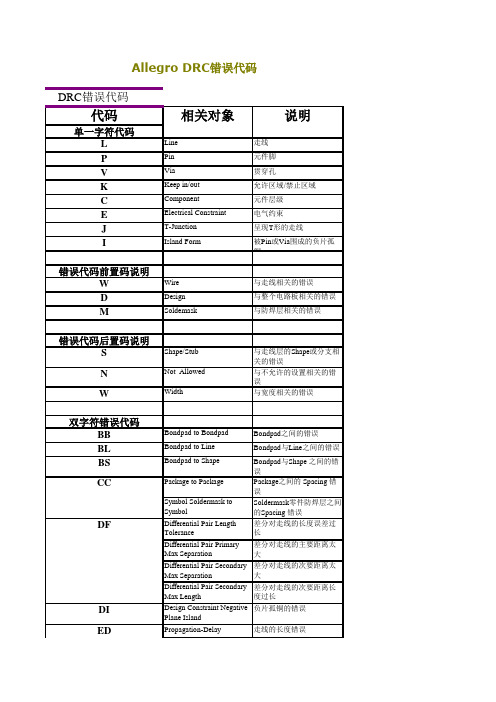

Allegro DRC错误代码清单

DRC 错误代码代码单一字符代码L Line 走线P Pin 元件脚V Via贯穿孔K Keep in/out 允许区域/禁止区域C Component 元件层级E Electrical Constraint 电气约束J T-Junction 呈现T 形的走线I Island Form被Pin 或Via 围成的负片孤铜错误代码前置码说明W Wire 与走线相关的错误D Design 与整个电路板相关的错误M Soldemask与防焊层相关的错误错误代码后置码说明SShape/Stub 与走线层的Shape 或分支相关的错误N Not Allowed 与不允许的设置相关的错误WWidth 与宽度相关的错误双字符错误代码BB Bondpad to Bondpad Bondpad 之间的错误BL Bondpad to Line Bondpad 与Line 之间的错误BSBondpad to Shape Bondpad 与Shape 之间的错误Package to Package Package 之间的 Spacing 错误Symbol Soldermask to SymbolSoldermask 零件防焊层之间的Spacing 错误Differential Pair Length Tolerance差分对走线的长度误差过长Differential Pair Primary Max Separation差分对走线的主要距离太大Differential Pair Secondary Max Separation差分对走线的次要距离太大Differential Pair Secondary Max Length差分对走线的次要距离长度过长DI Design Constraint Negative Plane Island负片孤铜的错误Propagation-Delay走线的长度错误相关对象说明CCDFEDAllegro DRC 错误代码152 | 顶:0 顶一下 | 评论:0 | 收藏| 打印 |下一篇:Allegro学习笔记之3—电源层、 >>。

ALLEGRO中常见的DRC错误代码意思

90Degree Turn to Adjacent Crossing Distance

EV

Max Via Count

已超过走线使用的VIA的最大数目

EX

Max Crosstalk

已超过Crosstalk值

Max Peak Crosstalk

已超过Peak Crosstalk值

HH

Hold to Hold Spacing

钻孔之间的距离太近

HW

Diagonal Wire to Hold Spacing

BBVia to SMD Pin Spacing

BBVia与SMD元件脚太近

BBVia to Test Pin Spacing

BBVia与Test元件脚太近

BBVia to Through Pin Spacing

BBVia与Through元件脚太近

SMDPin to Test Via Spacing

斜线与垂直/水平线之间的距离太近

Orthogonal Wire to Orthogonal Wire Spacing

垂直/水平线之间的距离太近

WX

Max Number of Crossing

无

Min Distance between Crossing

无

XB

135 Degree Turn to Adjacent Crossing Distance

Test元件脚与Test元件脚太近

Test Pin to Through Pin Spacing

Test元件脚与Through元件脚太近

Through Pin to SMD Pin Spacing

Through元件脚与SMD元件脚太近

ALLEGRO中常见的DRC错误代码意思

KL

Line to RouteKeepinSpacing

走线在RouteKeepin之外

Line to RouteKeepoutSpacing

走线在RouteKeepout之内

KS

Shape to RouteKeepinSpacing

Shape在RouteKeepin之外

Test Via在ViaKeepout之内

Through Via to RouteKeepinSpacing

Through Via在RouteKeepin之外

Through Via to RouteKeepoutSpacing

Through Via在RouteKeepout之内

Through Via to ViaKeepoutSpacing

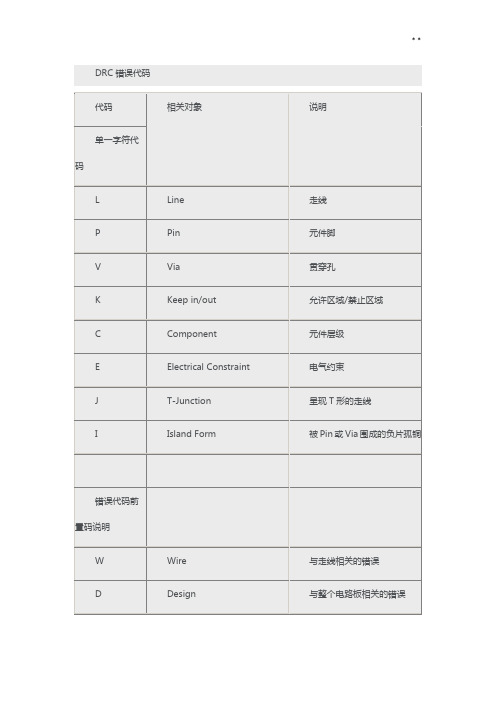

DRC错误代码

代码

相关对象

说明

单一字符代码

L

Line

走线

P

Pin

元件脚

V

Via

贯穿孔

K

Keep in/out

允许区域/禁止区域

C

Component

元件层级

E

Electrical Constraint

电气约束

J

T-Junction

呈现T形的走线

I

Island Form

被Pin或Via围成的负片孤铜

错误代码前置码说明

Through ViatoThrough Via Spacing

Through Via之间太近

WA

Min Bonding Wire Length

Bonding Wire长度太短

WE

Min End Segment Length

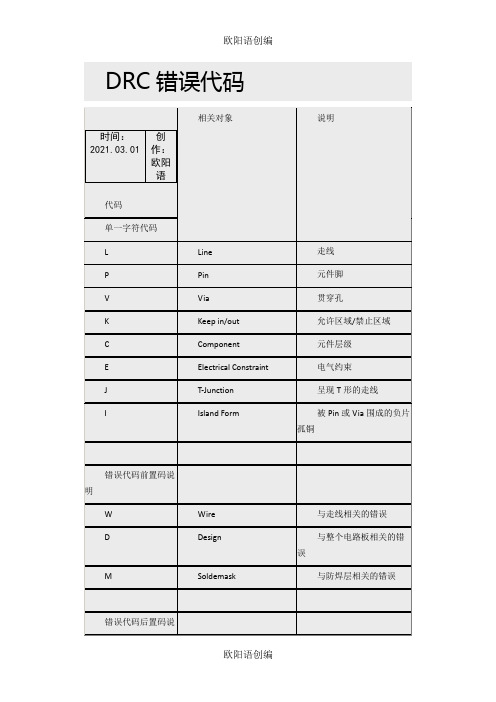

ALLEGRO中常见的DRC错误代码意思之欧阳语创编

时间:2021.03.01

创作:欧阳语

代码

相关对象

说明

单一字符代码

L

Line

走线

P

Pin

元件脚

V

Via

贯穿孔

K

Keep in/out

允许区域/禁止区域

C

Component

元件层级

E

Electrical Constraint

电气约束

J

T-Junction

呈现T形的走线

I

Island Form

BBVia to Via Keepout Spacing

BBVia在Via Keepout之内

Test Via to Route Keepin Spacing

Test Via在Route Keepin之外

Test Via to Route Keepout Spacing

Test Via在Route Keepout之内

Test Pin to Test Pin Spacing

Test元件脚与Test元件脚太近

Test Pin to Through Pin Spacing

Test元件脚与Through元件脚太近

Through Pin to SMD Pin Spacing

Through元件脚与SMD元件脚太近

Through Pin to Through Pin Spacing

EV

Max Via Count

已超过走线使用的VIA的最大数目

EX

Max Crosstalk

已超过Crosstalk值

Max Peak Crosstalk

已超过Peak Crosstalk值

ALLEGRO中常见的DRC错误代码意思讲课稿

Hold to Orthogonal Wire Spacing

钻孔与垂直/水平线之间的距离太近

IM

Impedance Constraint

走线的阻抗值错误

JN

T Junction Not Allowed

走线呈T形的错误

KB

Route Keepin to Bondpad

Bondpad在Keepin之外

BBVia to Via Keepout Spacing

BBVia在Via Keepout之内

Test Via to Route Keepin Spacing

Test Via在Route Keepin之外

Test Via to Route Keepout Spacing

Test Via在Route Keepout之内

LS

Line to Shape Spacing

走线与Shape太近

LW

Min Line Width

走线的宽度太细

Min Neck Width

走线变细的宽度太细

MA

Soldermask Alignment Error Pad

Soldermask Tolerance太小

MC

Pin/Via Soldermask to Symbol Soldermask

Pad与Symbol Soldermask之间的错误

MM

Pin/Via Soldermask to Pin/Via Soldermask

Pad Soldermask之间的错误

PB

Pin to Bondpad

EV

Max Via Count

已超过走线使用的VIA的最大数目

Protel中ERC错误中英对照大全

Protel中ERC错误中英对照大全在PROTEL DXP2004中的DRC规则检查项目,对于一些英文水平较薄弱的朋友是一个大难题,英文水平有限,仅供参考:PROTEL DXP2004 DRC 规则英文对照一、Error Reporting 错误报告A:Violations Associated with Buses 有关总线电气错误的各类型(共12项)bus indices out of range 总线分支索引超出范围Bus range syntax errors 总线范围的语法错误Illegal bus range values 非法的总线范围值Illegal bus definitions 定义的总线非法Mismatched bus label ordering 总线分支网络标号错误排序Mismatched bus/wire object on wire/bus 总线/导线错误的连接导线/总线Mismatched bus widths 总线宽度错误Mismatched bus section index ordering 总线范围值表达错误Mismatched electrical types on bus 总线上错误的电气类型Mismatched generics on bus (first index) 总线范围值的首位错误Mismatched generics on bus (second index) 总线范围值末位错误Mixed generics and numeric bus labeling 总线命名规则错误B:Violations Associated Components 有关元件符号电气错误(共20项)Component Implementations with duplicate pins usage 元件管脚在原理图中重复被使用Component Implementations with invalid pin mappings 元件管脚在应用中和PCB封装中的焊盘不符Component Implementations with missing pins in sequence 元件管脚的序号出现序号丢失Component contaning duplicate sub-parts 元件中出现了重复的子部分Component with duplicate Implementations 元件被重复使用Component with duplicate pins 元件中有重复的管脚Duplicate component models 一个元件被定义多种重复模型Duplicate part designators 元件中出现标示号重复的部分Errors in component model parameters 元件模型中出现错误的的参数Extra pin found in component display mode 多余的管脚在元件上显示Mismatched hidden pin component 元件隐藏管脚的连接不匹配Mismatched pin visibility 管脚的可视性不匹配Missing component model parameters 元件模型参数丢失Missing component models 元件模型丢失Missing component models in model files 元件模型不能在模型文件中找到Missing pin found in component display mode 不见的管脚在元件上显示Models found in different model locations 元件模型在未知的路径中找到Sheet symbol with duplicate entries 方框电路图中出现重复的端口Un-designated parts requiring annotation 未标记的部分需要自动标号Unused sub-part in component 元件中某个部分未使用C:violations associated with document 相关的文档电气错误(共10项)conflicting constraints 约束不一致的duplicate sheet symbol name 层次原理图中使用了重复的方框电路图duplicate sheet numbers 重复的原理图图纸序号missing child sheet for sheet symbol 方框图没有对应的子电路图missing configuration target 缺少配置对象missing sub-project sheet for component 元件丢失子项目multiple configuration targets 无效的配置对象multiple top-level document 无效的顶层文件port not linked to parent sheet symbol 子原理图中的端口没有对应到总原理图上的端口sheet enter not linked to child sheet 方框电路图上的端口在对应子原理图中没有对应端口D:violations associated with nets 有关网络电气错误(共19项)adding hidden net to sheet 原理图中出现隐藏网络adding items from hidden net to net 在隐藏网络中添加对象到已有网络中auto-assigned ports to device pins 自动分配端口到设备引脚duplicate nets 原理图中出现重名的网络floating net labels 原理图中有悬空的网络标签global power-objects scope changes 全局的电源符号错误net parameters with no name 网络属性中缺少名称net parameters with no value 网络属性中缺少赋值nets containing floating input pins 网络包括悬空的输入引脚nets with multiple names 同一个网络被附加多个网络名nets with no driving source 网络中没有驱动nets with only one pin 网络只连接一个引脚nets with possible connection problems 网络可能有连接上的错误signals with multiple drivers 重复的驱动信号sheets containing duplicate ports 原理图中包含重复的端口signals with load 信号无负载signals with drivers 信号无驱动unconnected objects in net 网络中的元件出现未连接对象unconnected wires 原理图中有没连接的导线E:Violations associated with others有关原理图的各种类型的错误(3项)No Error 无错误Object not completely within sheet boundaries 原理图中的对象超出了图纸边框Off-grid object原理图中的对象不在格点位置F:Violations associated with parameters 有关参数错误的各种类型same parameter containing different types 相同的参数出现在不同的模型中same parameter containing different values 相同的参数出现了不同的取值二、Comparator 规则比较A:Differences associated with components 原理图和PCB上有关的不同(共16项) Changed channel class name 通道类名称变化Changed component class name 元件类名称变化Changed net class name 网络类名称变化Changed room definitions 区域定义的变化Changed Rule 设计规则的变化Channel classes with extra members 通道类出现了多余的成员Component classes with extra members 元件类出现了多余的成员Difference component 元件出现不同的描述Different designators 元件标示的改变Different library references 出现不同的元件参考库Different types 出现不同的标准Different footprints 元件封装的改变Extra channel classes 多余的通道类Extra component classes 多余的元件类Extra component 多余的元件Extra room definitions 多余的区域定义B:Differences associated with nets 原理图和PCB上有关网络不同(共6项)Changed net name 网络名称出现改变Extra net classes 出现多余的网络类Extra nets 出现多余的网络Extra pins in nets 网络中出现多余的管脚Extra rules 网络中出现多余的设计规则Net class with Extra members 网络中出现多余的成员C:Differences associated with parameters 原理图和PCB上有关的参数不同(共3项)Changed parameter types 改变参数类型Changed parameter value 改变参数的取值Object with extra parameter 对象出现多余的参数【Violations Associated with Buses】栏——总线电气错误类型(1)【Bus indices out of range】:总线分支索引超出范围。

ALLEGRO-DRC-错误代码

ALLEGRO-DRC-错误代码(2013-01-04 10:54:48)转载▼标签:杂谈Q: Allegra中颜色设置好以后,应该可以导出相关设置文件,下次碰到不同设置的板子,看着难受就可以直接读入自己的文件改变设置了A:16.2版本的可以这样做:file->export->parameters, 选中颜色就行了,其它的参数一样可以保存。

Q:ALLEGRO 自动布线后,为直角.如何调整成45度角走线A: ROUTE –GLOSS—PARAMETERS—CONVERT CORNET TO ARC一、群组布线;群组布线包括总线布线和一次布多外Trance.1.一次布多个Trance .鼠标左键进行选择多外PIN,或VIA. 同时可以在布线过程中用右键切换到单线模式。

群组布线只能在一个层中,不允许打过孔。

也可以在群组布线过程中,右键,―CHANGE Control Trace‖Cadence CIS即原理图中,放大缩小缩小的快捷键按住CTRL键+鼠标中间滚轮)5. ALLEGRO 出光绘文件前,最好加个PHOTO_OUTLINE,确认输出光绘文件的范围Class: manufacture — Subclass: photoplot outline6. 光绘设置详解/bbs/viewthread.php?tid=28&page=1ALLEGRO 标注 1. dimension linear : 对于比较规则,简单的板子,通常采用.2.dimension datum :对于较复杂的板子可以采用。

先确定一个基准点,接下来对每个点所标注的数据都是相对基准点的坐标值。

Manufacture——dimension/draft —–dimension linear / dimension datum2.表层铺铜时,由于铺铜和PIN 的间距问题,在PIN 和PIN 之间经常产生一些尖角。

产生这种原因的解决办法:一。

ALLEGRO DRC错误代码表

BBVia在Via Keepout之内

Test Via to Route Keepin Spacing

Test Via在Route Keepin之外

Test Via to Route Keepout Spacing

Test Via在Route Keepout之内

无

VB

Via to Bondpad

Via与Bondpad之间的错误

VG

Max BB Via Stagger Distance

同一段线的BB Via之间的距离太长

Min BB Via Gap

BB Via之间太近

Min BB Via Stagger Distance

同一段线的BB Via之间的距离太近

Pad/Pad Direct Connect

Through Via在Route Keepout之内

Through Via to Via Keepout Spacing

Through Via在Via Keepout之内

LB

Min Self Crossing Loopback Length

无

LL

Line to Line Spacing

走线之间太近

Pad在另一个Pad之上

VL

BB Via to Line Spacing

BB Via与走线太近

Line to Through Via Spacing

走线与Through Via太近

Line to Test Via Spacing

走线与Test Via太近

VS

BB Via to Shape Spacing

BBVia to SMD Pin Spacing

allegro错误代码对应

双字符错误代码BB Bondpad to BondpadCC Package to PackageSymbol Soldermask to SymbolBL Bondpad to Line BS Bondpad to ShapeDF Differential Pair Length Tolerance Differential Pair Primary Max Separation Differential Pair Secondary Max Separation Differential Pair Secondary Max LengthDI Design Constraint Negative Plane IslandED Propagation-Delay Relative-Propagation-DelayEL Max Exposed LengthEP Max Net Parallelism Length-Distance Pair ES Max Stub LengthETRoute Keepinto BondpadRoute keepoutto BondpadVia KeepouttoBondpadETElectrical Topology EV Max Via CountEXMax CrosstalkMax Peak Crosstalk HH Hold to Hold SpacingHWDiagonal Wire to Hold Spacing Hold to Orthogonal Wire Spacing IMImpedance Constraint JN T Junction Not AllowedKC Package to Place Keepin Spacing Package to Place Keepout SpacingKB KS Shape to Route Keepin Spacing Shape to Route Keepout SpacingKL Line to Route Keepin Spacing Line to Route Keepout SpacingBBVia to Route Keepin SpacingSoldermask Alignment Error Pad KV BBVia to Route Keepout SpacingBBVia to Via Keepout SpacingTest Via to Route Keepin SpacingTest Via to Route Keepout SpacingThrough Via to Route Keepout Spacing Through Via to Via Keepout Spacing Test Via to Via Keepout SpacingThrough Via to Route Keepin Spacing LBMin Self Crossing Loopback Length LLLine to Line Spacing LS Line to Shape SpacingLWMin Line WidthMin Neck Width MMPin/Via Soldermask to Pin/Via Soldermask PB Pin to BondpadMA MC Pin/Via Soldermask to Symbol SoldermaskPL Line to SMD Pin Spacing Line to Test Pin Spacing Line to Through Pin SpacingPP SMD Pin to SMD Pin Spacing SMD Pin to Test Pin SpacingTest Pin to Test Pin SpacingTest Pin to Through Pin Spacing Through Pin to SMD Pin Spacing Through Pin to Through Pin SpacingPS Shape to SMD Pin Spacing Shape to Test Pin Spacing Through Pin to Shape Spacing BBVia to SMD Pin Spacing BBVia to Test Pin Spacing BBVia to Through Pin Spacing SMD Pin to Test Via Spacing SMD Pin to Through Via Spacing Test Pin to Test Via Spacing Test Pin to Through Via SpacingSB SNAllow on Etch Subclass PVTest Via to Through Pin SpacingThrough Pin to Through Via Spacing RC Package to Hard RoomRE Min Length Route End Segment at 135Degree Min Length Route End Segment at 45/90Degree SLMin Length Wire SegmentMin Length Single Segment Wire 135Degree Turn to Adjacent Crossing Distance90Degree Turn to Adjacent Crossing Distance SOSegment Orientaion BBBondpad to Bondpad SSShape to Shape TAMax Turn Angle VB Via to BondpadVGMax BB Via Stagger DistanceMin BB Via GapMin BB Via Stagger DistanceBB Via to BB ViaSpacingVG Pad/Pad Direct ConnectVL BB Via to Line SpacingLine to Through Via Spacing Line to Test Via SpacingVS BB Via to Shape SpacingShape to Test Via SpacingShape to Through Via SpacingBB Via to Through Via Spacing Test Via to Test Via SpacingTest Via to Through Via Spacing Min Length Wire End Segment at 45/90Degree Through Via to Through Via Spacing WA Min Bonding Wire LengthVVBB Via to Test Via SpacingWEMin End Segment LengthMin Length Wire End Segment at 135Degree WI Max Bonding Wire LengthDiagonal Wire to Diagonal Wire SpacingXS Crossing to Adjacent Segment DistancesDiagonal Wire to Orthogonal Wire Spacing Orthogonal Wire to Orthogonal Wire SpacingWX Max Number of CrossingMin Distance between CrossingWW XDExternally Determined ViolationXB135 Degree Turn to Adjacent Crossing Distance 90 Degree Turn to Adjacent Crossing DistanceBondpad之间的错误Bondpad与Line之间的错误Bondpad与Shape 之间的错误Package之间的 Spacing 错误Soldermask零件防焊层之间的Spacing 错误差分对走线的长度误差过长差分对走线的主要距离太大差分对走线的次要距离太大差分对走线的次要距离长度过长负片孤铜的错误走线的长度错误走线的等长错误走线在外层(TOP&BOTTOM)的长度过长已超过Net之间的平行长度走线的分支过长走线连接方式的错误已超过走线使用的VIA的最大数目已超过Crosstalk值已超过Peak Crosstalk值钻孔之间的距离太近斜线与钻孔之间的距离太近钻孔与垂直/水平线之间的距离太近走线的阻抗值错误走线呈T形的错误Bondpad在Keepin之外Bondpad在keepout之内Bondpad在Via Keepout之内元件在Place Keepin之外元件在Place Keepout之内走线在Route Keepin之外走线在Route Keepout之内Shape在Route Keepin之外Shape在Route Keepout之内BBVia在Route Keepin之外BBVia在Route Keepout之内BBVia在Via Keepout之内Test Via在Route Keepin之外Test Via在Route Keepout之内Test Via在Via Keepout之内Through Via在Route Keepin之外Through Via在Route Keepout之内Through Via在Via Keepout之内无走线之间太近走线与Shape 太近走线的宽度太细走线变细的宽度太细Soldermask Tolerance太小Pad与Symbol Soldermask之间的错误PadSoldermask之间的错误Pin与Bondpad之间的错误走线与SMD元件脚太近走线与Test元件脚太近走线与Through元件脚太近SMD元件脚与SMD元件脚太近SMD元件脚与Test元件脚太近Test元件脚与Test元件脚太近Test元件脚与Through元件脚太近Through元件脚与SMD元件脚太近Through元件脚与Through元件脚太近Shape与SMD元件脚太近Shape与Test元件脚太近Through元件脚与Shape太近BBVia与SMD元件脚太近BBVia与Test元件脚太近BBVia 与Through元件脚太近SMD Pin与Test Via太近SMD Pin与Through Via太近Test Pin与Test Via太近Test Pin与Through Via太近Test Via与Through Pin太近Through Pin与Through Via太近元件在其他的Room之内无无无无无无允许在走线层上无Bondpad之间的错误Shape之间的错误无Via 与Bondpad之间的错误同一段线的BB Via之间的距离太长BB Via之间太近同一段线的BB Via之间的距离太近在另一个Pad 之上Pad 在另一个Pad 之上BB Via与走线太近走线与Through Via太近走线与Test Via太近BB Via与Shape太近Shape 与Test Via太近Shape与Through Via太近BB Via之间太近BB Via与Test Via太近BB Via与Through Via太近Test Via之间太近Test Via与Through Via太近Through Via之间太近Bonding Wire 长度太短无无无Bonding Wire 长度太长斜线之间太近斜线与垂直/水平线之间的距离太近垂直/水平线之间的距离太近无无无无无无。

allegro错误代码

Line to Shape Spacing

走线与Shape太近

LW

Min Line Width

走线的宽度太细

Min Neck Width

走线变细的宽度太细

MA

Soldermask Alignment Error Pad

Soldermask Tolerance太小

MC

Pin/Via Soldermask to Symbol Soldermask

Route keepout to Bondpad

Bondpad在keepout之内

Via Keepout to Bondpad

Bondpad在Via Keepout之内

KC

Package to Place Keepin Spacing

元件在Place Keepin之外

Package to Place Keepout Spacing

Bondpad之间的错误

BL

Bondpad to Line

Bondpad与Line之间的错误

BS

Bondpad to Shape

Bondpad与Shape之间的错误

CC

Package to Package

Package之间的Spacing错误

Symbol Soldermask to Symbol

Soldermask零件防焊层之间的Spacing错误

BB Via与Test Via太近

BB Via to Through Via Spacing

BB Via与Through Via太近

Test Via to Test Via Spacing

Test Via之间太近

Test Via to Through Via Spacing

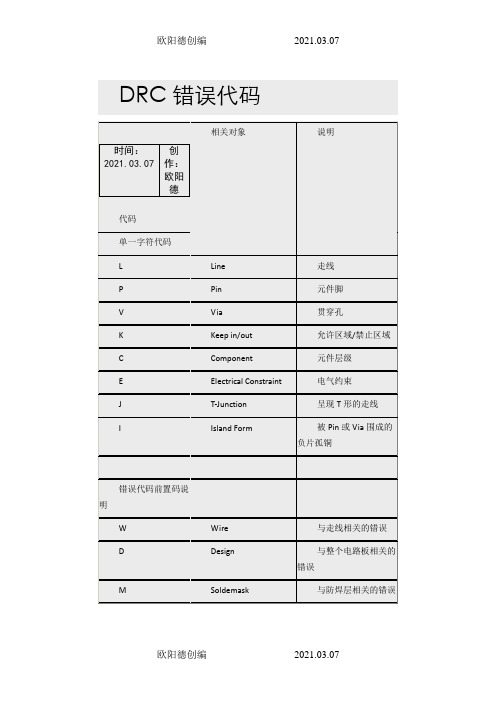

ALLEGRO中常见的DRC错误代码意思之欧阳德创编

Test Via与Through Pin太近

Through Pin to Through Via Spacing

Through Pin与Through Via太近

RC

Package to Hard Room

元件在其他的Room之内

RE

Min Length Route End Segment at 135Degree

Route keepout toBondpad

Bondpad在keepout之内

Via Keepout to Bondpad

Bondpad在Via Keepout之内

KC

Package to Place Keepin Spacing

元件在Place Keepin之外

Package to Place Keepout Spacing

BBVia to SMD Pin Spacing

BBVia与SMD元件脚太近

BBVia to Test Pin Spacing

BBVia与Test元件脚太近

BBVia to Through Pin Spacing

BBVia与Through元件脚太近

SMD Pin to Test Via Spacing

被Pin或Via围成的负片孤铜

错误代码前置码说明

W

Wire

与走线相关的错误

D

Design

与整个电路板相关的错误

M

Soldemask

与防焊层相关的错误

错误代码后置码说明

S

Shape/Stub

与走线层的Shape或分支相关的错误

N

Not Allowed

ALLEGRO中常见的DRC错误代码意思之欧阳道创编

Shape to Test Via Spacing

Shape与Test Via太近

Shape to Through Via Spacing

Shape与Through Via太近

VV

BB Via to BB Via Spacing

BB Via之间太近

BB Via to Test Via Spacing

差分对走线的次要距离太大

Differential Pair Secondary Max Length

差分对走线的次要距离长度过长

DI

Design ConstraintNegative Plane Island

负片孤铜的错误

ED

Propagation-Delay

走线的长度错误

Relative-Propagation-Delay

元件在Place Keepout之内

KL

Line to Route Keepin Spacing

走线在Route Keepin之外

Line to Route Keepout Spacing

走线在Route Keepout之内

KS

Shape to Route Keepin Spacing

Shape在Route Keepin之外

SMD Pin与Test Via太近

SMD Pin to Through Via Spacing

SMD Pin与Through Via太近

Test Pin to Test Via Spacing

Test Pin与Test Via太近

Test Pin to Through ViaSpacing

Test Pin与ThroughVia太近

ALLEGRO中常见的DRC错误代码意思之欧阳化创编

Hold to Orthogonal Wire Spacing

钻孔与垂直/水平线之间的距离太近

IM

Impedance Constraint

走线的阻抗值错误

JN

T Junction Not Allowed

走线呈T形的错误

KB

Route Keepin to Bondpad

Bondpad在Keepin之外

Through Via to Through Via Spacing

Through Via之间太近

WA

Min Bonding Wire Length

Bonding Wire长度太短

WE

Min End Segment Length

无

Min Length Wire End Segment at 135Degree

BB Via与Test Via太近

BB Via to Through Via Spacing

BB Via与Through Via太近

Test Via to Test Via Spacing

Test Via之间太近

Test Via to Through Via Spacing

Test Via与Through Via太近

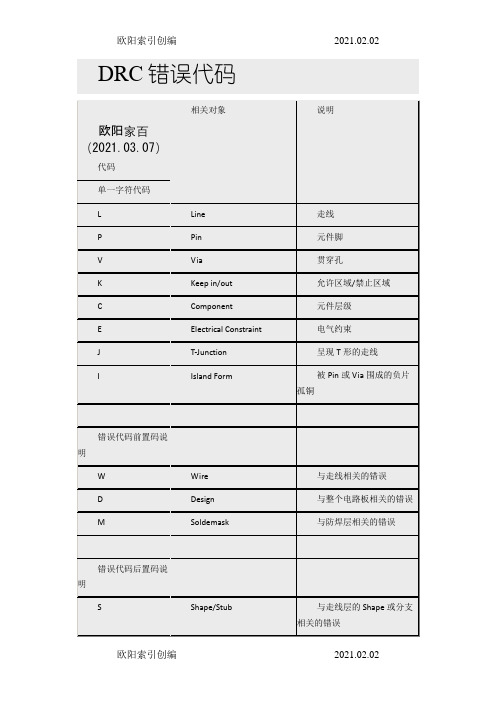

DRC错误代码

时间:2021.02.06

创作:欧阳化

代码

相关对象

说明

单一字符代码

L

Line

走线

P

Pin

元件脚

V

Via

贯穿孔

K

Keep in/out

允许区域/禁止区域

C

Component

元件层级

E

Electrical Constraint

ALLEGRO中常见的DRC错误代码意思之欧阳索引创编

Test元件脚与Test元件脚太近

Test Pin to Through Pin Spacing

Test元件脚与Through元件脚太近

Through Pin to SMD Pin Spacing

Through元件脚与SMD元件脚太近

Through Pin to Through Pin Spacing

Shape to Route KeepoutSpacing

Shape在Route Keepout之内

KV

BBVia to Route Keepin Spacing

BBVia在Route Keepin之外

BBVia to Route Keepout Spacing

BBVia在Route Keepout之内

EV

Max Via Count

已超过走线使用的VIA的最大数目

EX

Max Crosstalk

已超过Crosstalk值

Max Peak Crosstalk

已超过Peak Crosstalk值

HH

Hold to Hold Spacing

钻孔之间的距离太近

HW

Diagonal Wire to Hold Spacing

Bondpad之间的错误

BL

Bondpad to Line

Bondpad与Line之间的错误

BS

Bondpad to Shape

Bondpad与Shape之间的错误

CC

Package to Package

Package之间的Spacing错误

Symbol Soldermask to Symbol

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ALLEGRO使用(V16.2)-DRC错误代码对照代码相关对象说明单一字符代码L走线LineP元件脚PinV贯穿孔ViaK允许区域/禁止区域Keep in/outC元件层级ComponentE电气约束Electrical ConstraintJ呈现T形的走线T-JunctionI被Pin或Via围成的负片孤铜Island Form错误代码前置码说明W与走线相关的错误WireDDesign与整个电路板相关的错误MSoldemask与防焊层相关的错误错误代码后置码说明SShape/Stub与走线层的Shape或分支相关的错误NNotAllowed与不允许的设置相关的错误WWidth与宽度相关的错误双字符错误代码BBBondpad to BondpadBondpad之间的错误BLBondpad to LineBondpad与Line之间的错误BSBondpad to ShapeBondpad与Shape 之间的错误CC Package to PackagePackage之间的Spacing 错误Symbol Soldermask to Symbol Soldermask零件防焊层之间的Spacing错误DFDifferential Pair Length Tolerance差分对走线的长度误差过长Differential Pair Primary Max Separation差分对走线的主要距离太大Differential Pair Secondary Max Separation差分对走线的次要距离太大Differential Pair Secondary Max Length差分对走线的次要距离长度过长DIDesign Constraint Negative Plane Island负片孤铜的错误ED Propagation-Delay走线的长度错误Relative-Propagation-Delay走线的等长错误ELMax Exposed Length 走线在外层(TOP&BOTTOM)的长度过长EPMax Net Parallelism Length-Distance Pair已超过Net之间的平行长度ESMax Stub Length走线的分支过长ETElectrical Topology走线连接方式的错误EVMax Via Count已超过走线使用的VIA的最大数目EX Max Crosstalk已超过Crosstalk值Max Peak Crosstalk已超过Peak Crosstalk值HHHold to Hold Spacing钻孔之间的距离太近HW Diagonal Wire to Hold Spacing斜线与钻孔之间的距离太近Hold to Orthogonal Wire Spacing钻孔与垂直/水平线之间的距离太近IMImpedance Constraint走线的阻抗值错误JNT Junction Not Allowed走线呈T形的错误KB Route Keepinto BondpadBondpad在Keepin之外Route keepoutto BondpadBondpad在keepout之内Via KeepouttoBondpadBondpad在Via Keepout之内KC Package to Place Keepin Spacing 元件在Place Keepin之外Package to Place Keepout Spacing元件在Place Keepout之内KL Line to Route Keepin Spacing走线在Route Keepin之外Line to Route Keepout Spacing走线在Route Keepout之内KS Shape to Route Keepin Spacing Shape在Route Keepin之外Shape to Route Keepout SpacingShape在Route Keepout之内KVBBVia to Route Keepin SpacingBBVia在Route Keepin之外BBVia to Route Keepout SpacingBBVia在Route Keepout之内BBVia to Via Keepout SpacingBBVia在Via Keepout之内Test Via to Route Keepin SpacingTest Via在Route Keepin之外Test Via to Route Keepout SpacingTest Via在Route Keepout之内Test Via to Via Keepout SpacingTest Via在Via Keepout之内Through Via to Route Keepin SpacingThrough Via在Route Keepin之外Through Via to Route Keepout SpacingThrough Via在Route Keepout之内Through Via to Via Keepout SpacingThrough Via在Via Keepout之内LBMin Self Crossing Loopback Length无LLLine to Line Spacing走线之间太近LSLine to Shape Spacing走线与Shape 太近LW Min Line Width走线的宽度太细Min Neck Width走线变细的宽度太细MASoldermask Alignment ErrorPadSoldermask Tolerance太小MCPin/Via Soldermask to Symbol SoldermaskPad与Symbol Soldermask之间的错误MMPin/Via Soldermask to Pin/Via SoldermaskPad Soldermask之间的错误PBPin to BondpadPin与Bondpad之间的错误PLLine to SMD Pin Spacing走线与SMD元件脚太近Line to Test Pin Spacing走线与Test元件脚太近Line to Through Pin Spacing走线与Through元件脚太近PPSMD Pin to SMD Pin SpacingSMD元件脚与SMD元件脚太近SMD Pin to Test Pin SpacingSMD元件脚与Test元件脚太近Test Pin to Test Pin SpacingTest元件脚与Test元件脚太近Test Pin to Through Pin SpacingTest元件脚与Through元件脚太近Through Pin to SMD Pin SpacingThrough元件脚与SMD元件脚太近Through Pin to Through Pin SpacingThrough元件脚与Through元件脚太近PSShape to SMD Pin SpacingShape与SMD元件脚太近Shape to Test Pin SpacingShape与Test元件脚太近Through Pin to Shape SpacingThrough元件脚与Shape太近PVBBVia to SMD Pin SpacingBBVia与SMD元件脚太近BBVia to Test Pin SpacingBBVia与Test元件脚太近BBVia to Through Pin SpacingBBVia 与Through元件脚太近SMD Pin to Test Via SpacingSMD Pin与Test Via太近SMD Pin to Through Via SpacingSMD Pin与Through Via太近Test Pin to Test Via SpacingTest Pin与Test Via太近Test Pin to Through Via SpacingTest Pin与Through Via太近Test Via to Through Pin SpacingTest Via与Through Pin太近Through Pin to Through Via SpacingThrough Pin与Through Via太近RCPackage to Hard Room元件在其他的Room之内RE Min Length Route End Segment at135Degree无Min Length Route End Segment at45/90Degree无SB 135Degree Turn to Adjacent CrossingDistance无90Degree Turn to Adjacent CrossingDistance无SL Min Length Wire Segment无Min Length Single Segment Wire无SNAllow on Etch Subclass允许在走线层上SOSegment Orientaion无BBBondpad to BondpadBondpad之间的错误SSShape to ShapeShape之间的错误TAMax Turn Angle无VBVia to BondpadVia 与Bondpad之间的错误VG Max BB Via Stagger Distance同一段线的BB Via之间的距离太长Min BB Via GapBB Via之间太近Min BB Via Stagger Distance同一段线的BB Via之间的距离太近Pad/Pad Direct ConnectPad 在另一个Pad 之上VLBB Via to Line SpacingBB Via与走线太近Line to Through Via Spacing走线与Through Via太近Line to Test Via Spacing走线与Test Via太近VSBB Via to Shape SpacingBB Via与Shape太近Shape to Test Via SpacingShape 与Test Via太近Shape to Through Via SpacingShape与Through Via太近VVBB Via to BB ViaSpacingBB Via之间太近BB Via to Test Via SpacingBB Via与Test Via太近BB Via to Through Via SpacingBB Via与Through Via太近Test Via to Test Via SpacingTest Via之间太近Test Via to Through Via SpacingTest Via与Through Via太近Through Via to Through Via SpacingThrough Via之间太近WAMin Bonding Wire LengthBonding Wire 长度太短WEMin End Segment Length无Min Length Wire End Segment at 135Degree无Min Length Wire End Segment at45/90Degree无WIMax Bonding Wire LengthBonding Wire 长度太长WWDiagonal Wire to Diagonal Wire Spacing斜线之间太近斜线与垂直/水平线之间的距离太近Diagonal Wire to Orthogonal Wire SpacingOrthogonal Wire to Orthogonal Wire垂直/水平线之间的距离太近SpacingWX Max Number of Crossing无无Min Distance between Crossing无XB135 Degree Turn to Adjacent CrossingDistance90 Degree Turn to Adjacent Crossing无DistanceXD无Externally Determined ViolationXSCrossing to Adjacent Segment Distances无。