MAP40中文资料

PSD4235G2-70U;PSD4235G2-90U;PSD4235G2-90UI;中文规格书,Datasheet资料

February 2009 Rev 41/129PSD4235G2Flash in-system programmable (ISP)for 16-bit MCUs (5 V supply)Features■Dual bank Flash memories– 4 Mbit of Primary Flash memory (8 uniform sectors, 32K x 16)–256 Kbit Secondary Flash memory with 4 sectors–Concurrent operation: read from onememory while erasing and writing the other ■64 Kbit SRAM■PLD with macrocells–Over 3000 gates of PLD: CPLD and DPLD –CPLD with 16 output macrocells (OMCs) and 24 input macrocells (IMCs)–DPLD - user defined internal chip select decoding ■7 L/O ports with 52 I/O pins–52 individually configurable I/O port pins that can be used for the following functions:–MCU I/Os –PLD I/Os–Latched MCU address output –Special function l/Os–l/O ports may be configured as open-drain outputs ■In-system programming (ISP) with JTAG –Built-in JTAG compliant serial port allows full-chip In-System Programmability–Efficient manufacturing allow easy product testing and programmingUse low cost FlashLINK cable with PC■Page register–Internal page register that can be used to expand the microcontroller address space by a factor of 256–Programmable power management ●High endurance–100,000 Erase/write c ycles of Flash memory–1,000 Erase/WRITE Cycles of PLD –15 Y ear Data Retention ■Single supply voltage –5V ±10%■Memory speed–70ns Flash memory and SRAM access time ■Packages are ECOPACK ®Contents PSD4235G2Contents1Summary description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121.1In-system programming (ISP) via JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . 121.1.1First time programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121.1.2Inventory build-up of pre-programmed devices . . . . . . . . . . . . . . . . . . . 121.1.3Expensive sockets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121.2In-application programming (IAP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121.2.1Simultaneous READ and WRITE to Flash memory . . . . . . . . . . . . . . . . 131.2.2Complex memory mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131.2.3Separate Program and Data space . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131.3PSDsoft™ Express . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 2Pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163PSD architectural overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213.1Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213.2PLDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213.3I/O ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213.4MCU bus interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223.5ISP via JTAG port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223.6In-System Programming (ISP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223.7In-application programming (IAP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223.8Page register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223.9Power management unit (PMU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 4Development system . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 5PSD register description and address offsets . . . . . . . . . . . . . . . . . . . 266Register bit definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 286.1Data-In registers - port A, B, C, D, E, F, G . . . . . . . . . . . . . . . . . . . . . . . . 286.2Data-out registers - port A, B, C, D, E, F, G . . . . . . . . . . . . . . . . . . . . . . . 286.3Direction registers - ports A, B, C, D, E, F, G . . . . . . . . . . . . . . . . . . . . . . 286.4Control registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 2/129PSD4235G2Contents6.5Drive registers - Ports A, B, D, E, G . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 296.6Drive registers - Ports C and F . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 296.7Enable-Out registers - Ports A, B, C, F . . . . . . . . . . . . . . . . . . . . . . . . . . 296.8Input macrocells registers- ports A, B, C . . . . . . . . . . . . . . . . . . . . . . . . . 296.9Output macrocells A/B registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 306.10Mask macrocells A/B registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 306.11Flash Memory Protection register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 306.12Flash Boot Protection register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316.13JTAG Enable register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316.14Page register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316.15PMMR0 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316.16PMMR2 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 326.17VM register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 336.18Memory_ID0 registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 346.19Memory_ID1 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 347Detailed operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 357.1Memory blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 357.2Primary Flash memory and Secondary Flash memory description . . . . . 367.2.1Memory block Select signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367.2.2Ready/Busy (PE4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367.3Memory operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 368Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 398.1Power-up condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 398.2Reading Flash memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 408.3Read memory contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 408.4Read Primary Flash identifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 408.5Read Memory Sector Protection status . . . . . . . . . . . . . . . . . . . . . . . . . . 408.6Reading the Erase/Program status bits . . . . . . . . . . . . . . . . . . . . . . . . . . 408.7Data Polling (DQ7) - DQ15 for Motorola . . . . . . . . . . . . . . . . . . . . . . . . . . 418.8Toggle flag (DQ6) - DQ14 for Motorola . . . . . . . . . . . . . . . . . . . . . . . . . . 418.9Error flag (DQ5) - DQ13 for Motorola . . . . . . . . . . . . . . . . . . . . . . . . . . . . 428.10Erase timeout flag (DQ3) - DQ11 for Motorola . . . . . . . . . . . . . . . . . . . . . 423/129Contents PSD4235G29Programming Flash memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 439.1Data polling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 439.2Data toggle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 449.3Unlock Bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4510Erasing Flash memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4710.1Flash Bulk Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4710.2Suspend Sector Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4810.3Resume Sector Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4811Specific features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4911.1Flash Memory Sector Protect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4911.2Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4911.3Reset (RESET) pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49 12SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5013Memory Select signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5113.1Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5113.2Memory Select configuration for MCUs with separateProgram and Data spaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5113.3Separate space modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5213.4Combined space modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5213.580C51XA memory map example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53 14Page register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54 15Memory ID registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55 16PLDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56 17Decode PLD (DPLD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5918Complex PLD (CPLD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6118.1Output macrocell (OMC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6218.2Product Term Allocator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63 4/129PSD4235G2Contents18.3Loading and Reading the output macrocells (OMC) . . . . . . . . . . . . . . . . 6418.4The OMC Mask register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6418.5The output Enable of the OMC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6418.6Input macrocells (IMC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6518.7External Chip Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6719MCU bus interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6919.1PSD interface to a multiplexed bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7019.2PSD interface to a non-multiplexed 8-bit bus . . . . . . . . . . . . . . . . . . . . . . 7119.3Data Byte Enable reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7119.4MCU bus interface examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7219.580C196 and 80C186 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7319.6MC683xx and MC68HC16 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7419.780C51XA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7519.8H8/300 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7619.9MMC2001 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7719.10C16x family . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7720I/O ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8020.1General port architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8020.2Port operating modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8120.3MCU I/O mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8220.4PLD I/O mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8220.5Address Out mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8220.6Address In mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8420.7Data Port mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8420.8Peripheral I/O mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8420.9JTAG in-system programming (ISP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8520.10MCU Reset mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8520.11Port Configuration registers (PCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8620.12Control register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8620.13Direction register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8620.14Port Data registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8820.15Data In . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 885/129Contents PSD4235G26/12920.16Data Out register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88 20.17Output macrocells (OMC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88 20.18Mask macrocell register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88 20.19Input macrocells (IMC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88 20.20Enable Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89 20.21Ports A, B and C - functionality and structure . . . . . . . . . . . . . . . . . . . . . 89 20.22Port D - functionality and structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90 20.23Port E - functionality and structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91 20.24Port F - functionality and structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92 20.25Port G - functionality and structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9221Power management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9421.1Automatic Power-down (APD) Unit and Power-down mode . . . . . . . . . . . 9521.2Power-down mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9521.3Other power saving options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9621.4PLD power management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9621.5PSD Chip Select input (CSI, PD2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9721.6Input clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9721.7Input control signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9822Power-on Reset, Warm Reset and Power-down . . . . . . . . . . . . . . . . . . 9922.1Power-on Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9922.2Warm Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9922.3I/O pin, register and PLD status at Reset . . . . . . . . . . . . . . . . . . . . . . . . . 9922.4Reset of Flash Memory Erase and Program cycles . . . . . . . . . . . . . . . . . 9923Programming in-circuit using the JTAG serial interface . . . . . . . . . . 10123.1Standard JTAG signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10123.2JTAG extensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10223.3Security and Flash memory protection . . . . . . . . . . . . . . . . . . . . . . . . . . 102 24Initial delivery state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104 25Maximum rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105PSD4235G2Contents 26DC and AC parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106 27Package mechanical . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124 28Part numbering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126 Appendix A Pin assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127 29Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1287/129List of tables PSD4235G2 List of tablesTable 1.Pin names. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Table 2.Pin description (for the LQFP package) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Table 3.PLD I/O. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Table 4.JTAG signals on port E. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Table 5.Methods of programming different functional blocks of the PSD . . . . . . . . . . . . . . . . . . . . 23 Table 6.Register address offset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Table 7.Data-In registers - Ports A, B, C, D, E, F, G. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Table 8.Data-Out registers - Ports A, B, C, D, E, F, G . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Table 9.Direction registers - Ports A, B, C, D, E, F, G. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Table 10.Control registers - Ports E, F, G. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Table 11.Drive registers - Ports A, B, D, E, G. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Table 12.Drive registers - Ports C, F. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Table 13.Enable-Out registers - Ports A, B, C, F. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Table 14.Input macrocell registers - Port A, B, C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Table 15.Output macrocells A register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Table 16.Output macrocells B register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Table 17.Mask macrocells A register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Table 18.Mask macrocells B register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Table 19.Flash Memory Protection register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Table 20.Flash Boot Protection register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 Table 21.JTAG Enable register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 Table 22.Page register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 Table 23.PMMR0 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 Table 24.PMMR2 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 Table 25.VM register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 Table 26.Memory_ID0 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 Table 27.Memory_ID1 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 Table 28.Memory block size and organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 Table 29.Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37 Table 30.Status bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41 Table 31.Status bits for Motorola. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41 Table 32.DPLD and CPLD inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56 Table 33.Output macrocell Port and Data bit Assignments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63 Table 34.MCUs and their control signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69 Table 35.16-bit data bus with BHE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71 Table 36.16-bit data bus with WRH and WRL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72 Table 37.16-bit data bus with SIZ0, A0 (Motorola MCU). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72 Table 38.16-bit data bus with LDS, UDS (Motorola MCU). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72 Table 39.Port operating modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82 Table 40.Port operating mode settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83 Table 41.I/O port latched address output assignments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84 Table 42.Port Configuration registers (PCR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86 Table 43.Port Pin Direction Control, output Enable P.T. not defined. . . . . . . . . . . . . . . . . . . . . . . . . 87 Table 44.Port Pin Direction Control, output Enable P.T. defined. . . . . . . . . . . . . . . . . . . . . . . . . . . . 87 Table 45.Port direction assignment example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87 Table 46.Drive register pin assignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87 Table 47.Port Data registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88 Table 48.Effect of Power-down mode on ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95 8/129PSD4235G2List of tables Table 49.PSD timing and standby current during Power-down mode. . . . . . . . . . . . . . . . . . . . . . . . 96 Table 50.APD counter operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98 Table 51.Status During Power-On Reset, Warm Reset and Power-down mode. . . . . . . . . . . . . . . . 99 Table 52.JTAG port signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102 Table 53.Absolute maximum ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105 Table 54.Example of PSD typical power calculation at V CC = 5.0V (with Turbo mode on). . . . . . . 107 Table 55.Example of PSD typical power calculation at V CC = 5.0V (with Turbo mode off). . . . . . . 108 Table 56.Operating conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109 Table 57.AC signal letters for PLD timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109 Table 58.AC signal behavior symbols for PLD timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109 Table 59.AC measurement conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110 Table 60.Capacitance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110 Table 61.DC characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111 Table 62.CPLD Combinatorial timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112 Table 63.CPLD macrocell Synchronous clock mode timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113 Table 64.CPLD macrocell Asynchronous clock mode timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114 Table 65.Input macrocell timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115 Table 66.Program, WRITE and Erase times. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116 Table 67.READ timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117 Table 68.WRITE timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119 Table 69.Port F Peripheral Data Mode Read timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121 Table 70.Port F Peripheral Data Mode Write timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121 Table 71.Reset (RESET) timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121 Table 72.Power-down timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122 Table 73.ISC timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123 Table 74.LQFP80 - 80-lead plastic thin, quad, flat package mechanical data. . . . . . . . . . . . . . . . . 124 Table 75.Ordering information scheme. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126 Table 76.PSD4235G2 LQFP80. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127 Table 77.Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1289/129。

DVHV2812SFR-XXX资料

DVHV2800S SeriesHIGH RELIABILITY HYBRIDDC-DC CONVERTERSDESCRIPTIONThe DVHV series of high reliability DC-DCconverters is operable over the full military (-55 °C to +125 °C) temperature range with no power derating. Unique to the DVHV series is a magnetic feedback circuit that is radiation immune. Operating at a nominal fixed frequency of 475 kHz, these regulated, isolated units utilize well controlled undervoltage lockout circuitry to eliminate slow start-up problems. The output voltage is trimmable up to +10% or down –20%.These converters are designed and manufactured ina facility qualified to ISO9001 and certified to MIL-PRF-38534 and MIL-STD-883.This product may incorporate one or more of thefollowing U.S. patents:5,784,2665,790,3895,963,4385,999,4336,005,7806,084,7926,118,673 FEATURES• High Reliability • Very Low Output Noise • Output Voltage Trim Up +10% or Down –20% • Wide Input Voltage Range: 15 to 50 Volts per MIL-STD-704 • Up to 15 Watts Output Power • Radiation Immune Magnetic Feedback Circuit • NO Use of Optoisolators • Undervoltage Lockout • Indefinite Short Circuit Protection• Current Limit Protection• Industry Standard Pinout• High Input Transient Voltage: 80 Volts for 1 sec per MIL-STD-704A • Radiation Hardened Version Available • Precision Seam Seal or Solder Seal Hermetic Package • Custom Versions Available • Additional Environmental Screening Available • Meets MIL-STD-461C and MIL-STD-461D EMC Requirements When Used With a DVMC28 EMI Filter • Flanged and Non-flanged Versions Available. •MIL-PRF-38534 Element Evaluated ComponentsFigure 1 – DVHV2800S / DVHV2800SF DC-DC Converter(Not To Scale )DVHV2800S SeriesSPECIFICATIONS (T CASE = -55°C to +125°C, V IN = +28V ± 5%, Full Load, Unless Otherwise Specified)ABSOLUTE MAXIMUM RATINGSInput Voltage (Continuous)50 V DC Junction Temperature Rise to Case +15°CInput Voltage (Transient, 1 second) 80 Volts Storage Temperature-65°C to +150°C Output Power 115 Watts Lead Solder Temperature (10 seconds) 270°CPower Dissipation (Full Load, T CASE = +125°C)11 WattsWeight (Maximum) (Un-Flanged / Flanged)(49 / 52) GramsDVHV283R3S DVHV2805SParameter Conditions Min Typ Max Min Typ Max UnitsSTATICContinuous 15 28 50 15 28 50 V INPUTVoltage4Transient, 1 sec - - 80 - - 80 VInhibited - - 6 - - 6 mA CurrentNo Load - - 90 - - 90 mARipple Current Full Load, 20Hz to 10MHz--50--50mA p-pInhibit Pin Input40 - 1.5 0 - 1.5 V Inhibit Pin Open Circuit Voltage 49.0 11.0 13.0 9.0 11.0 13.0 V UVLO Turn On 12.0-14.812.0-14.8VUVLO Turn Off 411.0 - 14.5 11.0 - 14.5 V V OUT T CASE =25°C 3.26 3.30 3.34 4.95 5.00 5.05 VOUTPUTVoltageV OUT T CASE =-55°C to +125°C 3.25 3.30 3.35 4.925 5.00 5.075 VPower3 0 - 10 0 - 15 W Current 3V OUT0 - 3.03 0 - 3.0 ARipple Voltage V OUT Full Load, 20Hz to 10MHz - - 30 - - 30 mV p-p Line Regulation V OUT V IN = 15V to 50V - - 20 - - 20 mV Load Regulation V OUTNo Load to Full Load --50--50mVEFFICIENCY68 - - 73 - - % Overload 4- - 11 - - 11 W LOAD FAULT POWER DISSIPATION Short Circuit- - 11 - - 11 W CAPACITIVE LOAD4- - 1000 - - 1000 µF SWITCHING FREQUENCY400 475 550 400 475 550 kHzSYNC FREQUENCY RANGEV H – V L = 5VDuty Cycle = 20% - 80% 500 - 600 500 - 600 kHzISOLATION 500 V DC 100 - - 100 - - M Ω MTBF (MIL-HDBK-217F)AIF @ T C =55°C- 413 - - 413 - kHrsDYNAMICLoad Step Output Transient V OUT - - 200 - - 300 mV PK Load Step Recovery 2Half Load to Full Load - - 550 - - 500 µSec Line Step Output Transient 4V OUT - 300 600 - 300 600 mV PK Line Step Recovery 2, 4V IN = 16V to 40V - 300 500 - 300 500 µSec Turn On Delay V OUT- - 20 - - 20 mSecTurn On OvershootV IN = 0V to 28V- - 15 - - 25 mV PKNotes: 1. Dependant on output voltage.2. Time for output voltage to settle within 1% of its nominal value.3. Derate linearly to 0 at 135°C.4. Verified by qualification testing.DVHV2800S SeriesSPECIFICATIONS (T CASE = -55°C to +125°C, V IN = +28V ± 5%, Full Load, Unless Otherwise Specified)ABSOLUTE MAXIMUM RATINGSInput Voltage (Continuous)50 V DC Junction Temperature Rise to Case +15°CInput Voltage (Transient, 1 second) 80 Volts Storage Temperature-65°C to +150°C Output Power 115 Watts Lead Solder Temperature (10 seconds) 270°CPower Dissipation (Full Load, T CASE = +125°C)11 WattsWeight (Maximum) (Un-Flanged / Flanged)(49 / 52) GramsDVHV2812S DVHV2815SParameter Conditions Min Typ Max Min Typ MaxUnitsSTATICContinuous 15 28 50 15 28 50 V INPUTVoltage4Transient, 1 sec - - 80 - - 80 VInhibited - - 6 - - 6 mA CurrentNo Load - - 90 - - 90 mARipple Current Full Load, 20Hz to 10MHz--50--50mA p-pInhibit Pin Input40 - 1.5 0 - 1.5 V Inhibit Pin Open Circuit Voltage 49.0 11.0 13.0 9.0 11.0 13.0 V UVLO Turn On 12.0-14.812.0-14.8VUVLO Turn Off 411.0 - 14.5 11.0 - 14.5 V V OUT T CASE =25°C 11.88 12.0 12.12 14.85 15.0 15.15 V OUTPUTVoltageV OUT T CASE = -55°C to +125°C 11.8212.012.1814.77515.015.225VPower3 0 - 15 0 - 15 W Current 3V OUT0 - 1.25 0 - 1.0 ARipple Voltage V OUT Full Load, 20Hz to 10MHz - - 40 - - 40 mV p-p Line Regulation V OUT V IN = 15V to 50V - - 20 - - 20 mV Load Regulation V OUTNo Load to Full Load --50--50mVEFFICIENCY77 - - 77 - - % Overload4- - 11 - - 11 W LOAD FAULT POWER DISSIPATION Short Circuit - - 11 - - 11 W CAPACITIVE LOAD4- - 500 - - 500 µF SWITCHING FREQUENCY400 475 550 400 475 550 kHzSYNC FREQUENCY RANGEV H – V L = 5VDuty Cycle = 20% - 80% 500 - 600 500 - 600 KHzISOLATION 500 V DC 100 - - 100 - - M Ω MTBF (MIL-HDBK-217F)AIF @ T C =55°C- 413 - - 413 - kHrsDYNAMICLoad Step Output Transient V OUT - - 300 - - 350 mV PK Load Step Recovery 2Half Load to Full Load - - 550 - - 450 µSec Line Step Output Transient 4V OUT - 500 900 - 500 900 mV PK Line Step Recovery 2, 4V IN = 16V to 40V - 300 500 - 300 500 µSec Turn On Delay V OUT- - 20 - - 20 mSecTurn On OvershootV IN = 0V to 28V- - 50 - - 50 mV PKNotes: 1. Dependant on output voltage.2. Time for output voltage to settle within 1% of its nominal value.3. Derate linearly to 0 at 135°C.4. Verified by qualification testing.DVHV2800S SeriesSPECIFICATIONS (T CASE = -55°C to +125°C, V IN = +28V ± 5%, Full Load, Unless Otherwise Specified)ABSOLUTE MAXIMUM RATINGSInput Voltage (Continuous)50 V DC Junction Temperature Rise to Case +15°CInput Voltage (Transient, 1 second) 80 Volts Storage Temperature-65°C to +150°C Output Power 115 Watts Lead Solder Temperature (10 seconds) 270°CPower Dissipation (Full Load, T CASE = +125°C)11 WattsWeight (Maximum) (Un-Flanged / Flanged)(49 / 52) GramsDVHV285R2SParameter Conditions Min Typ MaxUnitsSTATICContinuous 15 28 50 V INPUTVoltage4Transient, 1 sec - - 80 V Inhibited - - 6 mACurrentNo Load- - 90 mA Ripple Current Full Load, 20Hz to 10MHz--50mA p-pInhibit Pin Input40 - 1.5 V Inhibit Pin Open Circuit Voltage 49.0 11.0 13.0 V UVLO Turn On12.0 - 14.8 V UVLO Turn Off 411.0 - 14.5 VV OUT T CASE = 25°C5.148 5.20 5.252 V OUTPUTVoltageV OUT T CASE = -55°C to +125°C5.1225.205.278VPower3 0 - 15 W Current3V OUT 0 - 3.0 A Ripple Voltage V OUT Full Load, 20Hz to 10MHz - - 30 mV p-p Line Regulation V OUT V IN = 15V to 50V - - 20 mV Load RegulationV OUTNo Load to Full Load --50mVEFFICIENCY 73 - - % Overload4- - 11 W LOAD FAULT POWER DISSIPATION Short Circuit --11WCAPACITIVE LOAD4- - 1000 µFSWITCHING FREQUENCY400 475 550 kHz SYNC FREQUENCY RANGEV H – V L = 5VDuty Cycle = 20% - 80% 500 - 600 kHzISOLATION 500 V DC 100 - - M Ω MTBF (MIL-HDBK-217F)AIF @ T C = 55°C-413-kHrsDYNAMICLoad Step Output Transient V OUT - - 300 mV PK Load Step Recovery 2Half Load to Full Load - - 500 µSec Line Step Output Transient 4V OUT - 300 600 mV PK Line Step Recovery 2, 4V IN = 16V to 40V - 300 500 µSecTurn On Delay V OUT- - 20 mSec Turn On OvershootV IN = 0V to 28V- - 25 mV PKNotes: 1. Dependant on output voltage.2. Time for output voltage to settle within 1% of its nominal value.3. Derate linearly to 0 at 135°C.4. Verified by qualification testing.DVHV2800S SeriesBLOCK DIAGRAMUNDER VOLTAGE SHUTDOWNPRIMARY HOUSEKEEPINGSUPPLYPWM CONTROLVOLTAGE AND CURRENT AMPLIFIERSSECONDARY HOUSEKEEPINGSUPPLYPIN 128V INPIN 10IN COML1C1Q1Rs1T1D1C2Rs2+V OUTPIN 5PIN 4OUT COM INHPIN 2FEEDBACKMAGNETIC SYNCPIN 9TRIM PIN 3Figure 2CONNECTION DIAGRAM10IN COM 2INH128V IN5+V OUT4OUT COMLOAD+-28 VdcSYNC9Figure 3DVHV2800S SeriesINHIBIT DRIVE CONNECTION DIAGRAMSFigure 4 – Internal Inhibit Circuit and Recommended DriveFigure 5 – Isolated Inhibit Drive(Shown with optional capacitor for turn-on delay)(Shown with optional capacitor for turn-on delay)EMI FILTER HOOKUP DIAGRAM10IN COM 2INH128V IN5+V OUT4OUT COMLOAD+-28 Vdc228V OUT4OUT COM 128V IN5IN COMCASE6, 7, 8SYNC93DVMC28 EMI FILTERDVHV2800S DC-DC CONVERTERFigure 6 – Converter with EMI FilterDVHV2800S SeriesPARALLEL CONNECTION DIAGRAM10IN COM 2INH128V IN5+V OUT4OUT COMLOAD+-28 Vdc228V OUT4OUT COM128V IN5IN COMCASESYNC936, 7, 86, 7, 8DVMC28 EMI FILTERDVHV2800S DC-DC CONVERTERCASE10IN COM 2INH128V IN 5+V OUT4OUT COMSYNC9DVHV2800S DC-DC CONVERTERCASEFigure 7DVHV2800S Series OUTPUT VOLTAGE TRIMThe output voltage can be trimmed down byconnecting a resistor between the TRIM pin(PIN 3) and the +V OUT pin (PIN 5), or canbe trimmed up by connecting a resistorbetween the TRIM pin (PIN 3) and the OUTCOM pin (PIN 4). The maximum trim rangeis +10% up and –20% down. Theappropriate resistor values versus theoutput voltage are given in the trim tablebelow.Figure 8 – Output Voltage TrimDVHV283R3S DVHV2805S DVHV285R2S DVHV2812S DVHV2815S+V OUT (V) R TRIM (Ω) +V OUT (V) R TRIM (Ω) +V OUT (V) R TRIM (Ω) +V OUT (V) R TRIM (Ω) +V OUT (V) R TRIM (Ω)3.75 25.4k 5.5 19k 5.7 23k 13.2 5.93k 16.75 03.70 32.5k 5.4 31.5k 5.6 36.5k 13.0 10.1k 16.50 1.67k3.65 41.8k 5.3 52.3k 5.5 59k 12.8 16.5k 16.25 5k3.60 54.2k5.2 94k 5.4 104k 12.6 27.1k 16.00 10k3.55 71.6k 5.1 219k 5.3 239k 12.4 48.4k 15.75 18.3k3.50 98.2k 5.0 - 5.2 - 12.2113.7k15.5035k3.45 143.2k4.9 209k5.1 249.8k 12.0 - 15.25 85k3.40 236k4.8 84k5.0 104k 11.8 437k 15.00 -3.35 543k4.7 42.3k 4.9 55.4k 11.6 209k 14.75 475k3.30 -4.6 21.5k 4.8 31.1k 11.4 132k 14.50 225k3.25 102k4.5 9k 4.7 16.5k 11.2 93k 14.25 142k3.20 34.8k 4.4 0 4.6 6.8k 11.0 69.5k 14.00 100k3.1510.5k 10.8 53.8k 13.75 75k3.100 10.642.6k 13.50 58.3k10.434.2k13.2546.4k10.227.6k13.0037.5k10.022.4k12.7530.6k9.818.1k12.5025k9.614.5k12.2520.5k9.411.5k12.0016.7k9.28.88k9.06.63kDVHV2800S SeriesEFFICIENCY PERFORMANCE CURVES (T CASE = 25°C, Full Load, Unless Otherwise Specified)V IN = 16VV IN = 28VV IN = 40V45505560657075345678910Output Power (W)E f f i c i e n c y (%)505560657075803691215Output P ow er (W)E f f i c i e n c y (%)Figure 9 – DVHV283R3S Figure 10 – DVHV2805S / DVHV285R2S Efficiency (%) vs. Output Power (W)Efficiency (%) vs. Output Power (W)6065707580853691215Output P ow er (W)E f f i c i e n c y (%)6065707580853691215Output Power (W)E f f i c i e n c y (%)Figure 11 – DVHV2812S Figure 12 – DVHV2815S Efficiency (%) vs. Output Power (W)Efficiency (%) vs. Output Power (W)DVHV2800S Series EMI PERFORMANCE CURVES(T CASE = 25°C, V IN = +28V ± 5%, Full Load, Unless Otherwise Specified)Figure 13 – DVHV2800S without EMI FilterFigure 14 – DVHV2800S with EMI FilterDVHV2800S Series PACKAGE SPECIFICATIONS (NON-FLANGED, SOLDER SEAL)TOP VIEW SIDE VIEWPIN FUNCTIONIN1 28V2 INHIBIT3 TRIMCOM4 OUTOUT5 +V6 CASE7 CASE8 CASE9 SYNCCOM10 INBOTTOM VIEWFigure 15 – Non-Flanged, Solder Seal Tin Plated Package and Pinout (Not Used for /HB or Higher Screened Products)(Dimensional Limits are ±0.005” Unless Otherwise Stated)DVHV2800S Series PACKAGE SPECIFICATIONS (NON-FLANGED, SEAM SEAL)TOP VIEW SIDE VIEWPIN FUNCTIONIN1 28V2 INHIBIT3 TRIMCOM4 OUTOUT5 +V6 CASE7 CASE8 CASE9 SYNCCOM10 INBOTTOM VIEWFigure 16 – Non-Flanged, Seam Seal Package and Pinout(Dimensional Limits are ±0.005” Unless Otherwise Stated)DVHV2800S Series PACKAGE SPECIFICATIONS (FLANGED, SOLDER SEAL)TOP VIEW SIDE VIEWPIN FUNCTIONIN1 28V2 INHIBIT3 TRIMCOM4 OUTOUT5 +V6 CASE7 CASE8 CASE9 SYNCCOM10 INBOTTOM VIEWFigure 17 – Flanged, Solder Seal Tin Plated Package and Pinout (Not Used for /HB or Higher Screened Products)(Dimensional Limits are ±0.005” Unless Otherwise Stated)DVHV2800S Series PACKAGE SPECIFICATIONS (FLANGED, SEAM SEAL)TOP VIEW SIDE VIEWPIN FUNCTIONIN1 28V2 INHIBIT3 TRIMCOM4 OUTOUT5 +V6 CASE7 CASE8 CASE9 SYNCCOM10 INBOTTOM VIEWFigure 18 – Flanged, Seam Seal Package and Pinout(Dimensional Limits are ±0.005” Unless Otherwise Stated)DVHV2800S Series PACKAGE PIN DESCRIPTIONPin Function Description1 28V IN Positive Input Voltage Connection2 INHIBIT Logic Low = Disabled Output. Connecting the inhibit pin to input common causes converter shutdown.Logic High = Enabled Output. Unconnected or open collector TTL.3 TRIM Trim Output Voltage to +10%, -20% of Nominal Value4 OUTCOM Output Common Connection5 +V OUT Positive Output Voltage Connection6 CASE CaseConnection7 CASE CaseConnection8 CASE CaseConnection9 SYNC SynchronizationSignal10 IN COM Input Common ConnectionDVHV2800S SeriesENVIRONMENTAL SCREENING (Per MIL-STD-883 as referenced to MIL-PRF-38534, Class H)Notes: 1. 100% R&R testing at –55°C, +25°C, and +125°C with all test data included in product shipment. 2. PIND test Certificate of Compliance included in product shipment.3. Radiographic test Certificate of Compliance and film(s) included in product shipment.Screening MIL-STD-883Standard(No Suffix)Extended /ES HB /HBClass H/HClass K /KNon-Destructive Bond Pull Method 2023 • • • • • Internal Visual Method 2017, 2032 Internal Procedure• • • • • Temperature Cycling Method 1010, Condition C Method 1010, -55°C to 125°C • • • • Constant Acceleration Method 2001, 3000g, Y1 Direction Method 2001, 500g, Y1 Direction • • • • PIND Method 2020, Condition A 2•Pre Burn-In Electrical100% at 25°C • Burn-InMethod 1015, 320 hours at +125°C Method 1015, 160 hours at +125°C 96 hours at +125°C 24 hours at +125°C • • • • • Final ElectricalMIL-PRF-38534, Group A 1 100% at 25°C• • • • • HermeticityMethod 1014, Fine Leak, Condition A Method 1014, Gross Leak, Condition CDip (1 x 10-3)• • • • • • • • • Radiography Method 20123 • External VisualMethod 2009•••••DVHV2800S Series ORDERING INFORMATIONDVHV 28 05 S F R /HB - XXX1 2 3 4 5 6 7 8(1) (2) (3) (4)Product Series Nominal InputVoltageOutput Voltage Number of OutputsDVHV 28 28 Volts 3R3055R21215 3.3 Volts5 Volts5.2 Volts12 Volts15 VoltsS Single(5) (6) (7) (8)Package Option Rad-Hard Option2 Screening Code1,3 Additional ScreeningCodeNone F Non-FlangedFlangedNoneRStandard100 kRadNone/ES/HB/H/KStandardExtendedHBClass HClass KContact SalesNotes: 1. Contact the VPT Inc. Sales Department for availability of Class H (/H) or Class K (/K) qualified products.2. VPT Inc. is not currently qualified to a DSCC certified radiation hardness assurance program.3. VPT Inc. reserves the right to ship higher screened or SMD products to meet lower screened orders at oursole discretion unless specifically forbidden by customer contract.Please contact your sales representative or the VPT Inc. Sales Department for more information concerning additional environmental screening and testing, different input voltage, output voltage, power requirement, source inspection, and/or special element evaluation for space or other higher quality applications.DVHV2800S Series SMD (STANDARD MICROCIRCUIT DRAWING) NUMBERSStandard Microcircuit Drawing (SMD)DVHV2800S Series Similar Part Number*T.B.D.DVHV283R3S/H DVHV283R3SF/H*T.B.D.DVHV2805S/H DVHV2805SF/H*T.B.D.DVHV285R2S/H DVHV285R2SF/H*T.B.D.DVHV2812S/H DVHV2812SF/H*T.B.D.DVHV2815S/H DVHV2815SF/HDo not use the DVHV2800S Series similar part number for SMD product acquisition. It is listed forreference only. For exact specifications for the SMD product, refer to the SMD drawing. SMD’s can be downloaded from the DSCC website at /programs/smcr/. The SMD numberlisted above is for MIL-PRF-38534 Class H screening, standard gold plated lead finish, and no RHA(Radiation Hardness Assurance) level. Please reference the SMD for other screening levels, leadfinishes, and radiation levels.CONTACT INFORMATIONTo request a quotation or place orders please contact your sales representative or the VPT Inc. Sales Department at:Phone: (425)353-3010Fax: (425) 353-4030E-mail: vptsales@All information contained in this datasheet is believed to be accurate, however, no responsibility is assumed for possible errors or omissions. The products or specifications contained herein are subject to change without notice.。

MAP55-4000中文资料

Features•RoHS lead-solder-exempt compliant•Wide Range Input for 110/220 VAC Applications •Meets EN55022, Conducted Class B Limits •Compact Footprint: 6.00" x 3.27" x 1.60"(152.4mm x 83.1mm x 40.6mm)•Greater than 225,000 Hours MTBF •Metric and SAE Mounting InsertsMultiple-Output Model Selection 55W Continuous Output PowerMODELOUTPUT ADJUSTMENT OUTPUT PEAK OUTPUT LINE LOAD RIPPLE & NOISE INITIAL SETTING VOLTAGERANGECURRENTCURRENT (NOTE 1)REGULATIONREGULATION%p-p (NOTE 2)ACCURACY+5V 4.7V to 5.6V 6A 8A 0.2%2%1% 5.0V to 5.2V MAP55-4000+12V Fixed 3A 5A 0.2%2%1%11.6V to 12.4V -5V Fixed 0.5A 1A (Note 3)0.5%2%1%-4.8V to -5.2V -12V Fixed 0.5A 1A (Note 3)0.5%2%1%-11.6V to -12.4V +5V 4.7V to 5.6V 6A 8A 0.2%2%1% 5.0V to 5.2V MAP55-4001+24V Fixed 1.5A 2.5A 0.2%2%1%23.0V to 24.9V -12V Fixed 0.5A 1A (Note 3)0.5%2%1%-11.6V to -12.4V +12V Fixed 0.5A 1A (Note 3)0.5%2%1%11.6V to 12.4V +5V 4.7V to 5.6V 6A 8A 0.2%2%1% 5.0V to 5.2V MAP55-4002+12V Fixed 3A 5A 0.2%2%1%11.6V to 12.4V -12V Fixed 0.5A 1A (Note 3)0.5%2%1%-11.6V to -12.4V +12V Fixed 0.5A 1A (Note 3)0.5%2%1%11.6V to 12.4V +5V 4.7V to 5.6V 6A 8A 0.2%2%1% 5.0V to 5.2V MAP55-4003+15V Fixed 2.5A 3.5A 0.2%2%1%14.6V to 15.4V -5V Fixed 0.5A 1A (Note 3)0.5%2%1%-4.8V to -5.2V -15V Fixed 0.5A 1A (Note 3)0.5%2%1%-14.4V to -15.6V+5V 4.7V to 5.6V 6A 8A 0.2%2%1% 5.0V to 5.2V MAP55-4004+24V Fixed 1.5A 2.5A 0.2%2%1%23.0V to 24.9V -15V Fixed0.5A 1A (Note 3)0.5%2%1%-14.5V to -15.5V +15V Fixed 0.5A 1A (Note 3)0.5%2%1%14.5V to 15.5VNOTES:1) Peak loads up to 65 watts for 60 seconds or less are acceptable, (10% duty cycle max.). Peak power must not exceed 65 watts.2) Maximum peak to peak noise expressed as a percentage of output voltage, 20 MHz bandwidth.3) Maximum load on V3 or V4 could be 1 amp continuous if output V4 or V3 is unloaded.DescriptionPower-One's MAP55 Series of power supplies provides reliable, tightly-regulated DC power for commercial and industrial systems. Wide-range AC input and full international safety, EMI, and ESD compliance ensure worldwide acceptance. All units bear the CE Mark.The MAP55 utilizes a thermally efficient U-channel chassis design, which allows full power operation in convection-cooled applications. Other mechanical design innovations include metric and SAE mounting inserts on each mounting surface to provide integration flexibility. Dual-mode connectors provide traditional terminal block connections or popular single row Molex connector mating.Single-output models feature wide-range output adjustability to meet a wide variety of standard and user-specific output voltage requirements.NUCLEAR AND MEDICAL APPLICATIONS - Power-One products are not designed, intended for use in, or authorized for use as critical components in life support systems, equipment used in hazardous environments, or nuclear control systems without the express written consent of the respective divisional president of Power-One, Inc.TECHNICAL REVISIONS - The appearance of products, including safety agency certifications pictured on labels, may change depending on the date manufactured. Specifications are subject to change without notice.Environmental SpecificationsPARAMETER CONDITIONS/DESCRIPTION MIN NOM MAX UNITS Altitude Operating.10k Feet Non-operating.40kOperating Temperature Derate linearly above 50°C by 2.5% per °C At 100% load:050°C to a maximum temperature of 70°C.At 50% load:070°C Storage Temperature-4085°C Temperature Coefficient 0°C to 70°C (after 15 minute warm-up).±0.02±0.03%/°C Relative Humidity Non-condensing.595%RH Shock Operating, peak acceleration.20G Vibration Random vibration, 10 Hz to 2 kHz, 3 axis.6G RMSOptionsDESCRIPTION NOTES DIMENSIONSCover Add ‘C’ suffix to model number or order part number 412-59584-G separately. 6.00" x 3.27" x 1.85"For convection cooled applications, derate output power to 45 watts on multiple (152.4mm x 83.1mm x 47.0mm)output units, 50 watts on MAP55-1012 and MAP55-1024,and 40 watts on MAP40-1005.OVERALL SIZE: 6.00" x 3.27" x 1.60" (152.4mm x 83.1mm x 40.6mm)WEIGHT: 1.1 LBS (0.55 kg)INPUT& OUTPUT CONNECTIONS: 6-32 SCREW WIRE CLAMPS ON 0.312" (7.9mm) CENTERS, 0.045" (1.1mm)SQUARE PINS ON 0.156" (3.4mm) CENTERS, MATES WITH MOLEX SERIES2139, 6442, OR 41695CHASSIS: 0.090" (2.3mm) ALUMINUM ALLOY, WITH CLEAR FINISH。

新世纪版国家大地图集

知识库

模型库

预案库

面向国家安全的信息服务 国防安全、重大工程、应 急防控等 面向社会发展的信息服务 “十二金”工程、数字城 市、区域可持续发展…… 面向科学研究的信息服务 区域模拟、全球变化、预 测预警…… 面向公众和企业信息服务 移动位置服务、汽车导航、 物流配送……

自 然 灾 害

基础 服务 技术

在新版国家地图集中除了一系列详细的解析型地图、组合型评价地图外,迫切 需要放置大量的预测预报地图和规划决策地图;就专业而言,各类资源评价地图、 环境动态监测地图、生态退化与恢复地图、防灾减灾战略规划地图、城市与区域综 合应急反应地图、区域可持续发展地图、全球变化的区域响应地图等都是新世纪版 国家地图集不可缺少的内容,也是其科学内容体系的新亮点,实现从数据中挖掘信 息,从信息中发现知识,从知识中提炼决策方案,集成多模型和群决策方案建立地 学信息图谱精品成果等一系列升华和飞跃。

功能定位知识的传播功能科学参考功能知识的传播功能科学参考功能面向决策支持的专业模型应用服务基于多媒体的科学可视化服务智能搜索和空间定位服务地图导航服务多种个性化的信息定制发布交互对弃式信息咨询和沟通服务实现科学理念技术体系服务水平三位一体的提升和创表现形式定位网络版电子光盘版印刷版可采用四开和大八开两种开本幅面既不失国家大地图集的厚重和气势又便于携带与使用拟采用高密度和大容量的dvd光盘以适应海量数据的存储将建立长期运行的中华人民共和国国家大地图集新世纪网站编辑ppt地图制印自动化编辑ppt遥感信息机理多尺度多维动态地理空间综合数据库海量空间数据处理增值服务技术基础服务技术决策服务技术计算服务技术第三代网络与空间信息网格计算技术面向国家安全的信息服务国防安全重大工程应移动位置服务汽车导航面向公众和企业信息服务移动位置服务汽车导航物流配送

FUJITSU SPARC ENTERPRISE M4000 服务器数据手册说明书

数据手册FUJITSU SPARC ENTERPRISE M4000服务器经济高效的UNIX®服务器集聚大型机优势,为您提供虚拟化、集成和自动化功能。

FUJITSU SPARC ENTERPRISE服务器永远是您的最佳选择FUJITSU SPARC Enterprise服务器基于可靠的SPARC架构,运行世界领先的Oracle Solaris 10操作系统,可通过虚拟化提高系统利用率和性能,是需要高可扩展性、高可靠性服务器的客户的理想选择。

结合Fujitsu(富士通)在关键业务计算技术和高性能处理器设计方面的丰富经验以及Oracle在开放式、可扩展、基于分区的网络计算方面的资深优势,此款服务器带来了能满足所有任务需求的整体灵活性。

秉承SPARC的优良传统FUJITSU SPARC Enterprise M4000服务器是一款中端系统,与其较大型的企业级兄弟产品一样,拥有强大的RAS功能。

不仅如此,其紧凑的机架安装设计还大大降低了用户的拥有成本。

该服务器具备不间断自我修复机制和坚如磐石的可靠性,能满足部门数据库和ERP应用程序的运行需求,还可跨两个物理分区集群设置这些应用程序,以确保高可靠性。

全面的二进制兼容性充分地保护您的应用程序投资,而且Oracle Solaris 容器也为您实现了进一步的无成本资源细分。

对于大多数业务应用程序而言,FUJITSU SPARC Enterprise M4000服务器的性能在同类产品中遥遥领先。

性能和优势灵活的投资保护可以在服务器中,甚至是分区中混用SPARC64TM VII/VII+双核处理器与SPARC64™VII四核处理器。

通过动态重新配置和可选的FUJITSU PRIMECLUSTER分区间集群,最多可支持2个物理分区和数以千计的Oracle Solaris容器。

满足用户的投资保护需求,更小的风险,更低的拥有成本。

在CPU路数、空间需求、能耗需求不变的情况下,性能可扩展近两倍。

40英尺国际标准通用集装箱说明书

40英尺国际标准通用集装箱技术规范(2008-07)深圳南方中集集装箱制造有限公司二00八年七月本说明书概括了设计、结构、材料、试验、质检和样箱制造。

按照I S O 标准1C C型钢质干货集装箱的要求进行制造。

=====================1.总述.................................................. .. (2)2.批准和证书........................................................ .. (2)3.装卸.................................................. .. (2)4.运输.................................................. .. (3)5.尺寸、技术参数和重量....................................................... .. (3)6.结构.................................................. .. (4)7.表面保护...................................................... . (7)8.标志.................................................. .. (8)9.试验和检查....................................................... (9)10.文件提交..................................................... (10)11.质量保证期........................................................ .. (10)12.材料表.................................................... (10)1.总述1.1使用环境本集装箱按照在世界范围内作海上(甲板上或甲板下)和陆上(公路或铁路)运输平常货物的应用要求来进行设计和制造。

AD9235中文资料

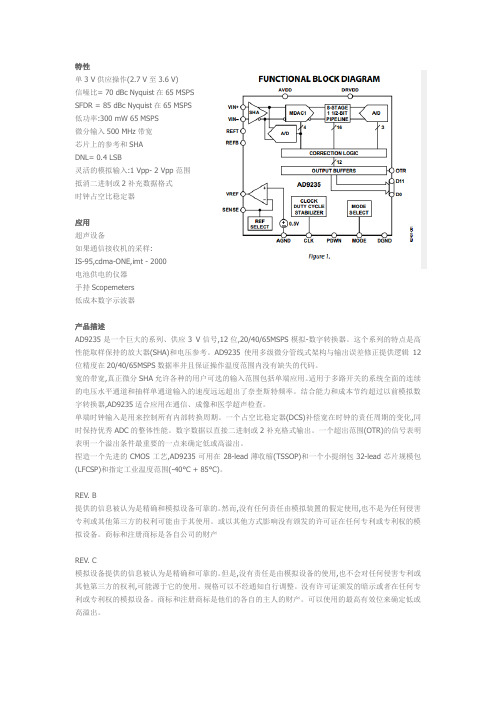

特性单3 V供应操作(2.7 V至3.6 V)信噪比= 70 dBc Nyquist在65MSPSSFDR = 85 dBc Nyquist在65MSPS低功率:300 mW 65MSPS微分输入500 MHz带宽芯片上的参考和SHADNL= 0.4 LSB灵活的模拟输入:1 Vpp- 2 Vpp范围抵消二进制或2补充数据格式时钟占空比稳定器应用超声设备如果通信接收机的采样:IS-95,cdma-ONE,imt - 2000电池供电的仪器手持Scopemeters低成本数字示波器产品描述AD9235是一个巨大的系列、供应3 V信号,12位,20/40/65MSPS模拟-数字转换器。

这个系列的特点是高性能取样保持的放大器(SHA)和电压参考。

AD9235使用多级微分管线式架构与输出误差修正提供逻辑12位精度在20/40/65MSPS数据率并且保证操作温度范围内没有缺失的代码。

宽的带宽,真正微分SHA允许各种的用户可选的输入范围包括单端应用。

适用于多路开关的系统全面的连续的电压水平通道和抽样单通道输入的速度远远超出了奈奎斯特频率。

结合能力和成本节约超过以前模拟数字转换器,AD9235适合应用在通信、成像和医学超声检查。

单端时钟输入是用来控制所有内部转换周期。

一个占空比稳定器(DCS)补偿宽在时钟的责任周期的变化,同时保持优秀ADC的整体性能。

数字数据以直接二进制或2补充格式输出。

一个超出范围(OTR)的信号表明表明一个溢出条件最重要的一点来确定低或高溢出。

捏造一个先进的CMOS工艺,AD9235可用在28-lead薄收缩(TSSOP)和一个小提纲包32-lead芯片规模包(LFCSP)和指定工业温度范围(-40°C + 85°C)。

REV. B提供的信息被认为是精确和模拟设备可靠的。

然而,没有任何责任由模拟装置的假定使用,也不是为任何侵害专利或其他第三方的权利可能由于其使用。

或以其他方式影响没有颁发的许可证在任何专利或专利权的模拟设备。

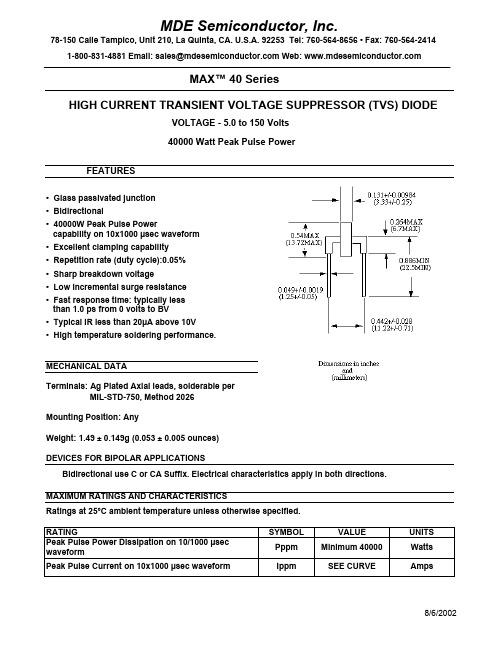

MAX40-5.0CA中文资料

8/6/2002

元器件交易网

MDE Semiconductor, Inc.

78-150 Calle Tampico, Unit 210, La Quinta, CA. U.S.A. Tel: 760-564-8656 • Fax 760-564-2414 1-800-831-4881 Email: sales@ Web:

50

10/1000µsec.Waveform as defined by R.E.A.

td

0 0 1.0 2.0

3.0

3.0

4.0

4.0

t - Time(ms)

Fig.3 - Pulse Waveform

10/21/2002

元器件交易网

MDE Semiconductor, Inc.

元器件交易网

MDE Semiconductor, Inc.

78-150 Calle Tampico, Unit 210, La Quinta, CA. U.S.A. 92253 Tel: 760-564-8656 • Fax: 760-564-2414 1-800-831-4881 Email: sales@ Web:

MAX™ 40 Series HIGH CURRENT TRANSIENT VOLTAGE SUPPRESSOR (TVS) DIODE

VOLTAGE - 5.0 to 150 Volts 40000 Watt Peak Pulse Power FEATURES

• Glass passivated junction • Bidirectional • 40000W Peak Pulse Power capability on 10x1000 µsec waveform • Excellent clamping capability • Repetition rate (duty cycle):0.05% • Sharp breakdown voltage • Low incremental surge resistance • Fast response time: typically less than 1.0 ps from 0 volts to BV • Typical IR less than 20µA above 10V • High temperature soldering performance.

Esri+CityEngine中文教程V1.0

1 基础内容 ..............................................................................................................1

1.1 基本操作.....................................................................................................1 1.2 教程与示例数据下载.................................................................................2 1.3 基本概念.....................................................................................................3

2.10 导出模型...................................................................................................17

CS5366-CQZ;CS5366-DQZ;CS5366-CQZR;CS5366-DQZR;中文规格书,Datasheet资料

114 dB, 192 kHz, 6-Channel A/D ConverterFeatures♦Advanced Multi-bit Delta-Sigma Architecture ♦24-Bit Conversion ♦114 dB Dynamic Range ♦-105 dB THD+N♦Supports Audio Sample Rates up to 216 kHz ♦Selectable Audio Interface Formats–Left-Justified, I²S, TDM–6-Channel TDM Interface Formats♦Low Latency Digital Filter♦Less than 535 mW Power Consumption ♦On-Chip Oscillator Driver♦Operation as System Clock Master or Slave ♦Auto-Detect Speed in Slave Mode ♦Differential Analog Architecture♦Separate 1.8 V to 5 V Logic Supplies forControl and Serial Ports♦High-Pass Filter for DC Offset Calibration ♦Overflow Detection♦Footprint Compatible with the 8-ChannelCS5368Additional Control Port Features♦Supports Standard I²C™ or SPI™ ControlInterface♦Individual Channel HPF Disable♦Overflow Detection for Individual Channels ♦Mute Control for Individual Channels♦Independent Power-Down Control per ChannelPairCS5366DescriptionThe CS5366 is a complete 6-channel analog-to-digital converter for digital audio systems. It performs sampling, an-alog-to-digital conversion, and anti-alias filtering, generating 24-bit values for all 6-channel inputs in serial form at sample rates up to 216 kHz per channel.The CS5366 uses a 5th-order, multi-bit delta sigma modulator followed by low latency digital filtering and decima-tion, which removes the need for an external anti-aliasing filter. The ADC uses a differential input architecture which provides excellent noise rejection.Dedicated level translators for the Serial Port and Control Port allow seamless interfacing between the CS5366 and other devices operating over a wide range of logic levels. In addition, an on-chip oscillator driver provides clocking flexibility and simplifies design.The CS5366 is the industry’s first audio A/D to support a high-speed TDM interface which provides a serial output of 6 channels of audio data with sample rates up to 216 kHz within a single data stream. It further reduces layout complexity and relieves input/output constraints in digital signal processors.The CS5366 is available in a 48-pin LQFP package in both Commercial (-40°C to 85°C) and Automotive grades (-40°C to +105°C). The CDB5366 Customer Demonstration board is also available for device evaluation and implementation suggestions. Please see “Ordering Information” on page 41 for complete ordering information.The CS5366 is ideal for high-end and pro-audio systems requiring unrivaled sound quality, transparent conversion, wide dynamic range and negligible distortion, such as A/V receivers, digital mixing consoles, multi-channel record-ers, outboard converters, digital effect processors, and automotive audio systems.TABLE OF CONTENTS1. PIN DESCRIPTION (6)2. TYPICAL CONNECTION DIAGRAM (9)3. CHARACTERISTICS AND SPECIFICATIONS (10)RECOMMENDED OPERATING CONDITIONS (10)ABSOLUTE RATINGS (10)SYSTEM CLOCKING (10)DC POWER (11)LOGIC LEVELS (11)PSRR, VQ AND FILT+ CHARACTERISTICS (11)ANALOG CHARACTERISTICS (COMMERCIAL) (12)ANALOG CHARACTERISTICS (AUTOMOTIVE) (13)DIGITAL FILTER CHARACTERISTICS (14)OVERFLOW TIMEOUT (14)SERIAL AUDIO INTERFACE - I²S/LJ TIMING (15)SERIAL AUDIO INTERFACE - TDM TIMING (16)SWITCHING SPECIFICATIONS - CONTROL PORT - I²C TIMING (17)SWITCHING SPECIFICATIONS - CONTROL PORT - SPI TIMING (18)4. APPLICATIONS (19)4.1 Power (19)4.2 Control Port Mode and Stand-Alone Operation (19)4.2.1 Stand-Alone Mode (19)4.2.2 Control Port Mode (19)4.3 Master Clock Source (20)4.3.1 On-Chip Crystal Oscillator Driver (20)4.3.2 Externally Generated Master Clock (20)4.4 Master and Slave Operation (21)4.4.1 Synchronization of Multiple Devices (21)4.5 Serial Audio Interface (SAI) Format (22)4.5.1 I²S and LJ Format (22)4.5.2 TDM Format (23)4.5.3 Configuring Serial Audio Interface Format (23)4.6 Speed Modes (23)4.6.1 Sample Rate Ranges (23)4.6.2 Using M1 and M0 to Set Sampling Parameters (23)4.6.3 Master Mode Clock Dividers (24)4.6.4 Slave Mode Audio Clocking With Auto-Detect (24)4.7 Master and Slave Clock Frequencies (25)4.8 Reset (27)4.8.1 Power-Down Mode (27)4.9 Overflow Detection (27)4.9.1 Overflow in Stand-Alone Mode (27)4.9.2 Overflow in Control Port Mode (27)4.10 Analog Connections (28)4.11 Optimizing Performance in TDM Mode (29)4.12 DC Offset Control (29)4.13 Control Port Operation (30)4.13.1 SPI Mode (30)4.13.2 I²C Mode (31)5. REGISTER MAP (32)5.1 Register Quick Reference (32)5.2 00h (REVI) Chip ID Code & Revision Register (32)5.3 01h (GCTL) Global Mode Control Register (32)5.4 02h (OVFL) Overflow Status Register (33)5.5 03h (OVFM) Overflow Mask Register (33)5.6 04h (HPF) High-Pass Filter Register (34)5.7 05h Reserved (34)5.8 06h (PDN) Power Down Register (34)5.9 07h Reserved (34)5.10 08h (MUTE) Mute Control Register (34)5.11 09h Reserved (35)5.12 0Ah (SDEN) SDOUT Enable Control Register (35)6. FILTER PLOTS (36)7. PARAMETER DEFINITIONS (39)8. PACKAGE DIMENSIONS (40)THERMAL CHARACTERISTICS (40)9. ORDERING INFORMATION (41)10. REVISION HISTORY (41)LIST OF FIGURESFigure 1. CS5368 Pinout (6)Figure 2. Typical Connection Diagram (9)Figure 3. I²S/LJ Timing (15)Figure 4. TDM Timing (16)Figure 5. I²C Timing (17)Figure 6. SPI Timing (18)Figure 7. Crystal Oscillator Topology (20)Figure 8. Master/Slave Clock Flow (21)Figure 9. Master and Slave Clocking for a Multi-Channel Application (21)Figure 10. I²S Format (22)Figure 11. LJ Format (22)Figure 12. TDM Format (23)Figure 13. Master Mode Clock Dividers (24)Figure 14. Slave Mode Auto-Detect Speed (24)Figure 15. Recommended Analog Input Buffer (28)Figure 16. SPI Format (30)Figure 17. I²C Write Format (31)Figure 18. I²C Read Format (31)Figure 19. SSM Passband (36)Figure 20. DSM Passband (36)Figure 21. QSM Passband (36)Figure 22. SSM Stopband (37)Figure 23. DSM Stopband (37)Figure 24. QSM Stopband (37)Figure 25. SSM -1 dB Cutoff (38)Figure 26. DSM -1 dB Cutoff (38)Figure 27. QSM -1 dB Cutoff (38)LIST OF TABLESTable 1. Power Supply Pin Definitions (19)Table 2. DIF1 and DIF0 Pin Settings (23)Table 3. M1 and M0 Settings (23)Table 4. Frequencies for 48 kHz Sample Rate using LJ/I²S (25)Table 5. Frequencies for 96 kHz Sample Rate using LJ/I²S (25)Table 6. Frequencies for 192 kHz Sample Rate using LJ/I²S (25)Table 7. Frequencies for 48 kHz Sample Rate using TDM (25)Table 8. Frequencies for 48 kHz Sample Rate using TDM (25)Table 9. Frequencies for 96 kHz Sample Rate using TDM (26)Table 10. Frequencies for 96 kHz Sample Rate using TDM (26)Table 11. Frequencies for 192 kHz Sample Rate using TDM (26)Table 12. Frequencies for 192 kHz Sample Rate using TDM (26)1.PIN DESCRIPTION ArrayFigure 1. CS5366 PinoutPin Name Pin #Pin DescriptionAIN2+, AIN2-AIN4+, AIN4-AIN3+, AIN3-AIN6+, AIN6-AIN5+, AIN5-AIN1+, AIN1-1,211,1213,1443,4445,4647,48Differential Analog (Inputs) - Audio signals are presented differently to the delta sigma modula-tors via the AIN+/- pins.GND3,810,1516,1718,1929,32Ground (Input) - Ground reference. Must be connected to analog ground.VA4,9Analog Power (Input)- Positive power supply for the analog sectionREF_GND5Reference Ground (Input) - For the internal sampling circuits. Must be connected to analog ground.FILT+6Positive Voltage Reference (Output) - Reference voltage for internal sampling circuits. VQ7Quiescent Voltage (Output) - Filter connection for the internal quiescent reference voltage.VX20Crystal Oscillator Power (Input) - Also powers control logic to enable or disable oscillator cir-cuits.XTI XTO 2122Crystal Oscillator Connections (Input/Output) - I/O pins for an external crystal which may be used to generate MCLK.MCLK23System Master Clock (Input/Output) - When a crystal is used, this pin acts as a buffered MCLK Source (Output). When the oscillator function is not used, this pin acts as an input for the system master clock. In this case, the XTI and XTO pins must be tied low.LRCK/FS24Serial Audio Channel Clock (Input/Output)In I²S mode Serial Audio Channel Select. When low, the odd channels are selected.In LJ mode Serial Audio Channel Select. When high, the odd channels are selected.In TDM Mode a frame sync signal. When high, it marks the beginning of a new frame of serial audio samples. In Slave Mode, this pin acts as an input pin.SCLK25Main timing clock for the Serial Audio Interface (Input/Output) - During Master Mode, this pin acts as an output, and during Slave Mode it acts as an input pin.TSTO26Test Out (Output) - Must be left unconnected.SDOUT227Serial Audio Data (Output) - Channels 3,4VLS28Serial Audio Interface Power - Positive power for the serial audio interface.SDOUT1/TDM30Serial Audio Data (Output) - Channels 1,2, TDM.SDOUT3/TDM31Serial Audio Data (Output) - Channels 5,6, TDM is complementary TDM data.VD33Digital Power (Input) - Positive power supply for the digital section.VLC35Control Port Interface Power - Positive power for the control port interface.OVFL36Overflow (Output, open drain) - Detects an overflow condition on both left and right channels.RST41Reset (Input) - The device enters a low power mode when low.Stand-Alone ModeCLKMODE34CLKMODE(Input) - Setting this pin HIGH places a divide-by-1.5 circuit in the MCLK path to the core device circuitry.DIF1 DIF03738DIF1, DIF0 (Input) - Sets the serial audio interface format.M1 M03940Mode Selection (Input) - Determines the operational mode of the device.MDIV42MCLK Divider (Input) - Setting this pin HIGH places a divide-by-2 circuit in the MCLK path to the core device circuitry.Control Port ModeCLKMODE34CLKMODE (Input) - This pin is ignored in Control Port Mode and the same functionality is obtained from the corresponding bit in the Global Control Register. Note: Should be connected to GND when using the part in Control Port Mode.AD1/CDIN37I²C Format, AD1 (Input) - Forms the device address input AD[1]. SPI Format, CDIN (Input) - Becomes the input data pin.AD0/CS38I²C Format, AD0 (Input) - Forms the device address input AD[0]. SPI Format, CS (Input) - Acts as the active low chip select input.SCL/CCLK39I²C Format, SCL (Input) - Serial clock for the serial control port. An external pull-up resistor is required for I²C control port operation.SPI Format, CCLK (Input) - Serial clock for the serial control port.SDA/CDOUT40I²C Format SDA (Input/Output) - Acts as an input/output data pin. An external pull-up resistor is required for I²C control port operation.SPI Format CDOUT (Output) - Acts as an output only data pin.MDIV42MCLK Divider (Input) - This pin is ignored in Control Port Mode and the same function-ality is obtained from the corresponding bit in the Global Control Register.Note: Should be connected to GND when using the part in Control Port Mode.2.TYPICAL CONNECTION DIAGRAM Array Figure 2. Typical Connection DiagramFor analog buffer configurations, refer to Cirrus Application Note AN241. Also, a low-cost single-ended-to-differen-tial solution is provided on the Customer Evaluation Board.3.CHARACTERISTICS AND SPECIFICATIONS RECOMMENDED OPERATING CONDITIONSGND = 0 V, all voltages with respect to 0 V.1.TDM Quad-Speed Mode specified to operate correctly at VLS ≥ 3.14 V.ABSOLUTE RATINGSOperation beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes. Transient currents up to ±100 mA on the analog input pins will not cause SCR latch-up.SYSTEM CLOCKINGParameterSymbol MinTypMax UnitDC Power Supplies:Positive Analog Positive Crystal Positive Digital Positive Serial Logic Positive Control LogicVA VX VD VLS VLC 4.754.753.141.7111.71 5.05.03.33.33.3 5.25VAmbient Operating Temperature(-CQZ) (-DQZ)T AC T AA-40-40--85105°CParameterSymbolMin Typ Max UnitsDC Power Supplies:Positive Analog Positive Crystal Positive Digital Positive Serial Logic Positive Control LogicVA VX VD VLS VLC -0.3-+6.0VInput Current I in -10-+10mA Analog Input Voltage V IN -0.3VA+0.3V Digital Input VoltageV IND VL+0.3Ambient Operating Temperature (Power Applied)T A -50+125°CStorage TemperatureT stg-65+150ParameterSymbolMinTyp MaxUnitInput Master Clock Frequency MCLK 0.51255.05MHz Input Master Clock Duty Cyclet clkhl4060%分销商库存信息:CIRRUS-LOGICCS5366-CQZ CS5366-DQZ CS5366-CQZR CS5366-DQZR。

Mapinfo内容简介

Mapinfo内容简介MapInfo地理信息系统平台作为一个图形-文字信息完善结合的软件工具,能将所需要的信息资料形象、直观地与地理图形紧密地联结起来,能提供大量常用的分析、查询功能,能将结果以图形或表格的方式显示出来。

MapInfo软件提供与一些常用数据库的接口,可以直接或间接地与这些数据库进行数据交换。

MapInfo软件提供的开发工具MapBasic, 可完成用户在图形、界面、查询、分析等方面的各种要求,以形成全用户化的应用集成。

配接多媒体系统可使用户对地图进行多媒体查询。

MapInfo软件适用于军队管理与指挥、市场营销、城市规划、市政管理、公安交通、邮电通讯、石油地质、土地资源、人口管理、金融保险等各个应用领域,能对用户的管理、决策提供有力的支持与帮助。

一、强大的图形表达、处理功能MapInfo做为一种功能强大的图形软件,利用点、线、区域等多种图形元素,及丰富的地图符号、文本类型、线型、填充模式和颜色等表现类型,可详尽、直观、形象地完成电子地图数据的显示。

同时MapInfo对于位图文件(如GIF、TIF、PCX、BMP、TGA等多种格式的位图文件)和卫片(SPOT)、航片、照片等栅格图象,也可以进行屏幕显示,根据实际需要还可以对其进行矢量化。

此外,DXF格式(AutoCAD和其它CAD软件包的图形/数据交换格式)的数据文件,也可以直接运用于MapInfo当中。

在图形处理方面,它提供了功能强大的编图工具箱,用户可以对各种图形元素任意进行增加、删除、修改等基本编辑操作。

MapInfo所处理的电子地图与一般地图不同。

一般的地图,各类要素、信息集中在一起,不利于不同用户对不同的地理信息的查询使用。

MapInfo对地图是分层处理,用户可以通过图形分层技术,根据自己的不同需求或一定的标准对各种图形元素进行分层组合,将一张地图分成不同图层。

例如对于某个城市图,可分为区划、道路、河流、建筑物、标注等若干层。

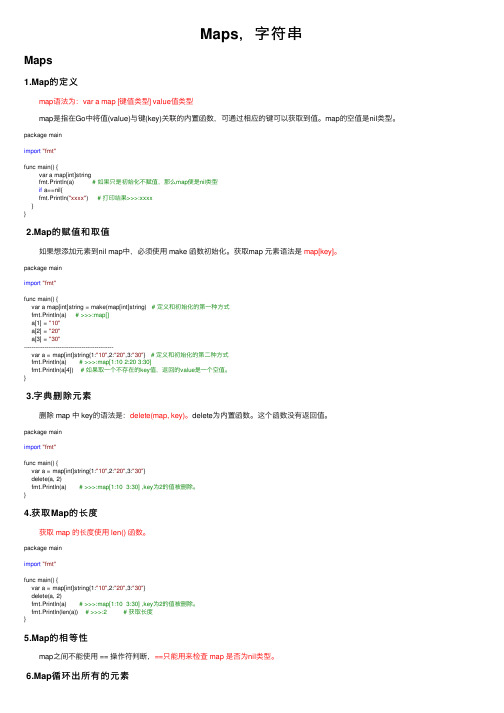

Maps,字符串

Maps,字符串Maps1.Map的定义 map语法为:var a map [键值类型] value值类型 map是指在Go中将值(value)与键(key)关联的内置函数,可通过相应的键可以获取到值。

map的空值是nil类型。

package mainimport"fmt"func main() {var a map[int]stringfmt.Println(a) # 如果只是初始化不赋值,那么map便是nil类型if a==nil{fmt.Println("xxxx") # 打印结果>>>:xxxx}}2.Map的赋值和取值 如果想添加元素到nil map中,必须使⽤ make 函数初始化。

获取map 元素语法是map[key]。

package mainimport"fmt"func main() {var a map[int]string = make(map[int]string) # 定义和初始化的第⼀种⽅式fmt.Println(a) # >>>:map[]a[1] = "10"a[2] = "20"a[3] = "30"------------------------------------------------var a = map[int]string{1:"10",2:"20",3:"30"} # 定义和初始化的第⼆种⽅式fmt.Println(a) # >>>:map[1:10 2:20 3:30]fmt.Println(a[4]) # 如果取⼀个不存在的key值,返回的value是⼀个空值。

}3.字典删除元素 删除 map 中 key的语法是:delete(map, key)。

ffmpeg中文文档

ffmpeg中文文档转自:https://wanglongqi.github.io/tools/2015/02/13/ffmpegcn/1. 概要ffmpeg [global_options] {[input_file_options] -i INPUT_FILE} ... {[output_file_options] OUTPUT_FILE} ...2. 说明ffmpeg是一个非常快的视频和音频转换器,还可以抓取实时的音频/视频流。

它可以在任意的采样率之间的转换和调整视频,并同时使用高品质的多相滤波器。

ffmpeg从输入“文件”(其可以是常规文件,管道,网络流,录制装置等),由指定任意数量的读取-i选项,并写入到任意数量的输出“文件”,只需指定一个输出的文件名。

任何一个命令行中不能被解释为选项的内容都被认为是一个输出文件名。

每个输入或输出文件可以在原则上,包含任意数量的不同类型(视频/音频/字幕/附件/数据)的流。

输出文件中允许流的数量和类型是由输出格式容器限制决定的。

输入流和输出流直接的映射可以自动完成也可以用-map选项给定(见流选择章节)。

引用输入文件的选项时,则必须使用他们的索引(从0开始)。

例如:第一输入文件是0 ,第二个是1等。

类似地,一个文件中的流也通过其索引指定。

例如2:3指的是在第三个输入文件中的第四数据流。

参见流章节。

作为一般规则,选项作用于下一个指定的文件。

因此,命令的顺序是重要,你可以在命令行上多次相同的选项。

每次选项的出现都将作用于下一个输入或输出文件。

这条规则若有例外将会提前声明(例如冗余级别)。

不要混合输入和输出文件。

首先指定所有输入文件,那么所有的输出文件。

也不要混用属于不同的文件的选项。

所有选项仅适用于下一个输入或输出文件,之后选项将被重置。

设置输出文件以64千比特/秒的视频比特率:ffmpeg -i input.avi -b:V 64K -bufsize 64K output.avi要强制输出文件为24 fps的帧速率:ffmpeg -i input.avi -r 24 output.avi 要强制输入文件的帧频(仅对原始格式有效),以1 FPS读入文件,以每秒24帧的帧速率输出:ffmpeg -r 1 -i input.m2v -r 24 output.aviformat 选项可能需要指定,对于原始输入文件。

TracePro中文使用手册(132-207页)

第六章 分析检验光线追迹结果完成光线追迹之后,当进行结果评估时,分析菜单提供多种方法来显示光线追迹数据。

Displaying Rays 和 Ray Sorting让你观察数据是否是你期待的结果。

Irradiance Maps, Ray Tables and Polarization Maps 提供每一个表面的模拟结果。

Candela Plots 显示模型中光线数据的角度分配。

Volume Flux Viewer能够观察模型内部的流量分布。

Reports Menu 帮助你完成分析光线数据和模型的多种报告形式。

Tools 菜单包括附加的功能来帮助你完成光线追迹结果。

Analysis Menu在本章中的描述中,大多数的光线追迹结果从Analysis Menu中得到,光线追迹也被包含在Analysis Menu项目的开始,这在第五章有详细地介绍。

Display RaysAnalysis | Display Rays 选项允许你控制光线的显示。

“Analysis Mode(分析模式)”下,在完成光线追迹后, 光线默认地被显示或取消。

光线在“Simulation Mode(模拟模式)”中不能够被显示。

要关闭显示的光线,只需进入Analysis | Display Rays,显示光线的状态是通过菜单上√ 标志来标注的。

如果被trace的光线有很多并且带有许多的splits or branches,程序会花很长时间来显示这些光线。

你可以根据需要设定Window|Auto Update来更新光线的显示,这时的光线不会被随时更新,直到你按“F5”或选择Window|Refresh。

光线也可能在和图画程序组合期间同步显示,当具有优先设置时。

参考2.43页的“Ray Display”。

你也可以按照下面的描述使用Ray Sorting来决定哪些光线显示。

Ray Colors可以通过Ray Color对话框来设置光线的颜色来取代预先设值的颜色值,对于单色光,Ray Color对话框提供三种预设的颜色值来显示光线颜色。

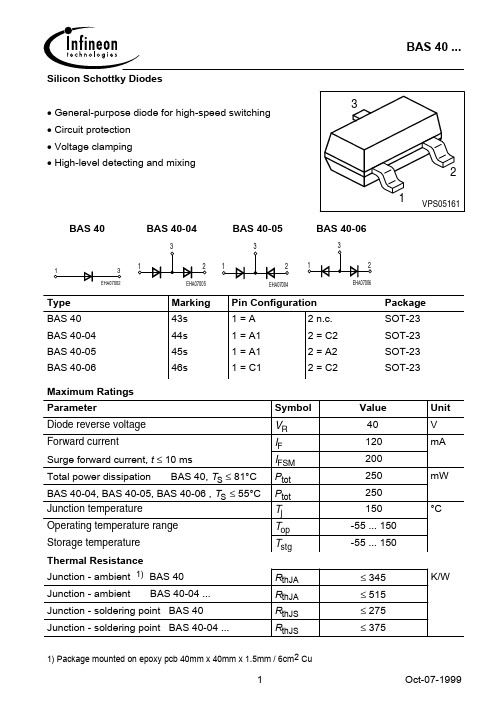

bas 40中文资料

2

Oct-07-1999

元器件交易网

BAS 40 ...

Forward current IF = f (VF )

TA = 25°C

10 2

BAS 40... EHB00038

Reverse current IR = f (VR)

TA = Parameter

BAS 40... EHB00039

ΙF

3

Oct-07-1999

元器件交易网

BAS 40 ...

Forward current IF = f (TA *;TS ) * Package mounted on epoxy

200

BAS 40... EHB00150

ΙF

mA 160 140 120 100 80 TA 60 40 20 0 0 50 100 ˚C 150 TS

Pin Configuration 1=A 1 = A1 1 = A1 1 = C1 2 n.c. 2 = C2 2 = A2 2 = C2

Package SOT-23 SOT-23 SOT-23 SOT-23

Maximum Ratings Parameter Diode reverse voltage Forward current Surge forward current, t ≤ 10 ms Total power dissipation BAS 40, TS ≤ 81°C BAS 40-04, BAS 40-05, BAS 40-06 , TS ≤ 55°C Junction temperature Operating temperature range Storage temperature Thermal Resistance Junction - ambient 1) BAS 40 Junction - ambient BAS 40-04 ... Junction - soldering point BAS 40 Junction - soldering point BAS 40-04 ...

MLX90620ESF-BAB-000;中文规格书,Datasheet资料

(1) Supply Voltage B = 3V

(3) Package options: A = reserved B = 60° FOV C = reserved D = 40° FOV

Example: MLX90620ESF-BAB-000-TU

Functional diagram

Digital Active Thermopile Array

16x4 IR array

General Description (continued)

The results of the infrared sensor measurements are stored in RAM: • 16-bit result of IR measurement for each individual sensor (64 words) • 16-bit result of PTAT sensor Depending on the application, the external microcontroller can read the different RAM data and, based on the calibration data stored in the EEPROM memory, compensate for difference between sensors to build up a thermal image, or calculate the temperature at each spot of the imaged scene. These constants are accessible by the user microcontroller through the I2C bus and have to be used for external post processing of the thermal data. This post processing includes: • Ta calculation • Pixel offset cancelling • Pixel to pixel sensitivity difference compensation • Object emissivity compensation • Object temperature calculation The result is an image with NETD better than 0.5K at 1Hz refresh rate. The refresh rate of the array is programmable by means of register settings or directly via I2C command. Changes of the refresh rate have a direct impact on the integration time and noise bandwidth (faster refresh rate means higher noise level). The frame rate is programmable in the range 0,5Hz…512Hz and can be changed to achieve the desired trade off between speed and accuracy. The MLX90620 requires a single 3V supply (±0,6V). The customer can choose between 3 operating modes: • Normal. In this mode the device is free running under control of the internal state machine. Depending on the selected refresh rate Fps (Frame per second) the chip is constantly measuring both IR and PTAT and is refreshing the data in the RAM with specified refresh rate; • Step. This mode is foreseen for synchronization with an external micro-controller. The internal state machine is halted. If the command ‘StartMeas’ is received via the I2C bus, a single measurement of all IR and PTAT sensors will be done, then the chip will return in wait state. When in wait state the data in RAM can be read. The MLX90620 is factory calibrated in wide temperature ranges: • -40…85 ˚C for the ambient temperature sensor • -50…300 ˚C for the object temperature. Each pixel of the array measures the average temperature of all objects in its own Field Of View (called nFOV). It is very important for the application designer to understand that the accuracy of the temperature measurement is very sensitive to the thermal equilibrium isothermal conditions (there are no temperature differences across the sensor package). The accuracy of the thermometer can be influenced by temperature differences in the package induced by causes like (among others): Hot electronics behind the sensor, heaters/coolers behind or beside the sensor or by a hot/cold object very close to the sensor that not only heats the sensing element in the thermometer but also the thermometer package. This effect is especially relevant for thermometers with a small FOV as the energy received by the sensor from the object is reduced

AD9273BSVZ-50;AD9273BSVZ-25;AD9273BBCZ-25;AD9273BSVZ-40;AD9273BBCZ-40;中文规格书,Datasheet资料

/

CLK+ CLK–

AD9273 TABLE OF CONTENTS

Features .............................................................................................. 1 Applications ....................................................................................... 1 General Description ......................................................................... 1 Functional Block Diagram .............................................................. 1 Revision History ............................................................................... 2 Product Highlights ........................................................................... 3 Specifications..................................................................................... 4 AC Specifications.......................................................................... 4 Digital Specifications ................................................................... 8 Switching Specifications .............................................................. 9 ADC Timing Diagrams ................................................................. 10 Absolute Maximum Ratings.......................................................... 11 Thermal Impedance ................................................................... 11 ESD Caution ................................................................................ 11 Pin Configuration and Function Descriptions ........................... 12 Typical Performance Characteristics ........................................... 15 Equivalent Circuits ......................................................................... 19 Theory of Operation ...................................................................... 21 Ultrasound .................................................................................. 21 Channel Overview ..................................................................... 22 Input Overdrive .......................................................................... 25 CW Doppler Operation............................................................. 25 TGC Operation ........................................................................... 27 ADC ............................................................................................. 31 Clock Input Considerations ...................................................... 31 Serial Port Interface (SPI) .............................................................. 38 Hardware Interface..................................................................... 38 Memory Map .................................................................................. 40 Reading the Memory Map Table .............................................. 40 Reserved Locations .................................................................... 40 Default Values ............................................................................. 40 Logic Levels ................................................................................. 40 Outline Dimensions ....................................................................... 44 Ordering Guide .......................................................................... 45

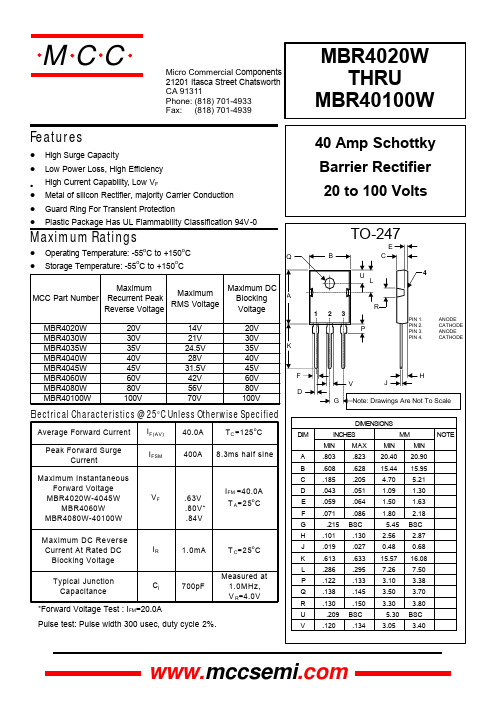

MBR4040W中文资料

o

o

MCC Part Number

Maximum DC Blocking Voltage 20V 30V 35V 40V 45V 60V 80V 100V

A R 1 2 3 P K

PIN 1. PIN 2. PIN 3. PIN 4. ANODE CATHODE ANODE CATHODE

1

2

5

102050100CASE TEMPERATURE , C

NUMBER OF CYCLES AT 60Hz

FIG.3 - TYPICAL REVERSE CHARACTERISTICS

100

FIG.4 - TYPICAL FORWARD CHARACTERISTICS

100

INSTANTANEOUS FORWARD CURRENT ,(A)

DIMENSIONS

Average Forward Current Peak Forward Surge Current Maximum Instantaneous Forward Voltage MBR4020W-4045W MBR4060W MBR4080W-40100W Maximum DC Reverse Current At Rated DC Blocking Voltage Typical Junction Capacitance

MM MIN 20.90 15.95 5.21 1.30 1.63 2.18 BSC 2.87 0.68 16.08 7.50 3.38 3.70 3.80 BSC 3.40

NOTE

VF

.63V .80V* .84V

I FM =40.0A T A = 2 5o C

D E F G H J K L

P40坦克资料

P-40坦克英文名称:P-40P-26类型:重型坦克所属国家:意大利研发单位:安萨尔多又名P-26为第二次世界大战中,由意大利所研制的一款坦克,装备口径75公厘的主炮和8公厘的布瑞达机枪,另外还有专用防空机枪可装备。

意大利官方将其称作“Carro Armato P 26/40”,“Carro Armato”意为装甲坦克,P指的是意大利语的“重(Pesante)”,26和40则分别为“重量(吨)”和设计通过的“年份(1940)研发历程变形义军计划了至少2种P-40的变形车,一种被命名为P-43,重量超过30吨,将有大约80公厘的正面装甲,加长型的75公厘主炮或是与赛门凡特相同的90公厘51倍径主炮,然而该变形车仅有一对木制模型被生产过。

另一种变形车为以P-40底盘所建造的赛门凡特149自行火炮,仅完成了一辆试作车,现收藏于美国火炮博物馆(Ordnance Museum)。

它的功能是对意大利军提供一个高速的自行火炮,40倍径、口径149公厘的赛门凡特是义军所拥有最大火力的武器,射程约有23.7公里,超过美国M59加农炮的部份型号。

这种火炮的生产数量极少,整场战争中义军主要是使用老旧的小口径火炮。

由于该炮的重量过重,不适合牵引移动,因此选用意大利动力最大的车体来装配为自行火炮,P-40就因此被选定了。

由于P-40车体主要的空间都被主炮所占据,弹药和人员需要以额外的车辆来支援行动。

研制赛门凡特自行火炮的工作始于1942年,1943年才对原型车进行了测试,但义军对其并无留下特别印象,其后接收它的德国人也是。

最后由美军入侵德国时掳获了它,并送到阿伯丁试验场进行测试。

装备配置设计P-40的起源是来自意大利军方面对即将投入的战争,要求开发新式的重型坦克而来。

虽然在1940年已完成了设计,第一辆原型车却是到1942年才被制造出来。

最初的计划是设计为26吨坦克,并配备口径75公厘的主炮,命名为P-26。

机动力除了引擎外,坦克技术发展迅速,意大利总参谋部认为应使用柴油引擎,而建造者却认为它应配备汽油引擎。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1

MAP55 SERIES

Power-One's MAP55 series of power supplies provides reliable, tightly regulated DC power for commercial and industrial systems. Wide-range AC input and full international safety, EMI, and ESD compliance ensure world-wide acceptance. All units bear the CE Mark.

The MAP55 utilizes a thermally efficient U-channel chassis design,which allows full power operation in convection cooled applications.Other mechanical design innovations include metric and SAE mounting inserts on each mounting surface to provide integration flexibility. Dual-mode connectors provide traditional terminal block connections or popular single row Molex connector mating.Single output models feature wide-range output adjustability to meet a wide variety of standard and user specific output voltage requirements.

FEATURES