SN67268中文资料

6lb184中文资料

6lb184中文资料6lb184中文资料【用途】RS485/422电平转换电路【性能参数】双列贴片8脚封装。

TTL-RS485/422电平转换。

工作电压4.75-5.25V,典型5V。

【互换兼容】SN65LBC184D【6LB184的原厂(中文)资料数据手册脚功能参数封装】摘要:电子镇流器(Electrical ballast)是镇流器的一种,是指采用电子技术驱动电光源,使之产生所需照明的电子设备。

电子镇流器自身功耗低,有更佳的照明效果,消除了闪频现象,发光更稳定,而且可以调光。

文章采用AVR单片机作为控制芯片,通过电子镇流器进行调光和相关功能的控制,最大限度地发挥智能型镇流器的特点。

实际应用表明,文中的方法有效。

0 引言电子镇流器是新型节能产品,不仅能带动一些照明灯具,还可以和一些紫外灯结合在一起,对于空气净化和水源净化都有着非常大的作用。

当前,全世界都在大力提倡环境保护,电子镇流器间接地为环保提供了原动力。

AVR单片机是一款性价比较高的单片机,用这种单片机来对电子镇流器进行调光和时间采样非常合适,首先是AVR单片机本身较稳定,抗干扰能力比较强,其次是其本身的Harvard结构使得运行速度比较快,数据回读时间较快,可以实现实时在线控制。

1 AVR单片机介绍1.1 AVR单片机的特点与以往的8位单片机相比,AVR单片机采用Harvard结构,也就是程序总线和数据总线分开,并采用两级流水线,具备1MIPS/MHz的高速运行处理能力。

片内集成多种频率的RC振荡器、上电自动复位、看门狗、启动延时等功能模块,外围电路简单,系统更加稳定可靠。

大部分AVR片上资源丰富:带E2PROM、PWM、RTC、SPI、UART、TWI、ISP、AD、Analog Comparator、WDT等单元模块。

1.2 AVR单片机的PWM功能AVR单片机的定时器功能强大,以Atmega48为例,它有两个8位定时器和一个16位定时器,都具有硬件PWM功能。

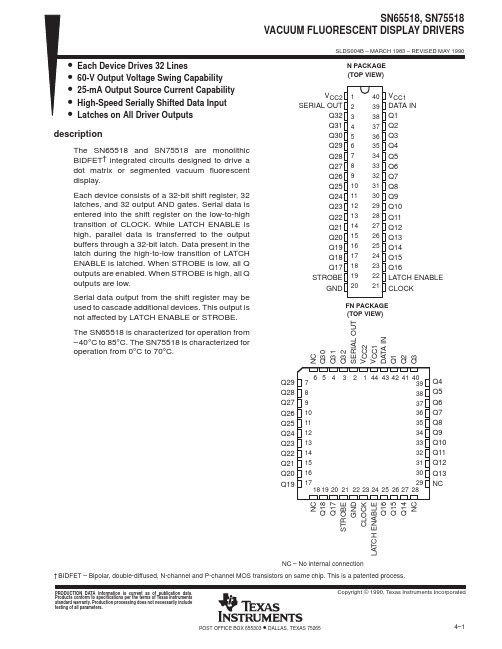

SN75518中文资料

元器件交易网IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinueany product or service without notice, and advise customers to obtain the latest version of relevant informationto verify, before placing orders, that information being relied on is current and complete. All products are soldsubject to the terms and conditions of sale supplied at the time of order acknowledgement, including thosepertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extentTI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarilyperformed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OFDEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICALAPPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, ORWARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHERCRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TOBE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operatingsafeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or representthat any license, either express or implied, is granted under any patent right, copyright, mask work right, or otherintellectual property right of TI covering or relating to any combination, machine, or process in which suchsemiconductor products or services might be or are used. TI’s publication of information regarding any thirdparty’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1998, Texas Instruments Incorporated。

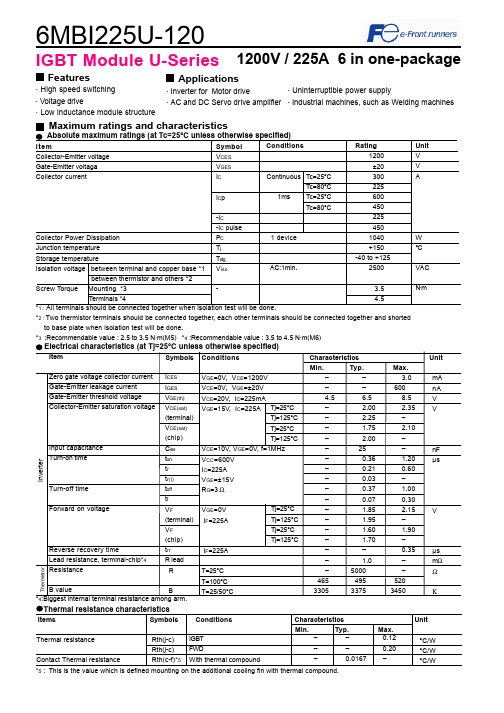

6MBI225U-120中文资料

6MBI225U-1201200V / 225A 6 in one-packageFeatures· High speed switching· Voltage drive· Low inductance module structureApplications · Inverter for Motor drive· AC and DC Servo drive amplifierMaximum ratings and characteristicsThermal resistance characteristicsThermal resistanceContact Thermal resistance––0.12––0.20–0.0167 –IGBTFWDWith thermal compound°C/W°C/W°C/W*2 : Two thermistor terminals should be connected together, each other terminals should be connected together and shortedto base plate when isolation test will be done.*3 :Recommendable value : 2.5 to 3.5 N·m(M5) *4 :Recommendable value : 3.5 to 4.5 N·m(M6)Rth(j-c)Rth(j-c)Rth(c-f)*5IGBT Module U-Series*5 : This is the value which is defined mounting on the additional cooling fin with thermal compound.4Items Symbols Conditions Characteristics UnitMin.Typ. Max.· Uninterruptible power supply· Industrial machines, such as Welding machinesCharacteristics (Representative)VGE=0V, f= 1MHz, Tj= 25°CVcc=600V, I=225A, Tj= 25°CCollector current vs. Collector-Emitter voltage (typ.)Tj= 125°C / chipCapacitance vs. Collector-Emitter voltage (typ.)Dynamic Gate charge (typ.)Collector current vs. Collector-Emitter voltage (typ.)Tj= 25°C / chipCollector current vs. Collector-Emitter voltage (typ.)VGE=15V / chipTj=25°C / chipCollector-Emitter voltage vs. Gate-Emitter voltage (typ.)010020030040050060012345C o l l e c t o r c u r r e n t : I c [A ]VGE=20V15V12V10V8V010020030040050060012345C o l l e c t o r c u r r e n t : I c [A ]VGE=20V 15V12V10V8V010020030040050060001234C o l l e c t o r c u r r e n t : I c [A ]Tj=125°CTj=25°C246810510152025C o l l e c t o r - E m i t t e r v o l t a g e : V C E [ V ]Ic=450A Ic=225A Ic= 112.5A0.11.010.0100.0102030C a p a c i t a n c e : C i e s , C o e s , C r e s [ n F ]200400600800100012001400C o l l e c t o r -E m i t t e r v o l t a g e : V C E [ 200V /d i v ]G a t e - E m i t t e r v o l t a g e : V G E [ 5V /d i v]Vcc=600V, Ic=225A, VGE=±15V, Tj= 25°CStray inductance <= 100nHSwitching loss vs. Collector current (typ.)Vcc=600V, VGE=±15V, Rg=3ΩVcc=600V, Ic=225A, VGE=±15V, Tj= 125°C+VGE=15V,-VGE <= 15V, RG >= 3Ω ,Tj <= 125°CSwitching time vs. Collector current (typ.)Vcc=600V, VGE=±15V, Rg=3Ω, Tj=125°CSwitching time vs. Gate resistance (typ.)Switching time vs. Collector current (typ.)Vcc=600V, VGE=±15V, Rg=3Ω, Tj= 25°CReverse bias safe operating area (max.)Switching loss vs. Gate resistance (typ.)10100100010000100200300400S w i t c h i n g t i m e : t o n , t r , t o f f , t f [ n s e c ]Collector current : Ic [ A ]10100100010000100200300400S w i t c h i n g t i m e : t o n , t r , t o f f , t f [ n s e c ]Collector current : Ic [ A ]10100100010000110100S w i t c h i n g t i m e : t o n , t r , t o f f , t f [ n s e c ]Gate resistance : Rg [ Ω ]trtftoffton 01020304050100200300400500S w i t c h i n g l o s s : E o n , E o f f , E r r [ m J /p u l s e ]Collector current : Ic [ A ]Eon(125°C)Eon(25°C)Eoff(125°C)Err(125°C)Err(25°C)Eoff(25°C)0255075100125150110100S w i t c h i n g l o s s : E o n , E o f f , E r r [ m J /p u l s e ]Gate resistance : Rg [ Ω ]EoffErrEon0100200300400500600200400600800100012001400C o l l e c t o r c u r r e n t : I c [ A ]Collector - Emitter voltage : VCE [ V ]Transient thermal resistance (max.)Reverse recovery characteristics (typ.)Vcc=600V, VGE=±15V, Rg=3ΩForward current vs. Forward on voltage (typ.)chipTemperature characteristic (typ.)01002003004005006001234F o r w a r d c u r r e n t : I F [ A ]Forward on voltage : VF [ V ]Tj=125°CTj=25°C101001000100200300400500R e v e r s e r e c o v e r y c u r r e n t : I r r [ A ]R e v e r s e r e c o v e r y t i m e : t r r [ n s e c ]Forward current : IF [ A ]Irr (125°C)Irr (25°C)trr (125°C)trr (25°C)0.0010.0100.1001.0000.0010.0100.1001.000T h e r m a l r e s i s t a n s e : R t h (j -c ) [ °C /W ]Pulse width : Pw [ sec ]0.1110100-60-40-20020406080100120140160180Temperature [°C ]R e s i s t a n c e : R [ k Ω ]Outline Drawings, mmM6296MBI225U-120IGBT ModuleEquivalent Circuit Schematic[Thermister]135111210987246[Inverter]。

TDA7268中文资料

TDA7268

2 x 2W STEREO AUDIO AMPLIFIER

WIDE OPERATING RANGE FROM 4.5V TO 18V POUT = 2W @ THD 10% 12V/8Ω INTERNAL FIXED GAIN 32dB NO FEEDBACK CAPACITOR NO BOUCHEROT CELL THERMAL PROTECTION AC SHORT CIRCUIT PROTECTION SVR CAPACITOR FOR BETTER RIPPLE REJECTION LOW TURN-ON/OFF POP VERY FEW EXTERNAL COMPONENTS STAND-BY MODE (IST-BY < 300µA)

Note: Add R1 & R2 on demoboard only for DC tests.

Fig. 2: PCB And Components Layout Of The Application Circuit of Figure 1

APPLICATION HINTS:

For 12V supply and 8Ω speaker application, its maximum power dissipation is about 2W.

DESCRIPTION The device TDA7268 is a new technology stereo Audio Amplifier in DIP package specially de-

BLOCK DIAGRAM

POWERDIP (8+8)

ORDERING NUMBER: TDA7268

6/5

Example of heatsink using PC board copper

7816nsn参数

7816nsn参数7816NSN是一种特定的参数,它在通信领域中起到了重要的作用。

本文将详细介绍7816NSN参数的定义、功能以及应用领域。

我们来了解一下7816NSN参数的定义。

7816NSN是一种标准化的参数,用于描述智能卡或芯片的通信协议。

它规定了智能卡与读卡器之间的通信方式和数据传输规则,确保了智能卡与读卡器之间的互操作性。

接下来,我们来了解一下7816NSN参数的功能。

7816NSN参数主要用于智能卡与读卡器之间的数据传输和通信控制。

通过采用7816NSN参数,智能卡可以与读卡器进行数据交换,包括读取卡片上的数据、写入数据到卡片、执行卡片上的指令等。

同时,7816NSN 参数还规定了错误处理机制,确保数据的完整性和安全性。

7816NSN参数在各个领域都有广泛的应用。

首先,在金融领域,7816NSN参数被广泛应用于银行卡和信用卡等支付卡的通信协议中。

通过7816NSN参数,银行卡可以与读卡器进行安全的数据传输,实现支付和身份验证等功能。

其次,在电信领域,7816NSN参数被应用于SIM卡的通信协议中。

通过7816NSN参数,SIM卡可以与手机进行通信,实现短信、电话、上网等功能。

此外,7816NSN参数还被应用于门禁卡、健康卡、交通卡等各种智能卡的通信协议中。

7816NSN参数的应用还可以扩展到更多领域。

例如,在物联网领域,通过采用7816NSN参数,智能设备可以与智能网关进行通信,实现设备的远程监控和控制。

在智能家居领域,通过7816NSN参数,智能家居设备可以与中央控制器进行通信,实现家庭自动化的功能。

此外,7816NSN参数还可以应用于车载设备、工业自动化等领域,实现设备之间的数据交换和通信控制。

7816NSN参数在通信领域中起到了重要的作用。

它规定了智能卡与读卡器之间的通信方式和数据传输规则,确保了智能卡与读卡器之间的互操作性。

通过采用7816NSN参数,智能卡可以与读卡器进行数据交换,实现各种功能,如支付、身份验证、远程监控等。

BA6287F中文资料

BA6287F

(7) Power consumption The power consumption by the IC varies widely with the power supply voltage and the output current. Give full consideration to the power dissipation rating and the thermal resistance data and transient thermal resistance data, to provide a thermal design so that none of the ratings for the IC are exceeded. (8) ASO Make sure that the output current and supply voltage do not exceed the ASO values. (9) Precautions for input mode switching To ensure reliability, it is recommended that the mode switching for the motor pass once through the open mode. (10) In-rush current There are no circuits built into these ICs that prevent inrush currents. Therefore, it is recommended to place a current limiting resistor or other physical countermeasure. (11) Factors regarding the thermal, power supply, and motor conditions If the potential of the output pin sways greatly and goes below the potential of ground, the operation of the IC may malfunction or be adversely affected. In such a case, place a diode between the output and ground, or other measure, to prevent this. (12) HIGH level output voltage setting pin Ensure that the voltage applied to VREF does not exceed the voltage on the motor power supply pin or the VCC pin. (13) The input pins have temperature-dependent characteristics. Take the temperature effect into consideration when using the IC. (14) To eliminate motor noise, connect a capacitor between OUT1 and GND and between OUT2 and GND. Alternatively, connect a capacitor between OUT1 and OUT2, and also a diode between OUT1 and GND and between OUT2 and GND (see Fig. 2).

MT7668SN模块(RL-SM01F-7668S-V3.0 )规格书

155 232 3.3 144 487 580 615 717 369

mA mA mA mA mA mA mA mA mA

7.Electrical Specifications

1) RF Characteristics for IEEE802.11b ( 11Mbps mode unless otherwise specified)

Security

Bus Interface

.0.Operating Channel

Power Consumption

Operating Temperature Storage Temperature Humidity Dimension

-10 ~ +70° C ambient temperature -20 ~ 85°C ambient temperature 5 to 90 % maximum (non-condensing) 15 x 13 x1.6mm (LxWxH) ±0.2MM

n Bluetooth5.0 n ANT/ANT+ n Integrated BALUN and PA n Scatternet support: Up to 7 piconets simultaneously with background inquiry/page scan n Up to 7 BT link and32BLE link n Support SCO and eSCO link with re-transmission n Support wide-band speech and hardware accelerated SBC codec for A2DP streaming n Packet loss concealment n Channel quality driven data rate adaptation n Channel assessment and WB RSSI for AFH n Integrate 8Kbit efuse to store device specific information and RF calibration data. n Advanced FDD/TDD mode Wi-Fi/Bluetooth coexistence scheme

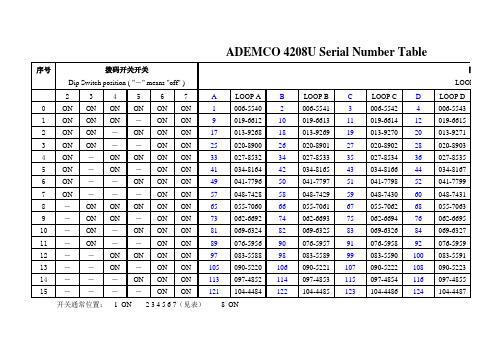

4208SN详细防区序列号表

79

062-6702

80

防 062-6703

85

069-6332

86

069-6333

87

069-6334

88

区 069-6335

93

076-5964

94

076-5965

95

076-5966

96

号 076-5967

101 083-5596 102 083-5597 103 083-5598 104 083-5599

13 - - ON - ON ON

14 - - - ON ON ON 15 - - - - ON ON

A

LOOP A

B

LOOP B

C

LOOP C

D

1

006-5540

2

006-5541

3

006-5542

4

9

019-6612 10 019-6613 11 019-6614 12

17 013-9268 18 013-9269 19 013-9270 20

序号

拨码开关开关

ADEMCO 4208U Serial Number Table

Dip Switch position ( "-" means "off" )

2

3

4

5

6

7

A

LOOP A

B

LOOP B

C

LOOP C

D

0 ON ON ON ON ON -

1

006-5796

2

006-5797

3

006-5798

4 ON - ON ON ON ON

5 ON - ON - ON ON

servo one操作手册

操作手册

伺服驱动器 2.0 A to 8 A

ServoOne junior 操作手册

ServoOne junior 高性能驱动器

ServoOne junior采用模块化设计,以确保在机械加工过程中发挥其最佳性能集。 无论高速现场总线与中央多轴设备控制器的通讯,还是与伺服驱动器中的分布式可编程 智能运动控制程序通讯,ServoOne junior均能应用自如。

预期用途................................................................................................................. 10 责任........................................................................................................................ 10

公告机构: 识别号: EC型式试验

TüV Rheinland Industrie Service GmbH Am Grauen Stein, 51105 Köln 0035 Certificate No.: 01/205/5036/10

授权编写本技术文件的人员: Matthias Wagner, Gewerbestrasse 5-9, 35633 Lahnau (Germany) CE标志年份: 2010

3.12 编码器接口 ............................................................................................................. 26 3.12.1 旋变(Resolver)接口 X6 ............................................................................. 28 3.12.2 高分辨率编码器接口 X7 .............................................................................. 28 3.13 电机连接................................................................................................................. 29 3.13.1 LSH/LST电机的连接 ................................................................................... 30 3.13.2 接通电机电缆............................................................................................... 31 3.14 制动电阻(RB)....................................................................................................... 31

PC87366中文资料

PC87366 128-Pin LPC SuperI/O with System Hardware Monitoring, MIDI and Game PortsGeneral DescriptionThe PC87366,a member of National Semiconductor’s 128-pin LPC SuperI/O family,combines National’s System Hardware Monitoring capability with a Musical Instrument Digital Interface (MIDI)Port and game port inputs for up to two joysticks.The PC87366is PC99and ACPI compliant,and offers a single-chip solution to the most commonly used PC I/O peripherals.System Hardware Monitoring provides minimum power con-sumption and maximum operating efficiency within the system environment.It integrates National’s diode-based or thermistor-based Temperature Sensor (TMS)with National’s Voltage Lev-el Monitor (VLM)for full,PC system thermal control.The PC87366monitors system voltages using 8-bit Analog to Dig-ital (A/D)conversion with seven analog input channels and four internal measuring points.The PC87366also incorporates:Fan Speed Control and Monitor (FSCM)for three fans,extended wake-up support for a wide range of wake-up events,system design protection features,a Floppy Disk Controller (FDC),a Keyboard and Mouse Controller (KBC),a full IEEE 1284Parallel Port,two enhanced Serial Ports (UARTs),one with Infrared (IR)sup-port,ACCESS.bus ®Interface (ACB),System Wake-Up Control (SWC),General-Purpose Input/Output (GPIO)sup-port for 40ports,Interrupt Serializer for Parallel IRQs and an enhanced WATCHDOG ™ timer (WDT).Outstanding FeaturesqSystem Hardware Monitoring including:—Diode-based or thermistor-based T emperature Sen-sor (TMS)—Voltage Level Monitor (VLM) with VID inputs q MIDI interface compatible with MPU-401UART mode q Game port inputs for up to two joysticksqExtended Wake-Up support,including legacy/ACPI power button support,direct power supply control in response to wake-up events,power-fail recovery qProtection features,including chassis intrusion detection,GPIO lock and pin configuration lockq Fan Speed Control and Monitor for three fans q Serial IRQ support (15options)q Interrupt Serializer (11Parallel IRQs to Serial IRQ)qBus interface,based on Intel’s LPC Interface Specifi-cation Revision 1.0,September 29th,1997q ACCESS.bus interface,SMBus physical layer compatible q40GPIO Ports (29standard,including 15with Assert IRQ/SMI/PWUREQs interrupts;11V SB -powered)q Blinking LEDsq128-pin PQFP PackageBlock DiagramSystem Wake-UpSerial Port 2IEEE 1284Parallel PortPorts Keyboard &Mouse I/F SCL ACCESS.bus Floppy Disk ControllerFloppy Drive InterfaceKeyboard &Serial Infrared Interface InterfaceControl Bus InterfaceLPC Interface I/O3 Control WATCHDOGTimer WDOSerial Port 1Serial InterfaceOutputs Fan Speed Control & Monitor Interface Mouse Controllerwith IRGPIO Ports3 Monitor InputsSDA Serial IRQ Analog Inputs System Parallel Port Interface Diode InterfaceSMI PortsHardware MonitoringV REF MIDIInterface MIDI &Game PortsGame Inputs Wake-Up EventsPWUREQ Power Control V DD V BdAT V SBAV DD ACCESS.bus® is a registered trademark of Digital Equipment Corporation.I2C® is a registered trademark of Philips Corporation.IBM®, MicroChannel®, PC-AT® and PS/2® are registered trademarks of International Business Machines Corporation.Microsoft® and Windows® are registered trademarks of Microsoft Corporation.TRI-STATE® is a registered trademark of National Semiconductor Corporation.WATCHDOG‰ is a trademark of National Semiconductor Corporation.SMBus® is a registered trademark of Intel Corporation.© 1999 National Semiconductor CorporationPRELIMINARYJanuary 11,1999PC87366128-Pin LPC SuperI/O with System Hardware Monitoring,MIDI and Game PortsFeatures•Voltage Level Monitor (VLM)—Seven analog inputs that can support both positive and negative voltages—Four internal measuring points—Three thermistor-based temperature monitoring channels—Internal or external V REF—VID inputs—Meets ACPI and DMI requirements for system volt-age monitoring•Temperature Sensor (TMS)—Up to two remote diode inputs—Environment temperature sensing via an internal di-ode—A/D analog channels provide thermal inputs to di-rectly sense die temperature of remote diodes —Meets ACPI and DMI requirements for thermal man-agement—Standby mode to minimize power consumption •Extended Wake-Up—Legacy and ACPI power button support—Direct power supply control in response to wake-up events—Power-fail recovery•Musical Instrument Digital Interface (MIDI) Port —Compatible with MPU-401 UART mode—16-byte Receive and T ransmit FIFOs—Loopback mode supportq Game Port—Full digital implementation—Supports up to two analog joysticks •Protection—Chassis intrusion detection (CHASI, CHASO)—GPIO lock—Pin configuration lock•40 General-Purpose I/O (GPIO) Ports—29standard,with Assert IRQ/SMI/PWUREQ for15 ports—11 V SB-powered—Programmable drive type for each output pin(open-drain, push-pull or output disable)—Programmable option for internal pull-up resistor on each input pin—Output lock option—Input debounce mechanism•Fan Speed Control and Fan Speed Monitor (FSCM)—Supports different fan types—Speed monitoring for three fanst Digital filtering of the tachometer input signalt Alarm for fan slower than programmable thresh-old speedt Alarm for fan stop—Three speed control lines with Pulse Width Modula-tion (PWM)t Output signal in the range of 6 Hz to 93.75 KHzt Duty cycle resolution of 1/256•LPC System Interface—Synchronous cycles, up to 33 MHz bus clock—8-bit I/O cycles—Up to four DMA channels—8-bit DMA cycles—Basic read,write and DMA bus cycles are13clock cycles long•PC99 and ACPI Compliant—PnP Configuration Register structure—Flexible resource allocation for all logical devices t Relocatable base addresst15 IRQ routing optionst4optional8-bit DMA channels(where applicable)•Floppy Disk Controller (FDC)—Programmable write protect—FM and MFM mode support—Enhanced mode command for three-mode Floppy Disk Drive (FDD) support—Perpendicular recording drive support for 2.88 MB—Burst and non-burst modes—Full support for IBM T ape Drive register(TDR)im-plementation of AT and PS/2 drive types—16-byte FIFO—Software compatible with the PC8477,which con-tains a superset of the FDC functions in themicroDP8473,the NEC microPD765A and theN82077—High-performance, digital separator—Standard 5.25” and 3.5” FDD support•Parallel Port—Software or hardware control—Enhanced Parallel Port(EPP)compatible with new version EPP 1.9 and IEEE 1284 compliant—EPP support for version EPP1.7of the Xircom spec-ification—EPP support as mode4of the Extended Capabilities Port (ECP)—IEEE 1284 compliant ECP, including level 2—Selection of internal pull-up or pull-down resistor for Paper End (PE) pin—PCI bus utilization reduction by supporting a de-mand DMA mode mechanism and a DMA fairnessmechanism—Protection circuit that prevents damage to the paral-lel port when a printer connected to it powers up oris operated at high voltages,even if the device is inpower-down—Output buffers that can sink and source 14 mA•Serial Port 1 (UART1)—Software compatible with the 16550A and the 164502Features(Continued)3—Shadow register support for write-only bit monitoring —UART data rates up to 1.5 Mbaud•Serial Port 2 with Infrared (UART2)—Software compatible with the 16550A and the 16450—Shadow register support for write-only bit monitoring —UART data rates up to 1.5 Mbaud —HP-SIR—ASK-IR option of SHARP-IR —DASK-IR option of SHARP-IR—Consumer Remote Control supports RC-5,RC-6,NEC, RCA and RECS 80—Non-standard DMA support −1 or 2 channels —PnP dongle support •Keyboard and Mouse Controller (KBC)—8-bit microcontroller—Software compatible with the 8042AH and PC87911microcontrollers— 2 KB custom-designed program ROM —256 bytes RAM for data—Five programmable dedicated open-drain I/O lines —Asynchronous access to two data registers and onestatus register during normal operation —Support for both interrupt and polling —93 instructions —8-bit timer/counter—Support for binary and BCD arithmetic—Operation at 8MHz,12MHz or 16MHz (programma-ble option)—Can be customized by using the PC87323,which in-cludes a RAM-based KBC as a development plat-form for KBC code•ACCESS.bus Interface (ACB)—Serial interface compatible with SMBus physical layer —Compatible with Philips’ I 2C ®—ACB master and slave—Supports polling and interrupt controlled operation —Optional internal pull-up on SDA and SCL pins•WATCHDOG Timer (WDT)—Times out the system based on user-programmabletime-out period—System power-down capability for power saving —User-defined trigger events to restart WATCHDOG —Optional routing of WATCHDOG output on IRQand/or SMI lines•System Wake-Up Control (SWC)—Power-up request upon detection of Keyboard,Mouse,RI1,RI2,RING activity and General-Pur-pose Input Events, as follows:t Preprogrammed Keyboard or Mouse sequence t External modem ring on serial portt Ring pulse or pulse train on the RING input signal t Preprogrammed CEIR address in a preselectedstandard (NEC, RCA or RC-5)t General-Purpose Input Events t IRQs of internal logical devices —Optional routing of power-up request on IRQ,SMIand/or PWBTOUT—Battery-backed event configuration—Programmable V SB -powered output for blinkingLEDs (LED1, LED2) control•Clock Sources—48 MHz clock input—LPC clock, up to 33 MHz—On-chip low frequency clock generator for wake-up•Power Supplies— 3.3V supply operation —Main (V DD and AV DD )—Standby (V SB )—Battery backup (V BA T )—All pins are 5V tolerant and back-drive protected,ex-cept LPC bus pins•Strap Configuration—Base Address (BADDR)strap to determine the baseaddress of the Index-Data register pair—T est strap to force the device into test mode (re-served for National Semiconductor use)—Power Supply and LED Configuration (PSLDC0,1)straps to determine the power suppy control func-tions and the V SB power-up defaults of LED2—Power Supply On Polarity (PSONPOL)strap to setPSON active state and output typeDatasheet Revision RecordRevision Date Status CommentsNovember1998Draft0.3Specification subject to change without notice;MIDI andGame Port information is incompleteJanuary1999Preliminary1.0Specification subject to change without notice;PowerSupply Control and LED sections in Chapter2areincompleteItem Topic Change/Correction Location 4Table of ContentsDatasheet Revision Record (4) (4)1.0Signal/Pin Connection and Description1.1CONNECTION DIAGRAM (16)1.2BUFFER TYPES AND SIGNAL/PIN DIRECTORY (17)1.3PIN MULTIPLEXING (22)1.4DETAILED SIGNAL/PIN DESCRIPTIONS (24)1.4.1ACCESS.bus Interface (ACB) (24)1.4.2Bus Interface (24)1.4.3Clock (24)1.4.4Fan Speed Control and Monitor (FSCM) (24)1.4.5Floppy Disk Controller (FDC) (25)1.4.6Game Port (26)1.4.7General-Purpose Input/Output (GPIO) Ports (26)1.4.8Infrared (IR) (26)1.4.9Keyboard and Mouse Controller (KBC) (27)1.4.10Musical Instrument Digital Interface (MIDI) Port (27)1.4.11Parallel Port (28)1.4.12Power and Ground (28)1.4.13Protection (29)1.4.14Serial Port 1 and Serial Port 2 (29)1.4.15Strap Configuration (30)1.4.16System Hardware Monitoring (30)1.4.17System Wake-Up Control (31)1.4.18WATCHDOG Timer (WDT) (31)1.5INTERNAL PULL-UP AND PULL-DOWN RESISTORS (32)2.0Device Architecture and Configuration2.1OVERVIEW (34)2.2CONFIGURATION STRUCTURE AND ACCESS (34)2.2.1The Index-Data Register Pair (34)2.2.2Banked Logical Device Registers Structure (36)2.2.3Standard Logical Device Configuration Register Definitions (37)2.2.4Standard Configuration Registers (39)2.2.5Default Configuration Setup (40)2.2.6Power States (40)2.2.7Address Decoding (41)2.3PROTECTION (41)2.3.1Chassis Intrusion Detection (41)2.3.2Pin Configuration Lock (41)2.3.3GPIO Pin Function Lock (42)2.4POWER SUPPLY CONTROL (PSC) (42)2.5LED OPERATION AND STATES (44)2.6POWER SUPPLY CONTROL AND LED CONFIGURATION (44)2.7REGISTER TYPE ABBREVIATIONS (45)2.8SUPERI/O CONFIGURATION REGISTERS (45)2.8.1SuperI/O ID Register (SID) (46)2.8.2SuperI/O Configuration 1 Register (SIOCF1) (46)2.8.3SuperI/O Configuration 2 Register (SIOCF2) (47)2.8.4SuperI/O Configuration 3 Register (SIOCF3) (48)2.8.5SuperI/O Configuration 4 Register (SIOCF4) (49)2.8.6SuperI/O Configuration 5 Register (SIOCF5) (50)2.8.7SuperI/O Revision ID Register (SRID) (50)2.8.8SuperI/O Configuration 8 Register (SIOCF8) (51)2.8.9SuperI/O Configuration A Register (SIOCFA) (52)2.8.10SuperI/O Configuration B Register (SIOCFB) (53)2.8.11SuperI/O Configuration C Register (SIOCFC) (54)2.8.12SuperI/O Configuration D Register (SIOCFD) (55)2.9FLOPPY DISK CONTROLLER (FDC) CONFIGURATION (56)2.9.1General Description (56)2.9.2Logical Device 0 (FDC) Configuration (56)2.9.3FDC Configuration Register (57)2.9.4Drive ID Register (58)2.10PARALLEL PORT CONFIGURATION (59)2.10.1General Description (59)2.10.2Logical Device 1 (PP) Configuration (60)2.10.3Parallel Port Configuration Register (60)2.11SERIAL PORT 2 CONFIGURATION (61)2.11.1General Description (61)2.11.2Logical Device 2 (SP2) Configuration (61)2.11.3Serial Port 2 Configuration Register (61)2.12SERIAL PORT 1 CONFIGURATION (62)2.12.1Logical Device 3 (SP1) Configuration (62)2.12.2Serial Port 1 Configuration Register (62)2.13SYSTEM WAKE-UP CONTROL (SWC) CONFIGURATION (63)2.13.1Logical Device 4 (SWC) Configuration (63)2.14KEYBOARD AND MOUSE CONTROLLER (KBC) CONFIGURATION (64)2.14.1General Description (64)2.14.2Logical Devices 5 and 6 (Mouse and Keyboard) Configuration (65)2.14.3KBC Configuration Register (66)2.15GENERAL-PURPOSE INPUT/OUTPUT (GPIO) PORTS CONFIGURATION (67)2.15.1General Description (67)2.15.2Implementation (67)2.15.3Logical Device 7 (GPIO) Configuration (68)2.15.4GPIO Pin Select Register (69)2.15.5GPIO Pin Configuration Register (70)2.15.6GPIO Event Routing Register (71)62.16ACCESS.BUS INTERFACE (ACB) CONFIGURATION (72)2.16.1General Description (72)2.16.2Logical Device 8 (ACB) Configuration (72)2.16.3ACB Configuration Register (73)2.17FAN SPEED CONTROL AND MONITOR (FSCM) CONFIGURATION (74)2.17.1General Description (74)2.17.2Logical Device 9 (FSCM) Configuration (74)2.17.3Fan Speed Control and Monitor Configuration 1 Register (75)2.17.4Fan Speed Control and Monitor Configuration 2 Register (76)2.17.5Fan Speed Control OTS Configuration Register (76)2.18WATCHDOG TIMER (WDT) CONFIGURATION (77)2.18.1Logical Device 10 (WDT) Configuration (77)2.18.2WATCHDOG Timer Configuration Register (77)2.19GAME PORT (GMP) CONFIGURATION (78)2.19.1Logical Device 11 (GMP) Configuration (78)2.19.2Game Port Configuration Register (78)2.20MIDI PORT (MIDI) CONFIGURATION (79)2.20.1Logical Device 12 (MIDI) Configuration (79)2.20.2MIDI Port Configuration Register (79)2.21VOLTAGE LEVEL MONITOR (VLM) CONFIGURATION (80)2.21.1Logical Device 13 (VLM) Configuration (80)2.22TEMPERATURE SENSOR (TMS) CONFIGURATION (80)2.22.1Logical Device 14 (TMS) Configuration (80)3.0System Wake-Up Control (SWC)3.1OVERVIEW (81)3.2FUNCTIONAL DESCRIPTION (82)3.3EVENT DETECTION (83)3.3.1Modem Ring (83)3.3.2Telephone Ring (83)3.3.3Keyboard and Mouse Activity (84)3.3.4CEIR Address (84)3.3.5Standby General-Purpose Input Events (84)3.3.6GPIO-Triggered Events (84)3.3.7Software Event (84)3.3.8Module IRQ Wake-Up Event (85)3.4SWC REGISTERS (85)3.4.1SWC Register Map (85)3.4.2Wake-Up Events Status Register 0 (WK_STS0) (88)3.4.3Wake-Up Events Status Register (WK_STS1) (89)3.4.4Wake-Up Events Enable Register (WK_EN0) (90)3.4.5Wake-Up Events Enable Register 1 (WK_EN1) (91)3.4.6Wake-Up Configuration Register (WK_CFG) (92)3.4.7Wake-Up Events Routing to SMI Enable Register 0 (WK_SMIEN0) (93)3.4.8Wake-Up Events Routing to SMI Enable Register 1 (WK_SMIEN1) (94)3.4.9Wake-Up Events Routing to IRQ Enable Register 0 (WK_IRQEN0) (95)3.4.10Wake-Up Events Routing to IRQ Enable Register 1 (WK_IRQEN1) (96)3.4.11Wake-Up Extension 1 Enable Register 0 (WK_X1EN0) (97)3.4.12Wake-Up Extension 1 Enable Register 1 (WK_X1EN1) (98)3.4.13Wake-Up Extension 2 Enable Register 0 (WK_X2EN0) (99)3.4.14Wake-Up Extension 2 Enable Register 1 (WK_X2EN1) (100)3.4.15Wake-Up Extension 3 Enable Register 0 (WK_X3EN0) (101)3.4.16Wake-Up Extension 3 Enable Register 1 (WK_X3EN1) (102)3.4.17PS/2 Keyboard and Mouse Wake-Up Events (103)3.4.18PS/2 Protocol Control Register (PS2CTL) (104)3.4.19Keyboard Data Shift Register (KDSR) (104)3.4.20Mouse Data Shift Register (MDSR) (105)3.4.21PS/2 Keyboard Key Data Registers (PS2KEY0 - PS2KEY7) (105)3.4.22CEIR Wake-Up Control Register (IRWCR) (106)3.4.23CEIR Wake-Up Address Register (IRWAD) (107)3.4.24CEIR Wake-Up Address Mask Register (IRWAM) (107)3.4.25CEIR Address Shift Register (ADSR) (108)3.4.26CEIR Wake-Up Range 0 Registers (108)3.4.27CEIR Wake-Up Range 1 Registers (109)3.4.28CEIR Wake-Up Range 2 Registers (109)3.4.29CEIR Wake-Up Range 3 Registers (110)3.4.30Standby General-Purpose I/O (SBGPIO) Register Overview (111)3.4.31Standby GPIO Pin Select Register (SBGPSEL) (114)3.4.32Standby GPIO Pin Configuration Register (SBGPCFG) (115)3.4.33Standby GPIOE/GPIE Data Out Register 0 (SB_GPDO0) (117)3.4.34Standby GPIOE/GPIE Data In Register 0 (SB_GPDI0) (117)3.4.35Standby GPOS Data Out Register 1 (SB_GPDO1) (118)3.4.36Standby GPIS Data In Register 1 (SB_GPDI1) (118)3.5SWC REGISTER BITMAP (119)4.0Fan Speed Control4.1OVERVIEW (123)4.2FUNCTIONAL DESCRIPTION (123)4.3FAN SPEED CONTROL REGISTERS (124)4.3.1Fan Speed Control Register Map (124)4.3.2Fan Speed Control Pre-Scale Register (FCPSR) (124)4.3.3Fan Speed Control Duty Cycle Register (FCDCR) (125)4.4FAN SPEED CONTROL BITMAP (125)5.0Fan Speed Monitor5.1OVERVIEW (126)5.2FUNCTIONAL DESCRIPTION (126)5.3FAN SPEED MONITOR REGISTERS (127)5.3.1Fan Speed Monitor Register Map (127)85.3.2Fan Monitor Threshold Register (FMTHR) (128)5.3.3Fan Monitor Speed Register (FMSPR) (128)5.3.4Fan Monitor Control and Status Register (FMCSR) (128)5.4FAN SPEED MONITOR BITMAP (129)6.0General-Purpose Input/Output (GPIO) Port6.1OVERVIEW (130)6.2BASIC FUNCTIONALITY (131)6.2.1Configuration Options (131)6.2.2Operation (131)6.3EVENT HANDLING AND SYSTEM NOTIFICATION (132)6.3.1Event Configuration (132)6.3.2System Notification (132)6.4GPIO PORT REGISTERS (133)6.4.1GPIO Pin Configuration (GPCFG) Register (134)6.4.2GPIO Pin Event Routing (GPEVR) Register (135)6.4.3GPIO Port Runtime Register Map (135)6.4.4GPIO Data Out Register (GPDO) (136)6.4.5GPIO Data In Register (GPDI) (136)6.4.6GPIO Event Enable Register (GPEVEN) (137)6.4.7GPIO Event Status Register (GPEVST) (137)7.0WATCHDOG Timer (WDT)7.1OVERVIEW (138)7.2FUNCTIONAL DESCRIPTION (138)7.3WATCHDOG TIMER REGISTERS (139)7.3.1WATCHDOG Timer Register Map (139)7.3.2WATCHDOG Timeout Register (WDTO) (139)7.3.3WATCHDOG Mask Register (WDMSK) (140)7.3.4WATCHDOG Status Register (WDST) (141)7.4WATCHDOG TIMER REGISTER BITMAP (141)8.0ACCESS.bus Interface (ACB)8.1OVERVIEW (142)8.2FUNCTIONAL DESCRIPTION (142)8.2.1Data Transactions (142)8.2.2Start and Stop Conditions (142)8.2.3Acknowledge (ACK) Cycle (143)8.2.4Acknowledge after Every Byte Rule (144)8.2.5Addressing Transfer Formats (144)8.2.6Arbitration on the Bus (144)8.2.7Master Mode (145)8.2.8Slave Mode (147)8.2.9Configuration (147)8.3ACB REGISTERS (148)8.3.1ACB Register Map (148)8.3.2ACB Serial Data Register (ACBSDA) (148)8.3.3ACB Status Register (ACBST) (149)8.3.4ACB Control Status Register (ACBCST) (150)8.3.5ACB Control Register 1 (ACBCTL1) (151)8.3.6ACB Own Address Register (ACBADDR) (152)8.3.7ACB Control Register 2 (ACBCTL2) (152)8.4ACB REGISTER BITMAP (153)9.0Game Port (GMP)9.1OVERVIEW (154)9.2FUNCTIONAL DESCRIPTION (154)9.2.1Game Device Axis Position Indication (154)9.2.2Capturing the Position (155)9.2.3Button Status Indication (156)9.2.4Operation Modes (156)9.2.5Operation Control (157)9.3GAME PORT REGISTERS (158)9.3.1Game Port Register Map (158)9.3.2Game Port Control Register (GMPCTL) (159)9.3.3Game Port Legacy Status Register (GMPLST) (160)9.3.4Game Port Extended Status Register (GMPXST) (161)9.3.5Game Port Interrupt Enable Register (GMPIEN) (162)9.3.6Game Device A X-Axis Position Low Byte (GMPAXL) (163)9.3.7Game Device A X-Axis Position High Byte (GMPAXH) (163)9.3.8Game Device A YAxis Position Low Byte (GMPAYL) (163)9.3.9Game Device A Y-Axis Position High Byte (GMPAYH) (163)9.3.10Game Device B X-Axis Position Low Byte (GMPBXL) (164)9.3.11Game Device B X-Axis Position High Byte (GMPBXH) (164)9.3.12Game Device B Y-Axis Position Low Byte (GMPBYL) (164)9.3.13Game Device B Y-Axis Position High Byte (GMPBYH) (164)9.3.14Game Port Event Polarity Register (GMPEPOL) (165)9.4GAME PORT BITMAP (166)10.0Musical Instrument Digital Interface (MIDI) Port10.1OVERVIEW (167)10.2FUNCTIONAL DESCRIPTION (167)10.2.1Internal Bus Interface Unit (168)10.2.2Port Control and Status Registers (168)10.2.3Data Buffers and FIFOs (168)10.2.4MIDI Communication Engine (168)10.2.5MIDI Signals Routing Control Logic (169)10.2.6Operation Modes (169)10.2.7MIDI Port Status Flags (170)1010.2.8MIDI Port Interrupts (171)10.2.9Enhanced MIDI Port Features (172)10.3MIDI PORT REGISTERS (173)10.3.1MIDI Port Register Map (173)10.3.2MIDI Data In Register (MDI) (173)10.3.3MIDI Data Out Register (MDO) (173)10.3.4MIDI Status Register (MSTAT) (174)10.3.5MIDI Command Register (MCOM) (174)10.3.6MIDI Control Register (MCNTL) (175)10.4MIDI PORT BITMAP (176)11.0Voltage Level Monitor (VLM)11.1OVERVIEW (177)11.2FUNCTIONAL DESCRIPTION (177)11.2.1Voltage Measurement, Channels 0 through 10 (178)11.2.2Thermistor-Based Temperature Measurement, Channels 11 to 13 (179)11.2.3 V OS, V HIGH and V LOW Limits, OTS and ALERT Output, IRQ and SMI (179)11.2.4Power-On Reset Default States (180)11.2.5Standby Mode (180)11.3ANALOG SUPPLY CONNECTION (180)11.3.1Recommendations (180)11.3.2Reference Voltage (181)11.4REGISTER BANK OVERVIEW (181)11.5VLM REGISTERS (182)11.5.1VLM Register Map (182)11.5.2Voltage Event Status Register 0 (VEVSTS0) (183)11.5.3Voltage Event Status Register 1 (VEVSTS1) (183)11.5.4Voltage Event to SMI Register 0 (VEVSMI0) (184)11.5.5Voltage Event to SMI Register 1 (VEVSMI1) (185)11.5.6Voltage Event to IRQ Register 0 (VEVIRQ0) (186)11.5.7Voltage Event to IRQ Register 1 (VEVIRQ1) (186)11.5.8Voltage ID Register (VID) (187)11.5.9Voltage Conversion Rate Register (VCNVR) (188)11.5.10VLM Configuration Register (VLMCFG) (189)11.5.11VLM Bank Select Register (VLMBS) (189)11.5.12Voltage Channel Configuration and Status Register (VCHCFST) (190)11.5.13Read Channel Voltage Register (RDCHV) (191)11.5.14Channel Voltage High Limit Register (CHVH) (191)11.5.15Channel Voltage Low Limit Register (CHVL) (191)11.5.16Overtemperature Shutdown Limit Register (OTSL) (191)11.6VLM REGISTER BITMAP (192)11.6.1VLM Control and Status Registers (192)11.6.2VLM Channel Registers (192)11.7USAGE HINTS (193)11.7.2Measuring Out of Range Positive and Negative Voltages (194)12.0Temperature Sensor (TMS)12.1OVERVIEW (195)12.2FUNCTIONAL DESCRIPTION (195)12.2.1Register Bank Overview (196)12.2.2T OS, T HIGH and T LOW Limits, OTS and ALERT Output, IRQ and SMI (196)12.2.3ALERT Response Read Sequence (197)12.2.4Power-On Reset Default States (197)12.2.5Temperature Data Format (198)12.2.6Standby Mode (198)12.2.7Diode Fault Detection (198)12.3TMS REGISTERS (199)12.3.1TMS Register Map (199)12.3.2Temperature Event Status Register (TEVSTS) (200)12.3.3Temperature Event to SMI Register (TEVSMI) (201)12.3.4Temperature Event to IRQ Register (TEVIRQ) (202)12.3.5TMS Configuration Register (TMSCFG) (203)12.3.6TMS Bank Select Register (TMSBS) (203)12.3.7Temperature Channel Configuration and Status Register (TCHCFST) (204)12.3.8Read Channel Temperature Register (RDCHT) (205)12.3.9Channel Temperature High Limit Register (CHTH) (205)12.3.10Channel Temperature Low Limit Register (CHTL) (205)12.3.11Channel Overtemperature Limit Register (CHOTL) (205)12.4TMS REGISTER BITMAP (206)12.4.1TMS Control and Status Registers (206)12.4.2TMS Channel Registers (206)12.5USAGE HINTS (206)12.5.1Remote Diode Selection (206)12.5.2ADC Noise Filtering (207)12.5.3PC Board Layout (207)12.5.4Twisted Pair and Shielded Cables (209)13.0Legacy Functional Blocks13.1KEYBOARD AND MOUSE CONTROLLER (KBC) (210)13.1.1General Description (210)13.1.2KBC Register Map (210)13.1.3KBC Bitmap Summary (210)13.2FLOPPY DISK CONTROLLER (FDC) (211)13.2.1General Description (211)13.2.2FDC Register Map (211)13.2.3FDC Bitmap Summary (212)13.3PARALLEL PORT (213)13.3.1General Description (213)13.3.3Parallel Port Bitmap Summary (214)13.4UART FUNCTIONALITY (SP1 AND SP2) (216)13.4.1General Description (216)13.4.2UART Mode Register Bank Overview (216)13.4.3SP1 and SP2 Register Maps for UART Functionality (217)13.4.4SP1 and SP2 Bitmap Summary for UART Functionality (219)13.5IR FUNCTIONALITY (SP2) (221)13.5.1General Description (221)13.5.2IR Mode Register Bank Overview (221)13.5.3SP2 Register Map for IR Functionality (222)13.5.4SP2 Bitmap Summary for IR Functionality (223)14.0Device Characteristics14.1GENERAL DC ELECTRICAL CHARACTERISTICS (225)14.1.1Recommended Operating Conditions (225)14.1.2Absolute Maximum Ratings (225)14.1.3Capacitance (225)14.1.4Power Consumption under Recommended Operating Conditions (226)14.2DC CHARACTERISTICS OF PINS, BY I/O BUFFER TYPES (226)14.2.1Input, CMOS Compatible (226)14.2.2Input, PCI 3.3V (226)14.2.3Input, SMBus Compatible (227)14.2.4Input, Strap Pin (227)14.2.5Input, TTL Compatible (227)14.2.6Input, TTL Compatible with Schmitt Trigger (227)14.2.7Output, PCI 3.3V (228)14.2.8Output, Totem-Pole Buffer (228)14.2.9Output, Open-Drain Buffer (228)14.2.10Input, Analog (228)14.2.11Input, Analog (228)14.2.12Input, Analog (229)14.2.13Output, Analog (229)14.2.14Output, Analog (229)14.2.15Exceptions (229)14.3INTERNAL RESISTORS (230)14.3.1Pull-Up Resistor (230)14.3.2Pull-Down Resistor (230)14.4ANALOG CHARACTERISTICS (230)14.4.1VLM (230)14.4.2TMS (230)14.5AC ELECTRICAL CHARACTERISTICS (232)14.5.1AC Test Conditions (232)14.5.2Clock Timing (232)14.5.3LCLK and LRESET (233)14.5.5Serial Port, Sharp-IR, SIR and Consumer Remote Control Timing (235)14.5.6Modem Control Timing (236)14.5.7FDC Write Data Timing (236)14.5.8FDC Drive Control Timing (237)14.5.9FDC Read Data Timing (237)14.5.10Standard Parallel Port Timing (238)14.5.11Enhanced Parallel Port Timing (238)14.5.12Extended Capabilities Port (ECP) Timing (239)。

UMZ6.8ENTR;中文规格书,Datasheet资料

Zener diodeUMZ6.8ENz Application z Lead size figure (Unit : mm)Voltage regulation(Anode common twin type)z Features1) Small mold type. (UMD5)2) High reliability.z StructureSilicon epitaxial planerz Structurez Absolute maximum ratings (Ta=25°C)SymbolUnit P mW Tj °C Tstg °Cz Electrical characteristics (Ta=25°C)SymbolMin.Typ.Max.Unit ConditionsV Z 6.47-7.14V I Z =5mA I R --0.50µA V R =3.5V Z Z--40ΩI Z =5mADynamic impedance (*1) Total of 2 elementsZener voltage Reverse current Parameter Parameter Limits Power dissipation (*1)200Junction temperature 150Storage temperature -55 to +150UMZ6.8ENz Electrical characteristics curves11010010000.0010.11010001101000.11101515.51616.51717.51818.51919.52000.020.040.060.080.10.120.140.160.180.20.000010.00010.0010.010.1110100012340.010.111066.577.586.76.86.977.17.2REVERSE VOLTAGE : V R (V)V R -I R CHARACTERISTICSR E V E R S E C U R R E N T :I R (n A )R E V E R S E C U R R E N T :I R (n A )I R DISRESION MAPC A P A C I T A N C E B E T W E E N T E R M I N A L S :C t (p F )REVERSE VOLTAGE : V R (V)V R -Ct CHARACTERISTICSCt DISRESION MAPC A P A C I T A N C E B E T W E E N T E R M I N A L S :C t (p F )Z E N E R C U R R E N T :I z (m A )ZENER VOLTAGE : Vz(V)Vz-Iz CHARACTERISTICSVz DISRESION MAPZ E N E R V O L T A G E :V z (V)TIME:t(s)Rth-t CHARACTERISTICST R A N S I E N T T H A E R M A L I M P E D A N C E :R t h (°C /W )110100123456D Y N A M I C I M PE D A N C E :Z z (Ω)ZENER CURRENT(mA)Zz-Iz CHARACTERISTICSData SheetNoticeN o t e sNo copying or reproduction of this document, in part or in whole, is permitted without theconsent of ROHM Co.,Ltd.The content specified herein is subject to change for improvement without notice.The content specified herein is for the purpose of introd ucing ROHM's prod ucts (hereinafter"Products"). If you wish to use any such Product, please be sure to refer to the specifications,which can be obtained from ROHM upon request.Examples of application circuits, circuit constants and any other information contained hereinillustrate the standard usage and operations of the Products. The peripheral conditions mustbe taken into account when designing circuits for mass production.Great care was taken in ensuring the accuracy of the information specified in this document.However, should you incur any d amage arising from any inaccuracy or misprint of suchinformation, ROHM shall bear no responsibility for such damage.The technical information specified herein is intended only to show the typical functions of andexamples of application circuits for the Prod ucts. ROHM d oes not grant you, explicitly orimplicitly, any license to use or exercise intellectual property or other rights held by ROHM andother parties. ROHM shall bear no responsibility whatsoever for any dispute arising from theuse of such technical information.The Products specified in this document are intended to be used with general-use electronicequipment or devices (such as audio visual equipment, office-automation equipment, commu-nication devices, electronic appliances and amusement devices).The Products specified in this document are not designed to be radiation tolerant.While ROHM always makes efforts to enhance the quality and reliability of its Prod ucts, aProduct may fail or malfunction for a variety of reasons.Please be sure to implement in your equipment using the Products safety measures to guardagainst the possibility of physical injury, fire or any other d amage caused in the event of thefailure of any Product, such as derating, redundancy, fire control and fail-safe designs. ROHMshall bear no responsibility whatsoever for your use of any Product outside of the prescribedscope or not in accordance with the instruction manual.The Products are not designed or manufactured to be used with any equipment, device orsystem which requires an extremely high level of reliability the failure or malfunction of whichmay result in a direct threat to human life or create a risk of human injury (such as a medicalinstrument, transportation equipment, aerospace machinery, nuclear-reactor controller,fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use ofany of the Products for the above special purposes. If a Product is intended to be used for anysuch special purpose, please contact a ROHM sales representative before purchasing.If you intend to export or ship overseas any Product or technology specified herein that maybe controlled under the Foreign Exchange and the Foreign Trade Law, you will be required toobtain a license or permit under the Law.Thank you for your accessing to ROHM product informations.More detail product informations and catalogs are available, please contact us.ROHM Customer Support System/contact/分销商库存信息: ROHMUMZ6.8ENTR。

61048中文资料

61048SILICON PHOTOTRANSISTOR(TYPE GS4123)Mii OPTOELECTRONIC PRODUCTSDIVISIONFeatures:• Hermeticallysealed• HighSensitivity•Base lead provided for conventional transistor biasing•Wide receiving angle for easy alignment •Spectrally Matched to the 62030 Series LED.A pplications:• IncrementalEncoding • ReflectiveSensors • PositionSensors • LevelSensorsDESCRIPTIONThis is a N-P-N Planar Silicon phototransistor in a flat window TO-46 three-lead package featuring a large (0.06” X 0.06”) sensitive area. It is available in a range of sensitivities and is ideal for use wherever system considerations dictate the use of external optics to focus radiation on the sensor. Available custom binned to customer specifications and/or screened to MIL-PRF-19500.ABSOLUTE MAXIMUM RATINGSStorage Temperature..........................................................................................................................................-65°C to +150°C Operating Temperature (See part selection guide for actual operating temperature)...................................... -65°C to +125°C Collector-Emitter Voltage.. (50V)Emitter-Collector Voltage (7V)Continuous Collector Current..............................................................................................................................................50mA Power Dissipation (Derate at the rate of 2.5 mW/°C above 25°C)..................................................................................250mW61048SILICON PHOTOTRANSISTOR (GS4123)RECOMMENDED OPERATING CONDITIONS:PARAMETER SYMBOL MIN MAX UNITS Bias Voltage-Collector/Emitter I F510mAIrradiance (H)H1525mW/cm2SELECTION GUIDEPART NUMBER PART DESCRIPTION I L Range61048-001Silicon Phototransistor in TO-46 package, commercial version 5 to 20mA61048-101Silicon Phototransistor in TO-46 package (-55° to +100°C) with 100% screening 5 to 20mA61048-002Silicon Phototransistor in TO-46 package, commercial version20 to 30mA61048-102Silicon Phototransistor in TO-46 package (-55° to +100°C) with 100% screening20 to 30mA61048-003Silicon Phototransistor in TO-46 package, commercial version30 to 50mA61048-103Silicon Phototransistor in TO-46 package (-55° to +100°C) with 100% screening30 to 50mA61048-004Silicon Phototransistor in TO-46 package, commercial version+50mA61048-104Silicon Phototransistor in TO-46 package (-55° to +100°C) with 100% screening+50mA。

展讯NAND Flash高级教程

内容介绍

本文档包括四个章节,分别为: y 第一章:NAND Flash 工作原理 y 第二章:SC6800H NAND Flash 控制器简介 y 第三章:SC6800H NAND Flash 控制器寄存器介绍 y 第四章:SC6800H NAND Flash 驱动配置及分析 y 第五章:SC6800H NAND Flash 常见问题分析

SC6800H NAND Flash 专题培训

Version: 3.2 Date: 2011-07-08

GSM FAE SZ Yongjun.Zang

前言

文档说明

本文档为展讯 SC6800H NAND Flash 专题培训资料。

阅读对象Biblioteka 本文档针对于所有 SC6800H 平台驱动工程师及硬件工程师。

1-1

1.8.3 Data Input .............................................................................................................................1-19 1.8.4 Data Output...........................................................................................................................1-20 1.9 NAND Flash 常用的软件管理方案 ..............................................................................................1-20 1.9.1 FTL(Flash Translation Layer)...............................................................................................1-21 1.9.2 XSR(eXtended Sector Remapper) ........................................................................................1-21 1.10 NAND Flash 常用的数据管理算法 ............................................................................................1-24 1.10.1 Garbage Collection .............................................................................................................1-24 1.10.2 Wear-Leveling Algorithm ...................................................................................................1-24 1.10.3 Error Correction Code.........................................................................................................1-24 1.11 主要参考文档..............................................................................................................................1-24

(2021年整理)adc0808中文资料

adc0808中文资料编辑整理:尊敬的读者朋友们:这里是精品文档编辑中心,本文档内容是由我和我的同事精心编辑整理后发布的,发布之前我们对文中内容进行仔细校对,但是难免会有疏漏的地方,但是任然希望(adc0808中文资料)的内容能够给您的工作和学习带来便利。

同时也真诚的希望收到您的建议和反馈,这将是我们进步的源泉,前进的动力。

本文可编辑可修改,如果觉得对您有帮助请收藏以便随时查阅,最后祝您生活愉快业绩进步,以下为adc0808中文资料的全部内容。

11.2。

4 典型的集成ADC芯片为了满足多种需要,目前国内外各半导体器件生产厂家设计并生产出了多种多样的ADC芯片。

仅美国AD公司的ADC产品就有几十个系列、近百种型号之多.从性能上讲,它们有的精度高、速度快,有的则价格低廉.从功能上讲,有的不仅具有A/D转换的基本功能,还包括内部放大器和三态输出锁存器;有的甚至还包括多路开关、采样保持器等,已发展为一个单片的小型数据采集系统。

尽管ADC芯片的品种、型号很多,其内部功能强弱、转换速度快慢、转换精度高低有很大差别,但从用户最关心的外特性看,无论哪种芯片,都必不可少地要包括以下四种基本信号引脚端:模拟信号输入端(单极性或双极性);数字量输出端(并行或串行);转换启动信号输入端;转换结束信号输出端。

除此之外,各种不同型号的芯片可能还会有一些其他各不相同的控制信号端.选用ADC芯片时,除了必须考虑各种技术要求外,通常还需了解芯片以下两方面的特性.(1)数字输出的方式是否有可控三态输出。

有可控三态输出的ADC 芯片允许输出线与微机系统的数据总线直接相连,并在转换结束后利用读数信号RD选通三态门,将转换结果送上总线。

没有可控三态输出(包括内部根本没有输出三态门和虽有三态门、但外部不可控两种情况)的ADC芯片则不允许数据输出线与系统的数据总线直接相连,而必须通过I/O接口与MPU交换信息。

(2)启动转换的控制方式是脉冲控制式还是电平控制式.对脉冲启动转换的ADC芯片,只要在其启动转换引脚上施加一个宽度符合芯片要求的脉冲信号,就能启动转换并自动完成。

2N6798中文资料

SOURCE DRAIN DIODE RATING CHARACTERISTICS

Diode Forward Voltage1 Continues Current Pulsed Current2 IF = IS dIF/DT = 100A/mS 150 Reverse Recovery Time Reverse Recovered Charge

VDS =0.8 x V(BR)DSS 0.25 2.5 3.0 600 250 80 8 42 12 30 IF = IS VGS = 0

mA W s(É)

pF

4.0

f = 1.0MHZ VDD = 77V ID = 3.5A

30 50 50 40 1.4 5.5 22 V A ns ns

RG = 7.5 ohms

Underside View PIN 1 – Source PIN 2 – Gate PIN 3 – Drain

ABSOLUTE MAXIMUM RATINGS (Tcase = 25°C unless otherwise stated)

VDS VGS ID Drain–Source Voltage Gate–Source Voltage Drain Current Continuous TC = 25°C TC = 100°C Drain Current Pulsed IDM IA Avalanche Current PD Total Device Dissipation @ TC = 25°C TC = 100°C TJ , TSTG Operating and Storage Junction Temperature Range THERMAL CHARACTERISTICS RqJC Thermal Resistance Junction to Case RqJC Thermal Resistance Junction to Ambient TL Maximum Lead Temperature 1.5mm from Case for 10 secs. 200V ±20V 5.5A 3.5A 22A 3.1A 25W 10W –55 to +150°C 5.0°CW 175°CW 300°C

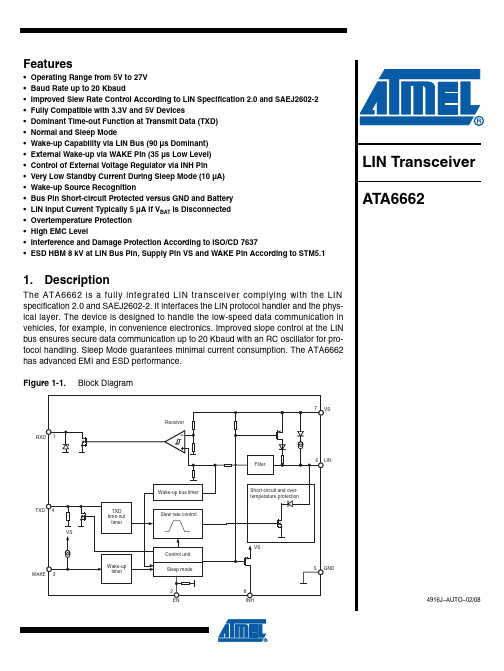

ATA6662_08资料

Features Array•Operating Range from 5V to 27V•Baud Rate up to 20 Kbaud•Improved Slew Rate Control According to LIN Specification 2.0 and SAEJ2602-2•Fully Compatible with 3.3V and 5V Devices•Dominant Time-out Function at Transmit Data (TXD)•Normal and Sleep Mode•Wake-up Capability via LIN Bus (90µs Dominant)•External Wake-up via WAKE Pin (35µs Low Level)•Control of External Voltage Regulator via INH Pin•Very Low Standby Current During Sleep Mode (10µA)•Wake-up Source Recognition•Bus Pin Short-circuit Protected versus GND and Battery•LIN Input Current Typically 5µA if VIs DisconnectedBAT•Overtemperature Protection•High EMC Level•Interference and Damage Protection According to ISO/CD7637•ESD HBM 8kV at LIN Bus Pin, Supply Pin VS and WAKE Pin According to STM5.1 1.DescriptionThe ATA6662 is a fully integrated LIN transceiver complying with the LIN specification2.0 and SAEJ2602-2. It interfaces the LIN protocol handler and the phys-ical layer. The device is designed to handle the low-speed data communication in vehicles, for example, in convenience electronics. Improved slope control at the LIN bus ensures secure data communication up to 20Kbaud with an RC oscillator for pro-tocol handling. Sleep Mode guarantees minimal current consumption. The ATA6662 has advanced EMI and ESD performance.Figure 1-1.Block Diagram24916J–AUTO–02/08ATA66622.Pin ConfigurationFigure 2-1.Pinning SO8Table 2-1.Pin DescriptionPin Symbol Function1RXD Receive data output (open drain)2EN Enables Normal Mode; when the input is open or low, the device is in Sleep Mode 3WAKE High voltage input for local wake-up request4TXD T ransmit data input; active low output (strong pull-down) after a local wake-up request 5GND Ground, heat sink 6LIN LIN bus line input/output 7VS Battery supply8INHBattery-related inhibit output for controlling an external voltage regulator; active high after a wake-up request34916J–AUTO–02/08ATA66623.Functional Description3.1Physical Layer CompatibilitySince the LIN physical layer is independent from higher LIN layers (e.g., the LIN protocol layer),all nodes with a LIN physical layer according to revision 2.0 can be mixed with LIN physical layer nodes, which, according to older versions (i.e., LIN 1.0, LIN 1.1, LIN 1.2, LIN 1.3), are without any restrictions.3.2Supply Pin (V S )Undervoltage detection is implemented to disable transmission if V S falls to a value below 5V in order to avoid false bus messages. After switching on V S , the IC switches to Pre-normal Mode and INHIBIT is switched on. The supply current in Sleep Mode is typically 10µA.3.3Ground Pin (GND)The ATA6662 is neutral on the LIN pin in the case of a GND disconnection. It is able to handle a ground shift up to 11.5% of V S .3.4Bus Pin (LIN)A low-side driver with internal current limitation and thermal shutdown and an internal pull-up resistor are implemented as specified for LIN 2.0. The voltage range is from –27V to +40V. This pin exhibits no reverse current from the LIN bus to V S , even in the case of a GND shift or V Batt disconnection. The LIN receiver thresholds are compatible to the LIN protocol specification.The fall time (from recessive to dominant) and the rise time (from dominant to recessive) are slope controlled. The output has a self-adapting short circuit limitation; that is, during current limitation,as the chip temperature increases, the current is reduced.3.5Input Pin (TXD)This pin is the microcontroller interface to control the state of the LIN output. TXD is low to bring LIN low. If TXD is high, the LIN output transistor is turned off. Then, the bus is in Recessive Mode via the internal pull-up resistor. The TXD pin is compatible to both a 3.3V or 5V supply.3.6TXD Dominant Time-out FunctionThe TXD input has an internal pull-down resistor. An internal timer prevents the bus line from being driven permanently in dominant state. If TXD is forced low longer than t dom >6ms, the pin LIN will be switched off (Recessive Mode). To reset this mode, switch TXD to high (>10µs)before switching LIN to dominant again.3.7Output Pin (RXD)This pin reports to the microcontroller the state of the LIN bus. LIN high (recessive) is reported by a high level at RXD, LIN low (dominant) is reported by a low voltage at RXD. The output is an open drain, therefore, it is compatible to a 3.3V or 5V power supply. The AC characteristics are defined with a pull-up resistor of 5k Ω to 5V and a load capacitor of 20pF. The output is short-current protected. In Unpowered Mode (V S =0V), RXD is switched off. For ESD protection a Zener diode is integrated, with V Z =6.1V.44916J–AUTO–02/08ATA66623.8Enable Input Pin (EN)This pin controls the Operation Mode of the interface. If EN =1, the interface is in Normal Mode,with the transmission path from TXD to LIN and from LIN to Rx both active. A falling edge on EN while TXD is already set to high, the device is switched to Sleep Mode and no transmission is possible. In Sleep Mode, the LIN bus pin is connected to V S with a weak pull-up current source.The device can transmit only after being woken up (see Section 3.9, “Inhibit Output Pin (INH)” ).During Sleep Mode the device is still supplied from the battery voltage. The supply current is typ-ically 10µA. The pin EN provides a pull-down resistor in order to force the transceiver into Sleep Mode in case the pin is disconnected.3.9Inhibit Output Pin (INH)This pin is used to control an external switchable voltage regulator having a wake-up input. Theinhibit pin provides an internal switch towards pin V S . If the device is in Normal Mode, the inhibit high-side switch is turned on and the external voltage regulator is activated. When the device is in Sleep Mode, the inhibit switch is turned off and disables the voltage regulator.A wake-up event on the LIN bus or at pin WAKE will switch the INH pin to the V S level. After a system power-up (V S rises from zero), the pin INH switches automatically to the V S level.3.10Wake-up Input Pin (WAKE)This pin is a high-voltage input used to wake the device up from Sleep Mode. It is usually con-nected to an external switch in the application to generate a local wake-up. If you do not need a local wake-up in your application, connect pin WAKE directly to pin VS. A pull-up current source with typically –10µA is implemented. The voltage threshold for a wake-up signal is 3V below the VS voltage with an output current of typically –3µA.Wake-up events from Sleep Mode:•LINbus •ENpin •WAKE pinFigure 3-1 on page 6, Figure 3-2 on page 7 and Figure 3-3 on page 7 show details of wake-up operations.54916J–AUTO–02/08ATA66623.11Operation Modes1.Normal ModeThis is the normal transmitting and Receiving Mode. All features are available.2.Sleep ModeIn this mode the transmission path is disabled and the device is in low power mode. Supply current from V Batt is typically 10µA. A wake-up signal from the LIN bus or via pin WAKE will be detected and will switch the device to Fail-safe Mode. If EN then switches to high, Normal Mode is activated. Input debounce timers at pin WAKE (t WAKE ), LIN (t BUS ) and EN (t sleep ,t nom ) prevent unwanted wake-up events due to automotive tran-sients or EMI. In Sleep Mode the INH pin is left floating. The internal termination between pin LIN and pin V S is disabled to minimize the power dissipation in case pin LIN is short-circuited to GND. Only a weak pull-up current (typical 10µA) between pin LIN and pin V S is present. The Sleep Mode can be activated independently from the actual level on pin LIN or WAKE, guaranteeing that the lowest power consumption is achievable even in the case of a continuous dominant level on pin LIN or a continuous LOW on pin WAKE.3.Fail-safe ModeAt system power-up, the device automatically switches to Fail-safe Mode. It switches the INH pin to a high state, to the V S level. The microcontroller of the application will then confirm the Normal Mode by setting the EN pin to high.3.12Remote Wake-up via Dominant Bus StateA voltage less than the LIN pre-wake detection V LINL at pin LIN activates the internal LIN transceiver.A falling edge at pin LIN, followed by a dominant bus level V BUSdom maintained for a certain time period (t BUS ) and a rising edge at pin LIN results in a remote wake-up request.The device switches to Fail-safe Mode. Pin INH is activated (switches to V S ) and the internal ter-mination resistor is switched on. The remote wake-up request is indicated by a low level at pin RXD to interrupt the microcontroller (see Figure 3-2 on page 7).3.13Local Wake-up via Pin WAKEA falling edge at pin WAKE, followed by a low level maintained for a certain time period (t WAKE ),results in a local wake-up request. The wake-up time (t WAKE ) ensures that no transient, accord-ing to ISO7637, creates a wake-up. The device switches to Fail-safe Mode. Pin INH is activated (switches to V S ) and the internal termination resistor is switched on. The local wake-up request is indicated by a low level at pin RXD to interrupt the microcontroller and a strong pull-down at pin TXD (see Figure 3-3 on page 7). The voltage threshold for a wake-up signal is 3V below the VS voltage with an output current of typical –3µA. Even in the case of a continuous low at pin WAKE it is possible to switch the IC into Sleep Mode via a low at pin EN. The IC will stay in Sleep Mode for an unlimited time. To generate a new wake up at pin WAKE it needs first a high signal >6µs before a negative edge starts the wake-up filtering time again.64916J–AUTO–02/08ATA66623.14Wake-up Source RecognitionThe device can distinguish between a local wake-up request (pin WAKE) and a remote wake-up request (dominant LIN bus). The wake-up source can be read on pin TXD in Fail-safe Mode. If an external pull-up resistor (typically 5k Ω) has been added on pin TXD to the power supply of the microcontroller, a high level indicates a remote wake-up request (weak pull-down at pin TXD) and a low level indicates a local wake-up request (strong pull-down at pin TXD).The wake-up request flag (signalled on pin RXD) as well as the wake-up source flag (signalled on pin TXD) are reset immediately if the microcontroller sets pin EN to high (see Figure 3-2 on page 7 and Figure 3-3 on page 7).Figure 3-1.Mode of Operation3.15Fail-safe Features•There are now reverse currents <15µA at pin LIN during loss of V BA T or GND; this is optimal behavior for bus systems where some slave nodes are supplied from battery or ignition.•Pin EN provides a pull-down resistor to force the transceiver into Sleep Mode if EN is disconnected.•Pin RXD is set floating if V BAT is disconnected.•Pin TXD provides a pull-down resistor to provide a static low if TXD is disconnected.•The LIN output driver has a current limitation, and if the junction temperature T j exceeds the thermal shut-down temperature T off , the output driver switches off.•The implemented hysteresis, T hys , enables the LIN output again after the temperature has been decreased.74916J–AUTO–02/08ATA6662Figure 3-2.LIN Wake-up Waveform DiagramFigure 3-3.Wake-up from Wake-up Switch84916J–AUTO–02/08ATA66624.Absolute Maximum RatingsStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.ParametersSymbolMin.Typ.Max.Unit V S- Continuous supply voltage–0.3+40V Wake DC and transient voltage (with 33-k Ω serial resistor)- Transient voltage due to ISO7637 (coupling 1 nF)–1–150+40+100V V Logic pins (RXD, TXD, EN)–0.3+5.5V LIN- DC voltage- Transient voltage due to ISO7637 (coupling 1 nF)–27–150+40+100V V INH- DC voltage–0.3+40VAccording to IBEE LIN EMCTest specification 1.0 following IEC 61000-4-2- Pin VS, LIN to GND- Pin WAKE (33 k Ω serial resistor)±6±5KV KVESD HBM following STM5.1with 1.5 k Ω/100 pF- Pin VS, LIN, WAKE to GND - Pin INH to GND ±8±6KV KV HBM ESDANSI/ESD-STM5.1JESD22-A114AEC-Q100 (002)±3KVCDM ESD STM 5.3.1±750V Junction temperature T j –40+150°C Storage temperature T stg –55+150°C Thermal shutdownT off 150165180°C Thermal shutdown hysteresis T hys 51020°CNote:1.Equivalent to discharge a 100-pF capacitor through a 1.5-k Ω resistor.5.Thermal ResistanceParametersSymbol Min.Typ.Max.Unit Thermal resistance junction ambientR thJA 145K/W Special heat sink at GND (pin 5) on PCB (fused lead frame to pin 5)R thJA80K/W94916J–AUTO–02/08ATA66626.Electrical Characteristics5V < V S < 27V , T j = –40°C to +150°C No.Parameters Test ConditionsPinSymbolMin.Typ.Max.UnitType*1V S Pin1.1DC voltage range nominal 7V S 513.527V A 1.2Supply current in Sleep ModeSleep ModeV lin > V Batt – 0.5V V Batt < 14V 7I VSstby 1020µA A 1.3Supply current in Normal Mode Bus recessive 7I VSrec 1.63mA A 1.4Bus dominantTotal bus load > 500Ω7I VSdom 1.63mA A 1.5V S undervoltage threshold on V Sth 4 4.95V A 1.6V S undervoltage threshold off V Sth 4.055V A 1.7V S undervoltage threshold hysteresis7V Sth_hys50500mVA2RXD Output Pin (Open Drain)2.1Low-level input current Normal ModeV LIN = 0V , V RXD = 0.4V 1I RXDL 1.32.58mA A 2.2RXD saturation voltage 5-k Ω pull-up resistor to 5V 1Vsat RXD 0.4V A 2.3High-level leakage current Normal ModeV LIN = V BA T , V RXD = 5V 1I RXDH –3+3µA A 2.4ESD zener diode I RXD = 100 µA1VZ RXD5.88.6VA3TXD Input Pin 3.1Low-level voltage input 4V TXDL –0.3+0.8V A 3.2High-level voltage input 4V TXDH 27V A 3.3Pull-down resistor V TXD = 5V 4R TXD 125250600k ΩA 3.4Low-level leakage current V TXD = 0V4I TXD –3+3µA A 3.5Low-level input current at local wake-up request Fail-safe ModeV LIN = V BA T ; V WAKE = 0V4I TXDwake1.32.58mAA4EN InputPin4.1Low-level voltage input 2V ENL –0.3+0.8V A 4.2High-level voltage input 2V ENH 27V A 4.3Pull-down resistor V EN = 5V 2R EN 125250600k ΩA 4.4Low-level input current V EN = 0V2I EN–3+3µAA5INH Output Pin 5.1High-level voltage Normal Mode I INH = –2mA8V INHH V S – 3V S V A 5.2High-level leakage current Sleep ModeV INH = 27V , V Batt = 27V8I INHL–3+3µAA6WAKE Pin6.1High-level input voltage 3V WAKEH V S – 1V V S + 0.3V V A 6.2Low-level input voltageI WAKE = T ypically –3µA3V WAKEL–1VV S – 3VVA*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter104916J–AUTO–02/08ATA66626.3Wake pull-up current V S < 27V3I WAKE –30–10µA A 6.4High-level leakage current V S = 27V , V WAKE = 27V3I WAKE–5+5µAA7LIN Bus Driver7.1Driver recessive output voltage R LOAD = 500Ω/1k Ω6V BUSrec 0.9 × V SV S V A 7.2Driver dominant voltage V BUSdom_DRV_LoSUP V VS = 7V , R load = 500Ω6V _LoSUP 1.2V A 7.3Driver dominant voltage V BUSdom_DRV_HiSUP V VS = 18V , R load = 500Ω6V _HiSUP 2V A 7.4Driver dominant voltage V BUSdom_DRV_LoSUP V VS = 7V , R load = 1000Ω6V _LoSUP_1k 0.6V A 7.5Driver dominant voltage V BUSdom_DRV_HiSUP V VS = 18V , R load = 1000Ω 6V _HiSUP_1k_0.8V A 7.6Pull-up resistor to V S The serial diode is mandatory6R LIN 203060k ΩA 7.7LIN current limitation V BUS = V BAT_max6I BUS_LIM 40120200mA A 7.8Input leakage current at the receiver, including pull-up resistor as specifiedInput leakage current Driver offV BUS = 0V , V Batt = 12V 6I BUS_PAS_dom–1mAA7.9Leakage current LIN recessiveDriver off8V < V BA T < 18V 8V < V BUS < 18V V BUS ≥ V BA T6I BUS_PAS_rec1520µA A7.10Leakage current at ground loss;Control unit disconnected from ground; Loss of local groundmust not affect communication in the residual networkGND Device = V SV BA T =12V 0V < V BUS < 18V 6I BUS_NO_gnd–10+0.5+10µA A7.11Node has to sustain the currentthat can flow under thiscondition; Bus must remainoperational under this condition V BA T disconnectedV SUP_Device = GND0V < V BUS < 18V6I BUS515µA A8LIN Bus Receiver8.1Center of receiver threshold V BUS_CNT =(V th_dom + V th_rec )/26V BUS_CNT 0.475 × V S 0.5 × V S 0.525 × V S V A 8.2Receiver dominant state V EN = 5V 6V BUSdom –270.4 × V S V A 8.3Receiver recessive state V EN = 5V6V BUSrec 0.6 × V S40V A 8.4Receiver input hysteresis V HYS = V th_rec – V th_dom6V BUShys 0.028 × V S 0.1 × V S 0.175 × V S V A 8.5Pre-wake detection LIN High-level input voltage 6V LINH V S – 1V V S + 0.3V V A 8.6Pre-wake detection LIN Low-level input voltageSwitches the LIN receiver on 6V LINL–27VV S – 3.3VVA6.Electrical Characteristics (Continued)5V < V S < 27V , T j = –40°C to +150°C No.Parameters Test Conditions Pin Symbol Min.Typ.Max.Unit Type**) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameterATA6662 9Internal Timers9.1Dominant time for wake-up viaLIN busV LIN = 0V6t BUS3090150µs A9.2Time of low pulse for wake-upvia pin WAKEV WAKE = 0V3t WAKE73550µs A9.3Time delay for mode changefrom Fail-safe Mode to NormalMode via pin ENV EN = 5V2t norm2715µs A9.4Time delay for mode changefrom Normal Mode into SleepMode via pin ENV EN = 0V2t sleep2712µs A9.5TXD dominant time out timer V TXD = 0V4t dom6920ms A9.6Power-up delay betweenV S=5V until INH switches tohighV VS = 5V t VS200µs A10LIN Bus Driver (see Figure 6-1 on page 12)Bus load conditions: Load1, small, 1nF 1kΩ; Load2, big, 10nF 500Ω; R RXD = 5kΩ; C RXD = 20pF; The following two rows specify the timing parameters for proper operation at 20.0kBits/s.10.1Duty cycle 1TH Rec(max) = 0.744 × V STH Dom(max) = 0.581 × V SV S = 7.0V to 18Vt Bit = 50 µsD1 = t bus_rec(min)/(2 × t Bit)6D10.396A10.2Duty cycle 2TH Rec(min) = 0.422 × V STH Dom(min) = 0.284 × V SV S = 7.0V to 18Vt Bit = 50 µsD2 = t bus_rec(max)/(2 × t Bit)6D20.581A10.3Duty cycle 3TH Rec(max) = 0.778 × V STH Dom(max) = 0.616 × V SV S = 7.0V to 18Vt Bit = 96 µsD3 = t bus_rec(min)/(2 × t Bit)6D30.417A10.4Duty cycle 4TH Rec(max) = 0.389 × V STH Dom(max) = 0.251 × V SV S = 7.0V to 18Vt Bit = 96 µsD4 = t bus_rec(min)/(2 × t Bit)6D40.590A11Receiver Electrical AC Parameters of the LIN Physical Layer LIN receiver, RXD load conditions (C RXD): 20 pF, R pull-up = 5 kΩ11.1Propagation delay of receiver(see Figure 6-1 on page 12)t rec_pd = max(t rx_pdr, t rx_pdf)V S = 7.0V to 18V1t rx_pd6µs A11.2Symmetry of receiverpropagation delay rising edgeminus falling edget rx_sym = t rx_pdr – t rx_pdfV S = 7.0V to 18V1t rx_sym–2+2µs A6.Electrical Characteristics (Continued)5V < V S < 27V, T j = –40°C to +150°CNo.Parameters Test Conditions Pin Symbol Min.Typ.Max.Unit Type* *) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter11Figure 6-1.Definition of Bus Timing Parameter12ATA6662ATA6662 Figure 6-2.Application Circuit137.Ordering InformationExtended Type Number Package RemarksA T A6662-TAQY SO8LIN transceiver, Pb-free, 4k, taped and reeled8.Package Information14ATA6662ATA6662 9.Revision HistoryPlease note that the following page numbers referred to in this section refer to the specific revisionmentioned, not to this document.Revision No.History4916J-AUTO-02/08• “Pre-normal Mode” in “Fail-safe Mode” changed• Section 3.9 “Inhibit Output Pin (INH) on page 4 changed• Section 4 “Absolute Maximum Ratings” on page 8 changed• Section 6 “Electrical Characteristics” number 5.1 on page 9 changed4916I-AUTO-12/07• Section 3.1 “Physical Layer Compatibility” on page 3 added• Section 6 “Electrical Characteristics” numbers 1.5, 1.6 and 1.7 on page 9 changed4916H-AUTO-10/07• Section 7 “Ordering Information” on page 14 changed4916G-AUTO-07/07• Put datasheet in a new template• Capital T for time generally changed in a lower case t4916F-AUTO-05/07• Figure 1-1 “Block Diagram” on page 1 changed• Figure 6-2 “Application Circuit” on page 13 changed• Features on page 1 changed• Section 6 “Electrical Characteristics” numbers 10.1 to 10.4 and 11.1, 11.2 changed4916E-AUTO-02/07• Section 4 “Absolute Maximum Ratings” on page 8 changed • Section 2 “Electrical Characteristics” on pages 9 to 11 changed4916D-AUTO-02/07• Features on page 1 changed• Section 1 “Description” on page 1 changed• Table 2-1 “Pin Description” on page 2 changed• Section 3.2 “Ground Pin (GND) on page 3 changed• Section 3.7 “Enable Input Pin (EN)” on page 4 changed• Section 3.11 “Remote Wake-up via Dominant Bus State” on page 5 changed• Figure 3-1 “Mode of Operation” on page 6 changed• Section 3-14 “Fail-safe Features” on page 6 changed• Section 4 “Absolute Maximum Ratings” on page 8 changed• Section 6 “Electrical Characteristics” on pages 9 to 11 changed15Headquarters InternationalAtmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USATel: 1(408) 441-0311 Fax: 1(408) 487-2600Atmel AsiaRoom 1219Chinachem Golden Plaza77 Mody Road TsimshatsuiEast KowloonHong KongTel: (852) 2721-9778Fax: (852) 2722-1369Atmel EuropeLe Krebs8, Rue Jean-Pierre TimbaudBP 30978054Saint-Quentin-en-Yvelines CedexFranceTel: (33) 1-30-60-70-00Fax: (33) 1-30-60-71-11Atmel Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Product ContactWeb SiteTechnical Supportauto_control@Sales Contact/contactsLiterature Requests/literatureDisclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise,to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.© 2008 Atmel Corporation. All rights reserved. Atmel®, logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.。

SA58672资料